## REALTEK

#### **RTL8305SB**

### REALTEK SINGLE CHIP 5-PORT 10/100 MBPS SWITCH CONTROLLER RTL8305SB

| 1  | . Features2                                                       |

|----|-------------------------------------------------------------------|

|    | General Description                                               |

|    | Block Diagram                                                     |

|    | . Pin Assignments                                                 |

|    | Pin Descriptions                                                  |

| Э. | 5.1 Media Connection Pins                                         |

|    | 5.2 Configuration Pins                                            |

|    | 5.3 Port4 External MAC Interface Pins                             |

|    | 5.4 Miscellaneous Pins                                            |

|    | 5.5 Per Port LED Pins                                             |

|    |                                                                   |

|    | 5.6 Power Pins                                                    |

|    | 5.7 Reserved Pins                                                 |

|    | 5.8 Serial EEPROM and SMI Pins                                    |

|    | 5.9 Strapping Pins                                                |

| ,  | 5.10 Port Status Strapping Pins                                   |

| 6. | . Register Description                                            |

|    | 6.1 PHY0 to 4: PHY Register of Each Port22                        |

|    | 6.1.1 Register0: Control Register                                 |

|    | 6.1.2 Register1: Status Register                                  |

|    | 6.1.3 Register4: Auto-Negotiation Advertisement Register23        |

|    | 6.1.4 Register5: Auto-Negotiation Link Partner Ability Register24 |

|    | 6.1.5 Register6: Auto-Negotiation Expansion Register24            |

|    | 6.2 PHY0: EEPROM Register025                                      |

|    | 6.2.1 Register16: EEPROM Byte0 and 1 Register25                   |

|    | 6.2.2 Register17: EEPROM Byte2 and 3 Register25                   |

|    | 6.2.3 Register18~20: EEPROM EthernetID Register.25                |

|    | 6.2.4 Register21: EEPROM Byte10 and 11 Register .26               |

|    | 6.2.5 Register22: EEPROM Byte12 and 13 Register .26               |

|    | 6.3 PHY1: EEPROM Register127                                      |

|    | 6.3.1 Register16~23: EEPROM (Byte 14~29) Register27               |

|    | 6.3.2 Register24~31: EEPROM VLAN (Byte 30-44) Register 27         |

|    | 6.4 PHY2: Pin & EEPROM Register                                   |

|    | 6.4.1 Register16: Pin Register                                    |

|    | 6.4.2 Register17: Pin & EEPROM Register for VLAN29                |

|    | 6.5 PHY3: Port Control Register                                   |

|    | 6.5.1 Register16: Port Control Register                           |

|    | 6.5.2 Register17: EEPROM (Byte 46) Register31                     |

|    | 6.5.3 Register18~20: EEPROM (Byte 47~52) Register31               |

| 7. | . Functional Description32                                        |

|    | 7.1 Switch Core Functional Overview                               |

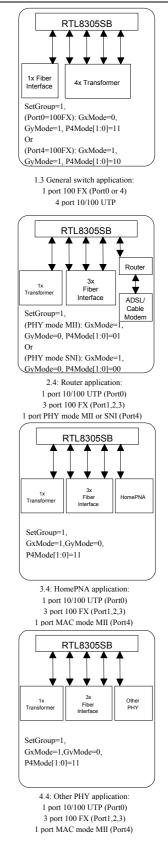

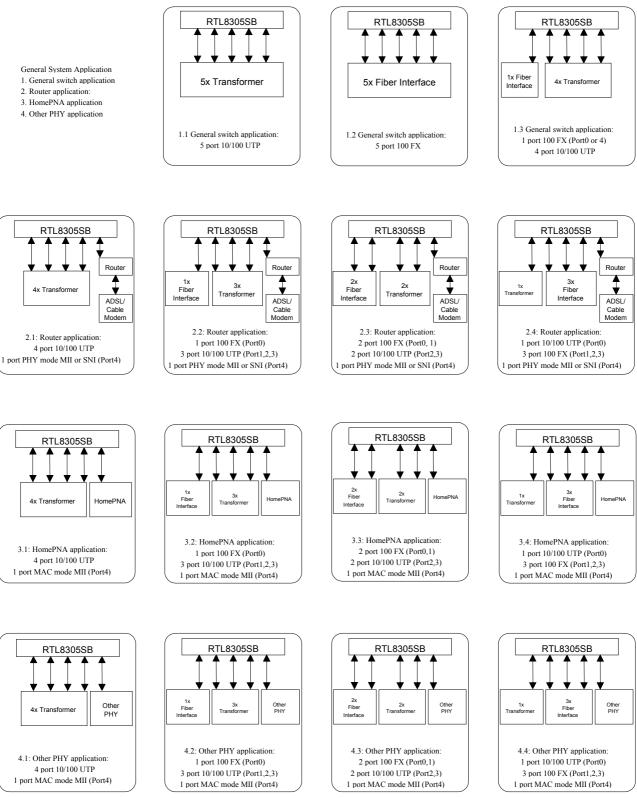

|    | 7.1.1 Application                                                 |

|    | 7.1.2 Port4                                                       |

|    | 7.1.3 Port Status Configuration                                   |

|    | 7.1.4 Enable Port                                                 |

|    | 7.1.5 Flow Control                                                |

|    | 7.1.6 Address Search, Learning and Aging                          |

|    | 7.1.7 Address Direct Mapping Mode                                 |

|    | 7.1.8 Half Duplex Operation                                       |

|    | 7.1.9 Inter-Frame Gap                                             |

|    | 7 1 10 Illegal Frame                                              |

| 7.2 Physical Layer Functional Overview                      | 39 |

|-------------------------------------------------------------|----|

| 7.2.1 Auto-Negotiation for UTP                              |    |

| 7.2.2 10Base-T Transmit Function                            |    |

| 7.2.3 10Base-T Receive Function                             |    |

| 7.2.4 Link Monitor                                          |    |

| 7.2.5 100Base-TX Transmit Function                          |    |

| 7.2.6 100Base-TX Receive Function                           |    |

| 7.2.7 100Base-FX                                            |    |

| 7.2.8 100Base-FX Transmit Function                          |    |

| 7.2.9 100Base-FX Receive Function                           |    |

| 7.2.10 100Base-FX Far-End-Fault-Indication (FEFI)           |    |

| 7.2.11 Reduced Fiber Interface                              |    |

| 7.2.12 Power Saving Mode                                    |    |

| 7.2.13 Reg0.11 Power Down Mode                              |    |

| 7.2.14 Crossover Detection and Auto Correction              |    |

| 7.2.15 Polarity Detection and Correction                    |    |

| 7.3 Advanced Functional Overview                            |    |

| 7.3.1 Reset                                                 |    |

| 7.3.2 Setup and Configuration                               |    |

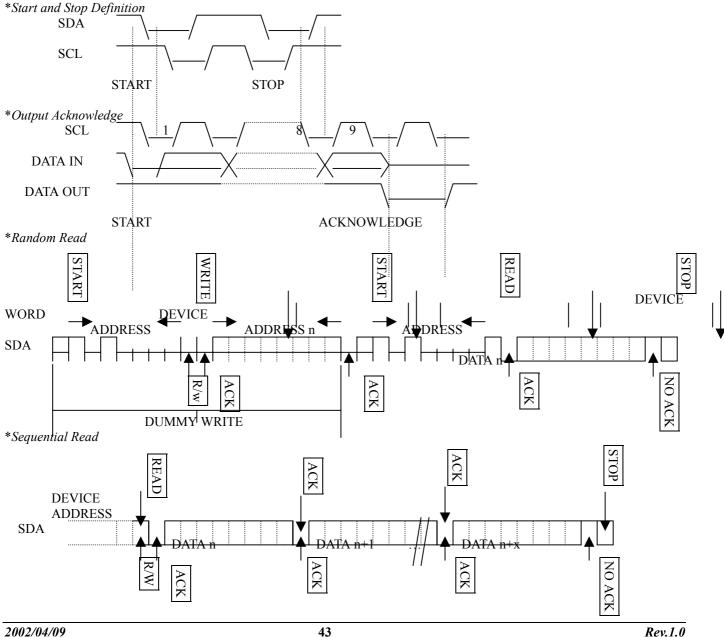

| 7.3.3 Example of Serial EEPROM: 24LC02                      | 42 |

| 7.3.4 24LC02 Device Operation                               | 43 |

| 7.3.5 SMI                                                   |    |

| 7.3.6 Head-Of-Line Blocking                                 |    |

|                                                             |    |

| 7.3.7 802.1Q Port Based VLAN                                |    |

| 7.3.8 QoS Function<br>7.3.9 Insert/Remove VLAN Priority Tag | 40 |

|                                                             |    |

| 7.3.10 Filtering/Forwarding Reserved Control Frame          |    |

| 7.3.11 Broadcast Storm Control                              |    |

| 7.3.12 Broadcast In/Out Drop                                |    |

| 7.3.13 Loop Detection                                       |    |

| 7.3.14 MAC Loopback return to External                      |    |

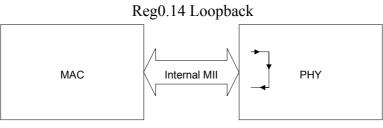

| 7.3.15 Reg0.14 PHY Loopback return to Internal              |    |

| 7.3.16 LED                                                  |    |

| 7.3.17 2.5V Power Generation                                |    |

| 7.3.18 Crystal/Oscillator                                   |    |

| 8. Serial EEPROM Description                                |    |

| 9. Electrical Characteristics                               |    |

| 9.1 Absolute Maximum Ratings:                               |    |

| 9.2 Operating Range:                                        |    |

| 9.3 DC Characteristics                                      |    |

| 9.4 AC Characteristics                                      |    |

| 9.5 Digital Timing Characteristics                          |    |

| 9.6 Thermal Data                                            |    |

| 10. Application Information                                 |    |

| 10.1 UTP (10Base-T/100Base-TX) Application                  |    |

| 10.2 100Base-FX Application:                                |    |

| 11. System Application Diagram                              |    |

| 12. Design and Layout Guide                                 |    |

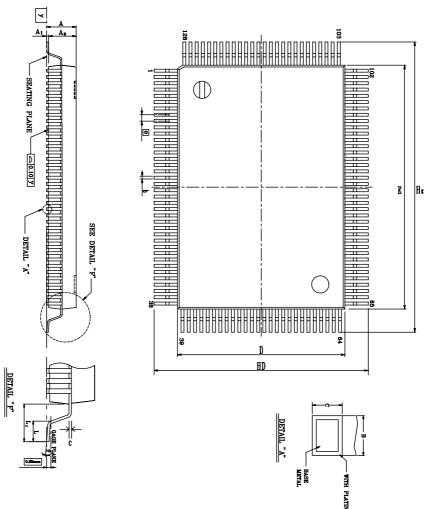

| 13. Mechanical Dimensions                                   | 65 |

A 12

## 1. Features

- 5-port integrated switch controller with memory and transceiver for 10Base-T and 100Base-TX with

- 5-port 10/100M UTP or

- ◆ 4-port 10/100M UTP + 1-port MII/SNI

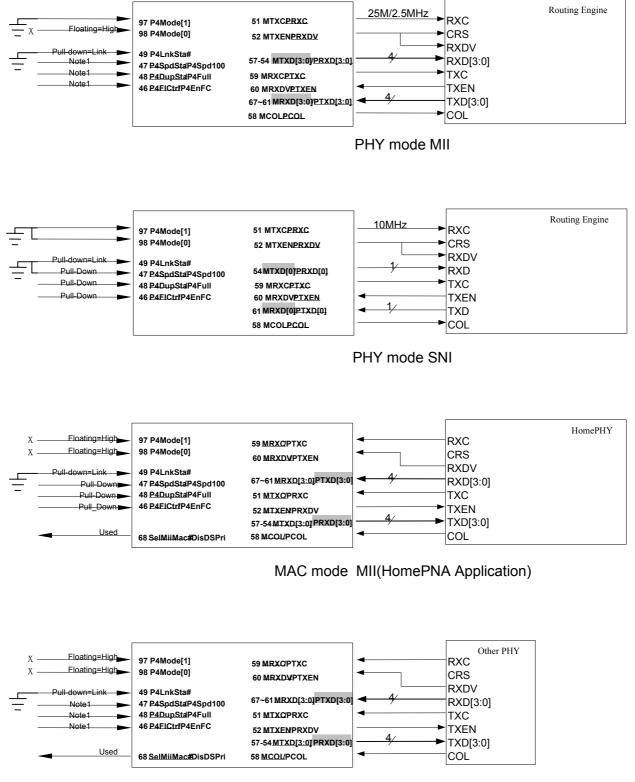

- Supports PHY mode MII /SNI for router applications and MAC mode MII for HomePNA or VDSL solutions

- All ports support 100Base-FX with optional flow control enable/disable and full/half duplex setting

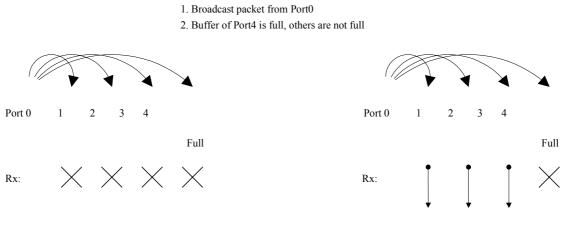

- Non-blocking wire-speed reception and transmission and non-head-of-line-blocking forwarding

- Fully compliant with IEEE 802.3/802.3u auto-negotiation function

- Built-in high efficiency SRAM for packet buffer and 1K entry look-up table, and 16 entry CAM

- Supports broadcast storm filtering function

- Supports IEEE802.3x full duplex flow control and back pressure half duplex flow control

- Supports SMI (Serial Management Interface: MDC/MDIO) for programming and diagnostics

- Supports loop detection function with one LED to indicate the existence of loop

- Supports loopback function for diagnosis

- Flexible 802.1Q Port based VLAN. Up to 5 VLAN

- Supports 802.1Q tag VLAN function

- Supports ARP VLAN for broadcast packets

- Supports Leaky VLAN for unicast packets

- Supports QoS function on each port:

- QoS based on: (1) Port-based (2) VLAN tag

(3) TCP/IP header's TOS/DS

- Supports two level priority queues

- Weighted round robin service

- Supports VLAN priority tag Insert/Remove function

- Optional 1536 or 1552 byte maximum packet length

- Supports reserved control frames (DID= 0180C2000003~0180C200000F) filtering function

- Flexible LED indicators for link, activity, speed, full/half duplex and collision

- LEDs blink upon reset for LED diagnostics

- Supports two Power Reduction methods:

- Power saving mode by cable detection

- Power down mode (by PHY register 0.11)

Robust baseline wander correction for improved 100BASE-TX performance

- Optional Crossover Detection and Auto Correction function

- Physical layer port Polarity Detection and Correction function

- Optional EEPROM interface for configuration

- 25MHz crystal or OSC input. Single 3.3V power system like by translating of an external transistor

- 0.25 μm, CMOS technology, 3.3V/2.5V with 3.3V input tolerant, 128 pin PQFP package

## 2. General Description

The RTL8305SB is a Fast Ethernet switch, which integrates memory, five MACs, and five physical layer transceivers for 10Base-T and 100Base-TX operation into a single chip. All ports support 100Base-FX, which share pins (TX+-/RX+-) with UTP ports and need no SD+/- pins, a development using Realtek proprietary technology. Due to the lack of auto-negotiation in 100Base-FX applications, the RTL8305SB can be forced into half or full duplex mode and can enable or disable flow control in fiber mode.

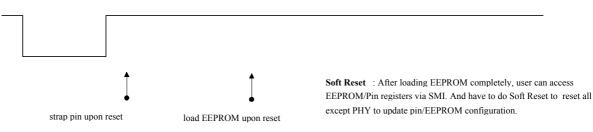

The five ports are separated into 3 groups (GroupX/GroupY/Port4) for flexible port configuration using strapping pins upon reset. The SetGroup pin is used to select port members in GroupX and GroupY. While the port members is determined, you can use mode selection pin (GxMode/Gymode/P4Mode[1:0]) to select operating interfaces such as 10/100Base-TX, 100Base-FX. Each group has 4 pins to select initial port status (ANEG/Force, 100/10, Full/Half, Enable/Disable Flow Control) upon reset. Upon reset, in addition to using strapping pins, the RTL8305SB also can be configured with an EEPROM or read/write operation by a CPU through the MDC/MDIO interface.

The fifth port (port 4) supports an external MAC interface, which can be set to PHY mode MII, PHY mode SNI, or MAC mode MII to work with a routing engine, HomePNA or VDSL transceiver. In order to accomplish diagnostics in complex network systems, the RTL8305SB also provides a loopback feature in each port for a variable CPU system.

The RTL8305SB contains a 1K entry address look-up table and supports a 16 entry CAM to avoid hash collisions and to maintain forwarding performance. The RTL8305SB supports IEEE 802.3x full duplex flow control and back- pressure half duplex flow control. The broadcast storm filtering function is provided to filter unusual broadcast storm issues and has an intelligent switch engine to prevent Head-Of -Line blocking problems.

The RTL8305SB supports 5 groups of VLANs which can be configured with port based VLAN and/or 802.1Q tag VLAN. ARP broadcast and Leaky VLAN are also supported for advanced applications.

The RTL8305SB supports several types of QoS functions with two level priority queues to improve multi-media or real-time networking applications. The QoS functions are based on: 1) Port based priority; 2) 802.1Q VLAN priority tag; 3) The TOS/DS (DiffServ) field of TCP/IP. In order to avoid the flow control function effecting the quality of high priority frames, the RTL8305SB supports an intelligent flow control for high priority frames by setting DisFCAutoOff to automatically turn off flow control for 1~2 seconds whenever the congestion port receives high priority frames. When the QoS function is enabled, a VLAN tag can be inserted or removed at the output port. The RTL8305SB will insert a VLAN priority-tag (VID=0x000) for untagged frames or remove the tag for all tagged frames.

Maximum packet length can be 1536 or 1552 bytes according to the initial configuration (strapping upon reset). The filtering function is supported for the 802.1D specified reserved group MAC addresses (01-80-C2-00-00-03 to 01-80-C2-00-00-0F).

The RTL8305B provides flexible LED functions for diagnostics, which include: 1) Four combinations of link, activity, speed, duplex and collision which are designed for convenient LED displays, such as bi-color LEDs; 2) Reset blinking; 3) Blinking time selection. The RTL8305SB also provides a loop detection function and alarm, for network existence notification, with an output pin which can be designed as a visual LED or a status input pin for a CPU.

The RTL8305SB implements a power saving mode on a per port basis. One port automatically enters power saving mode 10 seconds after the cable is disconnected from it. The RTL8305SB also implements a power down mode on a per port basis. Users can set MII Reg.0.11 to force the corresponding port to enter the power down mode, which disables all transmit/receive functions, except SMI (MDC/MDIO management interface).

Each physical layer channel of the RTL8305SB consists of a 4B5B encoder/decoder, a Manchester encoder/decoder, a scrambler/descrambler, a transmit output driver, output wave shaping filters, a digital adaptive equalizer, a PLL circuit and a DC restoration circuit for clock/data recovery. Friendly crossover auto detection and correction functions are also supported for easy cable connection.

The integrated chip benefits from low power consumption, advanced functions with flexible configurations for 5-port SOHO switch, Home Gateway, xDSL/Cable router, and other IA applications.

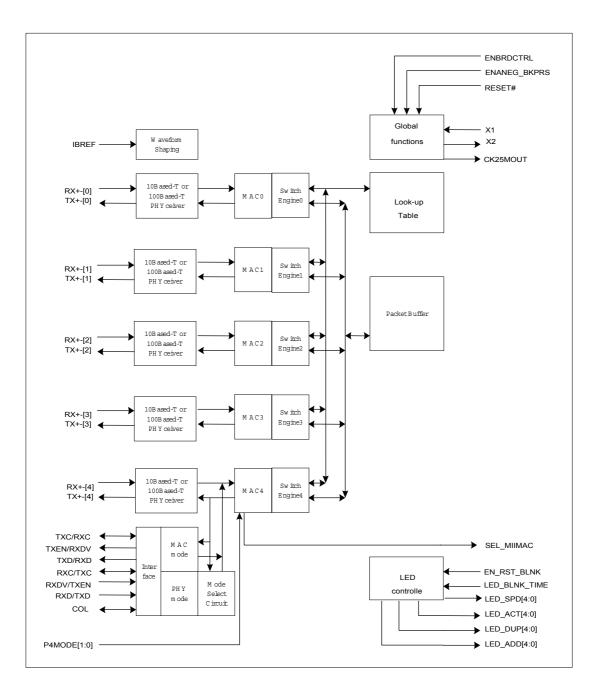

## 3. Block Diagram

**RTL8305SB**

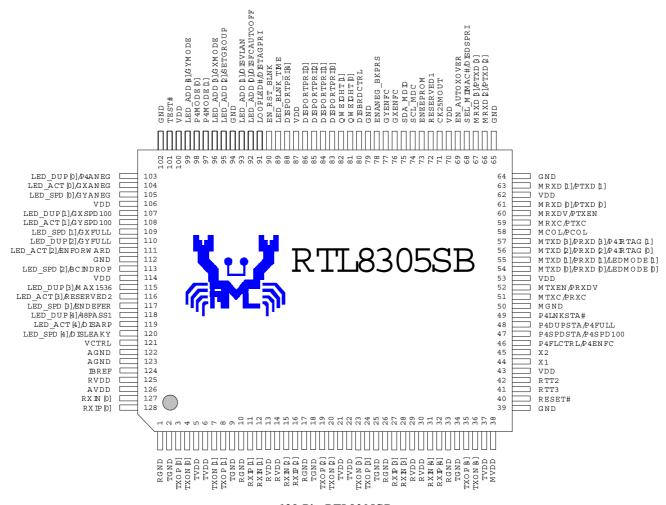

## 4. Pin Assignments

128 Pin RTL8305SB

#### RTL8305SB

#### 'I' stands for inputs; 'O' stands for outputs; 'A' stands for analog; 'D' stands for digital

| NAME                       | PIN No. | TYPE | NAME                    | PIN No. | TYPE       |

|----------------------------|---------|------|-------------------------|---------|------------|

| RGND                       | 1       | AGND | GND                     | 65      | DGNI       |

| TGND                       | 2       | AGND | MRXD[2]/PTXD[2]         | 66      | Ι          |

| TXOP[0]                    | 3       | AO   | MRXD[3]/PTXD[3]         | 67      | I          |

| TXON[0]                    | 4       | AO   | SEL_MIIMAC#/DISDSPRI    | 68      | I/O        |

|                            |         |      |                         |         |            |

| TVDD                       | 5       | AVDD | EN_AUTOXOVER            | 69      | I          |

| TVDD                       | 6       | AVDD | VDD                     | 70      | DVDI       |

| TXON[1]                    | 7       | AO   | CK25MOUT                | 71      | 0          |

| TXOP[1]                    | 8       | AO   | RESERVED1               | 72      | I/O        |

| TGND                       | 9       | AGND | ENEEPROM                | 73      | Ι          |

| RGND                       | 10      | AGND | SCL MDC                 | 74      | I/O        |

| RXIP[1]                    | 11      | AI   | SDA MDIO                | 75      | I/O<br>I/O |

|                            |         |      | _                       | 76      |            |

| RXIN[1]                    | 12      | AI   | GXENFC                  |         | I          |

| RVDD                       | 13      | AVDD | GYENFC                  | 77      | Ι          |

| RVDD                       | 14      | AVDD | ENANEG_BKPRS            | 78      | Ι          |

| RXIN[2]                    | 15      | AI   | GND                     | 79      | DGNI       |

| RXIP[2]                    | 16      | AI   | DISBRDCTRL              | 80      | Ι          |

| RGND                       | 17      | AGND | QWEIGHT[0]              | 81      | Ι          |

| TGND                       | 18      | AGND | QWEIGHT[1]              | 82      | I          |

|                            |         |      |                         |         | I          |

| TXOP[2]                    | 19      | AO   | DISPORTPRI[0]           | 83      | -          |

| TXON[2]                    | 20      | AO   | DISPORTPRI[1]           | 84      | I          |

| TVDD                       | 21      | AVDD | DISPORTPRI[2]           | 85      | I          |

| TVDD                       | 22      | AVDD | DISPORTPRI[3]           | 86      | Ι          |

| TXON[3]                    | 23      | AO   | VDD                     | 87      | DVDI       |

| TXOP[3]                    | 24      | AO   | DISPORTPRI[4]           | 88      | Ι          |

| TGND                       | 25      | AGND | LED BLNK TIME           | 89      | Î          |

| RGND                       | 26      | AGND |                         | 90      | I          |

|                            |         |      | EN_RST_BLNK             |         |            |

| RXIP[3]                    | 27      | AI   | LOOPLED#/DISTAGPRI      | 91      | I/O        |

| RXIN[3]                    | 28      | AI   | LED_ADD[0]/DISFCAUTOOFF | 92      | I/O        |

| RVDD                       | 29      | AVDD | LED_ADD[1]/DISVLAN      | 93      | I/O        |

| RVDD                       | 30      | AVDD | GND                     | 94      | DGNI       |

| RXIN[4]                    | 31      | AI   | LED_ADD[2]/SETGROUP     | 95      | I/O        |

| RXIP[4]                    | 32      | AI   | LED ADD[3]/GXMODE       | 96      | I/O        |

| RGND                       | 33      | AGND | P4MODE[1]               | 97      | I          |

|                            |         |      |                         |         |            |

| TGND                       | 34      | AGND | P4MODE[0]               | 98      | Ι          |

| TXOP[4]                    | 35      | AO   | LED_ADD[4]/GYMODE       | 99      | I/O        |

| TXON[4]                    | 36      | AO   | VDD                     | 100     | DVDI       |

| TVDD                       | 37      | AVDD | TEST#                   | 101     | I/O        |

| MVDD                       | 38      | DVDD | GND                     | 102     | DGNI       |

| GND                        | 39      | DGND | LED DUP[0]/P4ANEG       | 102     | I/O        |

| RESET#                     | 40      |      | LED_DOT[0]/GXANEG       | 103     | I/O<br>I/O |

|                            |         | I    |                         |         |            |

| RTT3                       | 41      | 0    | LED_SPD[0]/GYANEG       | 105     | I/O        |

| RTT2                       | 42      | 0    | VDD                     | 106     | DVDI       |

| VDD                        | 43      | DVDD | LED_DUP[1]/GXSPD100     | 107     | I/O        |

| X1                         | 44      | Ι    | LED ACT 1/GYSPD100      | 108     | I/O        |

| X2                         | 45      | 0    | LED SPD[1]/GXFULL       | 109     | I/O        |

| P4FLCTRL/P4ENFC            | 46      | I    | LED_DUP[2]/GYFULL       | 110     | I/O        |

| P4SPDSTA/P4SPD100          | 40      | I    | LED ACT[2]/ENFORWARD    | 110     | I/O<br>I/O |

|                            |         |      |                         |         |            |

| P4DUPSTA/P4FULL            | 48      | I    | GND                     | 112     | GND        |

| P4LNKSTA#                  | 49      | I    | LED_SPD[2]/BCINDROP     | 113     | I/O        |

| MGND                       | 50      | DGND | VDD                     | 114     | DVDI       |

| MTXC/PRXC                  | 51      | I/O  | LED_DUP[3]/MAX1536      | 115     | I/O        |

| MTXEN/PRXDV                | 52      | 0    | LED_ACT[3]/RESERVED2    | 116     | I/O        |

| VDD                        | 53      | DVDD | LED SPD[3],/ENDEFER     | 117     | I/O        |

| MTXD[0]/PRXD[0]/LEDMODE[0] | 54      | I/O  | LED_DUP[4]/48PASS1      | 118     | I/O<br>I/O |

|                            |         |      |                         |         |            |

| MTXD[1]/PRXD[1]/LEDMODE[1] | 55      | I/O  | LED_ACT[4]/DISARP       | 119     | I/O        |

| MTXD[2]/PRXD[2]/P4IRTAG[0] | 56      | I/O  | LED_SPD[4]/DISLEAKY     | 120     | I/O        |

| MTXD[3]/PRXD[3]/P4IRTAG[1] | 57      | I/O  | VCTRL                   | 121     | 0          |

| MCOL/PCOL                  | 58      | I/O  | AGND                    | 122     | AGNI       |

| MRXC/PTXC                  | 59      | I/O  | AGND                    | 123     | AGNI       |

| MRXDV/PTXEN                | 60      | I    | IBREF                   | 123     | A          |

|                            |         |      |                         |         |            |

| MRXD[0]/PTXD[0]            | 61      | I    | RVDD                    | 125     | AVDI       |

| VDD                        | 62      | DVDD | AVDD                    | 126     | AVDI       |

| MRXD[1]/PTXD[1]            | 63      | I    | RXIN[0]                 | 127     | AI         |

| GND                        | 64      | DGND | RXIP[0]                 | 128     | AI         |

## 5. Pin Descriptions

#### ' I ' stands for inputs; 'O' stands for outputs; 'A' stands for analog; 'D' stands for digital

**Upon reset:** defined as a short time after at the end of a hardware reset. **After reset:** defined as the time after the specified "Upon Reset" time.

### **5.1 Media Connection Pins**

| Pin Name               | Pin No.                                    | Туре | Description                                                                                                                                                                                                                                    | Default |

|------------------------|--------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| RXIP[4:0]<br>RXIN[4:0] | 11,12,15,<br>16,27,28,<br>31,32<br>127,128 | AI   | <b>Differential Receive Data Input:</b> Shared by 100Base-TX, 10Base-T and 100Base-FX.<br>UTP or FX depends on pin GxMode/GyMode/P4Mode[1:0].<br>Note: The 8305SB uses these pins for UTP and Fiber. The 8305S uses these pins for UTP only.   |         |

| TXOP[4:0]<br>TXON[4:0] | 3,4<br>7,8<br>19,20<br>23,24<br>35,36      | AO   | <b>Differential Transmit Data Output:</b> Shared by 100Base-TX, 10Base-T and 100Base-FX.<br>UTP or FX depends on pin GxMode/GyMode/P4Mode[1:0].<br>Note: The 8305SB uses these pins for UTP and Fiber. The 8305S uses these pins for UTP only. |         |

#### **5.2 Configuration Pins**

| Pin Name      | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                     | Default |

|---------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| ENANEG_BKPRS  | 78      | Ι    | <b>Enable Auto-Negotiation Back Pressure:</b> This pin sets back pressure for auto-negotiation mode for all UTP ports.                                                                                                                                                                                                                                                          | 1       |

|               |         |      | 1: Enable<br>0: Disable                                                                                                                                                                                                                                                                                                                                                         |         |

|               |         |      | 8305SB=ENANEG_BKPRS, 8305S=ENBKPRS. This pin has the same function for both the RTL8305SB and RTL8305S. The RTL8305SB also supports Force mode (through P4ENFC/GxENFC/GyENFC), but this pin is used only for Auto-Negotiation mode. The pin name is changed to differentiate between "Enable back pressure for Auto-Negotiation mode" and "Enable backpressure for Force mode." |         |

| DISBRDCTRL    | 80      | Ι    | <b>Disable Broadcast Storm Control:</b><br>1= Disable                                                                                                                                                                                                                                                                                                                           | 1       |

|               |         |      | 0 = Enable                                                                                                                                                                                                                                                                                                                                                                      |         |

|               |         |      | 8305SB=DISBRDCTRL, 8305S=ENBRDCTRL. The RTL8305SB will                                                                                                                                                                                                                                                                                                                          |         |

|               |         |      | disable this function when pin DISBRDCTRL is left floating. However, the                                                                                                                                                                                                                                                                                                        |         |

|               | 00      | T    | RTL8305S will enable this function when pin ENBRDCTRL is left floating.                                                                                                                                                                                                                                                                                                         |         |

| LED_BLNK_TIME | 89      | Ι    | <b>LED Blink Time:</b> This pin selects the blinking speed of the activity and collision LEDs.                                                                                                                                                                                                                                                                                  | 1       |

|               |         |      | 1: On 43ms, then Off 43ms<br>0: On 120ms, then Off 120ms                                                                                                                                                                                                                                                                                                                        |         |

| EN_RST_BLNK   | 90      | Ι    | <b>Enable Reset Blink:</b> This pin enables the blinking of the LEDs upon reset for diagnosis purposes.                                                                                                                                                                                                                                                                         | 1       |

|               |         |      | 1: Enable reset LED blinking                                                                                                                                                                                                                                                                                                                                                    |         |

|               |         |      | 0: Disable reset LED blinking                                                                                                                                                                                                                                                                                                                                                   |         |

|               |         |      | 8305SB=EN_RST_BLNK, 8305S=DIS_RST_BLNK#. This pin has the same function for both the RTL8305SB and RTL8305S. The pin name has been changed for convenience.                                                                                                                                                                                                                     |         |

### **5.3 Port4 External MAC Interface Pins**

The external device should be 2.5V compatible, because the digital output of the RTL8305SB is 2.5V. The input or input/output pins listed below do not have internal pull-high resistors for connecting to external devices. External pull-high resistors are recommended for those floating input pins without internal pull-high resistor if reduced power consumption is desired.

In order to differentiate between MAC and PHY mode, the name of the pins change for PHY mode. For example: RTL8305SB=MRXD[0]/PTXD[0], RTL8305S=MRXD[0]/MTXD[0].

Tip: Connect the input of Port4 to the output of the external device.

| Pin Name    | Pin No.   | Туре | Description                                                                                                                                                                                                | Default |

|-------------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| MRXD[3:0]/  | 67,66,63, | Ι    | For MAC mode MII, these pins are MRXD[3:0], MII receive data nibble.                                                                                                                                       |         |

| PTXD[3:0]   | 61        |      | For PHY mode MII, these pins are PTXD[3:0], MII transmit data nibble.                                                                                                                                      |         |

|             |           |      | For PHY mode SNI, PTXD[0] is serial transmit data.                                                                                                                                                         |         |

|             |           |      | Because this pin can be connected to a 2.5V or 3.3V devices, these pins have no internal pull-high resistor.                                                                                               |         |

|             |           |      | RTL8305SB = MRXD[3:0] / PTXD[3:0], RTL8305S = MRXD[3:0] / MTXD[3:0]. In order to differentiate between MAC and PHY modes, the RTL8305SB changes the pin name for PHY mode.                                 |         |

| MRXDV/PTXEN | 60        | Ι    | For MAC mode MII, this pin represents MRXDV, MII receive data valid.<br>For PHY mode MII, this pin represents PTXEN, MII transmit enable.<br>For PHY mode SNI, this pin represents PTXEN, transmit enable. |         |

|             |           |      | Because this pin can be connected to a 2.5V or 3.3V device, this pin has no internal pull-high resistor.                                                                                                   |         |

|             |           |      | RTL8305SB = MRXDV/PTXEN, RTL8305S = MRXDV/MTXEN. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode.                                                      |         |

| MRXC/PTXC   | 59        | I/O  | For MAC mode MII, it is receive clock, MRXC (acts as input).<br>For PHY mode MII/PHY mode SNI, it is transmit clock, PTXC (acts as output).                                                                |         |

|             |           |      | Because this pin can be connected to a 2.5V or 3.3V device, this pin has no internal pull-high resistor.                                                                                                   |         |

|             |           |      | RTL8305SB = MRXC/PTXC, RTL8305S = MRXC/MTXC. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode.                                                          |         |

| MCOL/PCOL   | 58        | I/O  | For MAC mode MII, this pin represents MCOL collision (acts as input)<br>For PHY mode MII/PHY mode SNI, this pin represents PCOL collision                                                                  |         |

|             |           |      | (acts as output)                                                                                                                                                                                           |         |

|             |           |      | Because this pin can be connected to a 2.5V or 3.3V device, this pin has no internal pull-high resistor.                                                                                                   |         |

|             |           |      | RTL8305SB = MCOL/PCOL, RTL8305S = MCOL. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode.                                                               |         |

| MTXD[3]/<br>PRXD[3]/<br>P4IRTag[1] | 57 | I/O | Output after reset:<br>For MAC mode MII (P4Mode[1:0]=11), these pins are MTXD[3:0],<br>MII transmit data of MAC.                                                                                                                                                                                                                                                                          | 11 |

|------------------------------------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| MTXD[2]/<br>PRXD[2]/               | 56 |     | For PHY mode MII (P4Mode[1:0]=01), these pins are PRXD[3:0], <b>MII</b> receive data of PHY.                                                                                                                                                                                                                                                                                              |    |

| P4IRTag[0]                         |    |     | For PHY mode SNI (P4Mode[1:0]=00), PRXD[0] is SNI serial receive data.                                                                                                                                                                                                                                                                                                                    |    |

|                                    |    |     | Input upon reset: P4IRTag[1:0]<br>Insert/Remove Priority Tag of Port4.<br>11: Do not insert/remove Tag from Output High and Low Queue of Port4.<br>10: Insert Tag from Output High and Low Queue of Port4.<br>01: Insert Tag from Output High Queue only of Port4.<br>00: Remove Tag from Output High and Low Queue of Port4.<br>RTL8305SB = MTXD[3:2]/PRXD[3:2]/P4IRTag[1:0], RTL8305S = |    |

|                                    |    |     | MTXD[3:2]/MRXD[3:2]. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode. For RTL8305SB: These pins are input pins used for strapping upon reset and used as output pins (output data) after reset. For RTL8305S: These pins are used as output pins (output data) after reset.                                                           |    |

|                                    |    | 1/0 | These pins are used for Port4 only. Use serial EEPROM for other ports.                                                                                                                                                                                                                                                                                                                    |    |

| MTXD[1]/PRXD[1]/<br>LEDMode[1]     | 55 | I/O | Output after reset:<br>For MAC mode MII (P4Mode[1:0]=11), these pins are MTXD[3:0],<br>MII transmit data of MAC.                                                                                                                                                                                                                                                                          | 11 |

| MTXD[0]/PRXD[0]/<br>LEDMode[0]     | 54 |     | For PHY mode MII (P4Mode[1:0]=01), these pins are PRXD[3:0], <b>MII</b> receive data of PHY.                                                                                                                                                                                                                                                                                              |    |

|                                    |    |     | For PHY mode SNI (P4Mode[1:0]=00), PRXD[0] is <b>SNI serial receive</b> data.                                                                                                                                                                                                                                                                                                             |    |

|                                    |    |     | <b>Input upon reset: LEDMode[1:0]</b><br>Each port has four LED indicator pins. Each pin may has different indicator meaning set by pins LEDMode[1:0].                                                                                                                                                                                                                                    |    |

|                                    |    |     | LEDMode[1:0]=11 : Speed + Link/Act + Duplex/Col + Link/Act/Spd.<br>LEDMode[1:0]=10 : Speed + Act + Duplex/Col + Bi-color Link/Active.<br>LEDMode[1:0]=01 : Speed + RxAct + TxAct + Link.<br>LEDMode[1:0]=00 : Speed + Link/Act + Col + Duplex.                                                                                                                                            |    |

|                                    |    |     | All LED statuses are represented as active-low or high depending on input strapping, except Bi-color Link/Act in Bi-color LED mode, whose polarity depends on Spd status.                                                                                                                                                                                                                 |    |

|                                    |    |     | Link/Act/Spd: Link, Activity, and Speed Indicator. On for link established. Blinking every 43ms when the corresponding port is transmitting or receiving in 100Mb/s. Blinking every 120ms when the port is transmitting or receiving in 10Mb/s.                                                                                                                                           |    |

|                                    |    |     | RTL8305SB = MTXD[1:0]/PRXD[1:0]/LEDMode[1:0], RTL8305S = MTXD[1:0]/MRXD[1:0]. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode. For RTL8305SB: These pins are input pins used for strapping upon reset and used as output pins (output data) after reset. For RTL8305S: These pins are used as output pins (output data) after reset.  |    |

| MTXEN/PRXDV | 52    | 0   | For MAC mode MII, this pin represents MTXEN, MII transmit enable.<br>For PHY mode MII, this pin represents PRXDV, MII received data valid.<br>For PHY mode SNI, this pin represents PRXDV, received data valid.                                                    | 1  |

|-------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             |       |     | RTL8305SB = MTXEN/PRXDV, RTL8305S = MTXEN/MRXDV. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode.                                                                                                              |    |

| MTXC/PRXC   | 51    | I/O | For MAC mode MII, it is transmit clock, MTXC (acts as input).<br>For PHY mode MII/PHY mode SNI, it is receive clock, PRXC (acts as output).                                                                                                                        |    |

|             |       |     | Because this pin can be connected to a 2.5V or 3.3V device, this pin has no internal pull-high resistor.                                                                                                                                                           |    |

|             |       |     | RTL8305SB = MTXC/PRXC, RTL8305S = MTXC/MRXC. In order to differentiate between MAC and PHY mode, the RTL8305SB changes the pin name for PHY mode.                                                                                                                  |    |

| P4MODE[1:0] | 97,98 | Ι   | Select Port 4 operating mode:11: UTP / MAC mode MII10: 100Base-FX mode01: PHY mode MII00: PHY mode SNIThe RTL8305SB has 4 options and the RTL8305S has 3 options.                                                                                                  | 11 |

| P4LNKSTA#   | 49    | Ι   | <b>Port4 Link Status for MAC:</b> When the PHY part of Port4 is not used, this pin determines the link status of the Port4 MAC in real-time. That is link status of real-time for MII MAC/MII PHY/SNI PHY only. This pin is low active.                            | 1  |

|             |       |     | 1: No Link.<br>0: Link                                                                                                                                                                                                                                             |    |

|             |       |     | When P4MODE[1:0]=11 (UTP/MAC mode MII), this pin determines<br>the link status of MAC mode MII only in real time. The link status of<br>UTP mode is provided by the internal PHY in real time. If both UTP and<br>MII port are linked OK, UTP has higher priority. |    |

|             |       |     | When P4MODE[1:0]=10 (100Base-FX mode), this pin does nothing.<br>The internal PHY will provide the link status to the MAC in real time.                                                                                                                            |    |

|             |       |     | When P4MODE[1:0]=01 (PHY mode MII), this pin determines the link status of Port4 in real time.                                                                                                                                                                     |    |

|             |       |     | When P4MODE[1:0]=00 (PHY mode SNI), this pin determines the link status of Port4 in real time.                                                                                                                                                                     |    |

|             |       |     | This pin should be left floating in UTP or FX mode, and pulled down in the other three modes.                                                                                                                                                                      |    |

|             |       |     | In MAC mode MII/ PHY mode MII/ PHY mode SNI, configuration of this pin will not set the link status of the internal register. The link status depends on the external PHY or MAC.                                                                                  |    |

| P4DUPSTA/<br>P4FULL | 48 | Ι | <b>Port4 Duplex Status:</b> Port4 initial configuration pin for Duplex upon reset for PHY of UTP or FX mode and Duplex Status for MAC of other mode in real time after reset.                                                                                                                              | 1 |

|---------------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                     |    |   | 1: Full duplex<br>0: Half duplex                                                                                                                                                                                                                                                                           |   |

|                     |    |   | When P4MODE[1:0]=11 (UTP/MAC mode MII), this pin provides the initial duplex configuration for the PHY part upon reset (UTP) then determines the duplex status of MAC mode MII in real time after reset. The duplex status of the PHY part (UTP) is provided by the internal PHY in real time after reset. |   |

|                     |    |   | When P4MODE[1:0]=10 (100Base-FX mode), this pin provides the initial register configuration of duplex for PHY part upon reset (FX). The duplex status of the PHY part (FX) is provided by the internal PHY in real time after reset.                                                                       |   |

|                     |    |   | When P4MODE[1:0]=01 (PHY mode MII), this pin determines the duplex status of Port4 in real time after reset.                                                                                                                                                                                               |   |

|                     |    |   | When P4MODE[1:0]=00 (PHY mode SNI), this pin determines the duplex status of Port4 in real time after reset.                                                                                                                                                                                               |   |

|                     |    |   | 8305SB = P4DUPSTA/P4FULL, 8305S = P4DUPSTA#.                                                                                                                                                                                                                                                               |   |

|                     |    |   | In order to provide Full duplex as the default value for the PHY, this pin is changed as high active.                                                                                                                                                                                                      |   |

|                     |    |   | In 100Base-Fx/ MAC mode MII/ PHY mode MII/ PHY mode SNI, the configuration of this pin after reset will not set the link status of the internal register. The link status depends on the external PHY or MAC.                                                                                              |   |

| P4SPDSTA/<br>P4SPD100 | 47 | Ι | <b>Port4 Speed Status:</b> Port4 initial configuration pin for Speed upon reset for PHY of UTP mode only and Speed Status for MAC of other mode in real time after reset.                                                                                                                                                   | 1 |

|-----------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                       |    |   | 1: 100Mbps<br>0: 10Mbps                                                                                                                                                                                                                                                                                                     |   |

|                       |    |   | When P4MODE[1:0]=11 (UTP/MAC mode MII), this pin provides the initial configuration of speed for the PHY part upon reset (UTP) then determines speed status of MAC mode MII in real time after reset. The speed status of the PHY part (UTP) is provided by the internal PHY in real time after reset.                      |   |

|                       |    |   | When P4MODE[1:0]=10 (100Base-FX mode), speed is dedicated to 100M. This pin does nothing and should be left floating.                                                                                                                                                                                                       |   |

|                       |    |   | When P4MODE[1:0]=01 (PHY mode MII), this pin determines the duplex status of Port4 in real time after reset.                                                                                                                                                                                                                |   |

|                       |    |   | When P4MODE[1:0]=00 (PHY mode SNI), speed is dedicated to 10MHz clock rate. This pin should be pulled down.                                                                                                                                                                                                                 |   |

|                       |    |   | For the application listed below, this pin should be left floating:                                                                                                                                                                                                                                                         |   |

|                       |    |   | For P4MODE[1:0]=10 (100Base-FX mode).                                                                                                                                                                                                                                                                                       |   |

|                       |    |   | For the application listed below, this pin should be pulled down:                                                                                                                                                                                                                                                           |   |

|                       |    |   | For PHY mode SNI, speed is dedicated to 10MHz clock rate.                                                                                                                                                                                                                                                                   |   |

|                       |    |   | 8305SB = P4SPDSTA/P4SPD100, 8305S = P4SPDSTA#.                                                                                                                                                                                                                                                                              |   |

|                       |    |   | In order to provide 100M for the default value for PHY, this pin is changed as high active.                                                                                                                                                                                                                                 |   |

| P4FLCTRL/<br>P4EnFC   | 46 | Ι | <b>Port4 Flow Control:</b> Port4 initial configuration pin for Flow Control upon reset for PHY of UTP and FX mode and Flow Control Status for MAC of other mode in real time after reset.                                                                                                                                   | 1 |

|                       |    |   | 1=Enable Flow Control ability.<br>0=Disable Flow Control ability.                                                                                                                                                                                                                                                           |   |

|                       |    |   | When P4MODE[1:0]=11 (UTP/MAC mode MII), this pin provides the initial configuration of flow control for the PHY part upon reset (UTP) then determines the flow control status of MAC mode MII in real time after reset. The flow control status of PHY part (UTP) is provided by the internal PHY in real time after reset. |   |

|                       |    |   | When P4MODE[1:0]=10 (100Base-FX mode), this pin provides the initial configuration of flow control for the PHY part upon reset (FX).                                                                                                                                                                                        |   |

|                       |    |   | When P4MODE[1:0]=01 (PHY mode MII), this pin determines the duplex status of Port4 in real time after reset.                                                                                                                                                                                                                |   |

|                       |    |   | When P4MODE[1:0]=00 (PHY mode SNI), flow control should be disabled. This pin should be pulled down.                                                                                                                                                                                                                        |   |

|                       |    |   | 8305SB = P4FLCTRL/P4EnFC, 8305S = P4FLCTRL#.                                                                                                                                                                                                                                                                                |   |

|                       |    |   | In order to enable flow control ability for the PHY, this pin is changed as high active.                                                                                                                                                                                                                                    |   |

| SEL_MIIMAC#/<br>DisDSPri | 68 | I/O | <b>Output after reset = SEL_MIIMAC# used for LED:</b><br>When P4MODE[1:0]=11, this pin indicates whether the UTP path or the MII MAC path is selected. Otherwise, this pin is of no use.                                                                                                                                                                                                                                                             | 1 |

|--------------------------|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                          |    |     | The LED statuses are represented as active-low or high depending on<br>input strapping.<br>=> If Input=1: Output 0= MII MAC port is selected. 1= UTP is selected.<br>=> If Input=0: Output 1= MII MAC port is selected. 0= UTP is selected.<br>While P4MODE[1:0]=11, RTL8305S supports UTP/MII MAC<br>auto-detection function via the link status of Port4 UTP and the status of<br>pin P4LNKSTA# and MAC mode MII. UTP has higher priority over the |   |

|                          |    |     | MAC mode MII.<br><b>Input upon reset = DisDSPri. Disable Differentiated Service Priority.</b><br>1: Disable DS priority; 0: Enable DS priority<br>8305SB = SEL_MIIMAC#/DisDSPri, 8305S = SEL_MIIMAC#.                                                                                                                                                                                                                                                |   |

### **5.4 Miscellaneous Pins**

| Pin Name | Pin No.                                                                                                                                                                                   | Туре | Description                                                                                                                                                                                                   | Default |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| X1       | 44                                                                                                                                                                                        | Ι    | 25MHz crystal or oscillator clock input. The clock tolerance is +-50ppm.                                                                                                                                      |         |

| X2       | 45                                                                                                                                                                                        | 0    | To crystal input, when using an oscillator, this pin should be floating.                                                                                                                                      |         |

| CK25MOUT | X25MOUT71O25MHz clock output. The source of this output is clock from X1 and X2.<br>This pin is used to support an extra 25M clock for the external device<br>(for example: HomePNA PHY). |      |                                                                                                                                                                                                               |         |

|          |                                                                                                                                                                                           |      | The output voltage of the RTL8305SB is 2.5V. The output voltage of the RTL8305S is 3.3V.                                                                                                                      |         |

| RESET#   | 40                                                                                                                                                                                        | Ι    | Active low reset signal: To complete reset function, this pin must be asserted for at least 10ms. After reset, about 30ms is needed for the RTL8305SB to complete internal test functions and initialization. |         |

|          |                                                                                                                                                                                           |      | This pin is a Schmitt input.                                                                                                                                                                                  |         |

|          |                                                                                                                                                                                           |      | Because this pin can be connected to a 2.5V or 3.3V device, this pin has no internal pull-high resistor.                                                                                                      |         |

| IBREF    | 124                                                                                                                                                                                       | А    | <b>Control transmit output waveform Vpp:</b> This pin should be grounded through a $1.96K\Omega$ resistor.                                                                                                    |         |

| VCtrl    | 121                                                                                                                                                                                       | 0    | <b>Voltage control to external regulator:</b> This signal controls a power PNP transistor to generate the 2.5V power supply.                                                                                  |         |

| DTT2     | 4.1                                                                                                                                                                                       | 0    | 8305SB = VCtrl, 8305S = TEST#.                                                                                                                                                                                |         |

| RTT3     | 41                                                                                                                                                                                        | 0    | <b>Cap+ for future use:</b> Reserve capacitors in layout for future use, but do not use those capacitors in the BOM.                                                                                          |         |

|          |                                                                                                                                                                                           |      | 8305SB = RTT3, 8305S = TESTCLK.                                                                                                                                                                               |         |

| RTT2     | 42                                                                                                                                                                                        | 0    | <b>Cap- for future use:</b> Reserve capacitors in layout for future use, but do not use those capacitors in the BOM.                                                                                          |         |

|          |                                                                                                                                                                                           |      | 8305SB = RTT2, 8305S = TESTDATA.                                                                                                                                                                              |         |

| TEST#    | 101                                                                                                                                                                                       | I/O  | Reserved pin for internal use. Should be left floating.                                                                                                                                                       | 1       |

### 5.5 Per Port LED Pins

Each port has four LED indicator pins. Each pin may have different indicator meanings as set by pins LEDMode[1:0].

All LED statuses are represented as active-low or high depending on input strapping, except Bi-color Link/Act in Bi-color LED mode, whose polarity depends on Spd status.

Those pins which are dual function pins are output for LED or input for strapping. Below are LED descriptions only.

| Pin Name      | Pin No. | Туре | Description                                                            | Default |

|---------------|---------|------|------------------------------------------------------------------------|---------|

| LED_SPD[4:0]/ | 120,    | I/O  | Output after reset = used for 1 <sup>st</sup> LED:                     | 11111   |

|               | 117,    |      | LEDMode[1:0]=11 -> Speed (0n=100, Off=10)                              |         |

|               | 113,    |      | LEDMode[1:0]=10 -> Speed (0n=100, Off=10)                              |         |

|               | 109,    |      | LEDMode[1:0]=01 -> Speed (0n=100, Off=10)                              |         |

|               | 105     |      | LEDMode[1:0]=00 -> Speed (0n=100, Off=10)                              |         |

|               |         |      | Input upon reset = Refer below for each pin.                           |         |

| LED_ACT[4:0]/ | 119,    | I/O  | Output after reset = used for 2 <sup>nd</sup> LED:                     | 11111   |

|               | 116,    |      | LEDMode[1:0]=11 -> Link/Act: (On=Link, Off=no Link, Flash=Tx or        |         |

|               | 111,    |      | Rx activity)                                                           |         |

|               | 108,    |      | LEDMode[1:0]=10 -> Act: (Off=no activity, ON=Tx or Rx activity)        |         |

|               | 104     |      | LEDMode[1:0]=01 -> RxAct: (Off=no activity, ON=Rx activity)            |         |

|               |         |      | LEDMode[1:0]=00 -> Link/Act: (On=Link, Off=no Link, Flash=Tx or        |         |

|               |         |      | Rx activity)                                                           |         |

|               |         |      | Input upon reset = Refer below for each pin.                           |         |

| LED_DUP[4:0]/ | 118,    | I/O  | Output after reset = used for 3 <sup>rd</sup> LED:                     | 11111   |

|               | 115,    |      | LEDMode[1:0]=11 -> Duplex/Col: (On=Full, Off=Half with no              |         |

|               | 110,    |      | collision, Flash=Collision)                                            |         |

|               | 107,    |      | LEDMode[1:0]=10 -> Duplex/Col: (On=Full, Off=Half with no              |         |

|               | 103     |      | collision, Flash=Collision)                                            |         |

|               |         |      | LEDMode[1:0]=01 -> TxAct: (Off=no activity, ON=Tx activity)            |         |

|               |         |      | LEDMode[1:0]=00 -> Col: (Off=Half with no collision, ON=Collide)       |         |

|               |         |      | Input upon reset = Refer below for each pin.                           |         |

| LED_ADD[4:0]/ | 99,96,  | I/O  | Output after reset = used for 4 <sup>th</sup> LED:                     | 11111   |

|               | 95,93,  |      | LEDMode[1:0]=11 -> Link/Act/Spd: On for link established. Blinking     |         |

|               | 92      |      | every 43ms when the corresponding port is transmitting or receiving in |         |

|               |         |      | 100Mb/s. Blinking every 120ms when the port is transmitting or         |         |

|               |         |      | receiving in 10Mb/s.                                                   |         |

|               |         |      | LEDMode[1:0]=10 -> Bi-color Link/Active: polarity depends on Spd       |         |

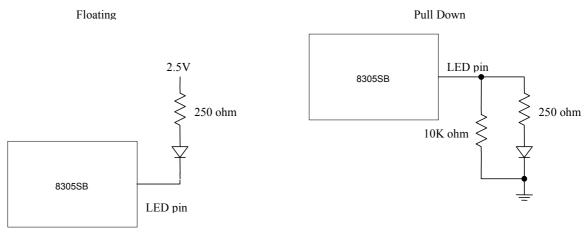

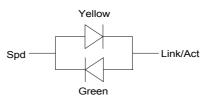

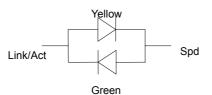

|               |         |      | status. See Figure2 and Table1.                                        |         |

|               |         |      | LEDMode[1:0]=01 -> Link: (On=Link, Off=no Link)                        |         |

|               |         |      | LEDMode[1:0]=00 -> Duplex: (On=Full, Off=Half)                         |         |

|               |         |      | Input upon reset = Refer below for each pin.                           |         |

|               |         |      | $8305SB = LED_ADD[4:0]/, 8305S = NC.$                                  |         |

RTL8305SB

### 5.6 Power Pins

| Pin Name | Pin No.  | Туре | Description                             | Default |

|----------|----------|------|-----------------------------------------|---------|

| TVDD     | 5,6,21,  | Р    | 3.3V Analog Transmit Power              |         |

|          | 22,37    |      |                                         |         |

| RVDD     | 13,14    | Р    | 2.5V Analog Receive Power               |         |

|          | 29,30    |      | 8305SB = 2.5V, 8305S = 3.3V.            |         |

| AVDD     | 126      | Р    | 3.3V Analog Power                       |         |

|          |          |      | 8305SB = 3.3V AVDD, 8305S = 3.3V RVDD.  |         |

| RVDD     | 125      | Р    | 2.5V Analog Receive Power               |         |

|          |          |      | 8305SB = 2.5V RVDD, 8305S = 3.3V AVDD.  |         |

| MVDD     | 38       | Р    | 2.5V Internal RAM Power                 |         |

|          |          |      | 8305SB = 2.5V, 8305S = 3.3V.            |         |

| VDD      | 43,53    | Р    | 2.5V Digital Power                      |         |

|          | 62,70    |      | 8305SB = 2.5V, 8305S = 3.3V.            |         |

|          | 87,100   |      |                                         |         |

|          | 106,114  |      |                                         |         |

| RGND     | 1,10,17, | Р    | Analog Ground                           |         |

|          | 26,33    |      |                                         |         |

| TGND     | 2,9,18,  | Р    | Analog Ground                           |         |

|          | 25,34    |      |                                         |         |

| AGND     | 122      | Р    | Analog GND                              |         |

|          | 123      |      | Pin122 for 8305SB = AGND, 8305S = DGND. |         |

| MGND     | 50       | Р    | Internal RAM GND                        |         |

|          |          |      | Pin50 for 8305SB = MGND, 8305S = GND.   |         |

| GND      | 39,64,   | Р    | Digital GND                             |         |

|          | 65,79    |      | Pin64 for 8305SB = GND, 8305S = MGND.   |         |

|          | 94,102   |      |                                         |         |

|          | 112      |      |                                         |         |

### **5.7 Reserved Pins**

| Pin Name  | Pin No. | Туре | Description                                                       | Default |

|-----------|---------|------|-------------------------------------------------------------------|---------|

| RESERVED1 | 72      | I/O  | Reserved: Reserved pin for internal use. Should be left floating. | 1       |

### **5.8 Serial EEPROM and SMI Pins**

The serial EEPROM and external device should be 2.5V compatible, as the output of the RTL8305SB is 2.5V.

If the external device output is 3.3V. There are 0.7V (3.3V-2.5V) on pull-high resistors which one side is a 3.3V external device and the other side is 2.5V VDD. There are 0.7V (3.3V-2.5V) on pull-high resistors which one side is 3.3V VDD and the other side is the 2.5V output of the RTL8305SB.

| Pin Name | Pin No. | Туре | Description                                                                                                                                                                                                             | Default |

|----------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| EnEEPROM | 73      | Ι    | <b>Enable EEPROM:</b> This pin sets the RTL8305SB to enable the loading of the serial EEPROM upon reset.                                                                                                                | 1       |

|          |         |      | 1: Enable<br>0: Disable                                                                                                                                                                                                 |         |

|          |         |      | 8305SB = EnEEPROM, $8305S = NC$ .                                                                                                                                                                                       |         |

| SCL_MDC  | 74      | I/O  | <b>SCL or MDC:</b> This pin is tri state when pin RESET#=0.                                                                                                                                                             |         |

|          |         |      | When pin EnEEPROM=1, this pin becomes SCL (output) to load the serial EEPROM upon reset. Then this pin changes as MDC (input) after reset. In this case, this pin should be pulled-high (2.5V) by an external resistor. |         |

|          |         |      | When pin EnEEPROM=0, this pin is MDC (input): 0 to 25MHz clock, sourced by an external device to sample MDIO. In this case, if, and only if, this pin is floating, it needs an external pull-high (2.5V) resistor.      |         |

|          |         |      | Because this pin can be connected to a 2.5V or 3.3V device, this pin has no internal pull-high resistor.                                                                                                                |         |

|          |         |      | $8305SB = SCL\_MDC, 8305S = NC.$                                                                                                                                                                                        |         |

| SDA_MDIO | 75      | IO   | <b>SDA or MDIO:</b> This pin is tri state when RESET#=0.                                                                                                                                                                |         |

|          |         |      | When pin EnEEPROM=1, this pin becomes SDA (input/output) to load the serial EEPROM upon reset. Then this pin changes as MDIO (input/output) after reset.                                                                |         |

|          |         |      | When pin EnEEPROM=0, this pin is MDIO (input/output).                                                                                                                                                                   |         |

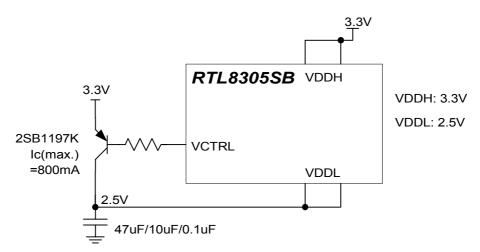

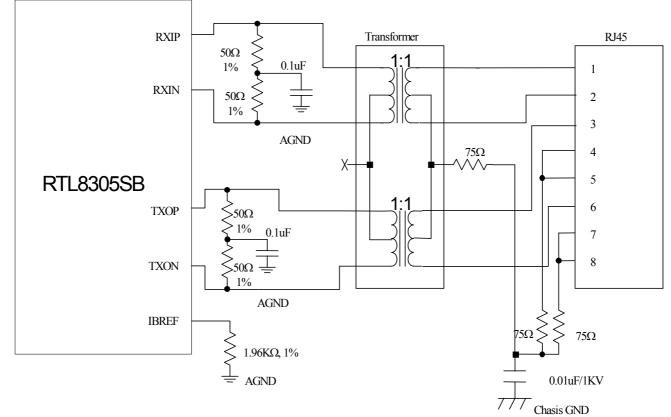

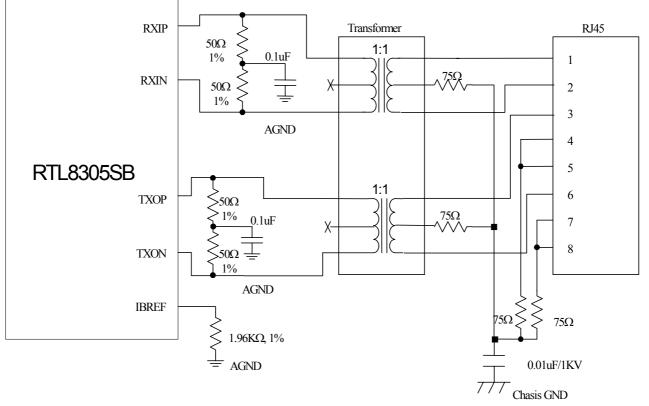

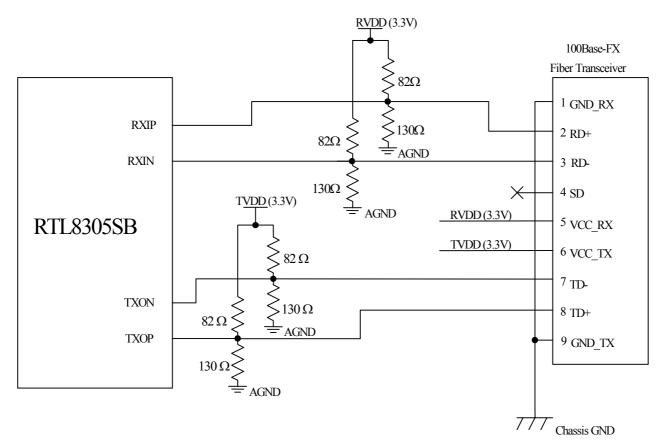

|          |         |      | It should be pulled-high by an external resistor.                                                                                                                                                                       |         |