May 2007

### LME49810 200V Audio Power Amplifier Driver with Baker Clamp

### **General Description**

The LME49810 is a high fidelity audio power amplifier driver designed for demanding consumer and pro-audio applications. Amplifier output power may be scaled by changing the supply voltage and number of power transistors. The LME49810's minimum output current is 50mA. When using a discrete output stage the LME49810 is capable of delivering in excess of 300 watts into a single-ended  $8\Omega$  load.

Unique to the LME49810 is an internal Baker Clamp. This clamp insures that the amplifier output does not saturate when over driven. The resultant "soft clipping" of high level audio signals suppresses undesirable audio artifacts generated when conventional solid state amplifiers are driven hard into clipping.

The LME49810 includes thermal shutdown circuitry that activates when the die temperature exceeds 150°C. The LME49810's mute function, when activated, mutes the input drive signal and forces the amplifier output to a quiescent state.

### **Key Specifications**

| <ul><li>Wide operating voltage range</li></ul> | ±20V to ±100V |

|------------------------------------------------|---------------|

| ■ Slew Rate                                    | 50V/µs (typ)  |

| <ul><li>Output Drive Current</li></ul>         | 60mA (typ)    |

| ■ PSRR (f = DC)                                | 110dB (typ)   |

| ■ THD:N (f = 1kHz)                             | 0.0007 (tvp)  |

#### **Features**

- Very high voltage operation

- Output clamp logic output

- Thermal shutdown and mute

- Customizable external compensation

- Scalable output power

### **Applications**

- Guitar amplifiers

- Powered studio monitors

- Powered subwoofers

- Pro audio

- Audio video receivers

- High voltage industrial applications

n 20216

www.national

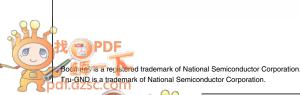

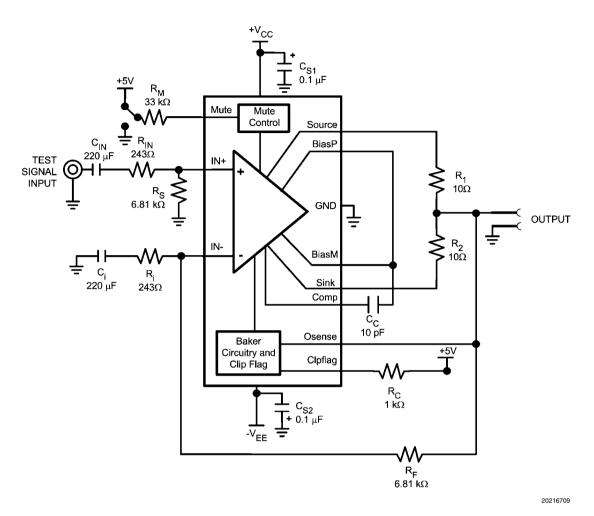

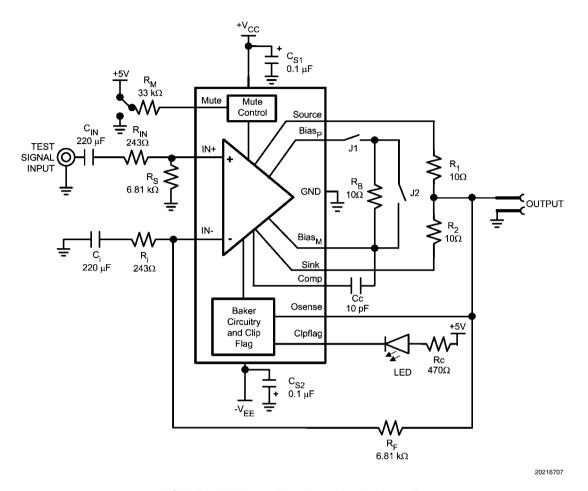

### **Typical Application**

FIGURE 1. LME49810 Audio Amplifier Schematic

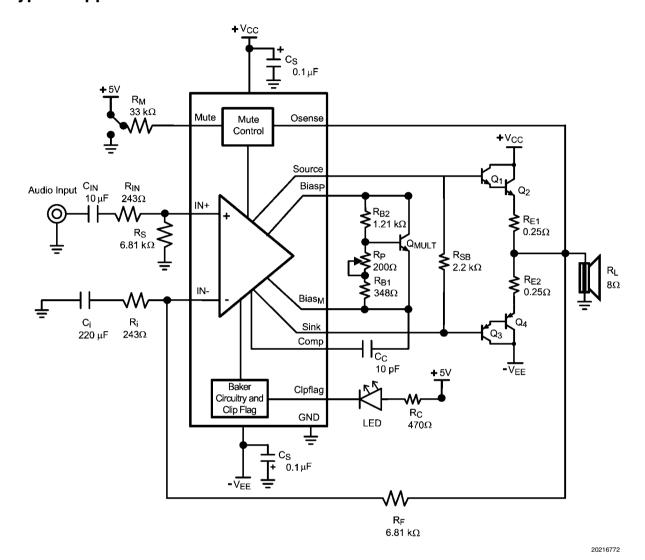

### **Connection Diagram**

Top View

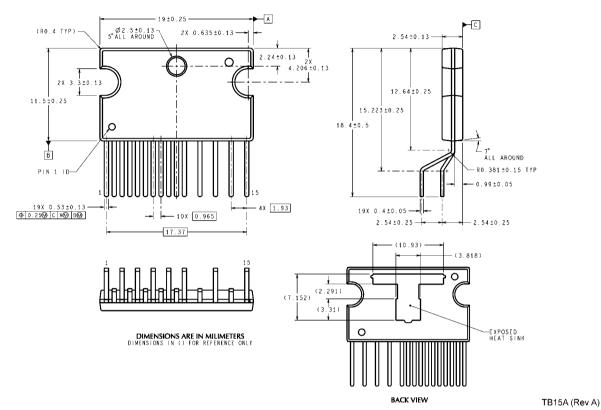

Order Number LME49810TB

See NS Package Number TB15A

N = National Logo

U = Fabrication plant code

Z = Assembly plant code

XY = 2 Digit date code

TT = Die traceability

TB = Package code

### **Pin Descriptions**

| Pin | Pin Name          | Description                           |

|-----|-------------------|---------------------------------------|

| 1   | ClpFlag           | Baker Clamp Clip Flag Output          |

| 2   | Mute              | Mute Control                          |

| 3   | GND               | Device Ground                         |

| 4   | IN+               | Non-Inverting Input                   |

| 5   | IN-               | Inverting Input                       |

| 6   | Comp              | External Compensation Connection      |

| 7   | NC                | No Connect, Pin electrically isolated |

| 8   | Osense            | Output Sense                          |

| 9   | NC                | No Connect, Pin electrically isolated |

| 10  | -V <sub>EE</sub>  | Negative Power Supply                 |

| 11  | Bias <sub>M</sub> | Negative External Bias Control        |

| 12  | Bias <sub>P</sub> | Positive External Bias Control        |

| 13  | Sink              | Output Sink                           |

| 14  | Source            | Output Source                         |

| 15  | +V <sub>CC</sub>  | Positive Power Supply                 |

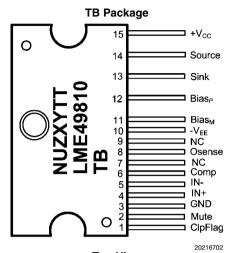

FIGURE 2. LME49810 Simplified Schematic

### **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage  $|V^+| + |V^-|$  200V Differential Input Voltage  $\pm 6V$  Common Mode Input Range 0.4V<sub>EE</sub> to 0.4V<sub>CC</sub> Power Dissipation (Note 3) 4W ESD Susceptibility (Note 4) 1kV ESD Susceptibility (Note 5) 200V Junction Temperature  $(T_{JMAX})$  (Note 9) 150°C Soldering Information

T Package (10 seconds) 260°C Storage Temperature -40°C to +150°C Thermal Resistance  $\theta_{JA}$  73°C/W  $\theta_{JC}$  4°C/W

### **Operating Ratings**

Temperature Range

$T_{MIN} \le T_A \le T_{MAX}$   $-40^{\circ}C \le T_A \le +85^{\circ}C$ Supply Voltage  $\pm 20V \le V_{SUPPLY} \le \pm 100V$

## Electrical Characteristics $V_{CC} = +100V$ , $V_{EE} = -100V$ (Notes 1, 2)

The following specifications apply for  $I_{MUTE}$  = 100 $\mu$ A, unless otherwise specified. Limits apply for  $T_{A}$  = 25°C,  $C_{C}$  = 10pF, and  $A_{V}$  = 29dB.

| Symbol             | Parameter                         | Conditions                                                     | LME49810            |                        |                      |

|--------------------|-----------------------------------|----------------------------------------------------------------|---------------------|------------------------|----------------------|

|                    |                                   |                                                                | Typical<br>(Note 6) | Limits<br>(Notes 7, 8) | Units<br>(Limits)    |

| I <sub>CC</sub>    | Quiescent Power Supply Current    | $V_{CM} = 0V, V_{O} = 0V, I_{O} = 0A$                          | 11                  | 18                     | mA (max)             |

| I <sub>EE</sub>    | Quiescent Power Supply Current    | $V_{CM} = 0V, V_{O} = 0V, I_{O} = 0A$                          | 13                  |                        | mA (max)             |

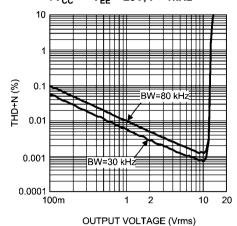

| THD+N              | Total Harmonic Distortion + Noise | No Load, BW = $30kHz$<br>$V_{OUT} = 30V_{RMS}$ , $f = 1kHz$    | 0.0007              |                        | % (max)              |

| A <sub>V</sub>     | Open Loop Gain                    | f = DC<br>$f = 1kHz$ , $V_{IN} = 1mV_{RMS}$                    | 120<br>88           |                        | dB<br>dB             |

| V <sub>OM</sub>    | Output Voltage Swing              | THD+N = 0.05%, f = 1kHz                                        | 67.5                |                        | V <sub>RMS</sub>     |

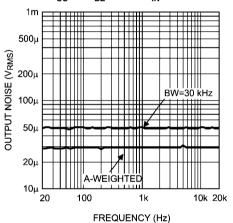

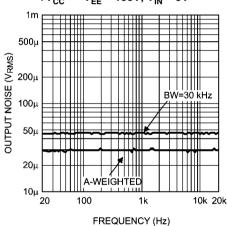

| V <sub>NOISE</sub> | Output Noise                      | BW = 30kHz,<br>A-weighted                                      | 50<br>34            | 150                    | μV<br>μV (max)       |

| I <sub>OUT</sub>   | Output Current                    | Current from Source to Sink Pins                               | 60                  | 50                     | mA (min)             |

| I <sub>MUTE</sub>  | Current into Mute Pin             | To activate the amplifier                                      | 100                 | 50<br>200              | μΑ (min)<br>μΑ (max) |

| SR                 | Slew Rate                         | V <sub>IN</sub> = 1V <sub>P-P</sub> ,<br>f = 10kHz square Wave | 50                  |                        | V/µs(min)            |

| V <sub>os</sub>    | Input Offset Voltage              | V <sub>CM</sub> = 0V, I <sub>O</sub> = 0mA                     | 1                   | 3                      | mV (max)             |

| I <sub>B</sub>     | Input Bias Current                | V <sub>CM</sub> = 0V, I <sub>O</sub> = 0mA                     | 100                 | 200                    | nA (max)             |

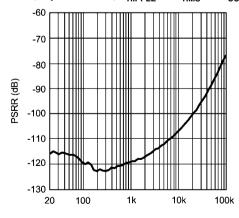

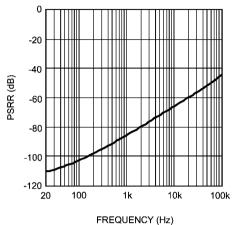

| PSRR               | Power Supply Rejection Ratio      | f = DC, Input Referred                                         | 110                 | 105                    | dB (min)             |

| V <sub>CLIP</sub>  | Baker Clamp Clipping Voltage      | Clip Output<br>Source pin<br>Sink pin                          | 97.2<br>-96.4       | 95.5<br>-95.5          | V (max)<br>V (min)   |

| V <sub>BC</sub>    | Baker Clamp Flag Output Voltage   | I <sub>FLAG</sub> = 4.7mA                                      | 0.4                 |                        | V                    |

| V <sub>BA</sub>    | Bias P&M Pin Open Voltage         | BiasP - BiasM                                                  | 10                  |                        | V                    |

| I <sub>BIAS</sub>  | Bias Adjust Function Current      |                                                                | 2.8                 |                        | mA                   |

Note 1: All voltages are measured with respect to the GND pin unless otherwise specified.

**Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

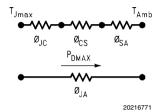

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JC}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JC}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LME49810,  $T_{JMAX} = 150^{\circ}$  C and the typical  $\theta_{JC}$  is 4°C/W. Refer to the **Thermal Considerations** section for more information.

Note 4: Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

Note 5: Machine Model, 220pF - 240pF discharged through all pins.

Note 6: Typicals are measured at +25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9: The maximum operating junction temperature is 150°C.

Note 10: Data taken with Bandwidth = 30kHz,  $A_V = 29$ dB,  $C_C = 10$ pF, and  $T_A = 25$ °C except where specified.

FIGURE 3. LME49810 Test Circuit Schematic (DC Coupled)

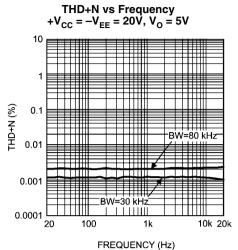

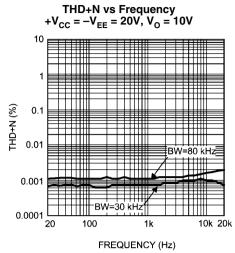

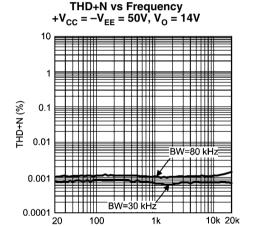

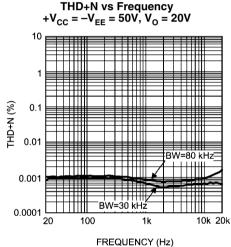

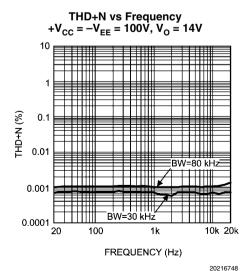

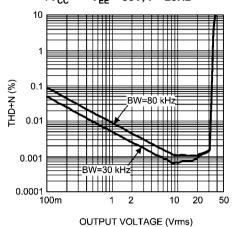

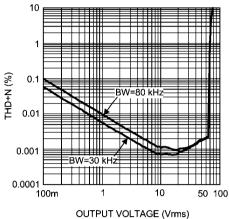

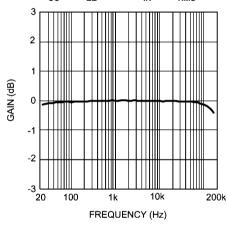

### **Typical Performance Characteristics** (Note 10)

20216744

20216745

FREQUENCY (Hz)

20216746

20216747

THD+N vs Frequency  $+V_{CC} = -V_{EE} = 50V, V_{O} = 30V$ (%) N+QH1 0.01 0.001 0.0001 20 100 10k 20k

FREQUENCY (Hz)

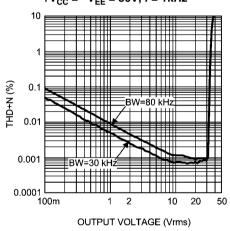

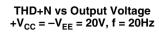

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 50V$ , f = 20Hz

20216757

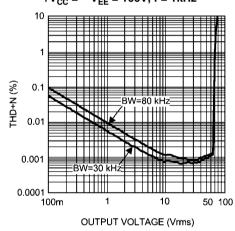

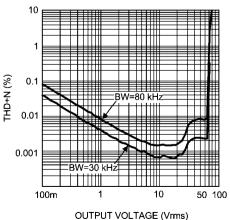

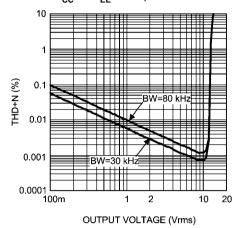

### THD+N vs Output Voltage +V<sub>CC</sub> = -V<sub>EE</sub> = 100V, f = 20Hz

20216755

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 50V$ , f = 1kHz

20216753

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 100V$ , f = 1kHz

20216754

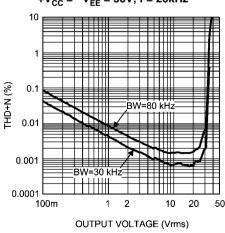

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 50V$ , f = 20kHz

20216758

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 100V$ , f = 20kHz

20216751

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 20V$ , f = 20kHz

2021675

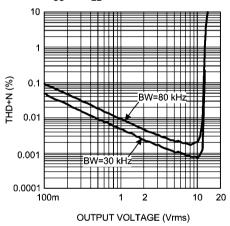

# Closed Loop Frequency Response $+V_{CC} = -V_{EE} = 100V$ , $V_{IN} = 1V_{RMS}$

20216736

# THD+N vs Output Voltage $+V_{CC} = -V_{EE} = 20V$ , f = 1kHz

20216750

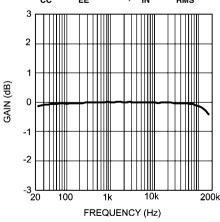

# Closed Loop Frequency Response $+V_{CC} = -V_{EE} = 50V$ , $V_{IN} = 1V_{RMS}$

20216735

PSRR vs Frequency  $+V_{CC}=-V_{EE}=100V,$  No Filters, Input referred,  $V_{RIPPLE}=1V_{RMS}$  on  $V_{CC}$  pin

FREQUENCY (Hz)

# PSRR vs Frequency $+V_{CC} = -V_{EE} = 100V$ , No Filters, Input referred, $V_{RIPPLE} = 1V_{RMS}$ on $V_{EE}$ pin

20216727

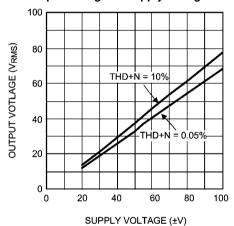

#### **Output Voltage vs Supply Voltage**

20216725

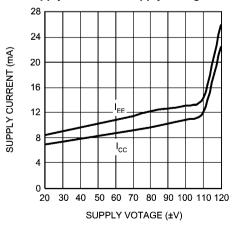

#### **Supply Current vs Supply Voltage**

20216741

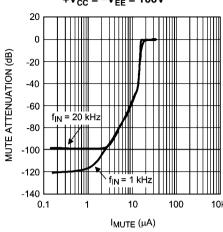

### Mute Attenuation vs $I_{MUTE}$ + $V_{CC} = -V_{EE} = 100V$

20216724

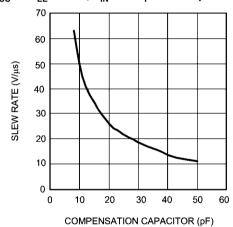

# Slew Rate vs Compensation Capacitor $+V_{CC} = -V_{EE} = 100V$ , $V_{IN} = 1.2V_p$ 10kHz squarewave

20216728

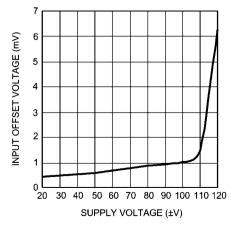

#### Input Offset Voltage vs Supply Voltage

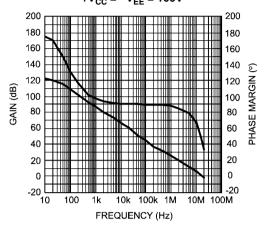

# Open Loop Gain and Phase Margin $+V_{CC} = -V_{EE} = 100V$

20216738

# Noise Floor $+V_{CC} = -V_{EE} = 50V, V_{IN} = 0V$

20216742

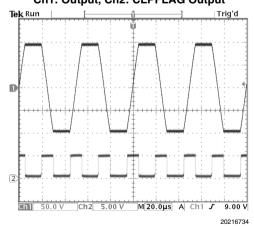

# $\begin{array}{c} \text{Baker Clamp Flag Output} \\ +\text{V}_{\text{CC}} = -\text{V}_{\text{EE}} = 100\text{V}, \, \text{V}_{\text{IN}} = 4\text{V}_{\text{RMS}}, \, \text{f}_{\text{IN}} = 20\text{kHz} \\ \text{Ch1: Output, Ch2: CLPFLAG Output} \end{array}$

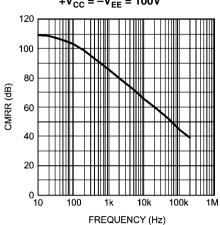

CMRR vs Frequency +V<sub>CC</sub> = -V<sub>EE</sub> = 100V

20216722

Noise Floor

$$+V_{CC} = -V_{EE} = 100V, V_{IN} = 0V$$

### **Application Information**

#### **MUTE FUNCTION**

The mute function of the LME49810 is controlled by the amount of current that flows into the MUTE pin. LME49810 typically requires  $50\mu\text{A}$  to  $100\mu\text{A}$  of mute current flowing in order to be in "play" mode. This can be done by connecting a reference voltage ( $V_{\text{MUTE}}$ ) to the MUTE pin through a resistor ( $R_{\text{M}}$ ). The following formula can be used to calculate the mute current.

$$I_{MUTE} = (V_{MUTE} - 0.7V) / (R_M + 10k\Omega) (A)$$

(1)

The  $10k\Omega$  resistor value in Equation 1 is internal. Please refer to Figure 2, LME49810 Simplified Schematic, for additional details. For example, if a 5V voltage is connected through a  $33k\Omega$  resistor to the MUTE pin, then the mute current will be  $100\mu\text{A}$ , according to Equation 1. Consequently,  $R_\text{M}$  can be changed to suit any other reference voltage requirement. The LME49810 will enter Mute mode if  $I_{\text{MUTE}}$  is less than  $1\mu\text{A}$  which can be accomplished by shorting the MUTE pin to ground or by floating the MUTE pin. It is not recommended that more than  $200\mu\text{A}$  flow into the MUTE pin because damage to LME49810 may occur and device may not function properly.

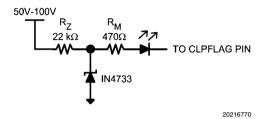

#### BAKER CLAMP AND CLAMP FLAG OUTPUT

The LME49810 features a Baker Clamp function with corresponding CLPFLAG output pin. The clamp function keeps all transistors in linear operation when the output goes into clipping. In addition, when the output goes into clipping, a logic low level appears at the CLPFLAG pin. The CLPFLGAG pin can be used to drive an LED or some other visual display as shown by Figure 1. The value of logic low voltage varies and depends on I<sub>FLAG</sub>. For example, if I<sub>FLAG</sub> is 4.7mA then a voltage (V<sub>BC</sub>) of 0.4V will appear at the CLPFLAG output pin. The smooth response of the Baker Clamp and the corresponding CLPFLAG logic output is shown in the scope photo below:

+ $V_{CC}$  = - $V_{EE}$  = 100V,  $V_{IN}$  = 4 $V_{RMS}$ ,  $f_{IN}$  = 1kHz,  $R_C$  = 1k $\Omega$  Ch1: Output, Ch2: CLPFLAG Output

The CLPFLAG pin can source up to 10mA, and since the CLPFLAG output is an open collector output as shown by Figure 2, LME49810 Simplified Schematic, it should never be left to float under normal operation. If CLPFLAG pin is not used, then it should be connected through a resistor to a reference voltage so that I<sub>FLAG</sub> is below 10mA. For example, a resistor of 1k can be used with a 5V reference voltage. This will give the I<sub>FLAG</sub> of 4.7mA. In a typical LED setup, if +5V

reference voltage is not available, the following circuit using a Zener diode can be used to power the CLPFLAG pin from the higher supply voltage rails of the LME49810. The power dissipation rating of  $\rm R_Z$  will need to be at-least ½W if using a 5V Zener Diode. Alternately, the following basic formula can be used to find the proper power rating of  $\rm R_Z:P_{DZ}=(V_{CC}-V_Z)^2/R_Z$  (W). This formula can also be used to meet the design requirements of any other reference voltage that the user desires

#### THERMAL PROTECTION

The LME49810 has a thermal protection scheme to prevent long-term thermal stress of the device. When the temperature on the die exceeds 150°C, the LME49810 goes into thermal shutdown. The LME49810 starts operating again when the die temperature drops to about 145°C, but if the temperature again begins to rise, shutdown will occur again above 150°C. Therefore, the device is allowed to heat up to a relatively high temperature if the fault condition is temporary, but a sustained fault will cause the device to cycle between the thermal shutdown temperature limits of 150°C and 145°C. This greatly reduces the stress imposed on the IC by thermal cycling, which in turn improves its reliability under sustained fault conditions. Since the die temperature is directly dependent upon the heat sink used, the heat sink should be chosen so that thermal shutdown is not activated during normal operation. Using the best heat sink possible within the cost and space constraints of the system will improve the long-term reliability of any power semiconductor device, as discussed in the Determining the Correct Heat Sink section.

#### POWER DISSIPATION

When in "play" mode, the LME49810 draws a constant amount of current, regardless of the input signal amplitude. Consequently, the power dissipation is constant for a given supply voltage and can be computed with the equation  $P_{DMAX} = I_{CC} \ \ (V_{CC} - V_{EE}).$  For a quick calculation of  $P_{DMAX}$ , approximate the current to be 11mA and multiply it by the total supply voltage (the current varies slightly from this value over the operating range).

#### **DETERMINING THE CORRECT HEAT SINK**

The choice of a heat sink for a high-power audio amplifier is made entirely to keep the die temperature at a level such that the thermal protection circuitry is not activated under normal circumstances.

The thermal resistance from the die to the outside air,  $\theta_{JA}$  (junction to ambient), is a combination of three thermal resistances,  $\theta_{JC}$  (junction to case),  $\theta_{CS}$  (case to sink), and  $\theta_{SA}$  (sink to ambient). The thermal resistance,  $\theta_{JC}$  (junction to case), of the LME49810 is 4°C/W. Using Thermalloy Thermacote thermal compound, the thermal resistance,  $\theta_{CS}$  (case to sink), is about 0.2°C/W. Since convection heat flow (power dissipation) is analogous to current flow, thermal resistance is analogous to electrical resistance, and temperature drops are

analogous to voltage drops, the power dissipation out of the LME49810 is equal to the following:

$$P_{DMAX} = (T_{JMAX} - T_{AMB}) / \theta_{JA}$$

(2)

where  $T_{JMAX}$  = 150°C,  $T_{AMB}$  is the system ambient temperature and  $\theta_{JA}$  =  $\theta_{JC}$  +  $\theta_{CS}$  +  $\theta_{SA}$ .

Once the maximum package power dissipation has been calculated using Equation 2, the maximum thermal resistance,  $\theta_{SA}$ , (heat sink to ambient) in °C/W for a heat sink can be calculated. This calculation is made using Equation 3 which is derived by solving for  $\theta_{SA}$  from Equation 2.

$$\theta_{SA} = \left[ \left( T_{JMAX} - T_{AMB} \right) - P_{DMAX} \left( \theta_{JC} + \theta_{CS} \right) \right] / P_{DMAX}$$

(3)

Again it must be noted that the value of  $\theta_{SA}$  is dependent upon the system designer's amplifier requirements. If the ambient temperature that the audio amplifier is to be working under is higher than 25°C, then the thermal resistance for the heat sink, given all other things are equal, will need to be smaller.

#### PROPER SELECTION OF EXTERNAL COMPONENTS

Proper selection of external components is required to meet the design targets of an application. The choice of external component values that will affect gain and low frequency response are discussed below.

The overall gain of the amplifier is set by resistors  $R_F$  and  $R_i$  for the non-inverting configuration shown in Figure 1. The gain is found by Equation 4 below given  $R_i = R_{IN}$  and  $R_F = R_S$ .

$$A_{V} = R_{F} / R_{i} (V/V)$$

(4)

For best Noise performance, lower values of resistors are used. A value of 243 is commonly used for  $\rm R_i$  and setting the value for  $\rm R_F$  for desired gain. For the LME49810 the gain should be set no lower than 10V/V. Gain settings below 10V/V may experience instability.

The combination of  $R_i$  and  $C_i$  (see Figure 1) creates a high pass filter. The gain at low frequency and therefore the response is determined by these components. The -3dB point can be determined from Equation 5 shown below:

$$f_i = 1 / (2\pi R_i C_i) (Hz)$$

(5)

If an input coupling capacitor  $(C_{IN})$  is used to block DC from the inputs as shown in Figure 1, there will be another high pass filter created with the combination of  $C_{IN}$  and  $R_{IN}$ . The resulting -3dB frequency response due to the combination of  $C_{IN}$  and  $R_{IN}$  can be found from equation 6 shown below:

$$f_{IN} = 1 / (2\pi R_{IN} C_{IN}) (Hz)$$

(6)

For best audio performance, the input capacitor should not be used. Without the input capacitor, any DC bias from the source will be transferred to the load. The feedback capacitor  $(C_i)$  is used to set the gain at DC to unity. Because a large value is required for a low frequency -3dB point, the capacitor

is an electrolytic type. An additional small value, high quality film capacitor may be used in parallel with the feedback resistor to improve high frequency sonic performance. If DC offset in the output stage is acceptable without the feedback capacitor, it may be removed but DC gain will now be equal to AC gain.

#### **COMPENSATION CAPACITOR**

The compensation capacitor ( $C_C$ ) is one of the most critical external components in value, placement and type. The capacitor should be placed close to the LME49810 and a silver mica type will give good performance. The value of the capacitor will affect slew rate and stability. The highest slew rate is possible while also maintaining stability through out the power and frequency range of operation results in the best audio performance. The value shown in Figure 1 should be considered a starting value with optimization done on the bench and in listening testing. Please refer to Slew Rate vs.  $C_C$  Graph in **Typical Performance Characteristics** for determining the proper slew rate for your particular application.

#### **SUPPLY BYPASSING**

The LME49810 has excellent power supply rejection and does not require a regulated supply. However, to eliminate possible oscillations all op amps and power op amps should have their supply leads bypassed with low-inductance capacitors having short leads and located close to the package terminals. Inadequate power supply bypassing will manifest itself by a low frequency oscillation known as "motorboating" or by high frequency instabilities. These instabilities can be eliminated through multiple bypassing utilizing a large electrolytic capacitor (10µF or larger) which is used to absorb low frequency variations and a small ceramic capacitor (0.1µF) to prevent any high frequency feedback through the power supply lines. If adequate bypassing is not provided the current in the supply leads which is a rectified component of the load current may be fed back into internal circuitry. This signal causes low distortion at high frequencies requiring that the supplies be bypassed at the package terminals with an electrolytic capacitor of 470µF or more.

#### **OUTPUT STAGE USING BIPOLAR TRANSISTORS**

With a properly designed output stage and supply voltage of  $\pm 100\text{V}$ , an output power up to 500W can be generated at 0.05% THD+N into an  $8\Omega$  speaker load. With an output current of several amperes, the output transistors need substantial base current drive because power transistors usually have quite low current gain—typical  $h_{fe}$  of 50 or so. To increase the current gain, audio amplifiers commonly use Darlington style devices. Power transistors should be mounted together with the  $V_{BE}$  multiplier transistor on the same heat sink to avoid thermal run away. Please see the section Biasing Technique and Avoiding Thermal Runaway for additional information.

### BIASING TECHNIQUES AND AVOIDING THERMAL RUNAWAY

A class AB amplifier has some amount of distortion called Crossover distortion. To effectively minimize the crossover distortion from the output, a  $\rm V_{BE}$  multiplier may be used instead of two biasing diodes. The LME49810 has two dedicated pins (BIAS $_{\rm M}$  and BIAS $_{\rm P}$ ) for Bias setup and provide a constant current source of about 2.8mA. A  $\rm V_{BE}$  multiplier normally consists of a bipolar transistor (Q $_{\rm MULT}$ , see Figure 1) and two resistors (R $_{\rm B1}$  and R $_{\rm B2}$ , see Figure 1). A trim pot can also be added in series with R $_{\rm B1}$  for optional bias adjustment. A properly designed output stage, combine with a  $\rm V_{BE}$  multiplier,

can eliminate the trim pot and virtually eliminate crossover distortion. The  $V_{CE}$  voltage of  $Q_{MULT}$  (also called BIAS of the output stage) can be set by following formula:

$$V_{BIAS} = V_{BE}(1 + R_{B2}/R_{B1}) (V)$$

(7)

When using a bipolar output stage with the LME49810 (as in Figure 1), the designer must beware of thermal runaway. Thermal runaway is a result of the temperature dependence of V<sub>RE</sub> (an inherent property of the transistor). As temperature increases, V<sub>RF</sub> decreases. In practice, current flowing through a bipolar transistor heats up the transistor, which lowers the V<sub>BE</sub>. This in turn increases the current gain, and the cycle repeats. If the system is not designed properly this positive feedback mechanism can destroy the bipolar transistors used in the output stage. One of the recommended methods of preventing thermal runaway is to use the same heat sink on the bipolar output stage transistor together with V<sub>BE</sub> multiplier transistor. When the V<sub>BE</sub> multiplier transistor is mounted to the same heat sink as the bipolar output stage transistors, it temperature will track that of the output transistors. Its V<sub>RE</sub> is dependent upon temperature as well, and so it will draw more current as the output transistors heat up, reducing the bias voltage to compensate. This will limit the base current into the output transistors, which counteracts thermal runaway. Another widely popular method of preventing thermal runaway is to use low value emitter degeneration resistors (R<sub>F1</sub> and R<sub>E2</sub>). As current increases, the voltage at the emitter also increases, which decreases the voltage across the base and emitter. This mechanism helps to limit the current and counteracts thermal runaway.

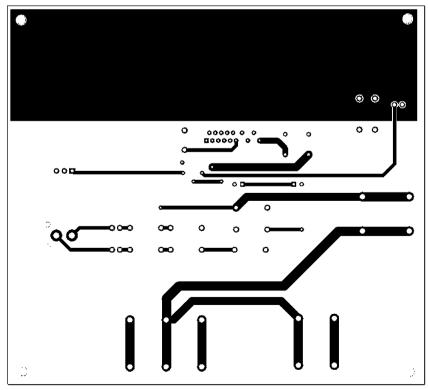

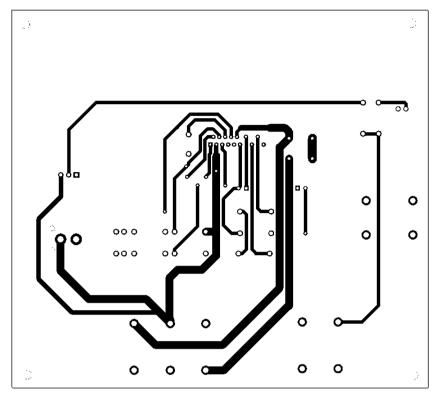

### LAYOUT CONSIDERATION AND AVOIDING GROUND LOOPS

A proper layout is virtually essential for a high performance audio amplifier. It is very important to return the load ground, supply grounds of output transistors, and the low level (feedback and input) grounds to the circuit board common ground point through separate paths. When ground is routed in this fashion, it is called a star ground or a single point ground. It is advisable to keep the supply decoupling capacitors of 0.1µF close as possible to LME49810 to reduce the effects of PCB trace resistance and inductance. Following the general rules will optimize the PCB layout and avoid ground loops problems:

- a) Make use of symmetrical placement of components.

- b) Make high current traces, such as output path traces, as wide as possible to accomodate output stage current requirement.

- c) To reduce the PCB trace resistance and inductance, same ground returns paths should be as short as possible. If possible, make the output traces short and equal in length.

- d) To reduce the PCB trace resistance and inductance, ground returns paths should be as short as possible.

- e) If possible, star ground or a single point ground should be observed. Advanced planning before starting the PCB can improve audio performance.

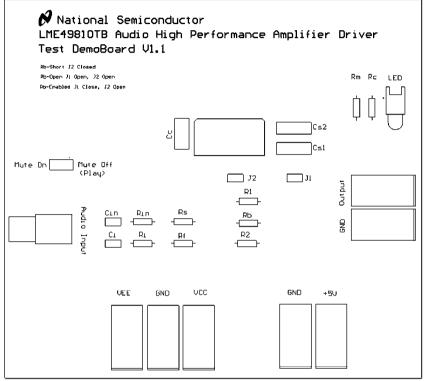

### **Demo Board Schematic**

FIGURE 4. LME49810 Test demo board schematic

### **Demonstration Board Layout**

Silkscreen Layer

20216704

**Top Layer**

**Bottom Layer**

## **Revision History**

| Rev  | Date     | Description          |

|------|----------|----------------------|

| 1.0  | 05/24/07 | Initial WEB release. |

| 1.01 | 05/29/07 | Few text edits.      |

### Physical Dimensions inches (millimeters) unless otherwise noted

TO-247 15-Lead Package Order Number LME49810TB NS Package Number TB15A

# Notes

### **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com

Tel: 1-800-272-9959

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560