TOSHIBA Original CMOS 32-Bit Microcontroller

# TLCS-900/H1 Series

# TMP92CH21FG

## **TOSHIBA CORPORATION**

Semiconductor Company

www.DataSheet4U.com

## Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions".

CMOS 32-bit Microcontroller

## TMP92CH21FG/JTMP92CH21

## 1. Outline and Device Characteristics

The TMP92CH21 is a high-speed advanced 32-bit Microcontroller developed for controlling equipment which processes mass data.

The TMP92CH21 has a high-performance CPU (900/H1 CPU) and various built-in I/Os.

The TMP92CH21FG is housed in a 144-pin flat package. The JTMP92CH21 is a chip form product.

Device characteristics are as follows:

- (1) CPU: 32-bit CPU (900/H1 CPU)

- Compatible with TLCS-900/L1 instruction code

- 16 Mbytes of linear address space

- General-purpose register and register banks

- Micro DMA: 8 channels (250 ns/4 bytes at f<sub>SYS</sub> = 20 MHz, best case)

- (2) Minimum instruction execution time: 50 ns (at  $f_{SYS} = 20 \text{ MHz}$ )

## RESTRICTIONS ON PRODUCT USE

060116EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of

Stress TOSHIBA products could cause loss of human life, bodily injury or damage to

property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. 021023\_C

- The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_s

92CH21-1

heet4U.com

- (3) Internal memory

- Internal RAM: 16 Kbytes (can be used for program, data and display memory)

- Internal ROM: 8 Kbytes (used as boot program) Possible downloading of user program through either USB, UART or NAND flash.

- (4) External memory expansion

- Expandable up to 512 Mbytes (shared program/data area)

- Can simultaneously support 8,- 16- or 32-bit width external data bus ... dynamic data bus sizing

- Separate bus system

- (5) Memory controller

- Chip select output: 4 channels

- (6) 8-bit timers: 4 channels

- (7) 16-bit timer/event counter: 1 channel

- (8) General-purpose serial interface: 2 channels

- UART/synchronous mode: 2 channels (channel 0 and 1)

- IrDA ver.1.0 (115 kbps) mode selectable: 1 channel (channel 0)

- (9) USB (universal serial bus) controller: 1 channel

- Compliant with USB ver.1.1

- Full-speed (12 MHz) (Low-speed is not supported.)

- Endpoints spec

- Endpoint 0: Control 64 bytes\* 1-FIFO

- Endpoint 1: BULK (out) 64 bytes\* 2-FIFO

- Endpoint 2: BULK (in) 64 bytes\* 2-FIFO

- Endpoint 3: Interrupt (in) 8 bytes\* 1-FIFO

- Descriptor RAM: 384 bytes

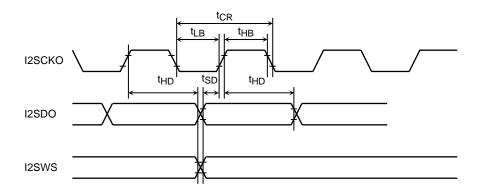

(10)  $I^2S$  (Inter-IC sound) interface: 1 channel

- I<sup>2</sup>S bus mode/SIO mode selectable (Master, transmission only)

- 32-byte FIFO buffer

- (11) LCD controller

- Supports up to 4096 color for TFT, 256 color, 16, 8, 4 gray levels and B/W for STN

- Shift register/built-in RAM LCD driver

(12) SDRAM controller: 1 channel

- Supports 16 M, 64 M, 128 M, 256 M, and up to 512-Mbit SDR (Single Data Rate)-SDRAM

- Possible to execute instruction on SDRAM

(13) Timer for real-time clock (RTC)

- (14) Key-on wakeup (Interrupt key input)

- (15) 10-bit AD converter: 4 channels

(16) Touch screen interface

• Available to reduce external components

(17) Watchdog timer

(18) Melody/alarm generator

- Melody: Output of clock 4 to 5461 Hz

- Alarm: Output of 8 kinds of alarm pattern and 5 kinds of interval interrupt

(19) MMU

- Expandable up to 512 Mbytes (3 local area/8 bank method)

- Independent bank for each program, read data, write data and LCD display data

(20) Interrupts: 50 interrupt

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 34 internal interrupts: Seven selectable priority levels

- 7 external interrupts: Seven selectable priority levels (6-edge selectable)

(21) Input/output ports: 82 pins (Except Data bus (16bit), Address bus (24bit) and RD pin)

(22) NAND flash interface: 2 channels

- Direct NAND flash connection capability

- ECC calculation (for SLC- type)

(23) Stand-by function

- Three HALT modes: IDLE2 (programmable), IDLE1, STOP

- Each pin status programmable for stand-by mode

(24) Triple-clock controller

- Clock doubler (PLL) supplies 48 MHz for USB, 36 MHz system-clock for others

- Clock gear function: Select high-frequency clock fc to fc/16

- RTC (fs = 32.768 kHz)

(25) Operating voltage:

- VCC = 3.0 V to 3.6 V (fc max = 40 MHz)

- VCC = 2.7 V to 3.6 V (fc max = 27 MHz)

(26) Package:

- 144-pin QFP (P-LQFP144 -1616-0.40C)

- 144-pin chip form is also available. For details, contact your local Toshiba sales representative.

2006-09-15

92CH21-3

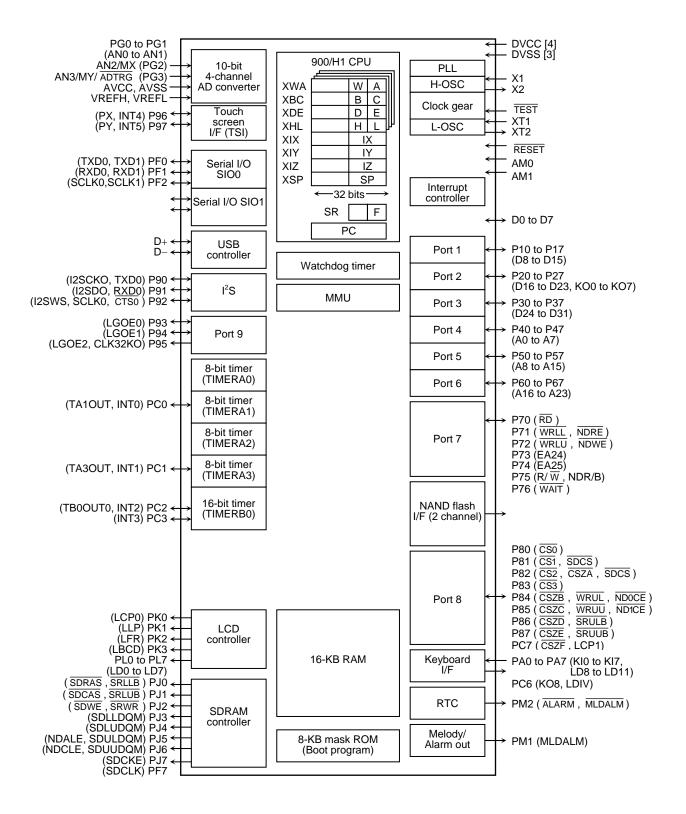

Figure 1.1 TMP92CH21 Block Diagram

## 2. Pin Assignment and Functions

The assignment of input/output pins for the TMP92CH21FG, their names and functions are as follows:

## 2.1 Pin Assignment

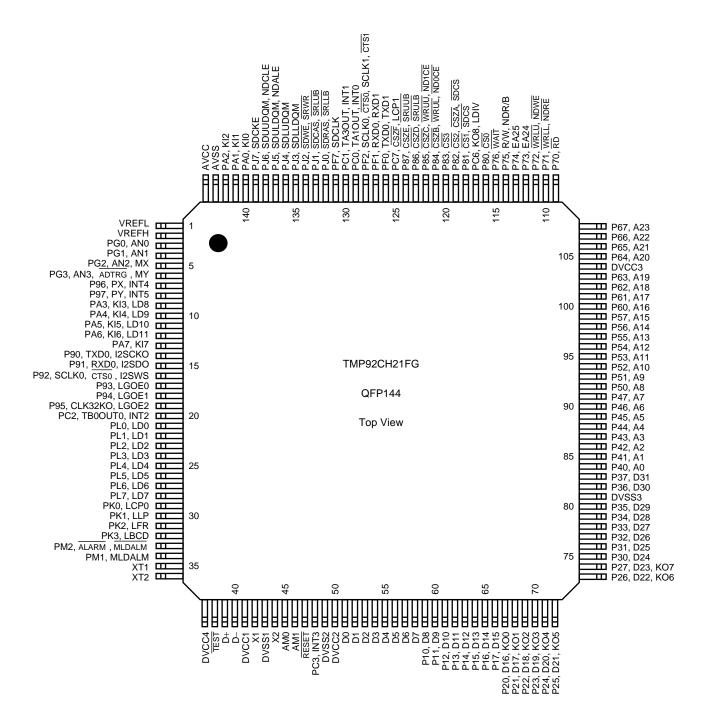

Figure 2.1.1 Pin Assignment Diagram (144-pin QFP)

## 2.2 PAD Assignment

(Chip size 5.98 mm  $\times$  6.42 mm)

| Table 2.2.1 Pad Assignment Diagram (1 | 44-pin chip) |

|---------------------------------------|--------------|

|---------------------------------------|--------------|

| Table 2.2.1 Pad Assignment Diagram (144-pin chip)<br>Unit: μr |            |                |              |          |            |              | Unit: µm       |            |            |            |              |

|---------------------------------------------------------------|------------|----------------|--------------|----------|------------|--------------|----------------|------------|------------|------------|--------------|

| Pin                                                           |            | Х              | Y            | Pin      |            | Х            | Y              | Pin        |            | Х          | Y.           |

| No                                                            | Name       | Point          | Point        | No       | Name       | Point        | Point          | No         | Name       | Point      | Point        |

| 1                                                             | VREFL      | -2852          | 2671         | 49       | DVSS2      | -488         | -3072          | 97         | P55        | 2848       | 815          |

| 2                                                             | VREFH      | -2852          | 2546         | 50       | DVCC2      | -338         | -3072          | 98         | P56        | 2848       | 941          |

| 3                                                             | PG0        | -2852          | 2421         | 51       | D0         | -200         | -3072          | 99         | P57        | 2848       | 1066         |

| 4                                                             | PG1        | -2852          | 2296         | 52       | D1         | -75          | -3072          | 100        | P60        | 2848       | 1191         |

| 5                                                             | PG2        | -2852          | 2171         | 53       | D2         | 49           | -3072          | 100        | P61        | 2848       | 1316         |

| 6                                                             | PG3        | -2852          | 2045         | 54       | D3         | 174          | -3072          | 102        | P62        | 2848       | 1441         |

| 7                                                             | P96        | -2852          | 1920         | 55       | D4         | 300          | -3072          | 103        | P63        | 2848       | 1566         |

| 8                                                             | P97        | -2852          | 1795         | 56       | D5         | 425          | -3072          | 104        | DVCC3      | 2848       | 1692         |

| 9                                                             | PA3        | -2852          | 1270         | 57       | D6         | 550          | -3072          | 105        | P64        | 2848       | 1823         |

| 10                                                            | PA4        | -2852          | 1145         | 58       | D7         | 675          | -3072          | 106        | P65        | 2848       | 1974         |

| 11                                                            | PA5        | -2852          | 1020         | 59       | P10        | 800          | -3072          | 107        | P66        | 2848       | 2130         |

| 12                                                            | PA6        | -2852          | 895          | 60       | P11        | 925          | -3072          | 108        | P67        | 2848       | 2292         |

| 13                                                            | PA7        | -2852          | 769          | 61       | P12        | 1050         | -3072          | 109        | P70        | 2460       | 3065         |

| 14                                                            | P90        | -2852          | 644          | 62       | P13        | 1176         | -3072          | 110        | P71        | 2295       | 3065         |

| 15                                                            | P91        | -2852          | 519          | 63       | P14        | 1301         | -3072          | 111        | P72        | 2127       | 3065         |

| 16                                                            | P92        | -2852          | 394          | 64       | P15        | 1426         | -3072          | 112        | P73        | 1964       | 3065         |

| 17                                                            | P93        | -2852          | 269          | 65       | P16        | 1551         | -3072          | 113        | P74        | 1807       | 3065         |

| 18                                                            | P94        | -2852          | 144          | 66       | P17        | 1676         | -3072          | 114        | P75        | 1654       | 3065         |

| 19                                                            | P95        | -2852          | 18           | 67       | P20        | 1801         | -3072          | 115        | P76        | 1506       | 3065         |

| 20                                                            | PC2        | -2852          | -106         | 68       | P21        | 1927         | -3072          | 116        | P80        | 1361       | 3065         |

| 21                                                            | PL0        | -2852          | -231         | 69       | P22        | 2052         | -3072          | 117        | PC6        | 1226       | 3065         |

| 22                                                            | PL1<br>PL2 | -2852          | -356<br>-481 | 70<br>71 | P23<br>P24 | 2177         | -3072<br>-3072 | 118        | P81<br>P82 | 1101       | 3065         |

| 23<br>24                                                      | PL2<br>PL3 | -2852<br>-2852 | -461<br>-606 | 71       | P24<br>P25 | 2303<br>2460 | -3072          | 119<br>120 | P82<br>P83 | 976<br>851 | 3065<br>3065 |

| 24                                                            | PL3<br>PL4 | -2852          | -732         | 72       | P25        | 2460         | -2279          | 120        | P84        | 726        | 3065         |

| 26                                                            | PL5        | -2852          | -857         | 74       | P27        | 2848         | -2138          | 121        | P85        | 600        | 3065         |

| 20                                                            | PL6        | -2852          | -982         | 75       | P30        | 2848         | -1982          | 123        | P86        | 475        | 3065         |

| 28                                                            | PL7        | -2852          | -1107        | 76       | P31        | 2848         | -1831          | 120        | P87        | 350        | 3065         |

| 29                                                            | PK0        | -2852          | -1232        | 77       | P32        | 2848         | -1687          | 125        | PC7        | 225        | 3065         |

| 30                                                            | PK1        | -2852          | -1357        | 78       | P33        | 2848         | -1562          | 126        | PF0        | 100        | 3065         |

| 31                                                            | PK2        | -2852          | -1482        | 79       | P34        | 2848         | -1437          | 127        | PF1        | -24        | 3065         |

| 32                                                            | PK3        | -2852          | -1608        | 80       | P35        | 2848         | -1311          | 128        | PF2        | -150       | 3065         |

| 33                                                            | PM2        | -2852          | -1892        | 81       | DVSS3      | 2848         | -1186          | 129        | PC0        | -275       | 3065         |

| 34                                                            | PM1        | -2852          | -2017        | 82       | P36        | 2848         | -1061          | 130        | PC1        | -400       | 3065         |

| 35                                                            | XT1        | -2852          | -2142        | 83       | P37        | 2848         | -936           | 131        | PF7        | -525       | 3065         |

| 36                                                            | XT2        | -2852          | -2444        | 84       | P40        | 2848         | -811           | 132        | PJ0        | -650       | 3065         |

| 37                                                            | DVCC4      | -2465          | -3072        | 85       | P41        | 2848         | -686           | 133        | PJ1        | -775       | 3065         |

| 38                                                            |            |                |              | 86       | P42        |              |                |            |            |            |              |

|                                                               | TEST       | -2339          | -3072        |          |            | 2848         | -560           | 134        | PJ2        | -901       | 3065         |

| 39                                                            | D+         | -2062          | -3072        | 87       | P43        | 2848         | -435           | 135        | PJ3        | -1026      | 3065         |

| 40                                                            | D-         | -1875          | -3072        | 88       | P44        | 2848         | -310           | 136        | PJ4        | -1151      | 3065         |

| 41                                                            | DVCC1      | -1598          | -3072        | 89       | P45        | 2848         | -185           | 137        | PJ5        | -1276      | 3065         |

| 42                                                            | X1         | -1472          | -3072        | 90       | P46        | 2848         | -60            | 138        | PJ6        | -1401      | 3065         |

| 43                                                            | DVSS1      | -1347          | -3072        | 91       | P47        | 2848         | 65             | 139        | PJ7        | -1526      | 3065         |

| 44                                                            | X2         | -1126          | -3072        | 92       | P50        | 2848         | 190            | 140        | PA0        | -1652      | 3065         |

| 45                                                            | AM0        | -1001          | -3072        | 93       | P51        | 2848         | 315            |            | PA1        | -1777      |              |

| 40                                                            | AM0<br>AM1 |                |              | 94       | P52        |              |                | 141        |            |            | 3065         |

|                                                               |            | -876           | -3072        |          |            | 2848         | 440            | 142        | PA2        | -1902      | 3065         |

| 47                                                            | RESET      | -750           | -3072        | 95       | P53        | 2848         | 565            | 143        | AVSS       | -2275      | 3065         |

| 48                                                            | PC3        | -625           | -3072        | 96       | P54        | 2848         | 690            | 144        | AVCC       | -2400      | 3065         |

## 2.3 Pin Names and Functions

#### The following table shows the names and functions of the input/output pins

## Table 2.3.1 Pin Names and Functions (1/5)

| Pin Name   | Number of<br>Pins | I/O    | Function                                                                         |

|------------|-------------------|--------|----------------------------------------------------------------------------------|

| D0 to D7   | 8                 | I/O    | Data: Data bus 0 to 7                                                            |

| P10 to P17 | 0                 | I/O    | Port 1: I/O port input or output specifiable in units of bits                    |

| D8 to D15  | 8                 | I/O    | Data: Data bus 8 to 15                                                           |

| P20 to P27 |                   | I/O    | Port 2: I/O port input or output specifiable in units of bits                    |

| D16 to D23 | 8                 | I/O    | Data: Data bus 16 to 23                                                          |

| KO0 to KO7 |                   | Output | Key output 0 to 7: Pins used of key-scan strobe (Open-drain output programmable) |

| P30 to P37 |                   | I/O    | Port 3: I/O port input or output specifiable in units of bits                    |

| D24 to D31 | 8                 | I/O    | Data24: Data bus 24 to 31                                                        |

| P40 to P47 |                   | Output | Port 4: Output port                                                              |

| A0 to A7   | 8                 | Output | Address: Address bus 0 to 7                                                      |

| P50 to P57 |                   | Output | Port 5: Output port                                                              |

| A8 to A15  | 8                 | Output | Address: Address bus 8 to 15                                                     |

| P60 to P67 |                   | I/O    | Port 6: I/O port input or output specifiable in units of bits                    |

| A16 to A23 | 8                 | Output | Address: Address bus 16 to 23                                                    |

| P70        |                   | Output | Port70: Output port                                                              |

| RD         | 1                 | Output | Read: Outputs strobe signal to read external memory                              |

| P71        |                   | I/O    | Port 71: I/O port                                                                |

| WRLL       | 1                 | Output | Write: Output strobe signal for writing data on pins D0 to D7                    |

| NDRE       |                   | Output | NAND flash read: Outputs strobe signal to read external NAND flash               |

| P72        |                   | I/O    | Port 72: I/O port                                                                |

| WRLU       | 1                 | Output | Write: Output strobe signal for writing data on pins D8 to D15                   |

| NDWE       |                   | Output | Write Enable for NAND flash                                                      |

| P73        | 1                 | Output | Port 73: Output port                                                             |

| EA24       | 1                 | Output | Extended Address 24                                                              |

| P74        |                   | Output | Port 74: Output port                                                             |

| EA25       | 1                 | Output | Extended Address 25                                                              |

| P75        |                   | I/O    | Port 75: I/O port                                                                |

| R/W        | 1                 | Output | Read/Write: 1 represents read or dummy cycle; 0 represents write cycle           |

| NDR/B      |                   | Input  | NAND flash ready (1)/Busy (0) input                                              |

| P76        | 1                 | I/O    | Port 76: I/O port                                                                |

| WAIT       | 1                 | Input  | Wait: Signal used to request CPU bus wait                                        |

| TOSHIBA |

|---------|

|---------|

| Pin Name     | Number of<br>Pins | I/O           | Function                                                                            |

|--------------|-------------------|---------------|-------------------------------------------------------------------------------------|

| P80          | 1                 | Output        | Port80: Output port                                                                 |

| <u>CS0</u>   |                   | Output        | Chip select 0: Outputs "low" when address is within specified address area          |

| P81          | 1                 | Output        | Port81: Output port                                                                 |

| CS1          |                   | Output        | Chip select 1: Outputs "low" when address is within specified address area          |

| SDCS         |                   | Output        | Chip select for SDRAM: Outputs "0" when address is within SDRAM address area        |

| P82          | 1                 | Output        | Port82: Output port                                                                 |

| CS2          |                   | Output        | Chip select 2: Outputs "Low" when address is within specified address area          |

| CSZA         |                   | Output        | Expand chip select: ZA: Outputs "0" when address is within specified address area   |

| SDCS         |                   | Output        | Chip select for SDRAM: Outputs "0" when address is within SDRAM address area        |

| P83          | 1                 | Output        | Port83: Output port                                                                 |

| CS3          |                   | Output        | Chip select 3: Outputs "low" when address is within specified address area          |

| P84          | 1                 | Output        | Port84: Output port                                                                 |

| WRUL         |                   | Output        | Write: Output strobe signal for writing data on pins D16 to D23                     |

| CSZB         |                   | Output        | Expand chip select: ZB: Outputs "0" when address is within specified address area   |

| ND0CE        |                   | Output        | Chip select for NAND flash 0: Outputs "0" when NAND flash 0 is enabled              |

| P85          | 1                 | Output        | Port85: Output port                                                                 |

| WRUU         |                   | Output        | Write: Output strobe signal for writing data on pins D24 to D31                     |

| CSZC         |                   | Output        | Expand chip select: ZC: Outputs "0" when address is within specified address area   |

| ND1CE        |                   | Output        | Chip select for NAND flash 1: Outputs "0" when NAND flash 1 is enabled              |

| P86          | 1                 | Output        | Port86: Output port                                                                 |

| CSZD         |                   | Output        | Expand chip select: ZD: outputs "0" when address is within specified address area   |

| SRULB        |                   | Output        | Data enable for SRAM on pins D16 to D23                                             |

| P87          | 1                 | Output        | Port87: Output port                                                                 |

| CSZE         |                   | Output        | Expand chip select: ZE: Outputs "0" when address is within specified address area   |

| SRUUB        |                   | Output        | Data enable for SRAM on pins D24 to D31                                             |

| P90          | 1                 | I/O           | Port90: I/O port                                                                    |

| TXD0         |                   | Output        | Serial 0 send data: Open-drain output programmable                                  |

| I2SCKO       |                   | Output        | I <sup>2</sup> S clock output                                                       |

| P91          | 1                 | I/O           | Port91: I/O port (Schmitt-input)                                                    |

| RXD0         |                   | Input         | Serial 0 receive data                                                               |

| I2SDO        |                   | Output        | I <sup>2</sup> S data output                                                        |

| P92          | 1                 | I/O           | Port92: I/O port (Schmitt-input)                                                    |

| SCLK0        |                   | I/O           | Serial 0 clock I/O                                                                  |

| CTS0         |                   | Input         | Serial 0 data send enable (Clear to send)                                           |

| I2SWS        |                   | Output        | I <sup>2</sup> S word select output                                                 |

| P93          | 1                 | I/O           | Port93: I/O port                                                                    |

| LGOE0        |                   | Output        | Output enable-0 for external TFT-LCD driver                                         |

| P94<br>LGOE1 | 1                 | I/O<br>Output | Port94: I/O port Output enable-1 for external TFT-LCD driver                        |

| P95          | 1                 | Output        | Port95: Output port                                                                 |

| CLK32KO      |                   | Output        | Output fs (32.768 kHz) clock                                                        |

| LGOE2        |                   | Output        | Output enable-2 for external TFT-LCD driver                                         |

| P96          | 1                 | Input         | Port 96: Input port (Schmitt-input)                                                 |

| INT4         |                   | Input         | Interrupt request pin4: Interrupt request with programmable rising/falling edge     |

| PX           |                   | Output        | X-Plus: Pin connectted to X+ for touch screen panel                                 |

| P97          | 1                 | Input         | Port 97: Input port (Schmitt-input)                                                 |

| INT5         |                   | Input         | Interrupt request pin5: Interrupt request with programmable rising/falling edge     |

| PY           |                   | Output        | Y-Plus: Pin connectted to Y+ for touch screen panel                                 |

| PA0 to PA2   | 3                 | Input         | Port: A0 to A2 port: Pin used to input ports (Schmitt input, with pull-up resistor) |

| KI0 to KI2   |                   | Input         | Key input 0 to 2: Pin used for key-on wakeup 0 to 2                                 |

| PA3 to PA6   | 4                 | Input         | Port: A3 to A6 port: Pin used to input ports (Schmitt input, with pull-up resistor) |

| KI3 to KI6   |                   | Input         | Key input 3 to 6: Pin used for key-on wakeup 3 to 6                                 |

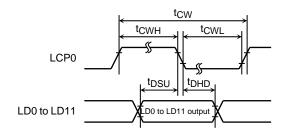

| LD8 to LD11  |                   | Output        | Data bus 8 to 11for LCD driver                                                      |

| PA7          | 1                 | Input         | Port: A7 port: Pin used to input ports (Schmitt input, with pull-up resistor)       |

| KI7          |                   | Input         | Key input 7: Pin used for key-on wakeup 7                                           |

## Table 2.3.2 Pin Names and Functions (2/5)

www.DataSheet4U.com

Table 2.3.3 Pin Names and Functions (3/5)

| Pin Name   | Number of<br>Pins | I/O    | Function                                                                                   |

|------------|-------------------|--------|--------------------------------------------------------------------------------------------|

| PC0        |                   | I/O    | Port C0: I/O port (Schmitt-input)                                                          |

| INT0       | 1                 | Input  | Interrupt request pin 0: Interrupt request pin with programmable level/rising/falling edge |

| TA1OUT     |                   | Output | 8-bit timer 1 output: Timer 1 output                                                       |

| PC1        |                   | I/O    | Port C1: I/O port (Schmitt-input)                                                          |

| INT1       | 1                 | Input  | Interrupt request pin 1: Interrupt request pin with programmable rising/falling edge       |

| TA3OUT     |                   | Output | 8-bit timer 3 output: Timer 3 output                                                       |

| PC2        |                   | I/O    | Port C2: I/O port (Schmitt-input)                                                          |

| INT2       | 1                 | Input  | Interrupt request pin 2: Interrupt request pin with programmable rising/falling edge       |

| TB0OUT0    |                   | Output | Timer B0 output                                                                            |

| PC3        | 1                 | I/O    | Port C3: I/O port (Schmitt-input)                                                          |

| INT3       | . I               | Input  | Interrupt request pin 3: Interrupt request pin with programmable rising/falling edge       |

| PC6        |                   | I/O    | Port C6: I/O port                                                                          |

| KO8        | 1                 | Output | Key Output 8: Pin used of key-scan strobe (Open-drain output programmable)                 |

| LDIV       |                   | Output | Data invert enable for external TFT-LCD driver                                             |

| PC7        |                   | I/O    | Port C7: I/O port                                                                          |

| CSZF       | 1                 | Output | Expand chip select: ZF: Outputs "0" when address is within specified address area          |

| LCP1       |                   | Output | Shift-clock-1 for external TFT-LCD driver                                                  |

| PF0        |                   | I/O    | Port F0: I/O port (Schmitt-input)                                                          |

| TXD0       | 1                 | Output | Serial 0 send data: Open-drain output programmable                                         |

| TXD1       |                   | Output | Serial 1 send data: Open-drain output programmable                                         |

| PF1        |                   | I/O    | Port F1: I/O port (Schmitt-input)                                                          |

| RXD0       | 1                 | Input  | Serial 0 receive data                                                                      |

| RXD1       |                   | Input  | Serial 1 receive data                                                                      |

| PF2        |                   | I/O    | Port F2: I/O port (Schmitt-input)                                                          |

| SCLK0      |                   | I/O    | Serial 0 clock I/O                                                                         |

| CTS0       | 1                 | Input  | Serial 0 data send enable (Clear to send)                                                  |

| SCLK1      |                   | I/O    | Serial 1 clock I/O                                                                         |

| CTS1       |                   | Input  | Serial 1 data send enable (Clear to send)                                                  |

| PF7        | 1                 | Output | Port F7: Output port                                                                       |

| SDCLK      |                   | Output | Clock for SDRAM (When SDRAM is not used, SDCLK can be used as system clock)                |

| PG0 to PG1 | 2                 | Input  | Port G0 to G1 port: Pin used to input ports                                                |

| AN0 to AN1 | 2                 | Input  | Analog input 0 to 1: Pin used to Input to AD conveter                                      |

| PG2        |                   | Input  | Port G2 port: Pin used to input ports                                                      |

| AN2        | 1                 | Input  | Analog input 2: Pin used to Input to AD conveter                                           |

| MX         |                   | Output | X-Minus: Pin connectted to X– for touch screen panel                                       |

| PG3        |                   | Input  | Port G3 port: Pin used to input ports                                                      |

| AN3        | 1                 | Input  | Analog input 3: Pin used to input to AD conveter                                           |

| MY         | I                 | Output | Y-Minus: Pin connectted to Y- for touch screen panel                                       |

| ADTRG      |                   | Intput | AD trigger: Signal used to request AD start                                                |

| Pin Name   | Number of<br>Pins | I/O    | Function                                       |

|------------|-------------------|--------|------------------------------------------------|

| PJ0        |                   | Output | Port J0: Output port                           |

| SDRAS      | 1                 | Output | Row address strobe for SDRAM                   |

| SRLLB      |                   | Output | Data enable for SRAM on pins D0 to D7          |

| PJ1        |                   | Output | Port J1: Output port                           |

| SDCAS      | 1                 | Output | Column address strobe for SDRAM                |

| SRLUB      |                   | Output | Data enable for SRAM on pins D8 to D15         |

| PJ2        |                   | Output | Port J2: Output port                           |

| SDWE       | 1                 | Output | Write enable for SDRAM                         |

| SRWR       |                   | Output | Write for SRAM: Strobe signal for writing data |

| PJ3        | 1                 | Output | Port J3: Output port                           |

| SDLLDQM    | I                 | Output | Data enable for SDRAM on pins D0 to D7         |

| PJ4        | 1                 | Output | Port J4: Output port                           |

| SDLUDQM    | I                 | Output | Data enable for SDRAM on pins D8 to D15        |

| PJ5        |                   | I/O    | Port J5: I/O port                              |

| SDULDQM    | 1                 | Output | Data enable for SDRAM on pins D16 to D23       |

| NDALE      |                   | Output | Address latch enable for NAND flash            |

| PJ6        |                   | I/O    | Port J6: I/O port                              |

| SDUUDQM    | 1                 | Output | Data enable for SDRAM on pins D24 to D31       |

| NDCLE      |                   | Output | Command latch enable for NAND flash            |

| PJ7        | 1                 | Output | Port J7: Output port                           |

| SDCKE      | I                 | Output | Clock enable for SDRAM                         |

| PK0        | 1                 | Output | Port K0: Output port                           |

| LCP0       | Ι                 | Output | LCD driver output pin                          |

| PK1        | 1                 | Output | Port K1: Output port                           |

| LLP        | Ι                 | Output | LCD driver output pin                          |

| PK2        | 1                 | Output | Port K2: Output port                           |

| LFR        | Ι                 | Output | LCD driver output pin                          |

| PK3        | 1                 | Output | Port K3: Output port                           |

| LBCD       | 1                 | Output | LCD driver output pin                          |

| PL0 to PL3 | 4                 | Output | Port L0 to L3: Output port                     |

| LD0 to LD3 | 4                 | Output | Data bus for LCD driver                        |

| PL4 to PL7 | 4                 | I/O    | Port L4 to L7: I/O port                        |

| LD4 to LD7 | 4                 | Output | Data bus for LCD driver                        |

| TEST       | 1                 | Input  | Connect to VCC.                                |

| PM1        | 1                 | Output | Port M1: Output port                           |

| MLDALM     | I                 | Output | Melody/alarm output pin                        |

| PM2        |                   | Output | Port M2: Output port                           |

| ALARM      | 1                 | Output | RTC alarm output pin                           |

| MLDALM     |                   | Output | Melody/alarm output pin (inverted)             |

| Table 2.3.4 Pin Names and Functions (4/5 | ) |

|------------------------------------------|---|

|------------------------------------------|---|

Note: The output functions SDULDQM, NDALE of PJ5-pin and SDUUDQM, NDCLE of PJ6-pin cannot be used simultaneously. Therefore, 32-bit SDRAM and NAND-Flash cannot be used at the same time.

| Pin Name | Number of<br>Pins | I/O   | Function                                                                                                                                                                                                                |

|----------|-------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

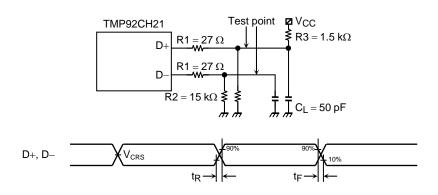

| D+, D-   | 2                 | I/O   | USB-data connecting pin<br>Connect pull-up resistor to both pins to avoid through current when USB is not in use.                                                                                                       |

| AMO, AM1 | 2                 | Input | Operation mode:<br>Fix to AM1 = "0", AM0 = "1" for 16-bit external bus starting<br>Fix to AM1 = "1", AM0 = "0" for 32-bit external bus starting<br>Fix to AM1 = "1", AM0 = "1" for BOOT (32-bit internal MROM) starting |

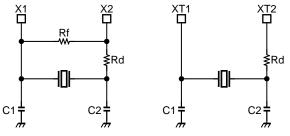

| X1/X2    | 2                 | I/O   | High-frequency oscillator connection pins                                                                                                                                                                               |

| XT1/XT2  | 2                 | I/O   | Low-frequency oscillator connection pins                                                                                                                                                                                |

| RESET    | 1                 | Input | Reset: Initializes TMP92CH21 (with pull-up resistor, Schmitt input)                                                                                                                                                     |

| VREFH    | 1                 | Input | Pin for reference voltage input to AD converter (H)                                                                                                                                                                     |

| VREFL    | 1                 | Input | Pin for reference voltage input to AD converter (L)                                                                                                                                                                     |

| AVCC     | 1                 | -     | Power supply pin for AD converter                                                                                                                                                                                       |

| AVSS     | 1                 | _     | GND pin for AD converter (0 V)                                                                                                                                                                                          |

| DVCC     | 4                 | _     | Power supply pins (All $V_{\mbox{CC}}$ pins should be connected to the power supply pin)                                                                                                                                |

| DVSS     | 3                 | _     | GND pins (0 V) (All pins should be connected to GND (0 V))                                                                                                                                                              |

#### Table 2.3.5 Pin Names and Functions (5/5)

Note: Use a 9.0 MHz oscillator at pins X1/X2 when USB is used.

## 3. Operation

This section describes the basic components, functions and operation of the TMP92CH21.

## 3.1 CPU

The TMP92CH21 contains an advanced high-speed 32-bit CPU (TLCS-900/H1 CPU)

## 3.1.1 CPU Outline

The TLCS-900/H1 CPU is a high-speed, high-performance CPU based on the TLCS-900/L1 CPU. The TLCS-900/H1 CPU has an expanded 32-bit internal data bus to process instructions more quickly.

The following is an outline of the CPU:

| Parameter                              | TMP92CH21                                          |

|----------------------------------------|----------------------------------------------------|

| Width of CPU address bus               | 24 bits                                            |

| Width of CPU data bus                  | 32 bits                                            |

| Internal operating frequency           | Max 20 MHz                                         |

| Minimum bus cycle                      | 1-clock access (50 ns at f <sub>SYS</sub> = 20MHz) |

| Internal RAM                           | 32-bit 1-clock access                              |

| Internal boot ROM                      | 32-bit 2-clock access                              |

|                                        | 8- or 16-bit 2-clock access or                     |

| Internal I/O                           | 8- or 16-bit 5 to 6-clock access                   |

| External SPAM Masked POM               | 8- or 16- or 32-bit 2-clock access                 |

| External SRAM, Masked ROM              | (waits can be inserted)                            |

| External SDRAM                         | 16- or 32-bit min. 1-clock access                  |

|                                        | 8-bit min. 4-clock access                          |

| External NAND flash                    | (waits can be inserted)                            |

| Minimum instruction<br>execution cycle | 1-clock (50 ns at f <sub>SYS</sub> =20MHz)         |

| Conditional jump                       | 2-clock (100 ns at f <sub>SYS</sub> =20MHz)        |

| Instruction queue buffer               | 12 bytes                                           |

|                                        | Compatible with TLCS-900/L1                        |

| Instruction set                        | (LDX instruction is deleted)                       |

| CPU mode                               | Maximum mode only                                  |

| Micro DMA                              | 8 channels                                         |

| Table 3.1.1 | TMP92CH21 | Outline |

|-------------|-----------|---------|

|-------------|-----------|---------|

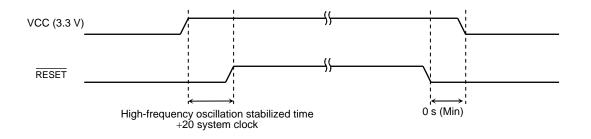

## 3.1.2 Reset Operation

When resetting the TMP92CH21, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input low for at least 20 system clocks (16 µs at fc = 40 MHz).

At reset, since the clock doubler (PLL) is bypassed and the clock-gear is set to 1/16, the system clock operates at 1.25 MHz (fc = 40 MHz).

When the reset has been accepted, the CPU performs the following:

• Sets the program counter (PC) as follows in accordance with the reset vector stored at address FFFF00H to FFFF02H:

| PC<7:0>   | $\leftarrow$ data in location FFFF00H |

|-----------|---------------------------------------|

| PC<15:8>  | $\leftarrow$ data in location FFFF01H |

| PC<23:16> | $\leftarrow$ data in location FFFF02H |

- Sets the stack pointer (XSP) to 00000000H.

- Sets bits <IFF2:0> of the status register (SR) to 111 (thereby setting the interrupt level mask register to level 7).

- Clears bits <RFP1:0> of the status register to 00 (there by selecting register bank 0).

When the reset is released, the CPU starts executing instructions according to the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports and other pins as follows.

- Initializes the internal I/O registers as shown in the "Special Function Register" table in section 5.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose input or output port mode.

Internal reset is released as soon as external reset is released.

Memory controller operation cannot be ensured until the power supply becomes stable after power-on reset. External RAM data provided before turning on the TMP92CH21 may be corrupted because the control signals are unstable until the power supply becomes stable after power on reset.

Figure 3.1.1 Power on Reset Timing Example

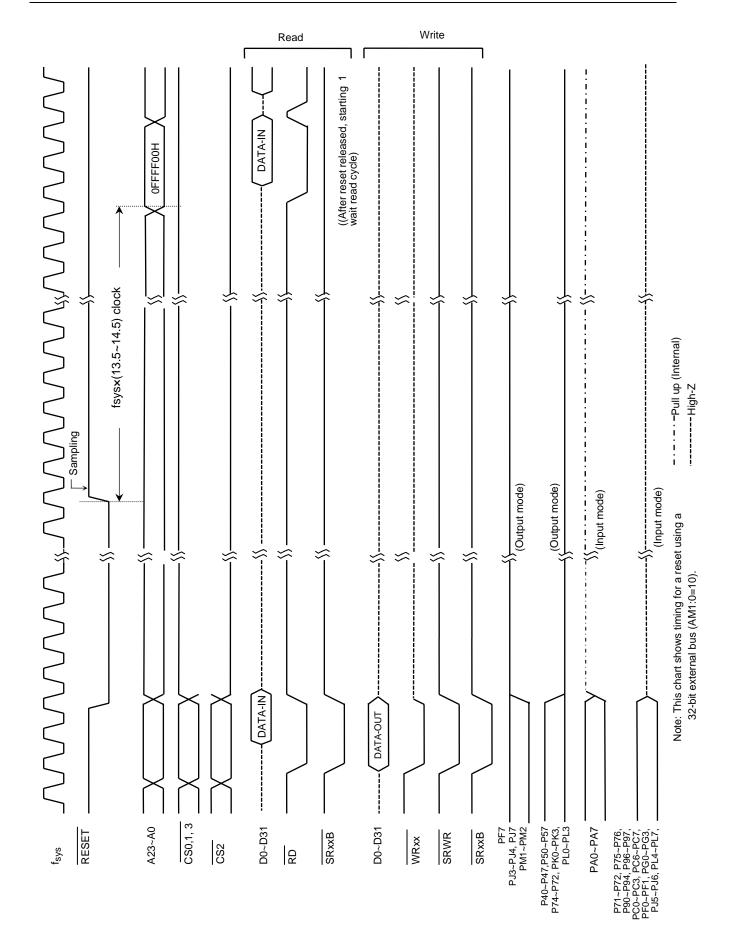

## Figure 3.1.2 TMP92CH21 Reset Timing Chart

www.DataSheet4U.com

## 3.1.3 Setting of AM0 and AM1

Set AM1 and AM0 pins as shown in Table 3.1.2 according to system usage.

| Operation Mode                                      | Mode Setup Input Pin |     |     |  |

|-----------------------------------------------------|----------------------|-----|-----|--|

| Operation mode                                      | RESET                | AM1 | AM0 |  |

| 16-bit external bus starting<br>(MULTI 16 mode)     |                      | 0   | 1   |  |

| 32-bit external bus starting<br>(MULTI 32 mode)     |                      | 1   | 0   |  |

| Boot (32-bit internal MROM) starting<br>(BOOT mode) |                      | 1   | 1   |  |

Table 3.1.2 Operation Mode Setup Table

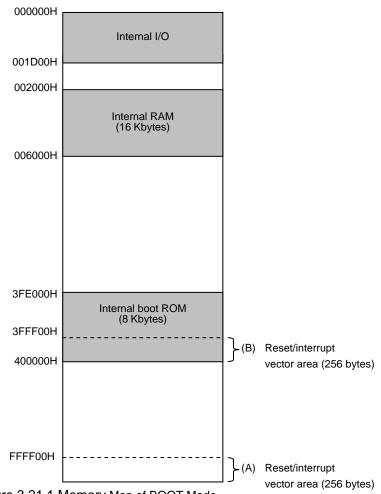

## 3.2 Memory Map

000000H ſ Internal I/O Direct area (n) (8 Kbytes) 000100H 001D00H 002000H 64-Kbyte area (nn) Internal RAM (16 Kbytes) 006000H 010000H 3FE000H Boot (Internal MROM) (Note 1) (8 Kbytes) 400000H External memory F00000H Provisional emulator control (64 Kbytes) (Note 2) 16-Mbyte area F10000H (R) (-R) (R+) (R + R8/16) (R + d8/16) External memory (nnn) FFFF00H .(Note 3) Vector table (256 bytes) FFFFFFH = Internal area) (

Figure 3.2.1 is a memory map of the TMP92CH21.

Figure 3.2.1 Memory Map

- Note 1: Boot program (Internal MROM) is mapped only for BOOT mode. For other starting modes, its area (3FE000H to 3FFFFFH) is mapped to external-memory.

- Note 2: The Provisional emulator control area, mapped F00000H to F0FFFH after reset, is for emulator use and so is not available. When emulator  $\overline{WR}$  signal and  $\overline{RD}$  signal are asserted, this area is accessed. Ensure external memory is used.

- Note 3: Do not use the last 16-byte area (FFFF0H to FFFFFFH). This area is reserved for an emulator.

#### 3.21.2 Hardware Specification for Internal Boot ROM

### (1) Memory map

Figure 3.21.1 shows a memory map of BOOT mode.

An 8-Kbyte ROM is built-in and it is mapped to address 3FE000H to 3FFFFFH.

In MULTI mode, the boot ROM is not mapped and its area is mapped as an external area.

Figure 3.21.1 Memory Map of BOOT Mode

(2) Reset/interrupt address conversion circuit

A reset/interrupt vector address conversion circuit is included.

This function allows for individual reset/interrupt vector areas. For details, refer to section 3.6.5, Internal Boot ROM Control.

(3) Clearing boot ROM

After boot sequence in BOOT mode, the application system program may continue to run without reset asserting. In this case, any external memory which is mapped to address 3FE000H to 3FFFFFH cannot be accessed because the boot ROM is assigned here.

So, an internal boot ROM can be cleared by setting BROMCR<ROMLESS> to "1". For the details, refer to section 3.6.5, Internal Boot ROM Control.

www.DataSheet4U.com

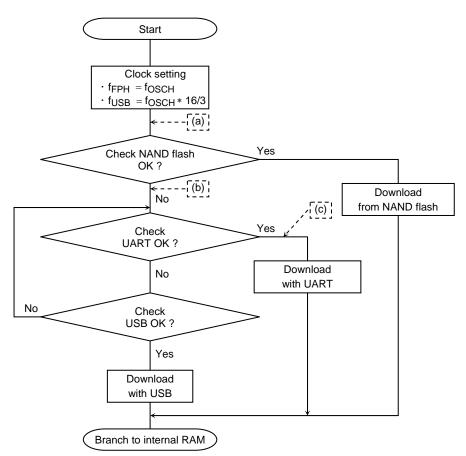

## 3.21.3 Outline of Boot Operation

There are 3 downloading methods: NAND flash, UART and USB.

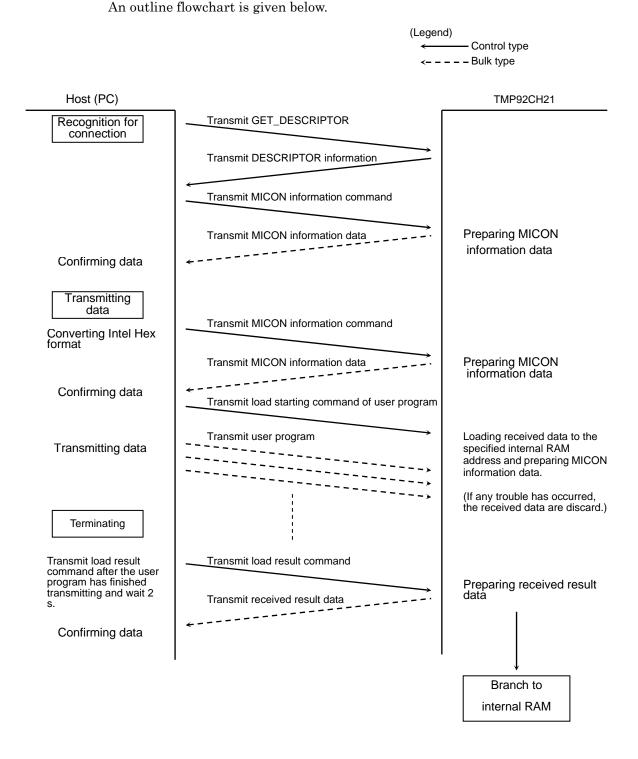

After reset, a boot program in the boot ROM operates as shown in the Figure 3.21.2 flow chart.

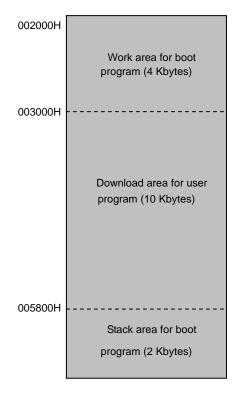

Internal RAM use is the same regardless of downloading method, and is shown in Figure 3.21.3.

- Note 1: When USB downloading is used, a special USB device driver and application software are needed on the PC.

- Note 2: When UART downloading is used, special application software is needed on the PC.

- Note 3: (a), (b) and (c) on the flow chart show the points at which external port pins are set. Refer to Table 3.21.3 for details.

Figure 3.21.2 Flow Chart Outline of Internal Boot ROM

Figure 3.21.3 Internal RAM Use

www.DataSheet4U.com

## (1) Port setting

The boot program port settings are shown in Table 3.21.3, and Table 3.21.4 shows PCB design. These port settings must be carefully noted when designing an application system.

The remaining ports are not set, so they maintain their status after reset.

|       |     |              |        | 5                                          |                            |                            |                    |

|-------|-----|--------------|--------|--------------------------------------------|----------------------------|----------------------------|--------------------|

| Port  |     | Function     | I/O    | Po                                         | ort Setting by Boot Progra | m                          |                    |

|       |     | Function     | 1/0    | (a)                                        | (b)                        | (c)                        |                    |

| NAND  | P71 | NDRE         | Output |                                            |                            |                            |                    |

| flash | P72 | NDWE         | Output |                                            |                            |                            |                    |

|       | P75 | NDR/B        | Input  | Set to the function pin shown              | No change from (a)         | No obongo from (o)         |                    |

|       | P84 | <b>ND0CE</b> | Output | left                                       | left No change nom (a)     | No change nom (a)          | No change from (a) |

|       | PJ5 | NDALE        | Output |                                            |                            |                            |                    |

|       | PJ6 | NDCLE        | Output |                                            |                            |                            |                    |

|       | -   | D7 to D0     | I/O    | No change                                  |                            |                            |                    |

| UART  | PF0 | TXD1         | Output | No change to input port status after reset | No change from (a)         | Set to the TXD1 output pin |                    |

|       | PF1 | RXD1         | Input  | Set to the RXD1 input pin                  |                            | No change from (a)         |                    |

| USB   | -   | D +          | I/O    | No change                                  |                            |                            |                    |

|       | -   | D –          | I/O    |                                            |                            |                            |                    |

|       | PC6 | PUCTL        | Output | No change to input port status after reset | Set to the output port pin | No change from (b)         |                    |

Table 3.21.3 Port Setting

| Port          |            | Function     | I/O              | Boot Method                                                                                                                        |                                                                                                    |                                                                                                                                                                             |

|---------------|------------|--------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |            | FUNCTION     | 1/0              | NAND flash                                                                                                                         | UART                                                                                               | USB                                                                                                                                                                         |

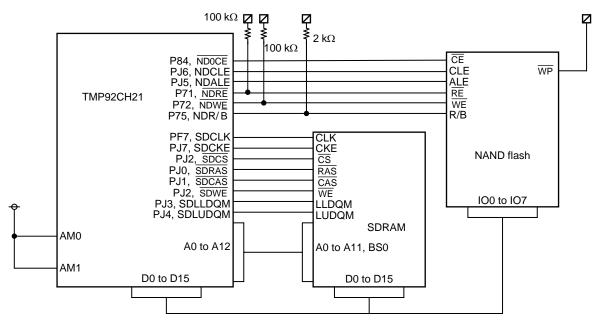

| NAND<br>flash | P71<br>P72 | NDRE<br>NDWE | Output<br>Output | Connect to NAND flash and pull-up by 100 k $\Omega$ resistor because this pin is changed to input port by reset.                   | If the NAND flash is not used in<br>the system, ensure no conflict<br>with the I/O direction shown | Not affected by USB boot.<br>If the NAND flash is not used<br>in the system, ensure no<br>conflict with the I/O direction<br>shown left.                                    |

|               | P75        | NDR/B        | Input            | Connect to NAND flash and<br>pull-up by 2 k $\Omega$ resistor<br>because R/B pin of NAND<br>flash has open-drain output<br>buffer. |                                                                                                    |                                                                                                                                                                             |

|               | P84        | ND0CE        | Output           | Connect to NAND flash.                                                                                                             |                                                                                                    |                                                                                                                                                                             |

|               | PJ5        | NDALE        | Output           |                                                                                                                                    |                                                                                                    |                                                                                                                                                                             |

|               | PJ6        | NDCLE        | Output           |                                                                                                                                    |                                                                                                    |                                                                                                                                                                             |

|               | -          | D7 to D0     | I/O              |                                                                                                                                    |                                                                                                    |                                                                                                                                                                             |

| UART          | PF0        | TXD1         | Output           | Not affected by NAND flash                                                                                                         | Connect to level shifter.                                                                          | Not affected by USB boot.                                                                                                                                                   |

|               | PF1        | RXD1         | Input            | boot.                                                                                                                              |                                                                                                    | Pull-up by 100 k $\Omega$ to avoid UART executing.                                                                                                                          |

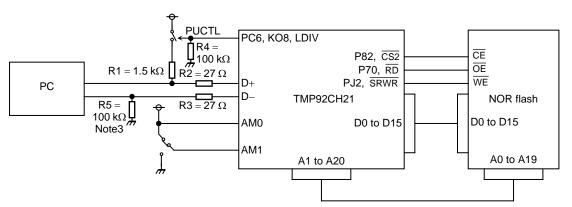

| USB           | _          | D +          | I/O              | Not affected NAND flash boot.                                                                                                      | Not affected by UART boot.                                                                         | Connect to USB connector,<br>add dumping resistor (27 $\Omega$ )<br>and 1.5 k $\Omega$ pull-up which can<br>be switched ON/OFF.                                             |

|               | _          | D –          | I/O              |                                                                                                                                    |                                                                                                    | Connect to USB connector<br>and add dumping resistor<br>(27Ω).                                                                                                              |

|               | PC6        | PUCTL        | Output           |                                                                                                                                    |                                                                                                    | Used to control ON/OFF<br>pull-up resistor of D + pin. The<br>switch should be ON by "1".<br>As this pin changes to input<br>port by reset, add100 k $\Omega$<br>pull-down. |

| Table 3.21.4 How to Design PC | B |

|-------------------------------|---|

|                               |   |

Note 1: When booting method is either NAND flash or UART and USB is used in the system, ensure the D + pin pull-up resistor is not on in the BOOT mode.

Note 2: When booting method is USB, do not start UART application software on the PC.

Note 3: When booting method is UART, do not connect the USB connector.

(2) I/O registers setting by boot program

Table 3.21.5 shows I/O register setting by boot program.

Take particular note of these set values when using an application system program which continues to run without asserting a reset after a boot sequence is executed .

Also take note of the status of the CPU registers and internal RAM following execution of a boot sequence.

| Symbol   | Set Value | Set Content                                        |  |

|----------|-----------|----------------------------------------------------|--|

| WDMOD    | 00H       | Stop watchdog timer.                               |  |

| WDCR     | B1H       | Disable watchdog timer.                            |  |

| SYSCR0   | 80H       | Set system clock.                                  |  |

| SYSCR1   | 00H       | Set system clock.                                  |  |

| SYSCR2   | 2CH       | Set system clock.                                  |  |

| PLLCR0   | 40H       | Where USB is used for boot, set to use PLL         |  |

|          |           | output clock for f <sub>FPH</sub> .                |  |

|          | 00H       | Where USB is not used for boot, set not to use PLL |  |

|          |           | output clock for f <sub>FPH</sub> .                |  |

| PLLCR1   | 80H       | Set to PLL ON. Not affected by boot method.        |  |

| INTEUSB  | 04H       | Set USB interrupt level.                           |  |

| INTETC01 | 44H       | Set INTTC interrupt level.                         |  |

Table 3.21.5 I/O Register Setting by Boot Program

Note: The setting values for NAND flash, UART and USB are not shown. Set each register where these functions are used in the system.

## 3.21.4 Download from NAND flash

#### (1) Connection example

Figure 3.21.4 shows an example of NAND flash. (A 16-bit SDRAM is used as program memory).

Note 1: The values of the pull-up resistors are recommended values.

Note 2: The WP (Write protect) pin of NAND flash is not supported by the TMP92CH21. If necessary, it must be prepared on an external circuit.

## Figure 3.21.4 Example of NAND Flash Connection

(2) Supported NAND flash

The boot program is designed based on SmartMedia<sup>™</sup> physical format specification Ver1.20. Table 3.21.6 shows supported memory devices and device codes.

| Memory Size [Mbyte] | NAND Flash<br>3.3 V Model | Masked ROM<br>3.3 V Model |

|---------------------|---------------------------|---------------------------|

| 1<br>2              | Not su                    | pported                   |

| 4                   | OK (E3H)                  | OK (D5H)                  |

| 8                   | OK (E6H)                  | OK (D6H)                  |

| 16                  | OK (73H)                  | OK (57H)                  |

| 32                  | OK (75H)                  | OK (58H)                  |

| 64                  | OK (76H)                  | OK (D9H)                  |

| 128                 | OK (79H)                  | OK (DAH)                  |

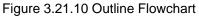

#### (3) Data format

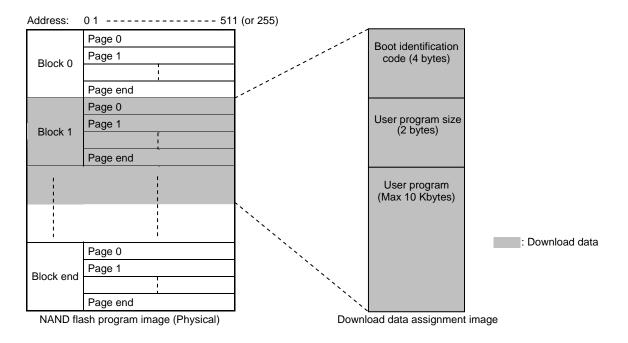

The download data consists of the boot identification code (4 bytes), user program size (2 bytes) and user program (max 10 Kbytes). These should be assigned (programmed) to NAND flash as shown in Figure 3.21.5. Also program the ECC code in the redundant area of the NAND flash, the block status area and thedata status area.

Figure 3.21.5 Download Data Image

a) Boot identification code (4 bytes)

The boot program initially checks the boot identification code. If the boot characters in ASCII code are read from the first 4 bytes in page 0, block 1 of the NAND flash, the boot program will recognize the boot method as NAND flash.

| 42H ("B") |

|-----------|

| 4FH ("O") |

| 4FH ("O") |

| 54H ("T") |

Figure 3.21.6 Boot Identification Code

b) User program size (2 bytes)

The program size should be programmed to the next 2 bytes. The first byte is the lower 8 bits and the second is the upper 8 bits. This size indicates only the user program size; it does not include the boot identification code (4 bytes) and user program size (2 bytes).

This must be less than or equal to 10 Kbytes. So, the maximum number is 2800H.

| Size (Lower 8 bits) |

|---------------------|

| Size (Upper 8 bits) |

Figure 3.21.7 User Program Size

2006-09-15

DataSheet4U.com

c) User program (max 10 Kbytes)

This refers to a user program that is loaded to internal RAM.

When creating a user program, note the following points.

• Set start address to 3000H

Beforehand, program (write) the user program to NAND flash in binary format.

An example explaining how to make a binary format file is given below.

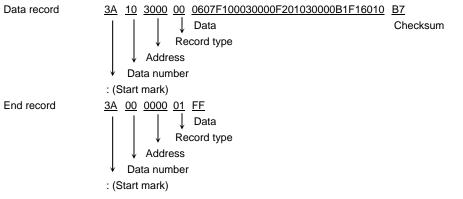

Example: How to convert from Intel Hex format file to binary format file

- The following is an example of display in text editor when an Intel Hex format file is opened. : 10300000607F100030000F201030000B1F16010B7

- :0000001FF

- In fact, their data are as below because ASCII code is used for Intel Hex format files. 3A313033303030303030363037463130303030303030304632303130333030303 423146313630313042370D0A3A30303030303030303146460D0A

So, first convert the above data to binary format using the table below.

| Before (ASCII) | After (Binary)                        |

|----------------|---------------------------------------|

| ЗA             | 3A (Only 3A should not be converted.) |

| 30 to 39       | 0 to 9                                |

| 41 or 61       | A                                     |

| 42 or 62       | В                                     |

| 43 or 63       | С                                     |

| 44 or 64       | D                                     |

| 45 or 65       | E                                     |

| 46 or 66       | F                                     |

| 0D0A           | Delete                                |

Next, delete characters other than data

(Start mark, data number, address, record type and checksum).

The Intel Hex format and its meaning are given below.

#### (4) Error check item

The items checked by the boot program are given below.

If an error occurs in any check, the boot program will cancel downloading from NAND flash and skip to the next operation (recognizing UART or USB).

a) Supported NAND flash

The boot program reads a device code from NAND flash and checks whether it is supported or not.

- b) Boot identification code

- c) User program size

The boot program checks whether it is less than or equal to 10 Kbytes.

d) Block status area

The boot program checks whether each block is normal or not. If the block status area on first page of any block has 2-bit or more "0" data, it is an error.

e) Data status area

The boot program checks whether each data status is correct or not. If the data status area has 4-bit or more "0" data, it is an error.

f) ECC error

The boot program reads both calculated code from NDFC and ECC code in NAND flash and checks whether they are correctable or not.

g) NAND flash R/B

The boot program checks whether NDR/B pin is normal or not in each action.

If the busy status is longer than 70  $[\mu s]$  at fFPH = 40 MHz, it is an error.

#### (5) ECC error check

a) Calculation ECC code

The NDFC (NAND flash controller) is used for calculation of ECC code.

b) ECC code correction

The boot program operates as below.

- 1. Compares both calculated ECC code from NDFC and ECC code in NAND flash.

- 2. Evaluates and corrects according to the following cases.

| Case (a): No data error               | $\rightarrow$ (OK) Next operation   |

|---------------------------------------|-------------------------------------|

| Case (b): 1-bit data error            | $\rightarrow$ (OK) Error correction |

|                                       | and next operation                  |

| Case (c): 2-bit or more data error    | $\rightarrow$ (Error) Termination   |

| Case (d): ECC code 1-bit error        | $\rightarrow$ (OK) Next operation   |

| Case (e): ECC code 2-bit or more erro | $r \rightarrow$ (Error) Termination |

For reference, details of calculation flow are given below.

1) Make XOR data by calculating exclusive OR after both ECC code from NDFC and NAND flash are placed to 4-byte data as below.

Lower 2 bytes: Line parity Upper 2 bytes: Column parity

(Valid data of column parity is lower 6-bit in upper 2 bytes)

- 2) If XOR data equals "0", it will terminate normally because the ECC code is the same, but if not, they are checked as to whether they are correctable or not.

- 3) If XOR data does not have 2-bit or more "1" data, it will terminate normally because of the ECC code 1-bit error.

- 4) If the effective data (2-bit width from bit0 to bit21 in XOR data) equals either 01B or 10B, it corrects data because they are correctable.

If the effective data has either 00B or 11B, it terminates abnormally because they are not correctable.

- 5) Data correcting takes error line information from line parity in XOR data and error bit information from column parity and inverts the bit.

- Example: If the XOR data equals 0026A65AH, line parity is shown below in binary. 10 10 01 10 01 01 10 10B

If 10B is converted to 1B and 01B is converted to 0B, they become 1 1 0 1 0 0 1 1B and meaning the 212th byte.

In the same manner, error bit information becomes bit5. As a result, it inverts bit5 of 212th byte.

2006-09-15

DataSheet4U.com

## 3.21.5 Download with UART

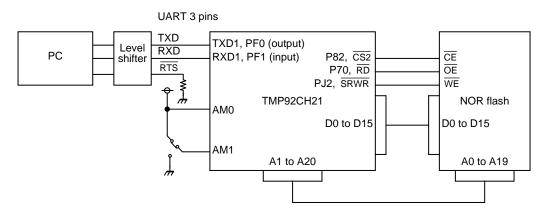

(1) Connection example

Figure 3.21.8 shows an example of UART. (A 16-bit NOR flash is used as program memory.)

Figure 3.21.8 Example of UART

(2) UART interface specification

SIO channel 1 is used to download.

The following shows the UART communication format in BOOT mode.

Before booting, the PC side must also be setup in the same way.

The default baud rate is 9600 bps, but it can be changed to other values as shown in Table 3.21.9.

| Serial transfer mode | : UART (Asynchronous communication) mode, full<br>duplex communication |

|----------------------|------------------------------------------------------------------------|

| Data length          | : 8 bits                                                               |

| Parity bit           | : None                                                                 |

| STOP bit             | : 1 bit                                                                |

| Handshake            | : None                                                                 |

| Baud rate (Default)  | : 9600 bps                                                             |

#### (3) UART data transfer format

Table 3.21.7 to Table 3.21.12 show the supported frequency, data transfer format, baud rate modification commands, operation commands, version management information, and frequency measurement result with data storing location, respectively.

Please also refer to the description of boot program operation in the following pages.

Table 3.21.7 Supported Frequency (f<sub>OSCH</sub>)

|      |      |      |       |       |       |        | 0000.0 |       |        |       |       |

|------|------|------|-------|-------|-------|--------|--------|-------|--------|-------|-------|

| 6.00 | 8.00 | 9.00 | 10.00 | 16.00 | 20.00 | 22.579 | 25.00  | 32.00 | 33.868 | 36.00 | 40.00 |

| MHz  | MHz  | MHz  | MHz   | MHz   | MHz   | MHz    | MHz    | MHz   | MHz    | MHz   | MHz   |

Note: Internal PLL (Clock multiplier) is not used.

|             | Byte Number<br>to Transfer | Transfer Data from PC to<br>TMP92CH21 | Baud Rate | Transfer Data from TMP92CH21 to<br>PC                                |

|-------------|----------------------------|---------------------------------------|-----------|----------------------------------------------------------------------|

| Boot<br>ROM | 1st byte                   | Matching data (5AH)                   | 9600 bps  | <ul> <li>– (Frequency measurement and baud rate auto set)</li> </ul> |

|             | 2nd byte                   | _                                     |           | OK: Echo back data (5AH)                                             |

|             |                            |                                       |           | Error: Nothing transmitted                                           |

|             | 3rd byte                   | -                                     |           | Version management information                                       |

|             | to                         |                                       |           | (Refer to Table 3.21.11)                                             |

|             | 6th byte                   |                                       |           |                                                                      |

|             | 7th byte                   | -                                     |           | Frequency information                                                |

|             |                            |                                       | _         | (Refer to Table 3.21.12)                                             |

|             | 8th byte                   | Baud rate modification command        |           | -                                                                    |

|             | 9th byte                   | (Refer to Table 3.21.9)               |           | OK: Echo back data                                                   |