# MOS INTEGRATED CIRCUIT $\mu PD3593$

# 2 048-BIT CCD LINEAR IMAGE SENSOR WITH PERIPHERAL CIRCUITS

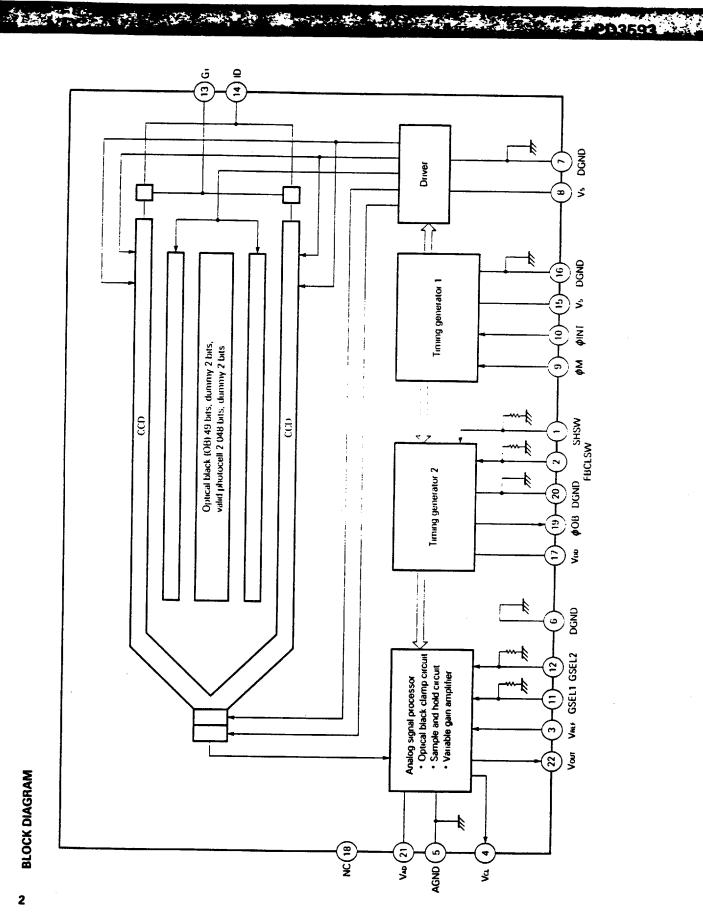

The  $\mu$ PD3593 is a 2048-bit high sensitivity CCD (Charge Coupled Device) linear image sensor which changes optical images to electrical signal.

The  $\mu$ PD3593 has an output amplifier which has wide output range, and which can switch gain. Therefore easy to get signal level which is easy to process from low illumination to high illumination, and it is easy to apply to many purposes.

With internal generation circuit of driving signal and internal driver, the µPD3593 performs only with two basic clock inputs. No special driving circuit is required. In addition, analog signal processor convert and output independent CCD register in every bit to continuous video signal. So it is easy to interface to A.D. converter or Bi-level converter.

#### **FEATURES**

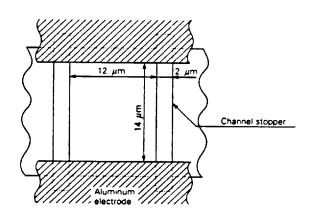

• Valid photocell 2 048-bit • Photocell's pitch 14 µm

CCD output

4 steps selectable gain (2, 4, 8, 16 times).

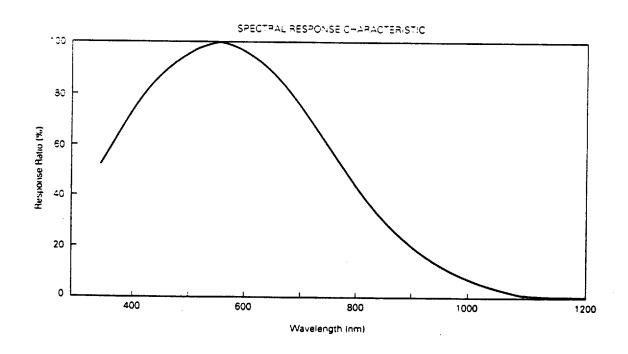

Peak response wavelength 550 nm (green)

Resolution

8 dot/mm across the shorter side of a B4-size (257 x 364 mm) sheet

• Power supply +12 V, +5 V

Drive clock level CMOS 5 V clock input x 2

High speed scan

1 ms/line

Built-in circuit Timing generator

CCD clock driver

Optical black clamp circuit

Sample and hold circuit

4-step valiable gain amplifier

#### ORDERING INFORMATION

| Part Number | Package                               | Quality Grade | OZSC- |

|-------------|---------------------------------------|---------------|-------|

| μPD3593D    | 22-pin ceramic DIP (CERDIP) (400 mil) | Standard      |       |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

ma Pen

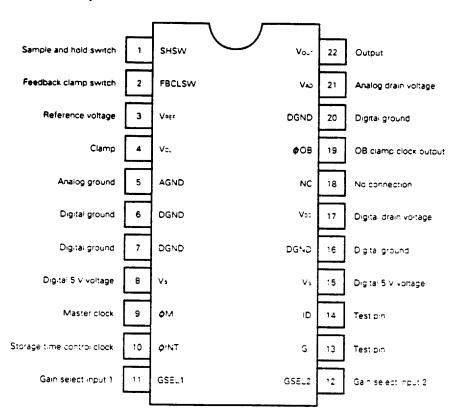

#### PIN CONFIGURATION (Top View)

#### Function of SHSW pin

#### Function of FBCLSW pin

| SHSW | Sample and hold circuit | FBCLSW | Feedback clamp circuit |

|------|-------------------------|--------|------------------------|

| V5   | Stop                    | V5     | Stop                   |

| 0 V  | Operate                 | 0 V    | Operate                |

#### PHOTOCELL STRUCTURE DIAGRAM

#### PIN FUNCTIONS

| Pín No. | Symbol | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SHSW   | Internal sample and hold enable pin.  Low level input: Internal sample and hold circuit operates.  High level input: Internal sample and hold circuit stops and signal from CCD is output just as it is  This pin is connected internally to pull-down resistor (refer to electrical characteristics to obtain pull-down resistance). Therefore, when internal sample and hold circuit is used, this pin can be left unconnected.                                                                                                               |

| 2       | FBCLSW | Internal optical black clamp enable pin.  Low level input: Internal optical black clamp circuit operates.  High level input: Internal optical black clamp circuit stops.  This pin is connected internally to pull-down resistor (refer to electrical characteristics to obtain pull-down resistance). Therefore, when internal optical black clamp circuit is used, this pin can be left unconnected.                                                                                                                                          |

|         |        | Optical black clamp equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |        | reset feed through cramp  optical brack clamp  3 Vass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |        | Connecting external capacitor to Vc. (pin 4), fix hold time according to the charge time.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3       | VREF   | Reference voltage input pin for internal optical black clamp circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4       | Va     | Connected to capacitor which sets hold time constant for internal optical black clamp circuit. Leak path resistance of internal capacitor (about 250 pF) will be 2 or 3 M $\Omega$ , therefore, when charge time is needed more than 1 ms, use external capacitor. When optical black clamp level precision is needed, this pin is input pin of feed back signal from external high precision comparator. Refer to parameter of clamp error in electrical characteristics to obtain dispersion of clamp level when internal comparator is used. |

| 5       | AGND   | Ground pin for analog signal processing unit (optical black clamp circuit, sample and hold circuit).                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6       | DGND   | Ground pin for digital circuits (timing generator unit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7       | DGND   | Ground pin for digital circuits (driver unit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Vs +5 V power supply pin for digital circuits.

| Pin No. | Symbol         | Functions                                                                                                                                                                                   |                                                         |                                     |                                                                               |  |  |  |

|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| 9       | фМ             | Master clock input pin.  Data rate is 1/2 of master clock frequency.                                                                                                                        |                                                         |                                     |                                                                               |  |  |  |

| 10      | <b>ØINT</b>    | Control clock input pin to set charge time. By inputting this signal, optical black signal is output from 26 clock pulses after $\phi$ M (Refer to timing chart to obtain detailed timing). |                                                         |                                     |                                                                               |  |  |  |

| 11      | GSEL1          | By combini                                                                                                                                                                                  | ng these 2 p                                            | oins, output amplifier circuit gain | can be selected.                                                              |  |  |  |

| 12      | GSEL2          |                                                                                                                                                                                             |                                                         |                                     |                                                                               |  |  |  |

|         |                | GSEL1                                                                                                                                                                                       | GSEL2                                                   | output amplifier circuit gain       |                                                                               |  |  |  |

|         |                | L                                                                                                                                                                                           | L                                                       | 2 times                             | ·                                                                             |  |  |  |

|         |                | L                                                                                                                                                                                           | н                                                       | 4 times                             |                                                                               |  |  |  |

|         |                | н                                                                                                                                                                                           | L                                                       | 8 times                             |                                                                               |  |  |  |

|         |                | н                                                                                                                                                                                           | н                                                       | 16 times                            | 1                                                                             |  |  |  |

|         |                | ,                                                                                                                                                                                           | down resist                                             | , ,                                 | or (refer to electrical characteristics input low level, this pin can be left |  |  |  |

| 13      | G <sub>1</sub> | Test pin. Connect to digital ground.                                                                                                                                                        |                                                         |                                     |                                                                               |  |  |  |

| 14      | ID             | Test pin. Connect to +5 V power supply.                                                                                                                                                     |                                                         |                                     |                                                                               |  |  |  |

| 15      | V5             | +5 V power supply pin for digital circuit.                                                                                                                                                  |                                                         |                                     |                                                                               |  |  |  |

| 16      | DGND           | Ground pin                                                                                                                                                                                  | Ground pin for digital circuit (timing generator unit). |                                     |                                                                               |  |  |  |

| 17      | Voo            | +12 V power supply pin for digital circuit.                                                                                                                                                 |                                                         |                                     |                                                                               |  |  |  |

| 18      | NC             | Non connect pin. Leave this pin unconnected or connect to digital GND.                                                                                                                      |                                                         |                                     |                                                                               |  |  |  |

| 19      | <i>ф</i> ОВ    | Output pin for optical black clamp pulse. CMOS output under 5 V operation.                                                                                                                  |                                                         |                                     |                                                                               |  |  |  |

| 20      | DGND           | Grond pin for digital circuit (timing generator unit).                                                                                                                                      |                                                         |                                     |                                                                               |  |  |  |

| 21      | VAD            | +12 V powe                                                                                                                                                                                  | +12 V power supply pin for analog circuit.              |                                     |                                                                               |  |  |  |

|         |                | Output pin.  Refer to timing chart to obtain detailed output timing.                                                                                                                        |                                                         |                                     |                                                                               |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS (Ta = +25 °C)

| Parameter                          | Symbol  | Ratings        | Unit |

|------------------------------------|---------|----------------|------|

| Analog drain voltage               | VAD     | -0.3 ~ +15     | ٧    |

| Digital drain voltage              | Voo     | -0.3 ~ +15     | ٧    |

| Test pin ID voltage                | Vio     | -0.3 ~ +15     | V    |

| Digital 5 V voltage                | Vs      | -0.3 ~ +7      | ٧    |

| Reference voltage                  | VREF    | -0.3 ~ +7      | ٧    |

| Clamp pin input voltage            | Vcr     | -0.3 +7        | ٧    |

| Sample and hold switch             | Vshsw   | Vs             | ٧    |

| Feedback clamp switch              | VF8CLSW | Vs             | ٧    |

| Master clock voltage               | Vom     | Vs             | ٧    |

| Storage time control clock voltage | Voint   | Vs             | ٧    |

| Gain select input voltage 1        | Vaseu   | Vs             | V    |

| Gain select input voltage 2        | VGSEL2  | V <sub>5</sub> | V    |

| Operating ambient temperature      | Тоет    | -25 ~ +60      | :C   |

| Storage temperature                | Tsra    | -40 ~ +100     | ·C   |

# RECOMMENDED OPERATING CONDITIONS (Ta = -25 to + 60 °C)

| Parameter                                                    | Symbol | MIN. | TYP.  | MAX.           | Unit |

|--------------------------------------------------------------|--------|------|-------|----------------|------|

| Analog drain voltage                                         | Vad    | 11.4 | 12.0  | 12.6           | ٧    |

| Digital drain voltage                                        | Voo    | 11.4 | 12.0  | 12.6           | V    |

| Test pin ID voltage                                          | V.o    | 11.4 | 12.0  | 12.6           | V    |

| Digital 5 V voltage                                          | Vs     | 4.5  | 5.0   | 5.5            | V    |

| Reference voltage                                            | VREF   | 4.0  | 4.5   | 5.0            | V    |

| Master clock ØM signal high level                            | Vэмн   | 4.5  | Vs    | Vs             | V    |

| Master clock φM signal low level                             | VomL   | -0.3 | 0     | 0.5            | V    |

| Storage time control clock ØINT signal high level            | Vointh | 4.5  | Vs    | Vs             | ٧    |

| Storage time control clock ØINT signal low level             | VOINTL | -0.3 | 0     | 0.5            | V    |

| Gain select input voltage GSEL 1,2 signal high level         | VGSELH | 4.5  | · Vs  | Vs             | V    |

| Gain select input voltage GSEL 1,2 signal low level (Note 1) | Vgseu  | -0.3 | 0     | 0.5            | V    |

| Sample and hold switch SHSW signal high level                | Vsнн   | 4.5  | Vs    | Vs             | V    |

| Sample and hold switch SHSW signal low level (Note 1)        | VSHL   | -0.3 | 0     | 0.5            |      |

| Feedback clamp switch FBCLSW signal high level               | VFBCLH | 4.5  | Vs    | V <sub>6</sub> | V    |

| Feedback clamp switch FBCLSW signal low level (Note 1)       | Vracu  | -0.3 | 0     | 0.5            | V    |

| Hold capacitor (Note 2)                                      | Ca     | _    | 0.001 | 0.01           | μF   |

| Master clock #M frequency                                    | føst   | 0.5  | 2     | 4              | MHz  |

- Note 1. Gain select pin (GSEL 1, 2), sample and hold switch pin (SHSW), feedback clamp switch pin (FBCLSW) are pull down to GND internally with 50 k $\Omega$  ~ 200 k $\Omega$  resistor.

- 2. Control voltage hold capacitor depending on storage time (Tint).

#### **ELECTRICAL CHARACTERISTICS**

$T_0 = +25$  °C,  $V_{AD} = V_{DO} = 12$  V,  $V_5 = 5$  V,  $f_{\phi M} = 2$  MHz, data rate = 1 MHz, storage time = 10ms input signal clock = 5 V<sub>P-P</sub>, V<sub>REF</sub> = 4.5 V, light source = 3200 K halogen lamp + C500 (infrared cut filter)

| Parameter                                                                                     | Symbol | Test Conditions                              | GSEL1    | GSEL2        | MIN.         | TYP.  | MAX.         | Unit       | , Built-in<br>amplifie<br>gain |

|-----------------------------------------------------------------------------------------------|--------|----------------------------------------------|----------|--------------|--------------|-------|--------------|------------|--------------------------------|

| Saturation voltage                                                                            | VSAT   | Daylight color fluorescent lamp              | -        | _            | 2            | ; 3   |              | · <b>v</b> |                                |

| Saturation exposure                                                                           | SE     | Daylight color                               | . 0      | 0            |              | 0.114 |              | ix·s       | ×2                             |

|                                                                                               |        | fluorescent lamp                             | 0        | 1            | <del>-</del> | 0.051 | ·            | -          | ×4                             |

|                                                                                               |        |                                              | 1        | 0            |              | 0.027 |              | -          | ×8                             |

|                                                                                               | :      |                                              | 1        | 1            | <del></del>  | 0.012 | <del>-</del> | -          | ×16                            |

| Photo response                                                                                | PRNU   | Vоит = 500 mV                                | 0        | 0            | -            | ±4    | ±8           | %          | ×2                             |

| Average dark signal                                                                           | ADS    | Tc = 25 °C Note,                             | 0        | 0            |              | 1     | 5            | m۷         | ×2                             |

| _g ·· •-g-·•-                                                                                 |        | Tint = 10 ms                                 | 0        | 1            |              | 2     | 10           | -          | ×4                             |

|                                                                                               |        | light shielding                              | 1        | 0            | <u>-</u>     | 4     | 20           | -          | ×8                             |

|                                                                                               |        |                                              | 1        | 1            |              | 8     | 40           | -          | ×16                            |

| Dark signal                                                                                   | DSNU   | Tc = 25 °C Note,                             | 0        | 0            | <b>-</b> 5   | ±1    | +5           | mV         | ×2                             |

| non-uniformity                                                                                | 55,10  | Tier = 10 ms                                 | 0        | 1            | -10          | ±2    | +10          | •          | ×4                             |

| •                                                                                             |        | light shielding                              | 1        | 0            | -20          | ±4    | +20          | -          | x8                             |

|                                                                                               |        | -                                            | 1        | 1            | -40          | ±8    | +40          | -          | ×16                            |

| Power consumption                                                                             | Pw     | Voc = Vcc = 12 V                             | 0        | 0            | 150          | 230   | 350          | mW         |                                |

| rower consumption                                                                             | rw     | $V_5 = 5 \text{ V, } f_{QM} = 2 \text{ MHz}$ | 1        | <u>.</u>     | 80           | 120   | 180          | -          |                                |

| Output impedance                                                                              | Zo     |                                              | <u>.</u> | <del></del>  | -            | 1     | 2            | kΩ         |                                |

| Response                                                                                      | Re     | Davillaha astas                              |          | - 0          | 18.5         | 26.4  | 34.3         |            | ×2                             |

| nesponse                                                                                      | M#     | Daylight color fluorescent lamp              |          | <u>-</u>     |              | 59.4  |              | -          | ×4                             |

|                                                                                               |        | madrescent tamp                              | 1 .      | <u>'</u>     | =            | 110   | •=           | _ V/ix∙s   | îī.<br>×8                      |

|                                                                                               |        |                                              | :        | <del>-</del> | =            | 248   | •            | -          | ×16                            |

| Response peak<br>wavelength                                                                   |        |                                              |          |              | _            | 550   | _            | nm         |                                |

| image lag                                                                                     | IL     | Vout = 1 V                                   | 0        | 0            | _            | 2     | 5            | %          | x2                             |

| Reference voltage input current                                                               | Iner   |                                              | . 0      | 0            | _            | 0.001 | 0.1          | mA         |                                |

| Transfer efficiency                                                                           | TTE    | Vout = 500 mV                                | 0        | . 0          | 92           | 98    | _            | %          | x2                             |

| Sample and hold noise                                                                         | SHN    | fight shielding                              | . 0      | 0            |              | 15    | 30           | m۷         | ×2                             |

| Clamp error                                                                                   | VERR   | light shielding<br>Vage = 4.5 V              | 0        | 0            | -100         | . 0   | +100         | m۷         | ×2                             |

| Clock input capacitance<br>Master clock input pin<br>Storage time control<br>clock input pin  | Сф     |                                              |          | -            | _            | 5     | 10           | pF         |                                |

| Pull down resistor Gain select input pin Sample and hold switch pin Feedback clamp switch pin | Reo    | Vin = 5 V                                    |          |              | 50           | 100   | 200          | kΩ         | !<br>:                         |

| Register imbalance                                                                            | RI     | Vout = 500 mV                                | 0        | 0            | _            | : -   | 3            | %          | x2                             |

| Dynamic range                                                                                 | DR     | VSAT/DSNU                                    | 0        | 0            |              | 3000  | ! <u>_</u>   | :          | ×2                             |

|                                                                                               |        |                                              | 0        | , 1 ;        |              | 1500  | ·            | times      | ×4                             |

|                                                                                               |        |                                              | 1        | 0            |              | 750   |              | _ (111163  | x8                             |

|                                                                                               |        | ı                                            | 1        | ; 1          |              | 375   | T            | -          | x16                            |

Note Tc = Case temperature

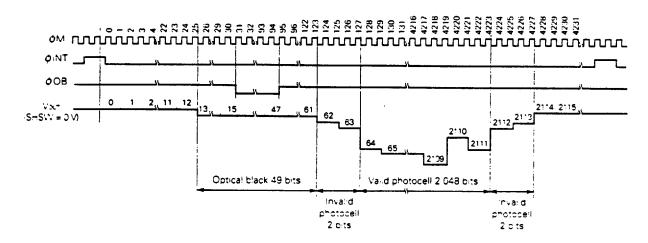

#### **TIMING CHART**

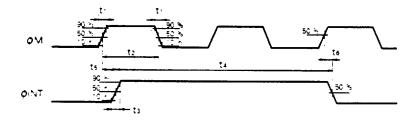

#### Timing Chart for ØM and ØINT

#### Recommended Timing

(Unit: ns)

| Parameter | MIN. | TYP. | MAX. |

|-----------|------|------|------|

| t1        | 0    | 20   | 100  |

| tz        | 125  | 250  | 1000 |

| ta        | 0    | 20   | 100  |

| te .      |      | 4t2  | -    |

| ts        | -30  | 0    | tz   |

| te .      | -tz  | 0    | tı   |

R

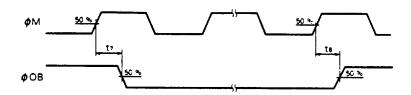

#### $\phi$ OB Signal Delay from $\phi$ M

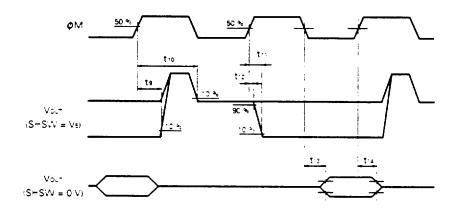

#### Vour Signal Delay from $\phi \mathbf{M}$

## Signal Delay Time (Vout = 500 mV, output amplifier gain: x2)

(Unit: ns)

| Parameter       | MIŅ. | TYP. | MAX. |

|-----------------|------|------|------|

| t7              | 200  | 280  | 370  |

| ta              | 150  | 220  | 290  |

| t9              | 40   | 60   | 80   |

| tio             | 160  | 230  | 300  |

| t <sub>11</sub> | 66   | 95   | 125  |

| <b>t</b> 12     | 40   | 60   | 80   |

| <b>t</b> 13     |      | 80   | 120  |

| <b>t</b> 14     | i    | 50   | 100  |

250 · 250

#### **DEFINITIONS OF CHARACTERISTIC ITEMS**

1. Saturation voltage: VSAT

Output signal voltage at which the response linearity is lost.

2. Saturation exposure: SE

Product of intensity of illumination (lx) and storage time (s) when saturation of output voltage occurs.

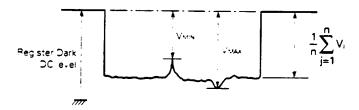

3. Photo response non-uniformity: PRNU

The peak/bottom ratio to the average output voltage of all the valid bits calculated by the following formula.

PRNU (%) =

$$\left(\frac{V_{\text{MAX. OF }V_{\text{MIN.}}}}{\frac{1}{n}\sum_{j=1}^{n}V_{i}} - 1\right) \times 100$$

n: Number of valid bits

Vi: Output voltage of each bit

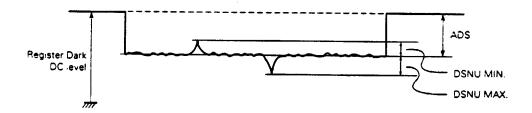

4. Average dark signal: ADS

Output average voltage in light shielding

$$ADS(mV) = \frac{1}{n} \sum_{i=1}^{n} V_i$$

5. Dark signal non-uniformity: DSNU

The difference between peak or bottom output voltage in light shielding and ADS.

6. Output impedance: Zo

ma 88

Output pin impedance viewed from outside.

7. Response: R

Output voltage divided by exposure (Ix-s).

Note that the response varies with the light source.

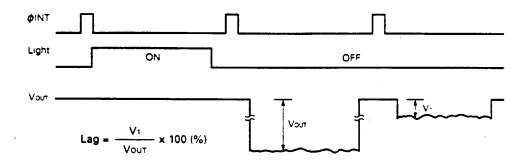

#### 8. Image Lag: IL

The rate between the last output voltage and the next one after read out the data of a line.

#### 9. Register Imbalance: RI

The rate of the average voltage which is the difference between the output voltage of Odd and Even bits, against the average output voltage of all the valid bits.

RI =

$$\frac{\frac{1}{n} \sum_{j=1}^{n} |V_{i} - V_{i+1}|}{\frac{1}{n} \sum_{j=1}^{n} V_{i}} \times 100 \text{ (%)}$$

#### 10. Clamp Error: VERR

VERR = OB unit offset voltage - VREF

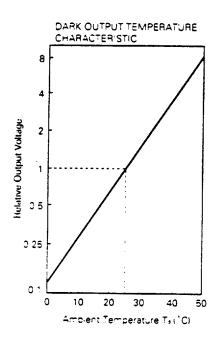

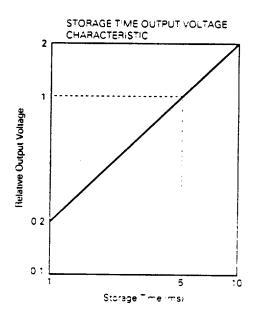

## STANDARD CHARACTERISTIC CURVES (T. = 25 °C)

ma 88

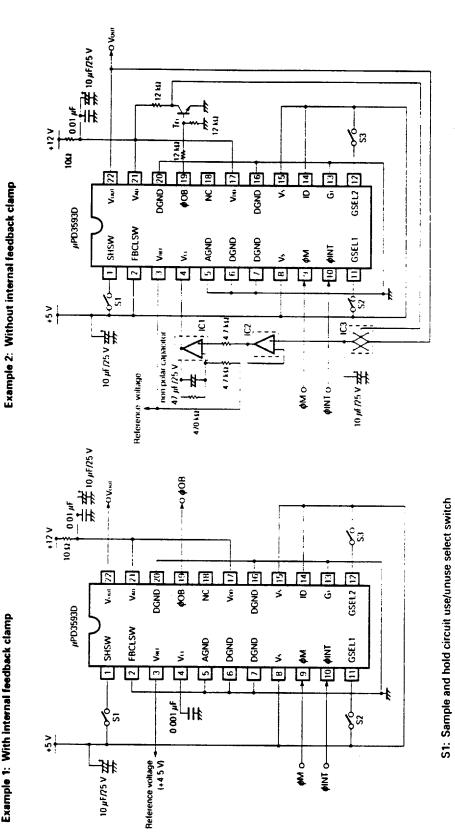

# **APPLICATION EXAMPLES**

Example 1: With internal feedback clamp

ma 88

) 5T3 🖿

IC1, IC2: Low offset, low input current IC3: µPD4066

S2, S3: Output amplifier gain select switch

(OFF; Use ON; Unuse)

Tr1: 2SC945

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

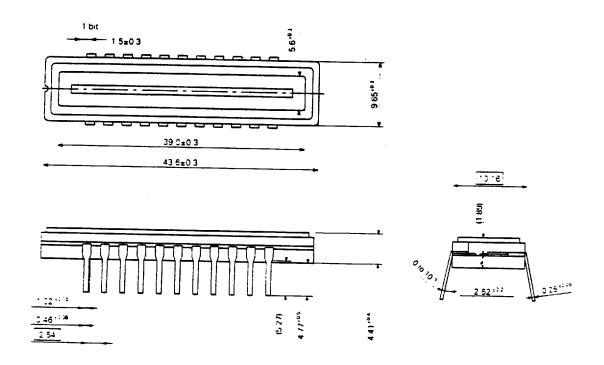

# PACKAGE DIMENSIONS (Unit: mm)

| Name      | D mensions | Refractive index |

|-----------|------------|------------------|

| Glass cap | 422×90×05  | 1.5              |