PAGE : 1/33

| A.   | General description                               | P3  |

|------|---------------------------------------------------|-----|

| В.   | Feature                                           | P3  |

| C.   | Pin description                                   | P4  |

| D.   | DC characteristics                                | P7  |

| a.   | Absolute maximum ratings                          | P7  |

| b.   | Recommended operating conditions                  | P7  |

| c.   | General DC characteristics                        | P7  |

| d.   | DC electrical characteristics for 3.3V operation  | P7  |

| e.   | DC electrical characteristics for 5V operation    | P8  |

| f. ( | Current consumption for different resolution mode | P8  |

| Ε.   | AC characteristics                                | P10 |

| a.   | Input signal characteristics                      | P10 |

| 1.   | 280 mode                                          | P10 |

| 2.   | 480 mode                                          | P10 |

| 3.   | 528 mode                                          | P11 |

| 4.   | 1152 mode                                         | P12 |

| 5.   | 960 mode                                          | P13 |

| 6.   | 1440 mode                                         | P14 |

| b.   | Output signal characteristics                     | P15 |

| 1.   | 280 mode                                          | P15 |

| 2.   | 480 mode (2.5")                                   | P16 |

| 3.   | 480 mode (4.0")                                   | P17 |

| 4.   | 528 mode                                          | P18 |

| 5.   | 1152 mode                                         | P19 |

| 6.   | 960 mode                                          | P20 |

| 7.   | 1440 mode                                         | P21 |

**Contents:**

|                                                 | PAGE | : 2/33     |

|-------------------------------------------------|------|------------|

| c. Video Output signal characteristics          |      | <b>P21</b> |

|                                                 |      |            |

| F. Color sequence for different resolution mode |      | P22        |

| G. Reliability test items                       |      | P23        |

| H. Package information                          |      | P24        |

# Appendix

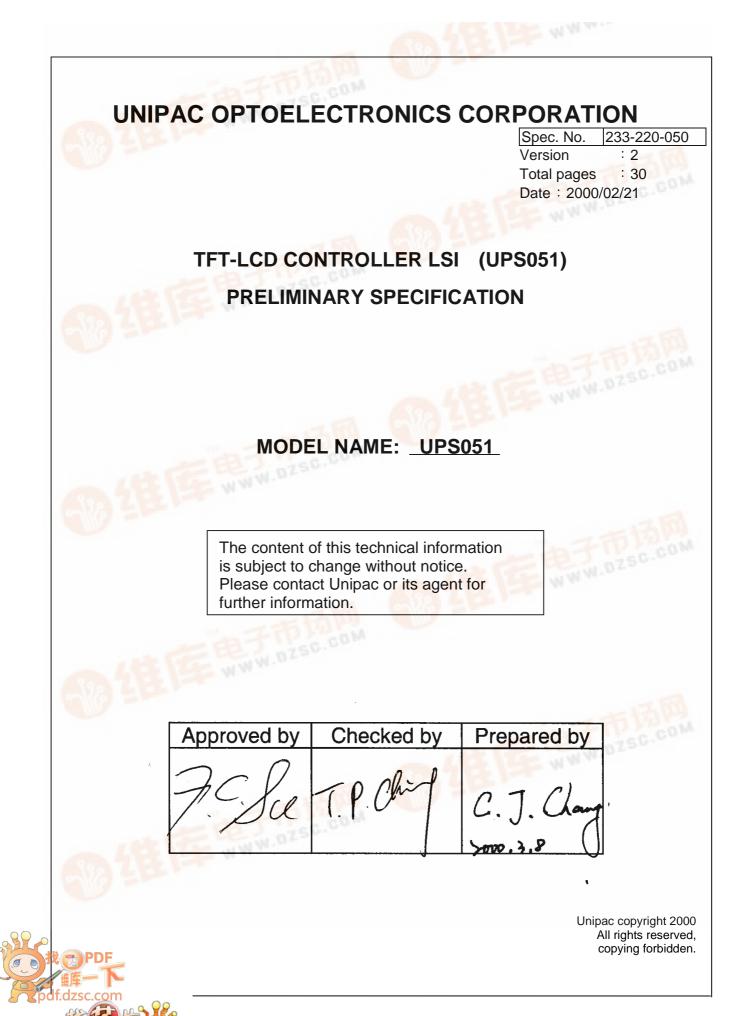

| Fig.1     | Input vertical timing           | P25 |

|-----------|---------------------------------|-----|

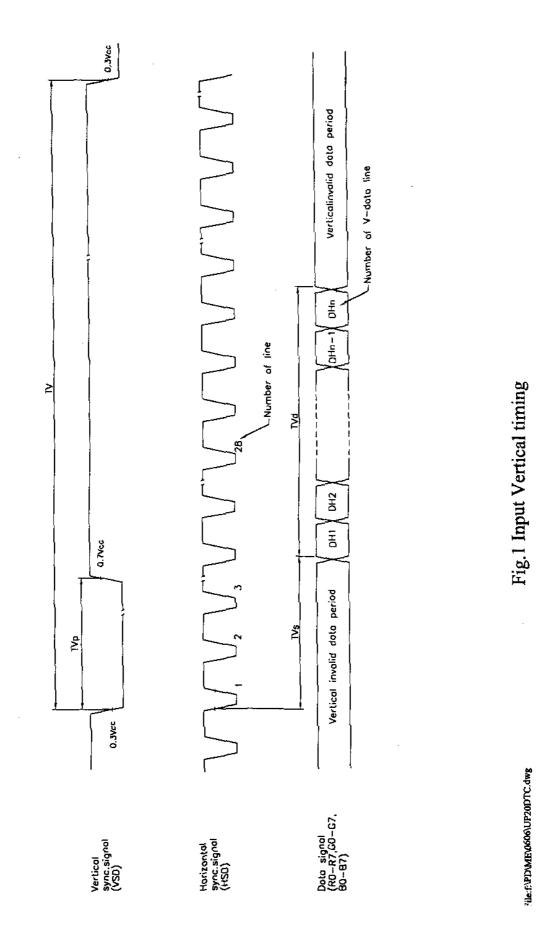

| Fig.2     | Input horizontal timing         | P26 |

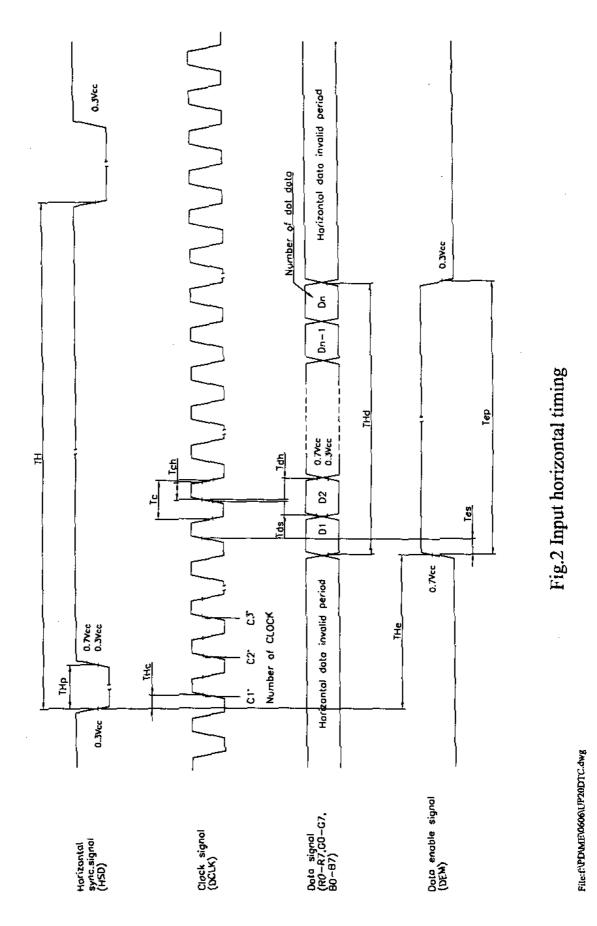

| Fig.3     | Sampling clock timing           | P27 |

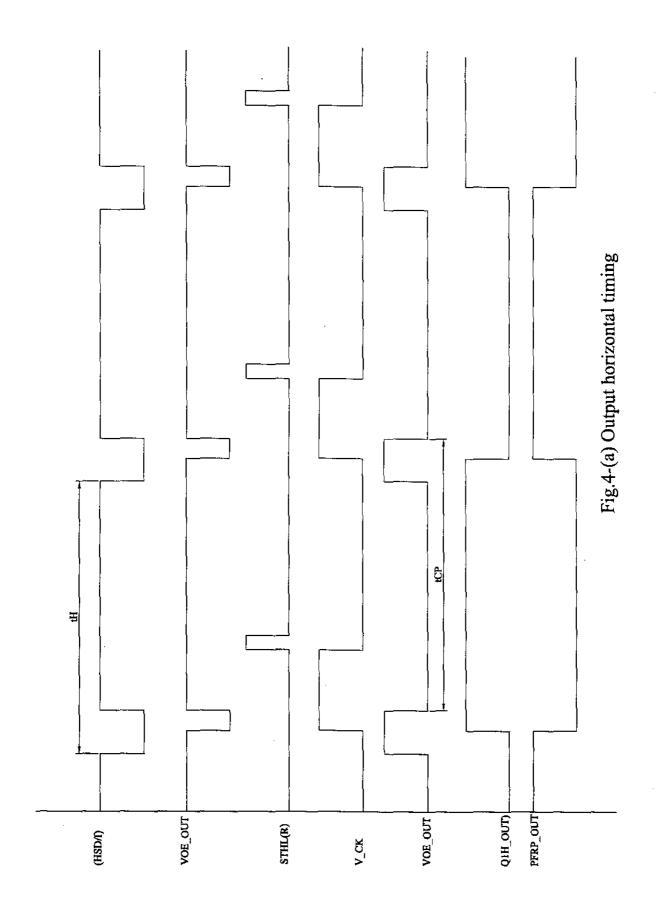

| Fig.4-(a) | Output horizontal timing        | P28 |

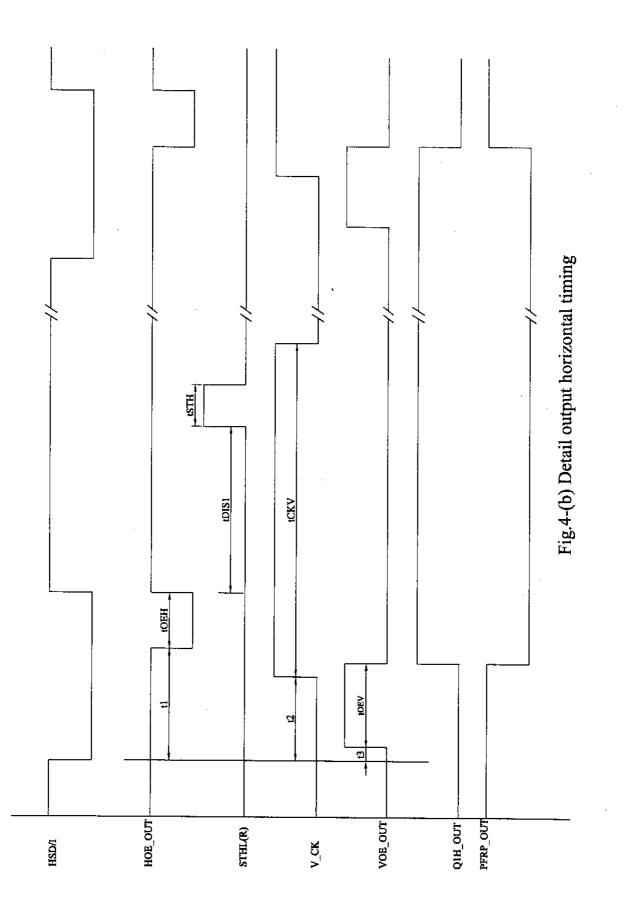

| Fig.4-(b) | Detail output horizontal timing | P29 |

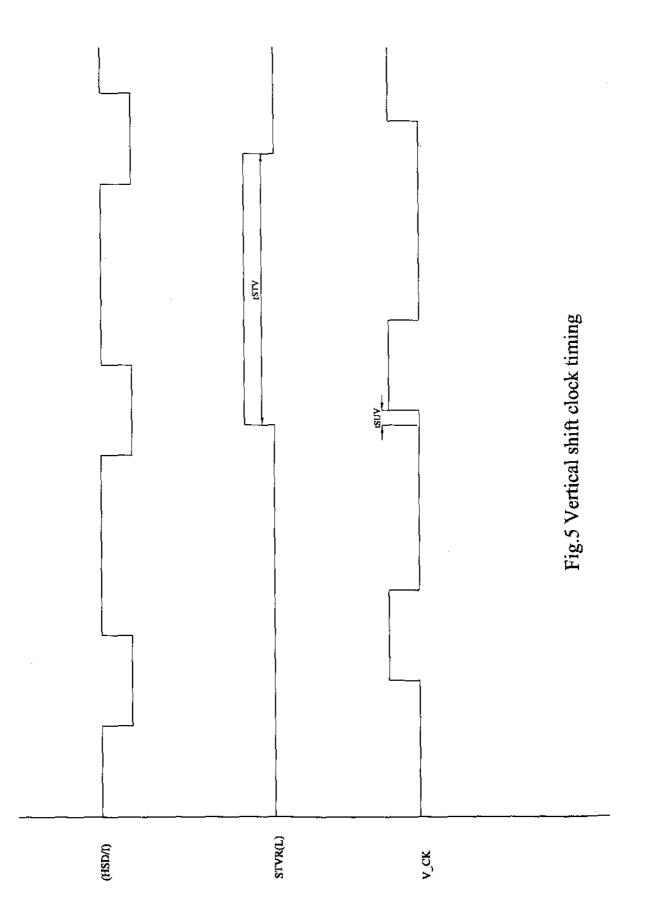

| Fig.5     | Vertical shift clock timing     | P30 |

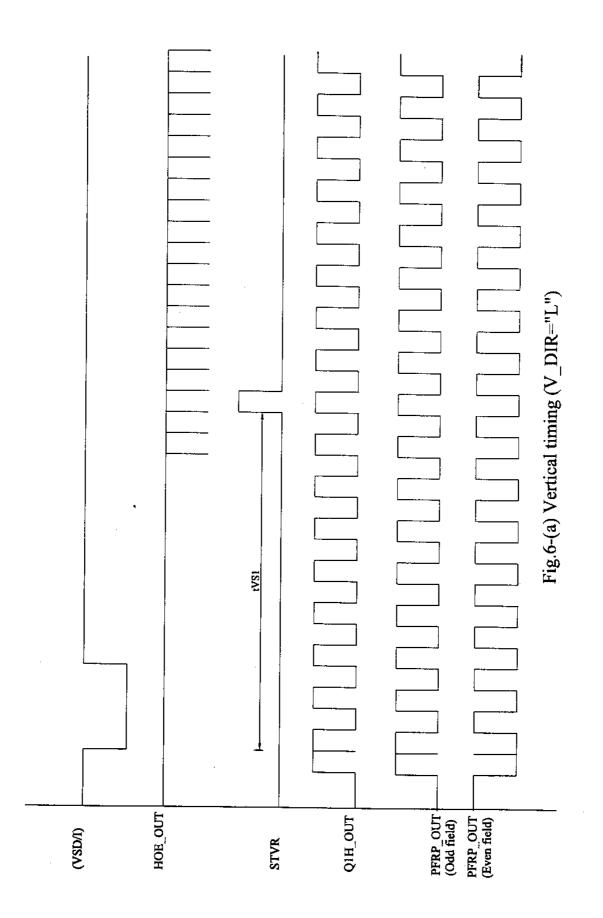

| Fig.6-(a) | Vertical timing(V-DIR="L")      | P31 |

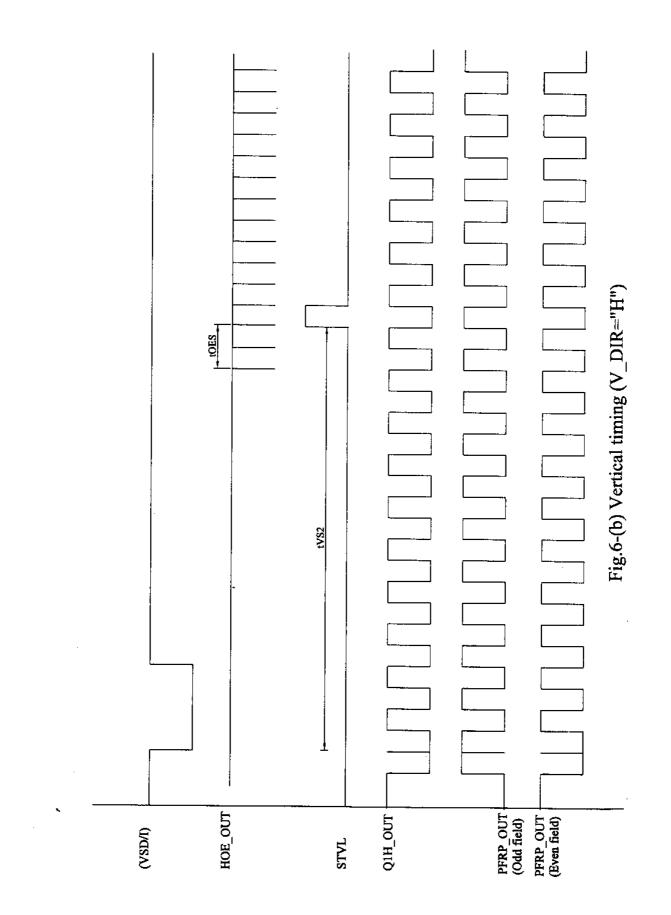

| Fig.6-(b) | Vertical timing(V_DIR="H")      | P32 |

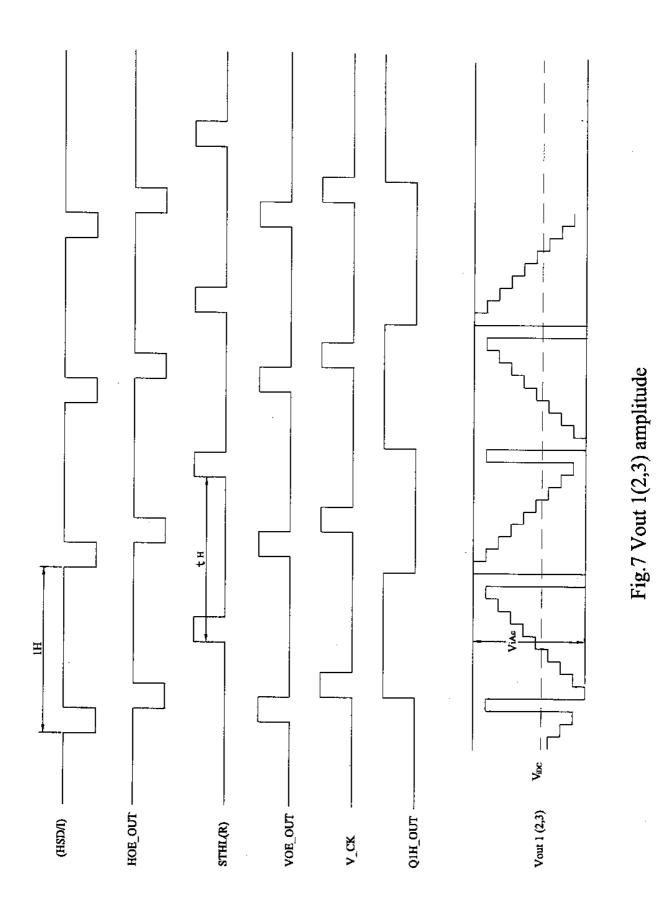

| Fig.7     | Vout 1(2,3) amplitude           | P33 |

|           |                                 |     |

PAGE :3/33

# A. General description:

This timing controller is a synchronizing signal controlling CMOS LSI for Unipac COG type LCD module. It accepts the digital signal and provides all the necessary control timing signals to the LCD source and gate drivers. This controller converts the digital input data to the analog alternated and amplified signals for the driving of the TFT-LCD panel. This controller also supports different resolution modes.

# **B. Feature:**

- \* Single power supply : +5.0 Volts.

- \* Low power consumption.

- \* 64 pins LQFP.

- \* Built-In PWM circuit.

- \* Built-In polarity inverted circuit.

- \* Provides timing scan signals for Left / Right and Up / Down shift control.

- \* Built-In GAMMA correction function.

- \* Multi-resolution modes.

- \* Optional 3.3V input level.

- \* NTSC/PAL system timing

PAGE : 4/33

# C. Pin description:

| Pin-no | Symbol   | I/O | Description                                                  | Remark |

|--------|----------|-----|--------------------------------------------------------------|--------|

| 1      | DCLK     | Ι   | Data clock input.                                            |        |

|        |          |     | Source driver start pulse. When                              |        |

| 2      | STHR     | 0   | (1).H_DIR=L, STHR is output pin of start pulse.              |        |

|        |          |     | (2).H_DIR=H, STHR is high impedance state.                   |        |

|        |          |     | Source driver start pulse. When                              |        |

| 3      | STHL     | 0   | (1).H_DIR=L, STHL is high impedance state.                   |        |

|        |          |     | (2).H_DIR=H, STHL is output pin of start pulse.              |        |

|        |          |     | Gate driver start pulse. When                                |        |

| 4      | STVR     | 0   | (1).V_DIR=L, STVR is output pin of start pulse.              |        |

|        |          |     | (2).V_DIR=H, STVR is high impedance state.                   |        |

|        |          |     | Gate driver start pulse. When                                |        |

| 5      | STVL     | 0   | (1).V_DIR=L, STVL is high impedance state.                   |        |

|        |          |     | (2).V_DIR=H, STVL is output pin of start pulse.              |        |

| 6      | VOE_OUT  | 0   | Gate driver output enable control signal.                    |        |

| 7      | V_CK     | 0   | Gate driver shift clock.                                     |        |

| 8      | HOE_OUT  | 0   | Source driver output enable control signal.                  |        |

| 9      | VCC1     | -   | Power pin for digital circuits.                              |        |

| 10     | VCI      | Ι   | Test pin, pull to ground.                                    |        |

| 11     | GND1     | -   | Ground pin for digital circuit.                              |        |

| 12     | GME      | Ι   | Gamma correction enable control signal. (Normally pulled-up) | Note 1 |

| 13     | HSD      | Ι   | Horizontal synchronization signal, negative polarity.        |        |

| 14     | VSD      | 1   | Vertical synchronization signal, negative polarity.          |        |

| 15     | Q1H_OUT  | 0   | Source driver sample & hold sequence control signal.         |        |

| 16     | PFRP_OUT | 0   | Polarity alternating signal for Vcom.                        |        |

| 17     | GND2     | -   | Ground pin for PWM circuits.                                 |        |

| 18     | VCC2     | -   | Power pin for PWM circuits.                                  |        |

| 19     | PWM_OUT3 | 0   | PWM output.                                                  |        |

| 20     | FBK3     | 1   | Reference voltage feedback.                                  |        |

| 21     | GND3     | -   | Ground pin for PWM circuits.                                 |        |

| 22     | VCC3     | -   | Power pin for PWM circuits.                                  |        |

| 23     | PWM_OUT2 | 0   | PWM output.                                                  |        |

| 24     | PWM OUT1 | 0   | PWM output.                                                  |        |

| 25     | FBK1     | 1   | Reference voltage feedback.                                  |        |

| 26     | FBK2     |     | Reference voltage feedback.                                  |        |

| 27     | RSC      | 1   | Resolution mode selection pin. (Normally pulled-up)          | Note 2 |

| 28     | UD_OUT   | 0   | Inverted V_DIR signal output.                                |        |

| 29     | LR OUT   | 0   | Inverted H_DIR signal output.                                |        |

| 30     | V_DIR    | 1   | Up/Down scan control pin. ( Normally pulled-up )             |        |

| 31     | H_DIR    | 1   | Left/Right scan control pin. (Normally pulled-up)            |        |

PAGE : 5/33

| Pin-no | Symbol   | I/IO | Description                                                      | Remark |

|--------|----------|------|------------------------------------------------------------------|--------|

| 32     | IN1      | Ι    | Test pin, pull to ground.                                        |        |

| 33     | VCC4     | -    | Power pin for digital circuits of DAC.                           |        |

| 34     | VIN      | Ι    | Test pin, pull to ground.                                        |        |

| 35     | NPC      | Ι    | NTSC/PAL system setting pin ( Normally pulled-up , NTSC )        | Note 3 |

| 36     | GND4     | -    | Ground pin for digital circuit of ADC and DAC.                   |        |

| 37     | IOUT     | 0    | DAC setting pin.                                                 |        |

| 38     | VTEST    | Ι    | Vertical timing test mode selection. (Normally pulled-up)        |        |

|        |          |      | Global reset. It should be connected to Vcc in normal operation. |        |

| 39     | GR_IN    | Ι    | If connected to GND, the controller is in reset state.           |        |

|        |          |      | (Normally pulled-up)                                             |        |

| 40     | VOUT3    | 0    | Alternated, amplified video output.                              |        |

| 41     | RSB      | Ι    | Resolution mode selection pin. (Normally pulled-up)              | Note 2 |

| 42     | VOUT2    | 0    | Alternated, amplified video output.                              |        |

| 43     | RSA      | Ι    | Resolution mode selection pin. (Normally pulled-up)              | Note 2 |

| 44     | VOUT1    | 0    | Alternated, amplified video output.                              |        |

| 45     | VCC5     | -    | Power pin for analog circuits of DAC.                            |        |

| 46     | GND5     | -    | Ground pin for analog circuits of DAC.                           |        |

| 47     | VG       | -    | Setting pin of DAC.                                              |        |

| 48     | VREF     | Ι    | Reference voltage setting pin of DAC.                            |        |

| 49     | IREF     | Ι    | Reference current setting pin of DAC.                            |        |

| 50     | DDX0     | Ι    | Digital data input, LSB.                                         |        |

| 51     | DDX1     | Ι    | Digital data input.                                              |        |

| 52     | DDX2     | Ι    | Digital data input.                                              |        |

| 53     | DDX3     | Ι    | Digital data input.                                              |        |

| 54     | GND1     | -    | Ground pin for digital circuits.                                 |        |

| 55     | VCC3IO   | -    | Power pin for 3.3V input optional.                               | Note 4 |

| 56     | VCC1     | -    | Power pin for digital circuits.                                  |        |

| 57     | DDX4     | Ι    | Digital data input                                               |        |

| 58     | DDX5     | Ι    | Digital data input                                               |        |

| 59     | DDX6     | -    | Digital data input                                               |        |

| 60     | DDX7     | Ι    | Digital data input, MSB.                                         |        |

| 61     | CPH3_OUT | 0    | Source driver shift clock .                                      |        |

| 62     | CPH2_OUT | 0    | Source driver shift clock .                                      |        |

| 63     | CPH1_OUT | 0    | Source driver shift clock .                                      |        |

| 64     | DEM      | Ι    | Data enable control signal. (Normally pulled-up)                 |        |

PAGE : 6/33

Note 1: GME=H , Gamma correction (Normally pulled-up) GME=L , No gamma correction

Note 2: Use RSA , RSB and RSC to select different resolution modes :

| Resolution mode | RSA | RSB | RSC |

|-----------------|-----|-----|-----|

| 220× 280        | L   | L   | L   |

| 220 × 528       | Н   | Н   | L   |

| 234× 480 (2.5") | Н   | Н   | Н   |

| 234× 480 (4.0") | L   | L   | Н   |

| 234× 960        | Н   | L   | Н   |

| 234× 1152       | L   | Н   | L   |

| 234× 1440       | L   | Н   | Н   |

- Note 3: NPC=H , NTSC System (Normally pulled-up ) NPC=L , PAL System

- Note 4: When connected to 3.3V , the input level of I/Ps ( DEM , DCLK , HSD , VSD , V\_DIR , H\_DIR , DDX0 ~ DDX7 ) is 3.3V , and when connected to 5.0V , the input level of I/Ps are 5.0V .

# PAGE : 7/33

# **D. DC characteristics**

#### a. Absolute maximum ratings:

| Symbol          | Parameter           | Rating            | Units | Remark |

|-----------------|---------------------|-------------------|-------|--------|

| Vcc             | Power supply        | -0.3 to 6.0       | V     | Note 1 |

| V <sub>IN</sub> | Input voltage       | -0.3 to VCC + 0.3 | V     |        |

| VOUT            | Output voltage      | -0.3 to VCC + 0.3 | V     |        |

| TSTG            | Storage temperature | -40 to 95         | °C    |        |

Note 1: For all V<sub>CC</sub> inputs, including V<sub>CC1</sub>, V<sub>CC2</sub>, V<sub>CC3</sub>, V<sub>CC4</sub>, V<sub>CC5</sub> and V<sub>CC3I0</sub>.

#### b. Recommended operating conditions:

| Symbol          | Parameter             | Min  | Тур | Max  | Units | Remark |

|-----------------|-----------------------|------|-----|------|-------|--------|

| VCC             | Power supply          | 4.75 | 5.0 | 5.25 | V     | Note 1 |

| V <sub>IN</sub> | Input voltage         | 0    | -   | VCC  | V     |        |

| TOPR            | Operating temperature | 0    | 25  | 85   | °C    |        |

Note 1: For all V<sub>CC</sub> inputs, including V<sub>CC1</sub>, V<sub>CC2</sub>, V<sub>CC3</sub>, V<sub>CC4</sub>, V<sub>CC5</sub> and V<sub>CC3I0</sub>.

# c. General DC characteristics:

| Symbol           | Parameter                         | Conditions              | Min | Тур | Max | Units    |

|------------------|-----------------------------------|-------------------------|-----|-----|-----|----------|

| ۱ <sub>۱</sub> ۲ | Input leakage current             | no pull-up or pull-down | -1  | -   | 1   | $\mu  A$ |

| loz              | Tri-state leakage current         |                         | -10 | -   | 10  | $\mu  A$ |

| C <sub>IN</sub>  | Input capacitance                 |                         | -   | 3   | -   | pF       |

| COUT             | Output capacitance                |                         | 3   | -   | 6   | pF       |

| CBID             | Bi-directional buffer capacitance |                         | 3   | -   | 6   | pF       |

d. DC electrical characteristics for 3.3V operation:

<sup>(</sup>Under recommended operating conditions and V<sub>CC</sub>=3.0V $\sim$ 3.6V, Tj= 0°C to +115°C)

| Symbol           | Parameter                                        | Conditions                 | Min                 | Тур  | Max                  | Units | Remark |

|------------------|--------------------------------------------------|----------------------------|---------------------|------|----------------------|-------|--------|

| -                |                                                  |                            |                     | чур  |                      |       |        |

| VIL              | Input Low voltage                                | CMOS                       | -                   | -    | 0.3× V <sub>CC</sub> | V     | Note 1 |

| VIH              | Input High voltage                               | CMOS                       | $0.7 \times V_{CC}$ | -    | -                    | V     | Note 1 |

| V <sub>t</sub> - | Schmitt trigger negative going threshold voltage | CMOS                       | -                   | 1.22 | -                    | V     |        |

| V <sub>t+</sub>  | Schmitt trigger positive going threshold voltage | CMOS                       | -                   | 2.08 | -                    | V     |        |

| VOL              | Output low voltage                               | I <sub>OL</sub> =2,4,8,12, |                     | -    | 0.4                  | V     |        |

| VOL              |                                                  | 16,24mA                    | -                   |      |                      |       |        |

| Vau              |                                                  | I <sub>OH</sub> =2,4,8,12, | 2.4                 |      |                      | V     |        |

| Vон              | Output high voltage                              | 16,24mA                    | 2.4                 | -    | -                    |       |        |

| RI               | Input pull up/down                               | Vil=0V or                  |                     | 75   |                      | KO    |        |

|                  | resistance                                       | Vih=V <sub>CC</sub>        | -                   | 75   | -                    | KΩ    |        |

Note 1: The applicable pins are DEM, DCLK, HSD, VSD, V\_DIR, H\_DIR DDX0  $\sim$  DDX7.

### PAGE : 8/33

# e. DC electrical characteristics for 5V operation:

| •                | •                                                | 5 00                              |                     |      |                     | ,     |

|------------------|--------------------------------------------------|-----------------------------------|---------------------|------|---------------------|-------|

| Symbol           | Parameter                                        | Conditions                        | Min                 | Тур  | Max                 | Units |

| $V_{IL}$         | Input Low voltage                                | CMOS                              | -                   | -    | $0.3 \times V_{CC}$ | V     |

| $v_{IH}$         | Input High voltage                               | CMOS                              | $0.7 \times V_{CC}$ | -    | -                   | V     |

| V <sub>t</sub> - | Schmitt trigger negative going threshold voltage | CMOS                              | -                   | 1.84 | -                   | V     |

| $V_{t+}$         | Schmitt trigger positive going threshold voltage | CMOS                              | -                   | 3.22 | -                   | V     |

| VOL              | Output low voltage                               | I <sub>OL</sub> =2,4,8,12,16,24mA | -                   | -    | 0.4                 | V     |

| VOH              | Output high voltage                              | I <sub>OH</sub> =2,4,8,12,16,24mA | 3.5                 | -    | -                   | V     |

| RI               | Input pull up/down<br>resistance                 | Vil=0V or Vih= $V_{CC}$           | -                   | 50   | -                   | ΚΩ    |

# (Under recommended operating conditions and V<sub>CC</sub>=4.75V $\sim$ 5.25V, Tj= 0°C to +115°C)

#### f. Current consumption for different resolution modes:

# 1. 280 mode:

| Parameter                                          | Symbol           | Conditions                                  | Min | Тур | Max | Units | Remark         |

|----------------------------------------------------|------------------|---------------------------------------------|-----|-----|-----|-------|----------------|

| Current for V <sub>CC1</sub>                       | ICC1             | V <sub>CC1</sub> =+5V                       | -   | 5.5 | -   | mA    | Pin 9 + Pin 56 |

| Current for<br>V <sub>CC2</sub> + V <sub>CC3</sub> | ICC2 +ICC3       | V <sub>CC2</sub> , V <sub>CC3</sub><br>=+5V | -   | 2.5 | -   | mA    | Pin 18+Pin 22  |

| Current for V <sub>CC4</sub>                       | I <sub>CC4</sub> | V <sub>CC4</sub> =+5V                       | -   | 1   | -   | mA    |                |

| Current for V <sub>CC5</sub>                       | ICC5             | V <sub>CC5</sub> =+5V                       | -   | 39  | -   | mA    |                |

| Current for V <sub>CC3IO</sub>                     | laassa           | V <sub>CC3IO</sub> =+5V                     | -   | 0.2 | -   | mA    |                |

|                                                    | ICC3IO           | V <sub>CC3IO</sub> =+3.3V                   | -   | 0.2 | -   | mA    |                |

### 2. 480 mode:

| Parameter                                          | Symbol     | Conditions                                  | Min | Тур | Max | Units | Remark         |

|----------------------------------------------------|------------|---------------------------------------------|-----|-----|-----|-------|----------------|

| Current for V <sub>CC1</sub>                       | ICC1       | V <sub>CC1</sub> =+5V                       | -   | 8.5 | -   | mA    | Pin 9 + Pin 56 |

| Current for<br>V <sub>CC2</sub> + V <sub>CC3</sub> | ICC2 +ICC3 | V <sub>CC2</sub> , V <sub>CC3</sub><br>=+5V | -   | 2.6 | -   | mA    | Pin 18+Pin 22  |

| Current for V <sub>CC4</sub>                       | ICC4       | V <sub>CC4</sub> =+5V                       | -   | 1.5 | -   | mA    |                |

| Current for V <sub>CC5</sub>                       | ICC5       | V <sub>CC5</sub> =+5V                       | -   | 40  | -   | mA    |                |

| Current for V <sub>CC3IO</sub>                     |            | V <sub>CC3IO</sub> =+5V                     | -   | 0.2 | -   | mA    |                |

| Content for VCC3IO                                 | ICC3IO     | V <sub>CC3IO</sub> =+3.3V                   | -   | 0.2 | -   | mA    |                |

### 3. 528 mode:

| Parameter                                          | Symbol                             | Conditions                                  | Min | Тур | Max | Units | Remark         |

|----------------------------------------------------|------------------------------------|---------------------------------------------|-----|-----|-----|-------|----------------|

| Current for V <sub>CC1</sub>                       | ICC1                               | V <sub>CC1</sub> =+5V                       | -   | 9   | -   | mA    | Pin 9 + Pin 56 |

| Current for<br>V <sub>CC2</sub> + V <sub>CC3</sub> | I <sub>CC2</sub> +I <sub>CC3</sub> | V <sub>CC2</sub> , V <sub>CC3</sub><br>=+5V | -   | 2.7 | -   | mA    | Pin 18+Pin 22  |

| Current for V <sub>CC4</sub>                       | I <sub>CC4</sub>                   | V <sub>CC4</sub> =+5V                       | -   | 1.3 | -   | mA    |                |

| Current for V <sub>CC5</sub>                       | ICC5                               | V <sub>CC5</sub> =+5V                       | -   | 41  | -   | mA    |                |

| Current for V <sub>CC3IO</sub>                     |                                    | V <sub>CC3IO</sub> =+5V                     | -   | 0.2 | -   | mA    |                |

|                                                    | ICC3IO                             | V <sub>CC3IO</sub> =+3.3V                   | -   | 0.2 | -   | mA    |                |

PAGE : 9/33

4. 1152 mode:

| 4. 1152 mode:                                      |                  |                                             |     |      |     |       |                |

|----------------------------------------------------|------------------|---------------------------------------------|-----|------|-----|-------|----------------|

| Parameter                                          | Symbol           | Conditions                                  | Min | Тур  | Max | Units | Remark         |

| Current for V <sub>CC1</sub>                       | ICC1             | V <sub>CC1</sub> =+5V                       | -   | 19.6 | -   | mA    | Pin 9 + Pin 56 |

| Current for<br>V <sub>CC2</sub> + V <sub>CC3</sub> | ICC2 +ICC3       | V <sub>CC2</sub> , V <sub>CC3</sub><br>=+5V | -   | 3.6  | -   | mA    | Pin 18+Pin 22  |

| Current for V <sub>CC4</sub>                       | I <sub>CC4</sub> | V <sub>CC4</sub> =+5V                       | -   | 3.6  | -   | mA    |                |

| Current for V <sub>CC5</sub>                       | ICC5             | V <sub>CC5</sub> =+5V                       | -   | 41   | -   | mA    |                |

| Current for V <sub>CC3IO</sub>                     |                  | V <sub>CC3IO</sub> =+5V                     | -   | 0.2  | -   | mA    |                |

|                                                    | ICC3IO           | V <sub>CC3IO</sub> =+3.3V                   | -   | 0.2  | -   | mA    |                |

### 5. 960 mode:

| Parameter                                          | Symbol           | Conditions                                  | Min | Тур  | Max | Units | Remark         |

|----------------------------------------------------|------------------|---------------------------------------------|-----|------|-----|-------|----------------|

| Current for V <sub>CC1</sub>                       | ICC1             | V <sub>CC1</sub> =+5V                       | -   | 17.0 | -   | mA    | Pin 9 + Pin 56 |

| Current for<br>V <sub>CC2</sub> + V <sub>CC3</sub> | ICC2 +ICC3       | V <sub>CC2</sub> , V <sub>CC3</sub><br>=+5V | -   | 3.2  | -   | mA    | Pin 18+Pin 22  |

| Current for V <sub>CC4</sub>                       | I <sub>CC4</sub> | V <sub>CC4</sub> =+5V                       | -   | 3.2  | -   | mA    |                |

| Current for V <sub>CC5</sub>                       | I <sub>CC5</sub> | V <sub>CC5</sub> =+5V                       | -   | 41   | -   | mA    |                |

| Current for V <sub>CC3IO</sub>                     |                  | V <sub>CC3IO</sub> =+5V                     | -   | 0.2  | -   | mA    |                |

| Cancilla ACC3IO                                    | ICC3IO           | V <sub>CC3IO</sub> =+3.3V                   | -   | 0.2  | -   | mA    |                |

# 6. 1440 mode:

| Parameter                                          | Symbol           | Conditions                                  | Min | Тур | Max | Units | Remark         |

|----------------------------------------------------|------------------|---------------------------------------------|-----|-----|-----|-------|----------------|

| Current for V <sub>CC1</sub>                       | ICC1             | V <sub>CC1</sub> =+5V                       | -   | 24  | -   | mA    | Pin 9 + Pin 56 |

| Current for<br>V <sub>CC2</sub> + V <sub>CC3</sub> | ICC2 +ICC3       | V <sub>CC2</sub> , V <sub>CC3</sub><br>=+5V | -   | 4.0 | -   | mA    | Pin 18+Pin 22  |

| Current for V <sub>CC4</sub>                       | I <sub>CC4</sub> | V <sub>CC4</sub> =+5V                       | -   | 4.0 | -   | mA    |                |

| Current for V <sub>CC5</sub>                       | ICC5             | V <sub>CC5</sub> =+5V                       | -   | 41  | -   | mA    |                |

| Current for V <sub>CC3IO</sub>                     |                  | V <sub>CC3IO</sub> =+5V                     | -   | 0.2 | -   | mA    |                |

|                                                    | ICC3IO           | V <sub>CC3IO</sub> =+3.3V                   | -   | 0.2 | -   | mA    |                |

# PAGE : 10/33

# **E. AC characteristics**

a. Input signal characteristics

Timing diagrams of input signal are shown in Fig 1 and Fig 2.

# 1. 280 mode

1-1. Input timing chart

|                | Parameter                   | Symbol | Min. | Тур.  | Max.  | Unit    | Remark |

|----------------|-----------------------------|--------|------|-------|-------|---------|--------|

|                | Frequency                   | 1/Tc   | -    | 5.67  | -     | MHz     |        |

| DCLK           | High time                   | Tch    | -    | -     | -     | ns      |        |

|                | Low time                    | Tcl    | -    | -     | -     | ns      |        |

|                | Period                      |        | 60   | 63.56 | 67    | $\mu$ s |        |

|                | renou                       | TH     | -    | 360   | -     | CLK     |        |

| HSD            | Display period              | THd    | -    | 49.4  | -     | $\mu$ s |        |

| 1150           | Display period              | тпи    |      | 280   |       | CLK     |        |

|                | Pulse width                 | ТНр    | 5    | 25    | -     | CLK     |        |

|                | Hsync-CLK timing            | THc    | 20   | -     | Tc-20 | ns      |        |

|                | Period                      | ΤV     | -    | 16.6  | -     | ms      |        |

|                | renou                       | IV     | -    | 262   | -     | TH      |        |

| VSD            | Display period              | TVd    | -    | 13.97 | -     | ms      |        |

|                | Display period              | TVU    |      | 220   |       | TH      |        |

|                | Pulse width                 | TVp    | 3    | -     | -     | TH      |        |

| DATA           | CLK-DATA timing             | Tds    | 10   | -     | -     | ns      |        |

| R0~R7          | DATA-CLK timing             | Tdh    | 10   | -     | -     | ns      |        |

| G0~G7<br>B0~B7 | Rising time<br>Falling time | Tdrf   | -    | -     | 10    | ns      |        |

# 1-2. Horizontal display position

1-2-1. ENAB mode:

The horizontal display position is determined by DEM signal and the input data corresponding to the rising edge of DEM.

| Parameter                  |             | Symbol | Min. | Тур. | Max. | Unit | Remark |

|----------------------------|-------------|--------|------|------|------|------|--------|

|                            | Setup time  | Tes    | -    | TBD  | -    | ns   |        |

| Enable signal              | Pulse width | Тер    | -    | 288  | -    | CLK  |        |

| Hsync-Enable signal timing |             | THe    | 33   | -    | 57   | CLK  |        |

1-2-2. Fix mode:

When DEM is fixed "Low", the display starts from the data of C62(clock) as shown in Fig 2. Be careful that the module does not work when DEM is fixed "High".

### 1-3. Vertical display position

| Parameter                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------------------|--------|------|------|------|------|--------|

| Vertical display position | TVS    |      | 25   |      | Н    | NTSC   |

| Vertical display position | 105    |      | 34   |      | Н    | PAL    |

# PAGE : 11/33

# 2. 480 mode

2-1. Input timing chart

|                | Parameter                   | Symbol | Min. | Тур.  | Max.  | Unit       | Remark |

|----------------|-----------------------------|--------|------|-------|-------|------------|--------|

|                | Frequency                   | 1/Tc   | -    | 9.70  | -     | MHz        |        |

| DCLK           | High time                   | Tch    | -    | -     | -     | ns         |        |

|                | Low time                    | Tcl    | -    | -     | -     | ns         |        |

|                | Period                      | ТН     | 60   | 63.56 | 67    | $\mu{f s}$ |        |

|                | renou                       | 111    | -    | 617   | -     | CLK        |        |

| HSD            | Display period              | THd    | -    | 49.4  | -     | $\mu$ s    |        |

| 1150           | Display period              | тпа    |      | 480   |       | CLK        |        |

|                | Pulse width                 | ТНр    | 5    | 44    | -     | CLK        |        |

|                | Hsync-CLK timing            | THc    | 20   | -     | Tc-20 | ns         |        |

|                | Period                      | ΤV     | -    | 16.6  | -     | ms         |        |

|                | renou                       | IV     | -    | 262   | -     | TH         |        |

| VSD            | Display period              | TVd    | -    | 14.83 | -     | ms         |        |

|                | Display period              | TVU    |      | 234   |       | TH         |        |

|                | Pulse width                 | TVp    | 3    | -     | -     | TH         |        |

| DATA           | CLK-DATA timing             | Tds    | 10   | -     | -     | ns         |        |

| R0~R7          |                             | Tdh    | 10   | -     | -     | ns         |        |

| G0~G7<br>B0~B7 | Rising time<br>Falling time | Tdrf   | -    | -     | 10    | ns         |        |

# 2-2. Horizontal display position

2-2-1. ENAB mode:

The horizontal display position is determined by DEM signal and the input data corresponding to the rising edge of DEM.

| Parameter                  |             | Symbol | Min. | Тур. | Max. | Unit | Remark |

|----------------------------|-------------|--------|------|------|------|------|--------|

| Enchle signal              | Setup time  | Tes    | -    | TBD  | -    | ns   |        |

| Enable signal              | Pulse width | Тер    | -    | 480  | -    | CLK  |        |

| Hsync-Enable signal timing |             | THe    | 60   | -    | 105  | CLK  |        |

#### 2-2-2. Fix mode:

When DEM is fixed "Low", the display starts from the data of C106(clock) as shown in Fig 2. Be careful that the module does not work when DEM is fixed "High".

#### 2-3. Vertical display position

| Parameter                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------------------|--------|------|------|------|------|--------|

| Vertical display position | TVC    | 18   |      |      | Н    | NTSC   |

| Vertical display position | TVS    |      | 27   |      | Н    | PAL    |

#### 3. 528 mode

3-1. Input timing chart

|      | Parameter        | Symbol | Min. | Тур.  | Max.  | Unit    | Remark |

|------|------------------|--------|------|-------|-------|---------|--------|

|      | Frequency        | 1/Tc   | -    | 10.7  | -     | MHz     |        |

| DCLK | High time        | Tch    | -    | -     | -     | ns      |        |

|      | Low time         | Tcl    | -    | -     | -     | ns      |        |

|      | Period           | ТН     | 60   | 63.56 | 67    | $\mu$ s |        |

|      | Fellou           | 111    | -    | 679   | -     | CLK     |        |

| HSD  | Display period   | THd    | -    | 49.4  | -     | $\mu$ s |        |

| HOD  | Display period   | THU    |      | 528   |       | CLK     |        |

|      | Pulse width      | THp    | 5    | 48    | -     | CLK     |        |

|      | Hsync-CLK timing | THc    | 20   | -     | Tc-20 | ns      |        |

# PAGE : 12/33

|                | Period                      | ΤV   | -  | 16.6  | -  | ms |  |

|----------------|-----------------------------|------|----|-------|----|----|--|

|                | renou                       | IV   | -  | 262   | -  | TH |  |

| VSD            | Display period              | TVd  | -  | 13.97 | -  | ms |  |

|                | Display period              | TVU  |    | 220   |    | TH |  |

|                | Pulse width                 | TVp  | 3  | -     | -  | TH |  |

| DATA           | CLK-DATA timing             | Tds  | 10 | -     | -  | ns |  |

|                | DATA-CLK timing             | Tdh  | 10 | -     | -  | ns |  |

| G0~G7<br>B0~B7 | Rising time<br>Falling time | Tdrf | -  | -     | 10 | ns |  |

### 3-2. Horizontal display position

3-2-1. ENAB mode:

The horizontal display position is determined by DEM signal and the input data corresponding to the rising edge of DEM.

| Parameter     |                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------|-----------------|--------|------|------|------|------|--------|

| Enable signal | Setup time      | Tes    | -    | TBD  | -    | ns   |        |

|               | Pulse width     | Тер    | -    | 576  | -    | CLK  |        |

| Hsync-Enabl   | e signal timing | THe    | 57   | -    | 90   | CLK  |        |

3-2-2. Fix mode:

When DEM is fixed "Low", the display starts from the data of C118(clock) as shown in Fig 2. Be careful that the module does not work when DEM is fixed "High".

### 3-3. Vertical display position

| Parameter                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------------------|--------|------|------|------|------|--------|

| Vertical display position | TVS    | 25   |      |      | Н    | NTSC   |

|                           | 103    | 34   |      |      | Н    | PAL    |

# 4. 1152 mode

### 4-1. Input timing chart

| Pa             | arameter                    | Symbol | Min. | Тур.  | Max.  | Unit       | Remark |

|----------------|-----------------------------|--------|------|-------|-------|------------|--------|

|                | Frequency                   | 1/Tc   | -    | 23.3  | -     | MHz        |        |

| DCLK           | High time                   | Tch    | -    | -     | -     | ns         |        |

|                | Low time                    | Tcl    | -    | -     | -     | ns         |        |

|                | Period                      | ТН     | 60   | 63.56 | 67    | $\mu{f s}$ |        |

|                | renou                       | 111    | -    | 1482  | -     | CLK        |        |

| HSD            | Display pariod              | THd    | -    | 49.4  | -     | $\mu{f s}$ |        |

| 1150           | Display period              | ТПО    |      | 1152  |       | CLK        |        |

|                | Pulse width                 | ТНр    | 5    | 109   | -     | CLK        |        |

|                | Hsync-CLK timing            | THc    | 20   | -     | Tc-20 | ns         |        |

|                | Period                      | ΤV     | -    | 16.6  | -     | ms         |        |

|                | r enou                      | IV     | -    | 262   | -     | TH         |        |

| VSD            | Display period              | TVd    | -    | 14.83 | -     | ms         |        |

|                | Display period              |        | 234  |       |       | TH         |        |

|                | Pulse width                 | TVp    | 3    | -     | -     | TH         |        |

| DATA           | CLK-DATA timing             | Tds    | 10   | -     | -     | ns         |        |

| R0~R7          | DATA-CLK timing             | Tdh    | 10   | -     | -     | ns         |        |

| G0~G7<br>B0~B7 | Rising time<br>Falling time | Tdrf   | -    | -     | 10    | ns         |        |

# PAGE : 13/33

# 4-2. Horizontal display position

# 4-2-1. ENAB mode:

The horizontal display position is determined by DEM signal and the input data corresponding to the rising edge of DEM.

| Parameter     |                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------|-----------------|--------|------|------|------|------|--------|

|               | Setup time      | Tes    | -    | TBD  | -    | ns   |        |

| Enable signal | Pulse width     | Тер    | -    | 1152 | -    | CLK  |        |

| Hsync-Enable  | e signal timing | THe    | 108  | -    | 243  | CLK  |        |

4-2-2. Fix mode:

When DEM is fixed "Low", the display starts from the data of C247(clock) as shown in Fig 2. Be careful that the module does not work when DEM is fixed "High".

### 4-3. Vertical display position

| Parameter                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------------------|--------|------|------|------|------|--------|

| Vertical display position | TVC    | 18   |      |      | Н    | NTSC   |

|                           | TVS    | 27   |      |      | Н    | PAL    |

### 5. 960 mode

5-1. Input timing chart

|                | Parameter                   | Symbol | Min. | Тур.  | Max.  | Unit    | Remark |

|----------------|-----------------------------|--------|------|-------|-------|---------|--------|

|                | Frequency                   | 1/Tc   | -    | 19.4  | -     | MHz     |        |

| DCLK           | High time                   | Tch    | -    | -     | -     | ns      |        |

|                | Low time                    | Tcl    | -    | -     | -     | ns      |        |

|                | Period                      | ТН     | 60   | 63.56 | 67    | $\mu$ S |        |

|                | renou                       |        | -    | 1235  | -     | CLK     |        |

| HSD            | Diaplay pariod              | тца    | -    | 49.4  | -     | $\mu$ S |        |

|                | Display period              | THd    |      | 960   |       | CLK     |        |

|                | Pulse width                 | THp    | 5    | 91    | -     | CLK     |        |

|                | Hsync-CLK timing            | THc    | 20   | -     | Tc-20 | ns      |        |

|                | Period                      | ΤV     | -    | 16.6  | -     | ms      |        |

|                | renou                       | IV     | -    | 262   | -     | TH      |        |

| VSD            | Display period              | TVd    | -    | 14.83 | -     | ms      |        |

|                | Display period              | TVU    |      | 234   | 234   |         |        |

|                | Pulse width                 | TVp    | 3    | -     | -     | TH      |        |

| DATA           | CLK-DATA timing             | Tds    | 10   | -     | -     | ns      |        |

| R0~R7          | DATA-CLK timing             | Tdh    | 10   | -     | -     | ns      |        |

| G0~G7<br>B0~B7 | Rising time<br>Falling time | Tdrf   | -    | -     | 10    | ns      |        |

### 5-2. Horizontal display position

5-2-1. ENAB mode:

The horizontal display position is determined by DEM signal and the input data corresponding to the rising edge of DEM.

| Pa            | Parameter         |     | Min. | Тур. | Max. | Unit | Remark |

|---------------|-------------------|-----|------|------|------|------|--------|

| Enable signal | Setup time        | Tes | -    | TBD  | -    | ns   |        |

| Enable signal | Pulse width       | Тер | -    | 960  | -    | CLK  |        |

| Hsync-Ena     | ble signal timing | THe | 97   | -    | 204  | CLK  |        |

5-2-2. Fix mode:

When DEM is fixed "Low", the display starts from the data of C207(clock) as shown in Fig 2. Be careful that the module does not work when DEM is fixed "High".

# PAGE : 14/33

| 5-3. Ver | tical display position    |        |      |      |      |      |        |

|----------|---------------------------|--------|------|------|------|------|--------|

|          | Parameter                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|          | Vortical display position | TVS    |      | 18   |      | Н    | NTSC   |

|          | Vertical display position |        | 27   |      |      | Н    | PAL    |

# 6. 1440 mode

# 6-1. Input timing chart

|                | Parameter                   | Symbol | Min. | Тур.  | Max.  | Unit       | Remark |

|----------------|-----------------------------|--------|------|-------|-------|------------|--------|

|                | Frequency                   | 1/Tc   | -    | 29.1  | -     | MHz        |        |

| DCLK           | High time                   | Tch    | -    | -     | -     | ns         |        |

|                | Low time                    | Tcl    | -    | -     | -     | ns         |        |

|                | Period                      | ТН     | 60   | 63.56 | 67    | $\mu{f s}$ |        |

|                | renou                       |        | -    | 1853  | -     | CLK        |        |

| HSD            | Diaplay pariod              | THd    | -    | 49.4  | -     | $\mu{f s}$ |        |

| 1130           | SD Display period           |        |      | 1440  |       | CLK        |        |

|                | Pulse width                 | ТНр    | 5    | 137   | -     | CLK        |        |

|                | Hsync-CLK timing            | THc    | 20   | -     | Tc-20 | ns         |        |

|                | Period                      | ΤV     | -    | 16.6  | -     | ms         |        |

|                | renou                       | IV     | -    | 262   | -     | TH         |        |

| VSD            | Display period              | TVd    | -    | 14.83 | -     | ms         |        |

|                | Display period              | TVU    |      | 234   |       | TH         |        |

|                | Pulse width                 | TVp    | 3    | -     | -     | TH         |        |

| DATA           | CLK-DATA timing             | Tds    | 10   | -     | -     | ns         |        |

| R0~R7          | DATA-CLK timing             | Tdh    | 10   | -     | -     | ns         |        |

| G0~G7<br>B0~B7 | Rising time<br>Falling time | Tdrf   | -    | -     | 10    | ns         |        |

# 6-2. Horizontal display position

# 6-2-1. ENAB mode:

The horizontal display position is determined by DEM signal and the input data corresponding to the rising edge of DEM.

| Parameter     |                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------|-----------------|--------|------|------|------|------|--------|

| Enchla signal | Setup time      | Tes    | -    | TBD  | -    | ns   |        |

| Enable signal | Pulse width     | Тер    | -    | 1440 | -    | CLK  |        |

| Hsync-Enable  | e signal timing | THe    | 145  | -    | 305  | CLK  |        |

6-2-2. Fix mode:

When DEM is fixed "Low", the display starts from the data of C309(clock) as shown in Fig 2. Be careful that the module does not work when DEM is fixed "High".

#### 6-3. Vertical display position

| Parameter                 | Symbol | Min. | Тур. | Max. | Unit | Remark |

|---------------------------|--------|------|------|------|------|--------|

| Vertical diaplay position |        | 18   |      |      | Н    | NTSC   |

| Vertical display position | TVS    |      | 27   |      | Н    | PAL    |

man 12

# PAGE : 15/33

# b. Output signal characteristics

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Remark            |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|-------------------|

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note 1            |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note 1            |

| Clock high and low level<br>pulse width    | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CPH3_<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CPH3_<br>OUT |

| 3 $\varphi$ clock phase difference         | <sup>t</sup> C12<br>t <sub>C23</sub><br>t <sub>C31</sub> | -    | t <sub>CPH</sub> /3 | -    | ns                |                   |

| STH setup time                             | <sup>t</sup> SUH                                         | -    | t <sub>CPH</sub> /6 | -    | ns                |                   |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                   |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 3                   | -    | <sup>t</sup> CPH  |                   |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 11                  | -    | <sup>t</sup> CPH  |                   |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 5                   | -    | <sup>t</sup> CPH  |                   |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 5                   | -    | <sup>t</sup> CPH  |                   |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 8                   | -    | <sup>t</sup> CPH  |                   |

| HSD/I-V_CK timing difference               | t <sub>2</sub>                                           | -    | 6                   | -    | <sup>t</sup> CPH  |                   |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 2                   | -    | <sup>t</sup> CPH  |                   |

| STV setup time                             | <sup>t</sup> SUV                                         | -    | 3                   | -    | <sup>t</sup> CPH  |                   |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                   |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tн                |                   |

| VSD/I-STVL timing<br>difference(V_DIR="H") | <sup>t</sup> VS2                                         | -    | 20                  | -    | tн                |                   |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tH                |                   |

Note 1: For all of the logic signals.

# PAGE : 16/33

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Remark           |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|------------------|

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note 1           |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note 1           |

| Clock high and low level<br>pulse width    | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CPH3<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CPH3<br>OUT |

| 3 $\varphi$ clock phase difference         | <sup>t</sup> C12<br>t <sub>C23</sub><br>t <sub>C31</sub> | -    | t <sub>CPH</sub> /3 | -    | ns                |                  |

| STH setup time                             | <sup>t</sup> SUH                                         | -    | t <sub>CPH</sub> /6 | -    | ns                |                  |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                  |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 6                   | -    | <sup>t</sup> CPH  |                  |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 17                  | -    | <sup>t</sup> CPH  |                  |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 10                  | -    | <sup>t</sup> CPH  |                  |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 7                   | -    | <sup>t</sup> CPH  |                  |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 12                  | -    | <sup>t</sup> CPH  |                  |

| HSD/I-V_CK timing difference               | t2                                                       | -    | 11                  | -    | <sup>t</sup> CPH  |                  |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 2                   | -    | <sup>t</sup> CPH  |                  |

| STV setup time                             | tSUV                                                     | -    | 8                   | -    | <sup>t</sup> CPH  |                  |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                  |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tн                |                  |

| VSD/I-STVL timing<br>difference(V_DIR="H") | <sup>t</sup> VS2                                         | -    | 20                  | -    | tн                |                  |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tн                |                  |

Note 1: For all of the logic signals.

# PAGE : 17/33

| 480 mode (4.0")                            |                                                          |      |                     |      |                   |                   |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|-------------------|

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Remark            |

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note 1            |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note 1            |

| Clock high and low level<br>pulse width    | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CPH3_<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CPH3_<br>OUT |

| 3 $\varphi$ clock phase difference         | <sup>t</sup> C12<br><sup>t</sup> C23<br><sup>t</sup> C31 | -    | t <sub>CPH</sub> /3 | -    | ns                |                   |

| STH setup time                             | <sup>t</sup> SUH                                         | -    | t <sub>CPH</sub> /6 | -    | ns                |                   |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                   |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 4                   | -    | <sup>t</sup> CPH  |                   |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 14                  | -    | <sup>t</sup> CPH  |                   |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 14                  | -    | <sup>t</sup> CPH  |                   |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 25                  | -    | <sup>t</sup> CPH  |                   |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 17                  | -    | <sup>t</sup> CPH  |                   |

| HSD/I-V_CK timing difference               | t <sub>2</sub>                                           | -    | 10                  | -    | <sup>t</sup> CPH  |                   |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 2                   | -    | <sup>t</sup> CPH  |                   |

| STV setup time                             | <sup>t</sup> SUV                                         | -    | 7                   | -    | <sup>t</sup> CPH  |                   |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                   |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tн                |                   |

| VSD/I-STVL timing<br>difference(V_DIR="H") | <sup>t</sup> VS2                                         | -    | 20                  | -    | tн                |                   |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tн                |                   |

Note 1: For all of the logic signals.

# PAGE : 18/33

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Rema           |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|----------------|

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note           |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note           |

| Clock high and low level<br>pulse width    | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CF<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CF<br>OUT |

| 3 $\varphi$ clock phase difference         | <sup>t</sup> C12<br><sup>t</sup> C23<br><sup>t</sup> C31 | -    | t <sub>CPH</sub> /3 | -    | ns                |                |

| STH setup time                             | <sup>t</sup> SUH                                         | -    | t <sub>CPH</sub> /6 | -    | ns                |                |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 6                   | -    | <sup>t</sup> CPH  |                |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 11                  | -    | <sup>t</sup> CPH  |                |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 11                  | -    | <sup>t</sup> CPH  |                |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 13                  | -    | <sup>t</sup> CPH  |                |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 14                  | -    | <sup>t</sup> CPH  |                |

| HSD/I-V_CK timing difference               | t <sub>2</sub>                                           | -    | 9                   | -    | <sup>t</sup> CPH  |                |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 2                   | -    | <sup>t</sup> CPH  |                |

| STV setup time                             | <sup>t</sup> SUV                                         | -    | 6                   | -    | <sup>t</sup> CPH  |                |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tH                |                |

| VSD/I-STVL timing<br>difference(V_DIR="H") | <sup>t</sup> VS2                                         | -    | 20                  | -    | tн                |                |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tH                |                |

Note 1: For all of the logic signals.

# PAGE : 19/33

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Remark          |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|-----------------|

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note 1          |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note 1          |

| Clock high and low level pulse width       | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CPH<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CPH<br>OUT |

| $3 \varphi$ clock phase difference         | <sup>t</sup> C12<br><sup>t</sup> C23<br><sup>t</sup> C31 | -    | t <sub>CPH</sub> /3 | -    | ns                |                 |

| STH setup time                             | <sup>t</sup> SUH                                         | -    | tCPH /6             | -    | ns                |                 |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                 |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 12                  | -    | <sup>t</sup> CPH  |                 |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 24                  | -    | <sup>t</sup> CPH  |                 |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 39                  | -    | <sup>t</sup> CPH  |                 |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 60                  | -    | <sup>t</sup> CPH  |                 |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 46                  | -    | <sup>t</sup> CPH  |                 |

| HSD/I-V_CK timing difference               | t <sub>2</sub>                                           | -    | 22                  | -    | <sup>t</sup> CPH  |                 |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 4                   | -    | <sup>t</sup> CPH  |                 |

| STV setup time                             | <sup>t</sup> SUV                                         | -    | 15                  | -    | <sup>t</sup> CPH  |                 |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                 |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tн                |                 |

| VSD/I-STVL timing<br>difference(V_DIR="H") | t <sub>VS2</sub>                                         | -    | 20                  | -    | tH                |                 |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tH                |                 |

Note 1: For all of the logic signals.

# PAGE : 20/33

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Remar          |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|----------------|

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note ?         |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note '         |

| Clock high and low level<br>pulse width    | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CP<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CP<br>OUT |

| 3 $\varphi$ clock phase difference         | <sup>t</sup> C12<br>t <sub>C23</sub><br>t <sub>C31</sub> | -    | t <sub>CPH</sub> /3 | -    | ns                |                |

| STH setup time                             | <sup>t</sup> SUH                                         | -    | tCPH /6             | -    | ns                |                |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 8                   | -    | <sup>t</sup> CPH  |                |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 29                  | -    | <sup>t</sup> CPH  |                |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 28                  | -    | <sup>t</sup> CPH  |                |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 50                  | -    | <sup>t</sup> CPH  |                |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 33                  | -    | <sup>t</sup> CPH  |                |

| HSD/I-V_CK timing difference               | t <sub>2</sub>                                           | -    | 19                  | -    | <sup>t</sup> CPH  |                |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 3                   | -    | <sup>t</sup> CPH  |                |

| STV setup time                             | <sup>t</sup> SUV                                         | -    | 15                  | -    | <sup>t</sup> CPH  |                |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tH                |                |

| VSD/I-STVL timing<br>difference(V_DIR="H") | <sup>t</sup> VS2                                         | -    | 20                  | -    | tH                |                |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tH                |                |

Note 1: For all of the logic signals.

PAGE : 21/33

| Parameter                                  | Symbol                                                   | Min. | Тур.                | Max. | Unit.             | Remark           |

|--------------------------------------------|----------------------------------------------------------|------|---------------------|------|-------------------|------------------|

| Rising time                                | t <sub>r</sub>                                           | -    | -                   | 10   | ns                | Note 1           |

| Falling time                               | t <sub>f</sub>                                           | -    | -                   | 10   | ns                | Note 1           |

| Clock high and low level<br>pulse width    | <sup>t</sup> CPH                                         | -    | 3                   | -    | <sup>t</sup> DCLK | CPH1~CPH3<br>OUT |

| Clock pulse duty                           | <sup>t</sup> CWH                                         | 40   | 50                  | 60   | %                 | CPH1~CPH3<br>OUT |

| 3 $\varphi$ clock phase difference         | <sup>t</sup> C12<br>t <sub>C23</sub><br>t <sub>C31</sub> | -    | t <sub>CPH</sub> /3 | -    | ns                |                  |

| STH setup time                             | <sup>t</sup> S∪H                                         | -    | t <sub>CPH</sub> /6 | -    | ns                |                  |

| STH pulse width                            | <sup>t</sup> STH                                         | -    | 1                   | -    | <sup>t</sup> CPH  |                  |

| HOE_OUT pulse width                        | <sup>t</sup> OEH                                         | -    | 12                  | -    | <sup>t</sup> CPH  |                  |

| Sample & hold disable time                 | <sup>t</sup> DIS1                                        | -    | 42                  | -    | <sup>t</sup> CPH  |                  |

| VOE_OUT pulse width                        | <sup>t</sup> OEV                                         | -    | 42                  | -    | <sup>t</sup> CPH  |                  |

| V_CK pulse width                           | <sup>t</sup> CKV                                         | -    | 75                  | -    | <sup>t</sup> CPH  |                  |

| HSD/I-HOE_OUT timing<br>difference         | t <sub>1</sub>                                           | -    | 49                  | -    | <sup>t</sup> CPH  |                  |

| HSD/I-V_CK timing difference               | t <sub>2</sub>                                           | -    | 28                  | -    | <sup>t</sup> CPH  |                  |

| HSD/I-VOE_OUT timing<br>difference         | t <sub>3</sub>                                           | -    | 4                   | -    | <sup>t</sup> CPH  |                  |

| STV setup time                             | <sup>t</sup> SUV                                         | -    | 15                  | -    | <sup>t</sup> CPH  |                  |

| STV pulse width                            | <sup>t</sup> STV                                         | -    | 1                   | -    | tH                |                  |

| VSD/I-STVR timing<br>difference(V_DIR="L") | <sup>t</sup> VS1                                         | -    | 16                  | -    | tн                |                  |

| VSD/I-STVL timing<br>difference(V_DIR="H") | <sup>t</sup> VS2                                         | -    | 20                  | -    | tн                |                  |

| HOE-STV timing difference                  | <sup>t</sup> OES                                         | -    | 2                   | -    | tH                |                  |

Note 1: For all of the logic signals.

c. Video signal output characteristics(refer to the attached drawing Fig.7)

| Item                   | Symbol | Min. | Тур. | Max. | Unit. | Remark       |

|------------------------|--------|------|------|------|-------|--------------|

| Video signal amplitude | VIAC   | -    | 3.5  | -    | V     | AC Component |

| (Vout1, Vout2, Vout3)  | VIDC   | -    | 3.15 | -    | V     | DC Component |

PAGE : 22/33

# F. Color sequence for different resolution modes:

# a. Delta type arrangement color filter :

Due to the "Delta" type arrangement of LCD's color filter, the R.G.B data are different in odd lines and even lines. Please follow the corresponding sequence under different conditions which are shown in Tab.1

Tab.1 Color sequence for different resolution modes. (Delta type)

| Scanning direction control setting                 | V_DIR (Note 1) | Low   | Low   | High  | High  |

|----------------------------------------------------|----------------|-------|-------|-------|-------|

| Display modules                                    | H_DIR (Note 2) | High  | Low   | High  | Low   |

| 4": 480 <sub>X</sub> 234<br>(UP40DXX)              | Odd Line       | BRG   | G R B | G B R | R B G |

|                                                    | Even Line      | G B R | R B G | B R G | G R B |

| 1.8": 280× 220<br>(SM26X Series)<br>2.0": 528× 220 | Odd Line       | R G B | BGR   | G B R | R B G |

| (UP20DXX)<br>2.5": 480x 234<br>(UP25DXX)           | Even Line      | G B R | R B G | R G B | BGR   |

Note 1: V\_DIR is an Up/Down scanning direction control pin of UPS051.

When V\_DIR is high , the scanning direction control is from "Down to Up ". When V\_DIR is low , the scanning direction control is from "Up to Down ".

Note 2: H\_DIR is a Left/Right scanning direction control pin of UPS051. When LR is high, the scanning direction is from "left to Right".

When LR is low, the scanning direction is from "right to Left".

- Note 3: The sequence specified in each column represents the order of data which should be sent to UPS051 for cycle #1, 2, 3, 4, 5,

- Note 4: The Q1H\_OUT (Pin 15) signal can be used as the index to specify odd line or even line for users.

PAGE : 23/33

# b. Stripe type arrangement color filter

The R.G.B sequences are same in odd line and even line in stripe type arrangement color filter.

Tab.2 Color sequence for different resolution modes. (Stripe type)

| Display module                                                                                   | H_DIR                 | High  | Low   |

|--------------------------------------------------------------------------------------------------|-----------------------|-------|-------|

| 6.8" : 1152× 234<br>(UP68DXX)<br>5.6" : 960× 234<br>(UP056DXX)<br>7.0" : 1440× 234<br>(UP070DXX) | Odd line<br>Even line | R G B | B G R |

# G. Reliability test item: