查询CD4015BE供应商

捷多邦,专业PCB打样工厂,24小时加急出货

# Data sheet acquired from Harris Semiconductor SCHS025

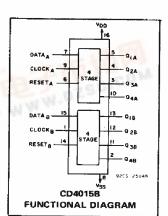

# CMOS Dual 4-Stage Static Shift Register

With Serial Input/Parallel Output

High-Voltage Types (20-Volt Rating)

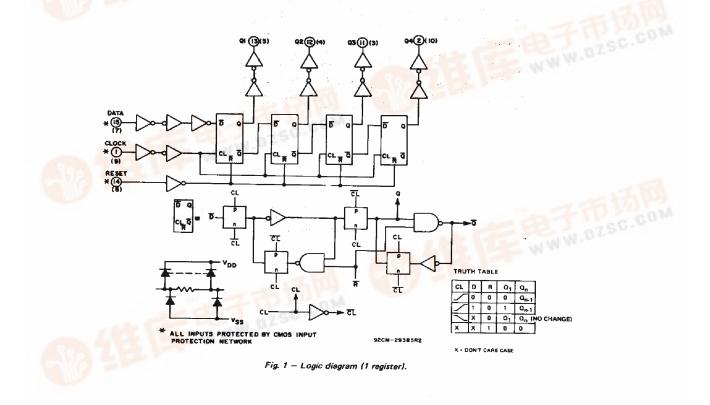

CD4015B consists of two identical. independent, 4-stage serial-input/paralleloutput registers. Each register has independent CLOCK and RESET inputs as well as a single serial DATA input. "Q" outputs are available from each of the four stages on both registers. All register stages are D-type, master-slave flip-flops. The logic level present at the DATA input is transferred into the first register stage and shifted over one stage at each positive-going clock transition. Resetting of all stages is accomplished by a high level on the reset line. Register expansion to 8 stages using one CD4015B package, or to more than 8 stages using additional CD4015B's is possible.

The CD4015B-series types are supplied in 16-lead hermetic dual-in-line ceramic packages (D and F suffixes), 16-lead dual-in-line plastic package (E suffix), and in chip form (H suffix).

### Features:

- Fully static operation

- 8 master-slave flip-flops plus input and output buffering

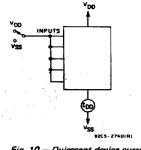

- 100% tested for quiescent current at 20 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) =

- 1 V at V<sub>DD</sub> = 5 V

- 2 V at V<sub>DD</sub> = 10 V

- 2.5 V at V<sub>DD</sub> = 15 V

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

### Applications:

- Serial-input/parallel-output data queueing

- Serial to parallel data conversion

- General-purpose register

#### TERMINAL DIAGRAM

|     |         |   | <u> </u> | $\neg$ |      | 1        |         |

|-----|---------|---|----------|--------|------|----------|---------|

|     | CLOCK B |   | 1.       |        | 16   |          | VDD     |

|     | Q4 B    |   | 2        |        | 15   |          | ÔATA B  |

|     | Q3A     |   | 3        |        | 14   | <b>-</b> | RESET B |

|     | Q2 A    | _ | 4        |        | 13   |          | Q ! B   |

|     | QIA     | - | 5        |        | 12   |          | 02.8    |

| ÷., | RESETA  |   | 6        |        | - 11 | _        | Q38     |

|     | DATA A  | - | 7        |        | 10   |          | Q4 A    |

|     | Vss     | _ | θ        |        | 9    |          | CLOCK A |

|     |         |   |          |        |      |          |         |

| ٠.  |         |   |          |        | ,    | acs      | -24457  |

# CD4015B Types

# CD4015B Types

| MAXIMUM RATINGS, Absolute-Maximum Values:                                  |      |

|----------------------------------------------------------------------------|------|

| DC SUPPLY-VOLTAGE RANGE, (VDD)                                             |      |

| Voltages referenced to V <sub>SS</sub> Terminal)0.5V to +                  | 20V  |

| INPUT VOLTAGE RANGE, ALL INPUTS                                            | 0.5V |

| DC INPUT CURRENT, ANY ONE INPUT                                            | JmA  |

| POWER DISSIPATION PER PACKAGE (PD):                                        |      |

| For $T_A = -55^{\circ}C$ to $+100^{\circ}C$                                | mŴ   |

| For T <sub>A</sub> = +100°C to +125°C Derate Linearity at 12mW/°C to 200   | mW   |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                   |      |

| FOR T <sub>A</sub> = FULL PACKAGE-TEMPERATURE RANGE (All Package Types)    | mW   |

| OPERATING-TEMPERATURE RANGE (TA)                                           | 5°C  |

| STORAGE TEMPERATURE RANGE (Tstg)65°C to +150                               |      |

| LEAD TEMPERATURE (DURING SOLDERING):                                       |      |

| At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79mm) from case for 10s max | 5°C  |

3

COMMERCIAL CMOS HIGH VOLTAGE ICS

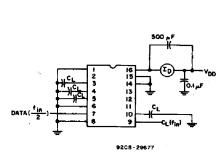

Fig. 4 Typical output high (source) current characteristics.

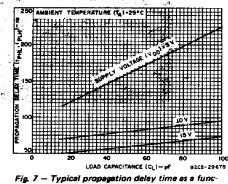

Fig. 7 — Typical propagation delay time as a func-tion of load-capacitance,

| RECOMMENDED          | OPERATING CONDITIO        | NS at T <sub>A</sub> = | <sup>250</sup> C, Except as Noted. F | or maximum      |

|----------------------|---------------------------|------------------------|--------------------------------------|-----------------|

| reliability, nominal | operating conditions shou | Id be selec            | ted so that operation is alv         | vays within the |

| following ranges:    |                           |                        |                                      | -               |

| CHARACTERISTIC                                                 |                                      | V <sub>DD</sub> | LIMITS          |               | UNITS |

|----------------------------------------------------------------|--------------------------------------|-----------------|-----------------|---------------|-------|

|                                                                | . (v)                                | Min.            | Max.            | 1             |       |

| Supply-Voltage Range (For T <sub>A</sub><br>Temperature Range) |                                      | 3               | 18              | v             |       |

| Clock Pulse Width,                                             | t <sub>W</sub> CL                    | 5<br>10<br>15   | 180<br>80<br>50 |               | ns    |

| Clock Rise and Fall Time,                                      | t <sub>r</sub> CL, t <sub>f</sub> CL | 5<br>10<br>15   |                 | 15<br>6<br>2  | μs    |

| Clock Input Frequency,                                         | fCL                                  | 5<br>10<br>15   | DC              | 3<br>6<br>8.5 | MHz   |

| Data Setup Time,                                               | ts∪                                  | 5<br>10<br>15   | 70<br>40<br>30  | -             | ns    |

| Reset Pulse Width,                                             | t <sub>W</sub> R                     | 5<br>10<br>15   | 200<br>80<br>60 | -             |       |

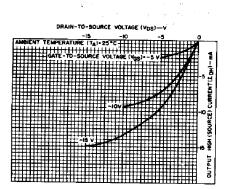

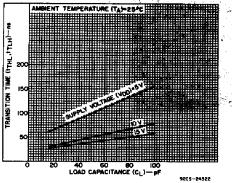

Fig. 6 — Typical transition time as a function of load capacitance.

## CD4015B Types

| CHARACTER                 | CONDITIONS |      |     | LIMITS AT INDICATED TEMPERATURES ( <sup>O</sup> C) |       |       |       |       |                  | 1.00 |     |  |  |

|---------------------------|------------|------|-----|----------------------------------------------------|-------|-------|-------|-------|------------------|------|-----|--|--|

| ISTIC                     | Vo         | VIN  | VDD |                                                    |       |       |       | +25   |                  |      |     |  |  |

|                           | (v)        | (V)  | (v) | 55                                                 | -40   | +85   | +125  | Min.  | Typ.             | Max. |     |  |  |

| Quiescent Device          | -          | 0,5  | 5   | 5                                                  | 5     | 150   | 150   | _     | 0.04             | 5    | μΑ  |  |  |

| Current,                  | -          | 0,10 | 10  | 10                                                 | 10    | 300   | 300   | -     | 0.04             | 10   |     |  |  |

| IDD Max.                  | -          | 0,15 | 15  | 20                                                 | 20    | 600   | 600   | -     | 0.04             | 20   |     |  |  |

|                           | · -        | 0,20 | 20  | 100                                                | 100   | 3000  | 3000  | -     | 0.08             | 100  |     |  |  |

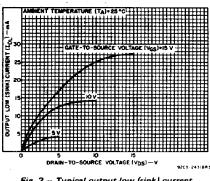

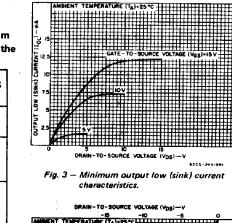

| Output Low                | 0.4        | 0,5  | 5   | 0.64                                               | 0.61  | 0.42  | 0.36  | 0.51  | 1                | -    | t   |  |  |

| (Sink) Current            | 0.5        | 0,10 | 10  | 1.6                                                | 1.5   | 1.1   | 0.9   | 1.3   | 2.6              | - 1  |     |  |  |

| IOL Min.                  | 1.5        | 0,15 | 15  | 4.2                                                | 4     | 2.8   | 2.4   | 3.4   | 6.8              |      | mA  |  |  |

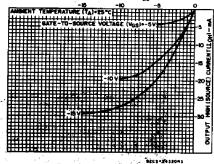

| Output High               | 4,6        | 0,5  | 5   | -0.64                                              | -0.61 | -0.42 | -0.36 | -0.51 | -1               | -    |     |  |  |

| (Source)                  | 2.5        | 0,5  | 5   | -2                                                 | -1.8  | -1.3  | -1.15 | -1.6  | -3.2             | -    |     |  |  |

| Current,                  | 9.5        | 0,10 | 10  | -1.6                                               | -1.5  | -1.1  | -0.9  | -1.3  | -2.6             | -    |     |  |  |

| IOH Min.                  | 13.5       | 0,15 | 15  | -4.2                                               | -4    | -2.8  | -2.4  | -3.4  | -6.8             | -    |     |  |  |

| Output Voltage:           | _          | 0,5  | 5   |                                                    | 0     | .05   |       | -     | 0                | 0.05 | .05 |  |  |

| Low-Level,<br>Vol. Max.   |            | 0,10 | 10  | 0.05                                               |       |       | -     | 0     | 0.05             |      |     |  |  |

| AOF Max.                  | _          | 0,15 | 15  |                                                    | 0     | .05   |       | -     | 0                | 0.05 |     |  |  |

| Output Voltage:           | _          | 0,5  | 5   | 4.95 4.95 5 -                                      |       |       |       | -     |                  |      |     |  |  |

| High-Level,               |            | 0,10 | 10  |                                                    | 9     | .95   |       | 9.95  | 10               | -    | 1   |  |  |

| VOH Min.                  | -          | 0,15 | 15  | 14.95                                              |       |       | 14.95 | 15    | -                |      |     |  |  |

| Input Low                 | 0.5, 4.5   | -    | 5   |                                                    | 1     | 1.5   |       | -     | _                | 1.5  |     |  |  |

| Voltage,                  | 1, 9       | - •  | 10  |                                                    |       | 3     |       | -     | -                | 3    | 1   |  |  |

| VIL Max.                  | 1.5,13.5   | -    | 15  |                                                    |       | 4     |       | -     | -                | 4    |     |  |  |

| Input High                | 0.5, 4.5   |      | 5   |                                                    | 3     | 3.5   |       | 3.5   | —                |      | 1 V |  |  |

| Voltage,                  | 1, 9       | _    | 10  |                                                    |       | 7     |       | 7     | -                | - 1  |     |  |  |

| VIH Min.                  | 1.5,13.5   | -    | 15  |                                                    |       | 11    |       | 11    |                  | - 1  | ]   |  |  |

| Input Current<br>IIN Max. | -          | 0,18 | 18  | ±0.1                                               | ±0.1  | ±1    | ±1    | -     | ±10 <sup>5</sup> | ±0.1 | Αμ  |  |  |

### STATIC ELECTRICAL CHARACTERISTICS

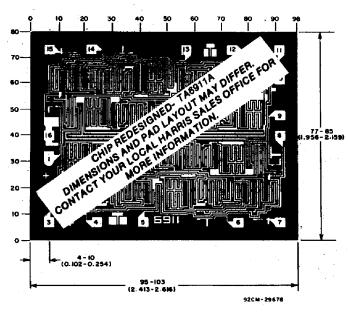

Photograph of Chip Layout for CD4015B.

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils ( $10^{-3}$  inch).

## DYNAMIC ELECTRICAL CHARACTERISTICS at TA = 25°C, Input tate = 20 ns,

$C_{\rm L}$  = 50 pF,  $R_{\rm L}$  = 200 k $\Omega$

| CHARACTERISTIC                         | TEST CONDITIONS |           |     |          |         |  |

|----------------------------------------|-----------------|-----------|-----|----------|---------|--|

| CHARACTERISTIC                         | V DD (V)        | MIN. TYP. |     | MAX.     | UNITS   |  |

| CLOCKED OPERATION                      |                 |           |     | <b>.</b> | ···     |  |

| Propagation Delay Time,                | 5               | —         | 160 | 320      |         |  |

|                                        | 10              | —         | 80  | 160      |         |  |

|                                        | 15              | —         | 60  | 120      |         |  |

|                                        | 5               | _         | 100 | 200      |         |  |

| Transition Time, true, true            | 10              | _         | 50  | 100      | ns      |  |

|                                        | 15              | —         | 40  | 80       |         |  |

| Minimum Clock Pulse                    | 5               | _         | 90  | 180      |         |  |

| Width, twCL                            | 10              | _         | 40  | 80       |         |  |

| ,                                      | 15              | —         | 25  | 50       |         |  |

| Clock Rise and Fall Time,              | 5               | -         |     | 15       |         |  |

| t,CL, t <sub>f</sub> CL*               | 10              | _         |     | 6        | μs      |  |

|                                        | 15              | —         | - 1 | 2        |         |  |

| Minimum Data Setup Time,               | 5               |           | 35  | 70       | <b></b> |  |

| tSU                                    | 10              | -         | 20  | 40       |         |  |

|                                        | . 15            |           | 15  | 30 -     |         |  |

|                                        | 5               | -         |     | 0        | ns      |  |

| Minimum Data Hold Time, t <sub>H</sub> | 10              | —         | _   | 0        |         |  |

|                                        | 15              | —         | ·   | 0        |         |  |

| Maximum Clock Input                    | 5               | 3         | 6   | -        |         |  |

| Frequency, f <sub>cL</sub>             | 10              | 6         | 12  | _        | MHz     |  |

|                                        | 15              | 8.5       | 17  | -        |         |  |

| Input Capacitance, CIN                 | Any Input       | _         | 5   | 7.5      | p۴      |  |

| RESET OPERATION                        |                 |           |     |          |         |  |

| Propagation Delay Time,                | 5               | _         | 200 | 400      |         |  |

| TPHL, TPLH                             | 10              |           | 100 | 200      |         |  |

|                                        | 15              | _         | 80  | 160      |         |  |

| Minimum Reset Pulse Width,             | 5               | _         | 100 | 200      | ns      |  |

| t <sub>w</sub> R                       | 10              | _         | 40  | 80       |         |  |

|                                        | 15              |           | 30  | 60       |         |  |

\*If more than one unit is cascaded t<sub>i</sub>CL should be made less than or equal to the sum of the transition time and the fixed propagation delay of the output of the driving stage for the estimated capacitive load.

Fig. 11 - Input voltage test circuit.

Fig. 12 - Input current test circuit.

3