TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9320F

# Frequency Counter System Microcontroller (DTS-10)

The TC9320F is a 4 bit CMOS microcontroller for frequency counter system with LCD driver. The CPU has 4 bit parallel addition / subtraction (AI, SI instructions, etc.) logical operation (OR, AN instructions, etc.) multiple bits judgment, comparison instructions (TM, SL instructions, etc.) and time base functions. The TC9320F is housed in an 60 pin mini-flat package and is provided with ample I/O ports and exclusive key input ports which are controlled by powerful I/O instructions (IO, KEY instruction, etc.) and 1/2 duty and 1/2 bias driving ample LCD use exclusive output terminals. Furthermore, the TC9320F has built in serial bus control function (SIO instruction) to powerfully control peripheral

Weight: 0.85 g (Typ.)

ICs, 6 bit A/D converter and D/A converter that are usable for field strength measurement and electronic volume control, and provides with many functions needed for frequency counter system.

#### **FEATURES**

f.dzsc.com

- 4 bit microcontroller frequency counter system

- 5 V ± 10% single power supply, CMOS structure for low power dissipation.

- Built-in LCD driver (1/2 duty, 1/2 bias, frame frequency: 100 Hz, 50 segments (Max.))

- Easy back up of data memory (RAM) and various ports (by the INH terminal).

- Program memory (ROM): 16 bits x 2048 steps

- Data memory (RAM) : 4 bits  $\times$  192 words

- 61 kinds of powerful instructions sets (all single word instructions)

The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws

- Instruction execution time 11.1  $\mu$ s (3.6 MHz or 7.2 MHz or 10.8 MHz crystal connection)

- Abundant add and subtract instructions (Add instruction: 12, subtract instruction: 12)

- Powerful composite judging instructions (TMTR, TMFR, TMT, TMF instructions, etc.)

- Data transfer at the same row address is possible.

- Register indirect transfer is possible (MVGD, MVGS instructions)

- Powerful 16 general registers (arranged in RAM)

- Stack level : 2 levels

- Program memory (ROM) has no conception of page and field, and JUMP and CAL instructions can be freely contained in 2048 steps.

- Further, contents of 16 bits data at any address in 1024 steps can be freely referred (DAL instruction)

- Built-in 20 bit general-use frequency counter (FM<sub>IN</sub>, AM<sub>IN</sub>)

- Independent frequency input terminals for FM and AM (FM<sub>IN</sub>, AM<sub>IN</sub>)

- 3 crystal oscillation frequencies are programmatically selectable. (3.6 MHz, 7.2 MHz, 10.8 MHz)

- Built-in powerful serial bus control function (I/O port-2 terminals are programmatically selectable.)

- Powerful I/O instructions (IO, KEY, SIO instruction, etc.)

- Exclusive key input port (K0~K3), abundant 25 (Max.) terminals LCD driver.

- Max. 27 I/O ports (I/O settable ports : 12 (Max.) output port : 8 (Max.) input port : 7 (Max.))

- Clock stop is possible programmatically (at CKSTP instruction : supply current below 10 μA)

- Built-in 2 Hz timer F/F, 10/100 Hz internal pulse output (Internal port for time base)

- LCD driver Terminal (S21~S25) and I/O port (P1-1~P1-4, P4-1) are programmatically selectable.

- Built-in 6 bit A/D and D/A converters (Selectable by selecting I/O port-3 terminals (P3-1~P3-3) programmatically).

- OTP product : TC93P20F

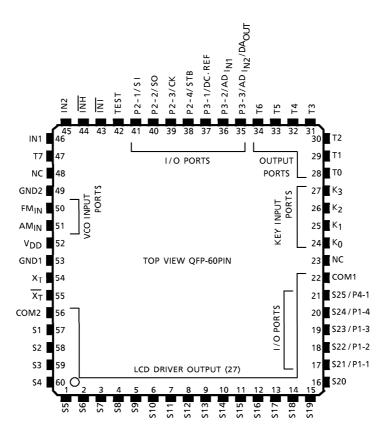

#### **PIN CONNECTION**

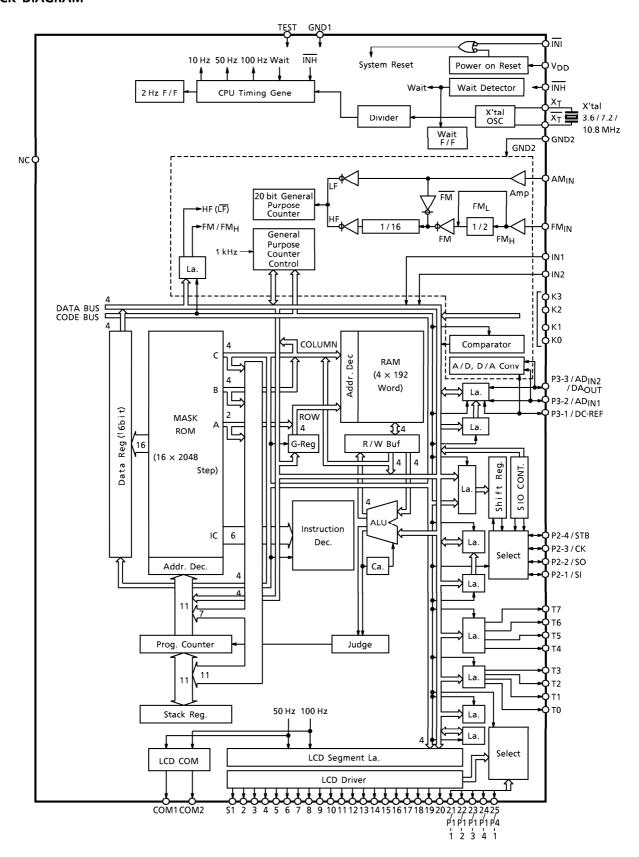

#### **BLOCK DIAGRAM**

#### PIN DESCRIPTION

| PIN<br>No.             | SYMBOL | PIN NAME                                              | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REMARKS                                       |

|------------------------|--------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 22<br>56               | COM1   | LCD Common<br>Output                                  | Common signal output terminals to LCD.  Maximum 50 segments can be displayed in a matrix with \$1~\$25.  Three levels of V <sub>DD</sub> , 1/2 V <sub>DD</sub> and GND are output to these terminals in a 50Hz cycle at intervals of 5ms.  (Note): At time of system reset and execution of CKSTP and DISP OFF, output is automatically fixed at "L" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>DD</sub><br>1<br>1<br>1<br>1<br>1<br>1 |

| 57~60<br>1~16<br>17~21 | S      | LCD Segment Output  LCD Segment Output /I/O port 1, 4 | Segment signal output terminals to LCD.  Maximum 50 segments can be displayed in a matrix with COM1 and COM2.  Data are output to these terminals by executing SEG instruction (COM1 system) and MARK instruction (COM2 system).  As to segment decoding, it is possible to perform it by creating its decoding pattern in ROM area and using DAL command.  S21/P1-1~S25/P4-1 can be used both as 5bit I/O port and segment output.  Assignment to I/O port is executed by contents of internal port called TERMINAL CONTROL.  I/O designation for every bit can be made for these ports, In case of using I/O port, it can be assigned to input or output for each bit by program.  There designate is executed by contents of internal port call PART-1, PORT-4 I/O CONTROL.  (Note): At time of system reset and execution of CKSTP command and DISP OFF, output is automatically fixed at "L" level.  (Refer to Note 3.) | V <sub>DD</sub> V                             |

| 23                     | NC     | No Connection                                         | This terminal must be left open. In case of OTP product TC93P20F, this terminal serves as Vpp terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                             |

| PIN<br>No.     | SYMBOL                                                        | PIN NAME                                                                                                        | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REMARKS                             |

|----------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 24~27          | K0~K3                                                         | Key Input Port                                                                                                  | 4 bit input ports for key matrix input. When KEY instruction these ports specified in the operand is executed, data of these terminals are read in RAM. All terminals have built in pull-down resistors. Further, the output ports T0~T6 are normally used for key return timing signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>DD</sub><br>R <sub>IN1</sub> |

| 28~34<br>47    | T0~T6                                                         | Key Timing<br>Output Port                                                                                       | 4 bit (T0~T3), 3 bit (T4~T6) and 1 bit (T7) output terminals.  T0~T6 ports are normally used for key return timing signal output of key matrix.  (Refer to Notes 2 and 3.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>DD</sub>                     |

| 35<br>36<br>37 | P3-3<br>/ADIN2<br>/DAOUT<br>P3-2<br>/ADIN1<br>P3-1<br>/DC-REF | I/O Port 3 /AD Analog Voltage Input /DA Analog Voltage Output /DA Analog Voltage Input /Reference Voltage Input | 3 bit I/O ports.  I/O designation for every bit can be made for these ports.  This designation is made according to contents of the internal port called PORT-3  I/O CONTROL.  Further, these terminals also serve for the analog input of the built-in 2 channel A/D converter and analog output of 1-channel D/A converter.  A/D and D/A converter input/output selection is controlled according to contents of ADON, DAON or ADSEL bit.  The built-in A/D converter is of programmably sequential comparison type, and P3-1 is the reference voltage input, and P3-3 is the analog comparison voltage input or analog voltage output.  (Note): A ladder resistance that generates internal D/A reference voltage is used commonly by the A/D and D/A converters.  When both the A/D and D/A converters are used simultaneously, DAON bit is set to "0" and D/A output is made to high impedance at time of A/D conversion.  It is therefore necessary to hold potential with a capacitor, etc.  (Refer to Notes 1, 2 and 3.) | VDD To AD or DA converter           |

| PIN<br>No. | SYMBOL                           | PIN NAME                                                                                                            | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REMARKS         |

|------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 38~<br>41  | P2-4/STB P2-3/CK P2-2/SO P2-1/SI | I/O Port 2<br>/Strobe Pulse<br>Output<br>/Serial Clock<br>Output<br>/Serial Data<br>Output<br>/Serial Data<br>Input | 4 bit I/O ports. I/O designation for every bit can be made for these ports. This designation is made according to contents of the internal port called PORT-2 I/O CONTROL. Further, these terminals are also used as the serial interface (SIO). Selection of SIO is controlled according to contents of SIO ON bit and in case of these serial interface, peripheral optional ICs can be controlled by executing SIO command. Serial transfer in NCD mode is programmably selectable. (Refer to Notes 1, 2 and 3.) | V <sub>DD</sub> |

| 42         | TEST                             | Test Mode<br>Control Input                                                                                          | Test mode control input terminal. The device is put in the test mode when "H" level signal is input and becomes the normal operating state when "L" level signal is input or in NC state.  (A pull-down resistor has been built in.)                                                                                                                                                                                                                                                                                | V <sub>DD</sub> |

| 43         | ĪNĪ                              | Initialize Input                                                                                                    | Device system reset signal input terminal. As long as the INI terminal is kept at "L" level, a system is kept in the reset state and when it becomes "H" level, a program startes from address 0.  Normally, the system is reset when 0~3.5 V is supplied to the VDD terminal (Power ON Reset) and therefore, this terminal is used by fixing at "H" level.  (Refer to Notes 1 and 3.)                                                                                                                              | V <sub>DD</sub> |

| PIN<br>No. | SYMBOL           | PIN NAME                  | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REMARKS         |

|------------|------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 44         | ĪNH              | Inhibit Input<br>Terminal | This is the INH port input terminal.  Normally, this terminal is used for radio mode selecting signal input or battery detection signal input.  When CKSTP instruction is used in a program and this CKSTP instruction is executed while the INH terminal is at "L" level, it is possible to stop the internal clock generator and CPU operation and put a system in the memory backup state with low current consumption (below 10 μA).  (Note): CKSTP instruction is effective when the INH terminal is at "L" level and when this instruction is executed at "H" level, the same operation as NOOP instruction results.  (Note): In the radio OFF mode or back-up mode, it is necessary to set reference internal ports (4 bits) at all "1" (Radio OFF mode). |                 |

| 45         | IN2              | Input Port 2              | These terminals are input ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DD</sub> |

| 46         | IN1              | Input Port 1              | These terminals are input ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

| 48         | NC               | No Connection             | This terminal must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _               |

| 49         | GND2             | Analog GND<br>Terminal    | GND terminal only for frequency counter and AD/DA converter analog units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _               |

| 50         | FM <sub>IN</sub> | FM Band Signal<br>Input   | This is an input terminal for FM band. The FM <sub>H</sub> mode and FM <sub>L</sub> mode are selectable by Radio instruction. In case of FM <sub>L</sub> mode, local oscillation output (VCO output) of 30 to 140 MHz (0.3 V <sub>p-p</sub> Min.) is input and in case of FM <sub>H</sub> mode, 30 to 185 MHz (0.5 V <sub>p-p</sub> Min.) is input. Having a built-in input amplifier, operates at small amplitude with a capacitor connected.                                                                                                                                                                                                                                                                                                                   | R <sub>f1</sub> |

| PIN<br>No. | SYMBOL          | PIN NAME                 | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REMARKS |

|------------|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 51         | AMIN            | AM Band Signal<br>Input  | This is an input terminal for AM band. The LF mode and HF mode are selectable by Radio instruction. In case of LF mode, local oscillation output (VCO output) of 0.5 to 20 MHz (0.3 V <sub>p-p</sub> Min.) and HF mode, 1 to 40 MHz (0.3 V <sub>p-p</sub> Min.) is input. Having a built-in input amplifier, operates at small amplitude with a capacitor connected. (Note): When reference internal ports (4 bits) are set at all "1" or FMH Mode or FML Mode is set, this input is pulled down.                                                                                                                                                                                                                                                 |         |

| 52         | V <sub>DD</sub> | Power Supply<br>Terminal | Power supply terminal.  At time of Rakio operation, 5 V ± 10% is applied.  In the back-up state (when executing CKSTP instruction), voltage can be reduced to 2 V.  Further, when voltage drops below 3.5 V during the operation of CPU, CPU stops (CPU Wait Mode) to prevent malfunction it restarts when voltage increases above 3.5 V.  As (Wait Mode) resulted under this condition can be detected by Wait F/F bit, perform initialization, clock correction, etc. programmatically.  Further, when 0 to 3.5 V is applied to this terminal, a device is reset and a program starts from address 0 (power On Reset).  (Note): Rise time of supply voltage on a device shall be 10~100 ms for the power ON reset operation.  (Refer to Note 1) |         |

| 53         | GND1            | Digital GND<br>Terminal  | GND terminal for CPU and the logic unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _       |

| PIN<br>No. | SYMBOL         | PIN NAME                           | FUNCTION AND OPERATION                                                                                                                                                                                                                                                              | REMARKS        |

|------------|----------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 54<br>55   | x <sub>T</sub> | Crystal<br>Oscillation<br>Terminal | Crystal resonator connecting terminal. It can be selectable Crystal resonator among 3.6 MHz, 7.2 MHz, 10.8 MHz. Adjust oscillation frequency (7.2 MHz) while observing LCD segment waveform. When CKSTP instruction is executed. oscillation stops automatically. (Refer to Note 1) | X <sub>T</sub> |

(Note 1): When a device is reset (V<sub>DD</sub> = 0→3.5 V and INI = "L"→"H"), I/O ports are set to the input, terminals serving as I/O ports and AD/DA converters are to the input of I/O ports, terminals serving as I/O ports and serial I/O ports are set to the input of I/O ports.

Crystal oscillation signal is designated to 10.8 MHz.

(Note 2): When CKSTP instruction is executed, outputs of the output ports and I/O ports are all set at "L" level.

(Note 3): When a device is reset, contents of output ports and internal ports are indefinite and it is therefore necessary to initialize them programmatically.

## **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                     | UNIT |

|-----------------------|------------------|----------------------------|------|

| Supply Voltage        | V <sub>DD</sub>  | -0.3~7.0                   | V    |

| Input Voltage         | VIN              | -0.3~V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation     | PD               | 400                        | mW   |

| Operation Temperature | T <sub>opr</sub> | - 40~85                    | °C   |

| Storage Temperature   | T <sub>stg</sub> | -65~150                    | °C   |

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, Ta = $-40 \sim 85$ °C, V<sub>DD</sub> = $4.5 \sim 5.5$ V)

| CHARACTERISTIC | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|--------|----------------------|----------------|------|------|------|------|

|----------------|--------|----------------------|----------------|------|------|------|------|

## CPU operation / PLL stop

| Operating Power Supply<br>Voltage Range | V <sub>DD1</sub> | _ | Radio Stop/CPU<br>Operation                                                                    | 3.5 | 5.0 | 5.5  | V   |

|-----------------------------------------|------------------|---|------------------------------------------------------------------------------------------------|-----|-----|------|-----|

| Memory Holding Voltage<br>Range         | V <sub>HD</sub>  | _ | Crystal oscillation stop                                                                       | 2.0 | ~   | 5.5  | V   |

| Operating Power Supply<br>Current       | I <sub>DD1</sub> | _ | Radio Stop/CPU Operation V <sub>DD</sub> = 5 V, Ta = 25°C in case of connecting 10.8 MHz X'tal | _   | 0.7 | 1.5  | mA  |

| Memory Holding Power<br>Supply Current  | l <sub>HD1</sub> | _ | V <sub>DD</sub> = 5 V,<br>Crystal oscillation stop                                             | _   | 0.1 | 10   | μΑ  |

| Memory Holding Power<br>Supply Current  | I <sub>HD2</sub> | _ | V <sub>DD</sub> = 2 V,<br>Crystal oscillation stop                                             | _   | _   | 5    | μΑ  |

| Crystal Oscillation Frequency           | fXT              | _ | _                                                                                              | 3.6 | 7.2 | 10.8 | MHz |

## CPU/Radio operation

| Operating Power Supply<br>Voltage Range | V <sub>DD2</sub> | _ | CPU / Radio Operation                                                                   | 4.5 | 5.0 | 5.5 | ٧  |

|-----------------------------------------|------------------|---|-----------------------------------------------------------------------------------------|-----|-----|-----|----|

| Operating Power Supply<br>Current       | I <sub>DD2</sub> | _ | CPU/Radio Operation<br>(FM <sub>IN</sub> = 140 MHz)<br>V <sub>DD</sub> = 5 V, Ta = 25°C | _   | 10  | 25  | mA |

# Radio operating frequency range

| FM <sub>IN</sub> (FM <sub>H</sub> Mode) | fгмн     | _ | $V_{IN} = 0.5 V_{p-p}$ | 30  | ~ | 185 | MHz |

|-----------------------------------------|----------|---|------------------------|-----|---|-----|-----|

| FM <sub>IN</sub> (FM <sub>L</sub> Mode) | fFML     | _ | $V_{IN} = 0.3 V_{p-p}$ | 30  | ~ | 140 | MHz |

| AM <sub>IN</sub> (HF Mode)              | fHF      | _ | $V_{IN} = 0.3 V_{p-p}$ | 1   | ~ | 40  | MHz |

| AM <sub>IN</sub> (LF Mode)              | $f_{LF}$ | _ | $V_{IN} = 0.3 V_{p-p}$ | 0.5 | ~ | 20  | MHz |

Pull-down Resistance

R<sub>IN1</sub>

| CHARACT                              | ERISTIC                     | SYMBOL                             | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                             | MIN.                 | TYP.         | MAX.                  | ПИП                |

|--------------------------------------|-----------------------------|------------------------------------|----------------------|----------------------------------------------------------------------------|----------------------|--------------|-----------------------|--------------------|

| Radio operatin                       | g input amp                 | olitude rang                       | e                    |                                                                            |                      |              |                       |                    |

| FM <sub>IN</sub> (FM <sub>H</sub> Me | ode)                        | V <sub>IN</sub> (FM <sub>H</sub> ) | _                    | f <sub>IN</sub> = 30~185 MHz                                               | 0.5                  | ~            | V <sub>DD</sub> - 0.5 | V <sub>p-p</sub>   |

| FM <sub>IN</sub> (FM <sub>L</sub> Mo | ode)                        | V <sub>IN</sub> (FM <sub>L</sub> ) | _                    | f <sub>IN</sub> = 30~140 MHz                                               | 0.3                  | ~            | V <sub>DD</sub> - 0.5 | 5 V <sub>p-1</sub> |

| AMIN (HF Mod                         | de)                         | V <sub>IN</sub> (HF)               | _                    | f <sub>IN</sub> = 1~40 MHz                                                 | 0.3                  | ~            | V <sub>DD</sub> - 0.5 | 5 V <sub>p-1</sub> |

| AM <sub>IN</sub> (LF Mod             | le)                         | V <sub>IN</sub> (LF)               | _                    | f <sub>IN</sub> = 0.5~20 MHz                                               | 0.3                  | ~            | V <sub>DD</sub> - 0.5 | ا- <sub>P-I</sub>  |

| LCD common o                         | output (COM                 | 1, COM2)                           |                      |                                                                            |                      |              |                       |                    |

| Output                               | High Level                  | lOH1                               | -                    | V <sub>OH</sub> = 4.5 V,<br>V <sub>DD</sub> = 5 V                          | - 250                | <b>-</b> 750 | _                     |                    |

| Current                              | Low Level                   | lOL1                               | _                    | V <sub>OH</sub> = 0.5 V,<br>V <sub>DD</sub> = 5 V                          | 250                  | 750          | _                     | - μ <b>Α</b>       |

| 1/2 Bias Volta                       | ige                         | V <sub>BS</sub>                    |                      | V <sub>DD</sub> = 5 V, No Load                                             | 2.30                 | 2.50         | 2.70                  | V                  |

| LCD segment o                        | utput (\$1~\$<br>High Level |                                    | Ι_                   | V <sub>OH</sub> = 4.5 V,                                                   | <b>– 100</b>         | <b>– 300</b> | T _                   | Τ                  |

| Output<br>Current                    | Low Level                   | I <sub>OL2</sub>                   | <br>  _              | V <sub>DD</sub> = 5 V<br>V <sub>OH</sub> = 0.5 V,<br>V <sub>DD</sub> = 5 V | 100                  | 300          | _                     | μΔ                 |

| P1-1~P1-4, P2-                       | 1∼P2-4 (SO,                 | CK, STB), P                        | 3-1~P                | 3-3, P4-1, T0~T7 outp                                                      | ut port              |              |                       |                    |

| Output                               | High Level                  | IOH3                               | _                    | V <sub>OH</sub> = 4.5 V,<br>V <sub>DD</sub> = 5 V                          | - 1.0                | - 3.0        | _                     | mA                 |

| Current                              | Low Level                   | l <sub>OL3</sub>                   | _                    | $V_{OH} = 0.5 V,$<br>$V_{DD} = 5 V$                                        | 1.0                  | 3.0          | _                     | ""                 |

| INH input port                       |                             |                                    |                      |                                                                            |                      |              |                       |                    |

| ĪNH                                  | High Level                  |                                    |                      | _                                                                          | $V_{DD} \times 0.85$ | ~            | $V_{DD}$              | V                  |

| Input Voltage                        |                             | V <sub>IL2</sub>                   |                      | _                                                                          | 0                    | ~            | $V_{DD} \times 0.5$   | 5 V                |

| Input Leak                           | High Level                  | l <sub>IH1</sub>                   |                      | $V_{IH} = V_{DD} = 5.5 V$                                                  |                      |              | ± 2                   |                    |

| Current                              | Low Level                   | l <sub>IL1</sub>                   | _                    | $V_{\text{IL}} = 0 \text{ V},$ $V_{\text{DD}} = 5.5 \text{ V}$             | _                    | _            | ± 2                   | μΑ                 |

| Key input port                       | (K0~K3)                     |                                    |                      |                                                                            |                      |              |                       |                    |

| Input                                | High Level                  | V <sub>IH1</sub>                   |                      | _                                                                          | $V_{DD} \times 0.7$  | ~            | V <sub>DD</sub>       | V                  |

| Voltage                              | Low Level                   | V <sub>IL1</sub>                   | _                    | _                                                                          | 0                    | ~            | $V_{DD} \times 0.3$   | <b>∛</b>           |

|                                      |                             | <del> </del>                       | t                    | 1,, ,, ,,                                                                  | +                    |              | <del> </del>          | +                  |

$V_{IH} = V_{DD} = 5 V$ , Ta = 25°C

150

$\mathsf{k}\Omega$

100

50

| CHARACTERISTIC SYMBO | TEST<br>CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------------|----------------------|----------------|------|------|------|------|

|----------------------|----------------------|----------------|------|------|------|------|

# $\overline{\text{INI}}$ , IN1, IN2, P1-1~P1-4, P2-1~P2-4 (SI), P3-1~P3-3, P4-1 port

| Input Voltage         | High Level | V <sub>IH1</sub> | _ | _                                                 | $V_{DD} \times 0.7$ | ~ | $V_{DD}$            | V          |

|-----------------------|------------|------------------|---|---------------------------------------------------|---------------------|---|---------------------|------------|

|                       | Low Level  | $V_{IL1}$        | _ | _                                                 | 0                   | ~ | $V_{DD} \times 0.3$ | , <b>'</b> |

| Input Leak<br>Current | High Level | l <sub>IH1</sub> | _ | $V_{IH} = V_{DD} = 5.5 V$                         | _                   | _ | ± 2                 |            |

|                       | Low Level  | llL1             |   | V <sub>IL</sub> = 0 V,<br>V <sub>DD</sub> = 5.5 V | _                   | _ | ± 2                 | $\mu$ A    |

# A/D, D/A converter (DC·REF, A/D $_{IN1}$ , A/D $_{IN2}$ , D/A $_{OUT}$ )

| Analogue Input Voltage<br>Range             | V <sub>ADI</sub> | _ | AD <sub>IN1</sub> , AD <sub>IN2</sub>                                               | 0   | ~     | V <sub>DD</sub>       | ٧   |

|---------------------------------------------|------------------|---|-------------------------------------------------------------------------------------|-----|-------|-----------------------|-----|

| Analogue Reference<br>Voltage Range         | V <sub>REF</sub> | _ | DC·REF                                                                              | 1.5 | ~     | V <sub>DD</sub>       | V   |

| Resolution                                  | V <sub>RES</sub> | _ | _                                                                                   | _   | _     | 6                     | bit |

| Analogue Reference<br>Voltage Input Current | IREF             | _ | DC·REF, Ta = 25°C,<br>$V_{IH} = V_{DD} = 5 V$                                       | _   | 0.5   | 1.0                   | mA  |

| Analogue Output<br>Voltage Range            | VDAO             | _ | DAOUT                                                                               | 0   | ~     | V <sub>DD</sub> – 1.0 | ٧   |

| Analogue Output<br>Voltage Deviation        | ∆V <sub>DA</sub> | _ | $I_{DA} = \pm 100 \mu\text{A},$<br>$V_{DD} = 5 \text{V},  \text{Ta} = 25 \text{°C}$ | _   | ± 50  | ± 150                 | mV  |

| Conversion Total Error                      | _                | _ | _                                                                                   | _   | ± 0.5 | ± 1.5                 | LSB |

#### Other

| FM <sub>IN</sub> , AM <sub>IN</sub><br>Input Feedback<br>Resistance | R <sub>f1</sub>  | _ | V <sub>DD</sub> = 5 V, Ta = 25°C            | 250 | 500  | 1000 | kΩ |

|---------------------------------------------------------------------|------------------|---|---------------------------------------------|-----|------|------|----|

| X <sub>T</sub> Input Feedback<br>Resistance                         | R <sub>f2</sub>  | _ | V <sub>DD</sub> = 5 V, Ta = 25°C            | 500 | 1000 | 1750 | kΩ |

| TEST Input Pull-down<br>Resistance                                  | R <sub>IN2</sub> | _ | $V_{IH} = V_{DD} = 5 V,$ $Ta = 25^{\circ}C$ | 15  | 30   | 60   | kΩ |

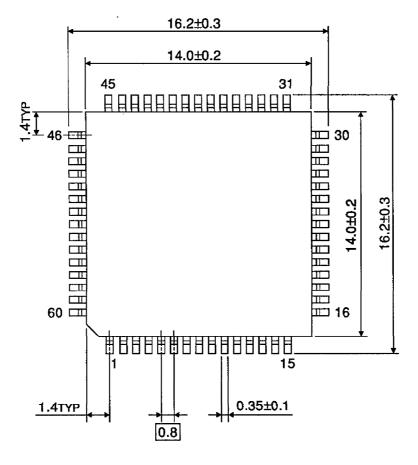

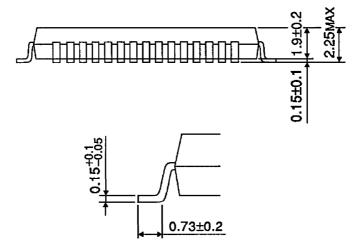

#### **PACKAGE DIMENSIONS**

QFP60-P-1414-0.80E

Unit: mm

Weight: 0.85 g (Typ.)