TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

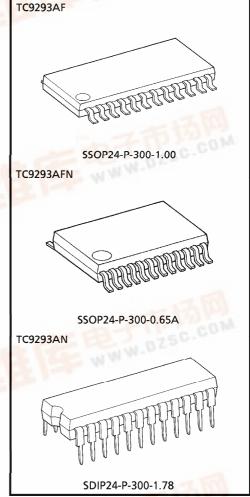

## TC9293AF, TC9293AFN, TC9293AN

#### Σ-Δ MODULATION SYSTEM DA CONVERTER WITH ANALOG FILTER

TC9293AF, TC9293AFN, TC9293AN are a 2'nd order ∑-∆ modulation system 1-bit DA converter with a built-in 8 times over sampling digital filter and analog filter developing for digital audio equipment. As this IC is small package, SSOP24 (1.00mm, 0.65mm) and SDIP24, and the analog filter has been incorporated, it is able to output a direct analog wave form and construct small the digital filter~the analog output unit at a low price.

#### **FEATURES**

f.dzsc.com

- Built in 8 times over sampling digital filter

- Low voltage operate (2.7~5.5V)

- Built-in digital de-emphasis filter

- In serial mode, output amplitude can be set in 128steps of resolution using microcontroller command.

- In parallel mode, soft mute can be set for the output signal in 64steps in 20ms.

- Over sampling ratio (OSR) of  $\Sigma$ - $\Delta$  modulation circuit is 192fs

- Support double speed operation

- Sampling frequency: 32kHz, 44.1kHz, 48kHz

- Built-in 3'rd order analog filter

- Characteristics of the digital filter and DA converter are as follows:

Weight

SSOP24-P-300-1.00 : 0.31g (Typ.) SSOP24-P-300-0.65A : 0.14g (Typ.) SDIP24-P-300-1.78

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws

- The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

#### **DIGITAL FILTER** (fs = 44.1kHz)

|                        | DIGITAL<br>FILTER | PASS-BAND<br>RIPPLE | TRANSIENT<br>BAND WIDTH | STOP BAND SUPPRESSION |

|------------------------|-------------------|---------------------|-------------------------|-----------------------|

| Standard Operation     | 8fs               | ± 0.11dB            | 20k~24.1kHz             | – 26dB                |

| Double Speed Operation | 8fs               | ± 0.11dB            | 20k~24.1kHz             | – 26dB                |

#### **DA CONVERTER** $(V_{DD} = 5V)$

|                        | OSR   | NOISE<br>DISTORTION | S/N         |

|------------------------|-------|---------------------|-------------|

| Standard Operation     | 192fs | – 85dB (Typ.)       | 96dB (Typ.) |

| Double Speed Operation | 96fs  | – 85dB (Typ.)       | 86dB (Typ.) |

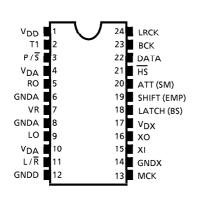

#### **PIN CONNECTION**

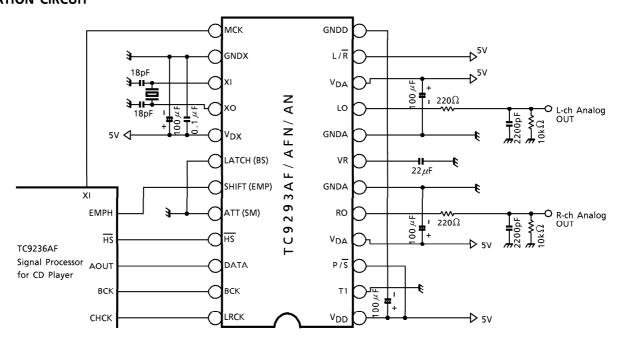

#### **BLOCK DIAGRAM**

#### **PIN FUNCTION**

| PIN No. | SYMBOL         | 1/0 | FUNCTION                                                                                                 | REMARKS          |

|---------|----------------|-----|----------------------------------------------------------------------------------------------------------|------------------|

| 1       | $V_{DD}$       | _   | Digital block power supply pin.                                                                          |                  |

| 2       | T1             | ı   | Test pin. Normally, use at "L".                                                                          |                  |

| 3       | P/S            | ı   | Parallel/serial mode select pin.                                                                         |                  |

| 4       | $V_{DA}$       | _   | Analog power supply pin.                                                                                 |                  |

| 5       | RO             | 0   | Right channel analog output pin.                                                                         |                  |

| 6       | GNDA           | _   | Analog ground pin.                                                                                       |                  |

| 7       | VR             | _   | Reference voltage pin.                                                                                   |                  |

| 8       | GNDA           | _   | Analog ground pin.                                                                                       |                  |

| 9       | LO             | 0   | L-ch analog output pin.                                                                                  |                  |

| 10      | $V_{DA}$       | 1   | Analog power supply pin.                                                                                 |                  |

| 11      | L/R            | ı   | LRCK polarity switching pin.                                                                             |                  |

| 12      | GNDD           | -   | Digital ground pin.                                                                                      |                  |

| 13      | MCK            | 0   | System clock output pin.                                                                                 |                  |

| 14      | GNDX           | 1   | Crystal oscillator ground pin.                                                                           |                  |

| 15      | ΧI             | ı   | Crystal oscillator connection pin.                                                                       |                  |

| 16      | хо             | 0   | Generates the clock required by the system.                                                              | XI XO            |

| 17      | $V_{DX}$       | _   | Crystal oscillator power supply pin.                                                                     |                  |

| 18      | LATCH<br>(BS)  | I   | Serial mode : Data latch signal input pin Parallel mode : De-emphasis filter mode select pin.            | SHUMITT<br>INPUT |

| 19      | SHIFT<br>(EMP) | I   | Serial mode : Shift clock input pin Parallel mode : De-emphasis filter control pin.                      | SHUMITT<br>INPUT |

| 20      | ATT<br>(SM)    | I   | Serial mode : Data input pin Parallel mode : Soft mute control pin.                                      | SHUMITT<br>INPUT |

| 21      | HS             | I   | Standard / double speed operation control pin. Standard operation at "H", double speed operation at "L". |                  |

| 22      | DATA           | ı   | Audio data input pin.                                                                                    |                  |

| 23      | ВСК            | I   | Bit clock input pin.                                                                                     |                  |

| 24      | LRCK           | I   | LR clock input pin.                                                                                      |                  |

#### **DESCRIPTION OF BLOCK OPERATION**

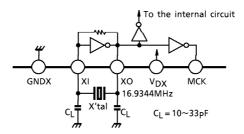

#### 1. Crystal oscillation circuit and timing generator

Clock required for internal operation can be generated when crystal and capacitors are connected as shown in the following figure.

Further, this converter is also operable when system clock is input from the outside through XI pin (pin(5)).

However, a through consideration is required in this case because noise distortion and S/N ratio of the DA converter are largely affected by qualities of wave form such as jitter, rising and falling characteristics, etc. of system clock.

Use a crystal having a low CI value and good statability.

Fig.1 Configuration of crystal oscillation circuit.

The timing generator generates clock required for the digital filter, de-emphasis filter, interpolation filter and process timing signal.

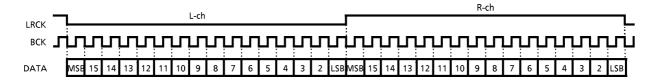

#### 2. Data input circuit

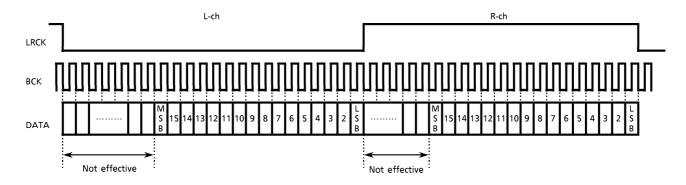

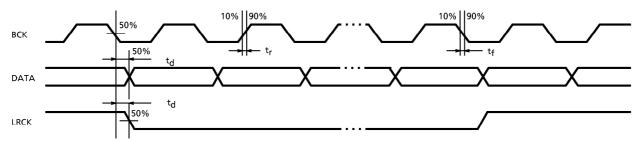

DATA and LRCK are taken in the shift register in the LSI at the rising edge of BCK.

As shown in the following timing example, it is therefore necessary to input DATA and LRCK in synchronism with the falling edge of BCK.

Further, because DATA has been to designed that 16 bits before the change point of LRCK are made effective data.

Fig.2a Example of input timing diagram  $(L/\overline{R} = "L")$

If BCK is 48fs or 64fs, please input data as follows.

Fig.2b Example of input timing diagram ( $L/\overline{R} = "L"$ )

L/R channel data selection pin is pin①.

Table-1 Channel data

| L/R INPUT   | LRCK      |           |  |  |

|-------------|-----------|-----------|--|--|

| L/K IIVI OI | L         | Н         |  |  |

| Н           | R-ch data | L-ch data |  |  |

| L           | L-ch data | R-ch data |  |  |

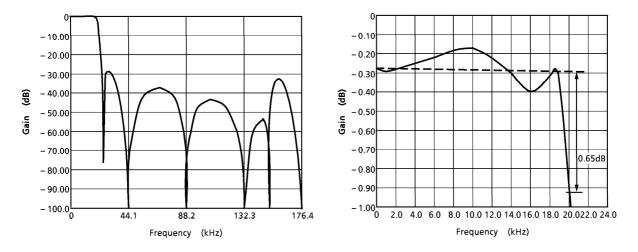

#### 3. Digital filter

Foldover noise component of the outside band is removed by the 8 times oversampling digital filter.

| iable                     | Table-2 Characteristics of the digital lifter |                        |                          |  |  |  |

|---------------------------|-----------------------------------------------|------------------------|--------------------------|--|--|--|

|                           | Pass-band<br>Ripple                           | Transient<br>Bandwidth | Stop-Band<br>Suppression |  |  |  |

| Standard<br>Operation     | ±0.11dB                                       | 20.0k~24.1kHz          | – 26dB                   |  |  |  |

| Double Speed<br>Operation | ± 0.11dB                                      | 20.0k~24.1kHz          | – 26dB                   |  |  |  |

Table-2 Characteristics of the digital filter

Frequency characteristics of the digital filter are as follows: (Double speed operation is same)

Fig.3 Digital filter frequency characteristics (fs = 44.1kHz)

#### 4. De-emphasis filter

The built-in digital de-emphasis circuit is available for three kinds of sampling frequency, fs of 32kHz, 44.1kHz, and 48kHz. The selection is done as shown in the following table.

Table-3 Truth table for de-emphasis filter selection at parallel mode

| LATCH (BS)       | Н  | Н  | L    | L   |       |

|------------------|----|----|------|-----|-------|

| SHIFT (EMP)      | Н  | L  | Н    | L   |       |

| MODE (fs SELECT) | 32 | 48 | 44.1 | OFF | (kHz) |

Digitization of the de-emphasis filter has eliminated the necessity for external parts such as resistor, capacitor, analog switch, etc.

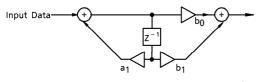

Further, to reduce the characteristic error of the de-emphasis filter, coefficients have been adjusted. The construction and characteristics of the de-emphasis filter are shown below.

Transfer function : H(Z) =  $\frac{(b_0 + b_1 Z^{-1})}{(1 - a_1 Z^{-1})}$

$|G(j\omega)|$   $T_1 = 50 \mu s, T_2 = 15 \mu s$

Fig.4 Construction of IIR type digital de-emphasis filter

Fig.5 Filter characteristic

#### 5. DA conversion circuit

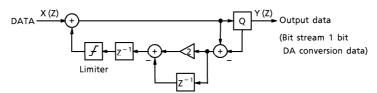

The 2'nd order  $\Sigma$ - $\Delta$  modulation system DA converter for 2 channels (simultaneous output type) has been incorporated.

2'nd order  $\Sigma - \Delta$  modulator: Y(Z) = X(Z) +  $(1 - Z^{-1})^2$ Q(Z)

Fig.6 Construction of  $\Sigma$ - $\Delta$  modulation DA converter

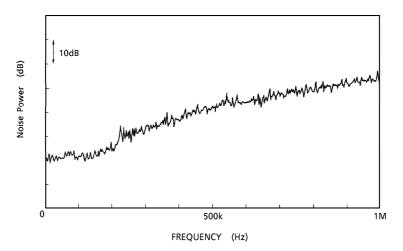

It has been designed that clock for the  $\Sigma$ - $\Delta$  modulator is a half of master clock (MCK : Crystal oscillation clock) and the converter operates at 192fs at the standard operation. The noise shaping characteristic is shown below.

Fig.7 Noise shaping characteristic

#### 6. Output circuit

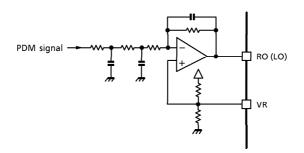

These ICs is built-in 3'rd order analog low pass filter.

These output is analog signal directly, RO (pin⑤) and LO (pin⑨) pins.

Fig.8 Analog filter circuit

#### 7. Soft mute circuit

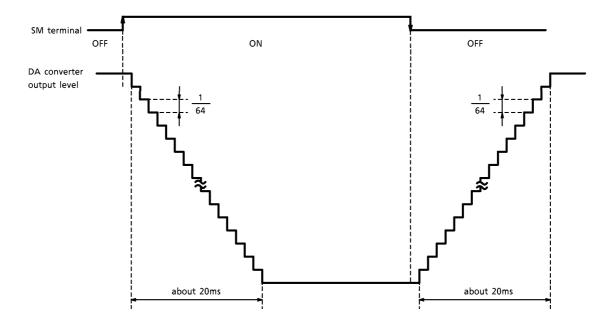

This IC is a built-in soft mute circuit, it is possible to do soft mute, when SM pin is changed "L" level to "H" level during parallel mode.

Characteristic of soft mute ON/OFF and DA converter output level is as follows.

While output level is changing, it is not possible to accept soft mute ON/OFF control.

Fig.9 Soft mute DA converter output level

#### 8. Description of internal control signal

Parallel and serial modes can be selected by the  $P/\overline{S}$  pin. The controll functions are described as follow.

#### 8-1 Parallel mode $(P/\overline{S} pin = H)$

In parallel mode, pin<sup>®</sup>, <sup>®</sup>, <sup>®</sup> are set as follows.

| Table-4 | Pin | names | at | parallel | mode |

|---------|-----|-------|----|----------|------|

|         |     |       |    |          |      |

| PIN No. | PIN NAME | FUNCTION                            |

|---------|----------|-------------------------------------|

| 18      | BS       | De-emphasis filter mode select pin. |

| 19      | EMP      | De-emphasis filter control pin.     |

| 20      | SM       | Soft mute control pin.              |

#### 8-2 Serial mode $(P/\overline{S} \text{ terminal} = L : For micro processor control use)$

In serial mode, these ICs can be controlled by micro processor. The control function of pin®, ® are as follows.

Table-5 Pin names at serial mode

| PIN No. | PIN NAME | FUNCTION                     |

|---------|----------|------------------------------|

| 18      | LATCH    | Data latch signal input pin  |

| 19      | SHIFT    | Shift clock signal input pin |

| 20      | ATT      | Data input pin               |

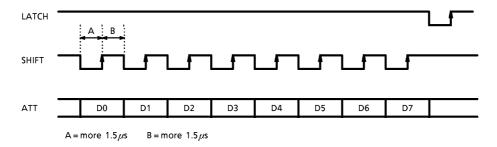

LATCH and ATT signals are entered to the shift register of the LSI at the rising edge of SHIFT signal.

Also, LATCH signal should rise after a minimum of  $1.5\mu$ s of the last data is shifted to the register. If the shift pulse is changed while LATCH is Low, Mis-operation may occur. LATCH should be keep at Low until after D7 is shifted into the register.

Fig.10 Example for serial control mode data

In serial control mode, the control features are as follows. When this IC's power is ON, all these data must be setting.

Table-6 Serial mode control

| SERIAL INPUT DATA | CONTROL SIGNA |           |

|-------------------|---------------|-----------|

| D7                | 0             | 1         |

| D6                | AT6           | $\mu$ BS  |

| D5                | AT5           | $\mu$ EMP |

| D4                | AT4           | _         |

| D3                | AT3           | _         |

| D2                | AT2           | _         |

| D1                | AT1           | _         |

| D0                | AT0           | _         |

AT0~6 : Attenuation level setting  $\mu$ BS : De-emphasis mode select EMP : De-emphasis ON/OF select

#### 1 Digital attenuator

D7 = "L" is the command for digital attenuator. It can be set to 128 levels as show below.

Table-7 Audio output of attenuation data

| ATTENUATION CONTROL DATA<br>D6~D0 | AUDIO OUTPUT |

|-----------------------------------|--------------|

| 7F (HEX)                          | – 0.000dB    |

| 7E (HEX)                          | – 0.069dB    |

| :                                 | :            |

| 01 (HEX)                          | – 42.076dB   |

| 00 (HEX)                          | _ 8          |

The attenuation value can be calculated from input data as follow:

ATT = 20log (input data / 127)dB

Example: In case of attenuator = 7A

ATT = 20log (122 / 127)dB = -0.349dB

#### 2 Digital De-emphasis filter

D7 = "H" is the command for Digital De-emphasis filter.

Table-8 De-emphasis filter setting

|           |    |    |      |     | _ |

|-----------|----|----|------|-----|---|

| $\mu$ BS  | Н  | Н  | L    | L   |   |

| $\mu$ EMP | Н  | L  | Н    | L   |   |

| MODE      | 32 | 48 | 44.1 | OFF | 1 |

(kHz)

#### **MAXIMUM RATINGS** (Ta = 25°C)

| CHARAC                | TERISTIC  | SYMBOL           | RATING                   | UNIT |  |

|-----------------------|-----------|------------------|--------------------------|------|--|

|                       |           | $V_{DD}$         | -0.3~6.0                 |      |  |

| Supply Voltage        |           | $V_{DA}$         | -0.3~6.0                 | _ v  |  |

|                       |           | V <sub>DX</sub>  | -0.3~6.0                 |      |  |

| Input Voltage         |           | V <sub>in</sub>  | $-0.3 \sim V_{DD} + 0.3$ | ٧    |  |

| Power<br>Dissipation  | TC9293AF  |                  | 200                      | mW   |  |

|                       | TC9293AFN | PD               | 200                      |      |  |

|                       | TC9293AN  |                  | 300                      |      |  |

| Operating Temperature |           | T <sub>opr</sub> | - 35~85                  | °C   |  |

| Storage Temperature   |           | T <sub>stg</sub> | <b>- 55∼150</b>          | °C   |  |

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, Ta = 25°C, V<sub>DD</sub> = V<sub>DX</sub> = V<sub>DA</sub> = 5V) DC item

| CHARACTERISTICS                 |           | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                         | MIN.                | TYP. | MAX.                | UNIT    |

|---------------------------------|-----------|-----------------|----------------------|----------------------------------------|---------------------|------|---------------------|---------|

| Operating Supply<br>Voltage (1) |           | $V_{DD}$        |                      |                                        | 4.5                 | 5.0  | 5.5                 |         |

|                                 |           | $V_{DX}$        | —                    | Ta = −35~85°C                          | 4.5                 | 5.0  | 5.5                 | V       |

|                                 |           | $V_{DA}$        |                      |                                        | 4.5                 | 5.0  | 5.5                 | .       |

| Operating Supply<br>Voltage (2) |           | $V_{DD}$        |                      | Ta = − 15~55°C                         | 2.7                 | 3.2  | 5.5                 |         |

|                                 |           | $V_{DX}$        | _                    | (Operation frequency                   | 2.7                 | 3.2  | 5.5                 | V       |

|                                 |           | $V_{DA}$        |                      | $\sqrt{12MHz} \le f_{opr} \le 18.5MHz$ | 2.7                 | 3.2  | 5.5                 |         |

| Power Dissipation               |           | I <sub>DD</sub> | _                    | XI = 16.9MHz                           |                     | 12   | 20                  | mΑ      |

| Input Voltage                   | "H" Level | $V_{IH}$        |                      |                                        | $V_{DD} \times 0.7$ |      | $V_{DD}$            | ٧       |

|                                 | "L" Level | V <sub>IL</sub> |                      |                                        | 0                   |      | $V_{DD} \times 0.3$ | V       |

| Input Current                   | "H" Level | ΙΗ              |                      |                                        | - 10                |      | 10                  | ۸,,     |

|                                 | "L" Level | կլ              |                      |                                        | _ 10                |      |                     | $\mu$ A |

### AC item (Over-sampling ratio = 192fs)

| CHARACTERISTICS      | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                      | MIN. | TYP.    | MAX. | UNIT              |

|----------------------|------------------|----------------------|-------------------------------------|------|---------|------|-------------------|

| Table Harmonic       | THD + N1         | 1                    | 1kHz Sine wave, full-scale input    |      | - 85    | - 80 | dB                |

| Distortion + Noise 1 | TINETINI         |                      | $V_{DD} = V_{DX} = V_{DA} = 5V$     |      |         |      |                   |

| Table Harmonic       | THD + N2         | 1                    | 1kHz Sine wave, full-scale input    | 1    | - 85    | - 78 | dB                |

| Distortion + Noise 2 |                  |                      | $V_{DD} = V_{DX} = V_{DA} = 3.0V$   |      |         |      |                   |

| S/N Ratio            | S/N              | 1                    |                                     | 88   | 96      | _    | dB                |

| Dynamic Range        | DR               | 1                    | 1kHz Sine wave,                     | 00   | 95      | 1    | dB                |

|                      |                  |                      | - 60dB input conversion             | 90   |         |      |                   |

| Cross-talk           | СТ               | 1                    | 1kHz Sine wave, full-scale input    | _    | - 95    | - 90 | dB                |

| Analog Output Level  | Aout 1           | - 1                  | 1kHz Sine wave, full-scale input    |      | 1250    | _    | mV <sub>rms</sub> |

|                      |                  |                      | $V_{DD} = V_{DX} = V_{DA} = 5V$     | _    |         |      |                   |

|                      | Aout 2           |                      | 1kHz Sine wave, full-scale input    | _    | 750     | _    |                   |

|                      |                  |                      | $V_{DD} = V_{DX} = V_{DA} = 3.0V$   |      |         |      |                   |

| Operating Frequency  | f <sub>opr</sub> | _                    | $V_{DD} = V_{DA} = V_{DX} \ge 4.5V$ | 10   | 16.9344 | 18.5 | MHz               |

| Input Frequency      | fLR              | _                    | LRCK duty cycle = 50%               | 30   | 44.1    | 100  | kHz               |

|                      | f <sub>BCK</sub> |                      | BCK duty cycle = 50%                | 0.96 | 2.1168  | 4.3  | MHz               |

| Rise Time            | t <sub>r</sub>   |                      | LBCK BCK (100/ - 000/)              | _    | _       | 15   |                   |

| Fall Time            | tf               | _                    | LRCK, BCK (10%~90%)                 | _    | _       | 15   | ns                |

| Delay Time           | td               | _                    | BCK                                 | _    | _       | 40   | ns                |

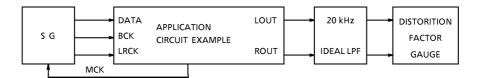

• TEST CIRCUIT 1: Application circuit example is used.

SG : ANRITSU MG-22A or equivalent LPF : SHIBASOKU 725C built-in Filter

Distortion Factor Gauge: SHIBASOKU 725C or equivalent

| Measuring Item | Distortion factor gauge filter setting A weight |  |  |

|----------------|-------------------------------------------------|--|--|

| THD + N, CT    | OFF                                             |  |  |

| S/N. DR        | ON                                              |  |  |

A weight: IEC-A or equivalent

• AC CHARACTERISTIC STIPUL ATED POINT (Input signal: LRCK, BCK, DATA)

#### APPLICATION CIRCUIT

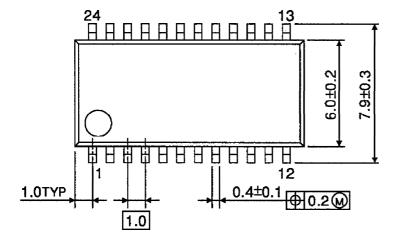

Unit: mm

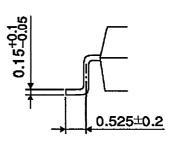

### **PACKAGE DIMENSIONS**

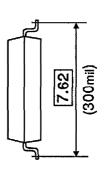

SSOP24-P-300-1.00

Weight: 0.31g (Typ.)

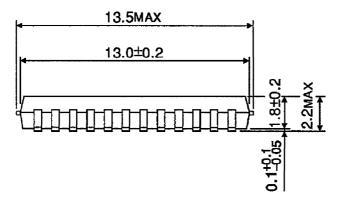

Weight: 0.14g (Typ.)

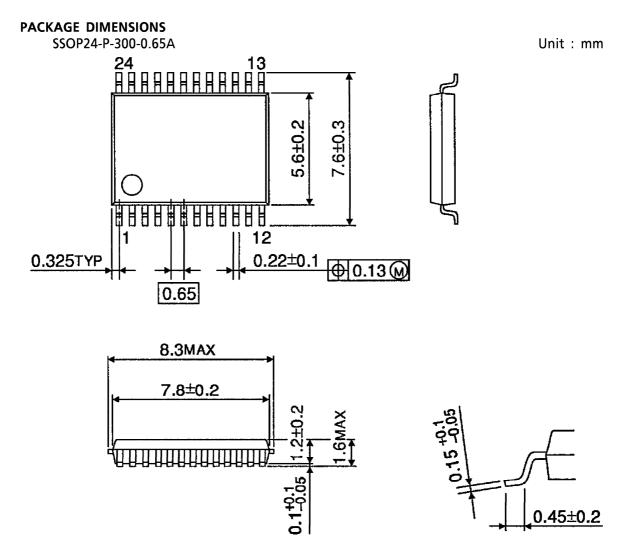

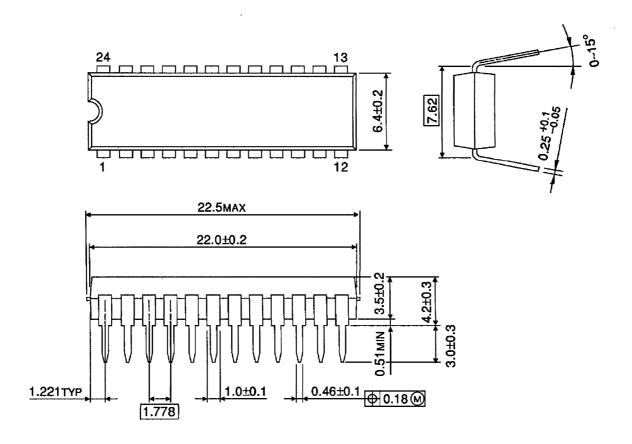

#### PACKAGE DIMENSIONS SDIP24-P-300-1.78

$\mathsf{Unit}:\mathsf{mm}$

Weight: 1.2g (Typ.)