查询W40C06A供应商

# 捷多邦,专业PCB打样工厂,24小时加急出货

# W40C06A

Six Outputs

# Features

- Six skew-controlled CMOS outputs with enables

- Low output impedance, high current output buffers

- Each output can drive two  $50\Omega$  (or higher) clock lines

CYPRESS

- 3.3V operation

- DC to 100-MHz operation

- Controlled output rate slew reduces EMI and output ringing

- Ideal for PCI or CPU clock distribution

- Low power CMOS design available in: — 16-pin SSOP (Shrink Small Outline Package)

Table 1. Output Enable Selection (-14)

| W40C06A-14 |        |        |  |  |

|------------|--------|--------|--|--|

| CKEN       | Q1:5   |        |  |  |

| 0          | Active | Low    |  |  |

| 1          | Active | Active |  |  |

# **Key Specifications**

| Supply Voltages:            | V <sub>CC</sub> = 3.3V ±10%<br>or 5.0V±10%    |

|-----------------------------|-----------------------------------------------|

| Operating Temperature:      | 0°C to +70°C                                  |

| Output Frequency:           | DC to 100 MHz                                 |

| Skew Output:                | <400 ps rising edges<br><500 ps falling edges |

| Output Drive Current:       | 48 mA max                                     |

| Output Impedance:           | 5Ω                                            |

| Output Rise/Fall Edge Rate: | 1 to 4 volts/ns                               |

| Output Duty Cycle:          | 40/65% worst case                             |

|                             |                                               |

#### **Pin Configuration Block Diagram** Q0 NC II □ NC 16 1 TCLK Input Q1 CKEN I 2 15 TCLK Control W40C06A-14 Q2 GND I 3 Q3 14 П 4 Q0 [ 13 ⊐ v<sub>dd</sub> Q3 5 □ Q4 V<sub>DD</sub> II 12 Q4 Q1 🖽 6 11 □ GND CKEN -Q5 GND II 7 10 П Q5 Syncl ronization I V<sub>DD</sub> Logic Q2 🛙 8 9

# **Pin Definitions**

| Pin Name | Pin<br>No.             | Pin<br>Type | Pin Description                                                                                      |  |

|----------|------------------------|-------------|------------------------------------------------------------------------------------------------------|--|

| Q0:5     | 4, 6, 8,<br>10, 12, 14 | 0           | Buffered Clock Outputs: Six skew controlled CMOS clock outputs.                                      |  |

| VDD      | 5, 9, 13               | Р           | <b>Power Connection:</b> Power supply for core logic and output buffers. Connected to a 3.3V supply. |  |

| GND      | 3, 7, 11               | G           | Ground Connection: Connect all ground pins to the common system ground plane.                        |  |

| CKEN     | 2                      | I           | Clock Enable: Provide Start/Stop control of buffer outputs refer to Table 1.                         |  |

| TCLK     | 15                     | I           | Clock Input: External reference frequency input.                                                     |  |

| NC       | 1, 16                  | NC          | No Connection: These pins should remain unconnected.                                                 |  |

## **General Overview**

The W40C06A is a six-output, low-skew clock buffer ideally suited for PCI, CPU, and other system clock applications. Each high-current, low-impedance output is specifically designed to drive up to two impedance-controlled signal lines. Controlled output rise/fall times further help to provide good signal characteristics.

The W40C06A is ideal for clock signal distribution in skew sensitive applications such as Pentium® processor or PCI applications. W40C06A-14 has an enable input pin (see *Table 1*) that starts and stops the clock outputs without producing short cycles.

#### **Functional Description**

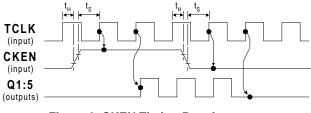

The W40C06A enable pin provides start/stop control of buffer outputs Q0 through Q5. Refer to *Table 1*, "Output Enable Selection," for decoding. Active (enabled) outputs are in phase with TCLK but are phase delayed by several nanoseconds. Low (disabled) outputs are held at logic LOW.

## Synchronization Logic

#### Output Control

To prevent output "short cycling," internal synchronization logic is used to ensure complete clocks cycles. This is true for both output enable or disable. Upon enabling an output, there is a maximum latency of four clock cycles, assuming the crystal oscillator is active.

#### **Clock Transmission Lines in System Applications**

With the increase in system clock frequencies, transmission line theory is commonly being applied to the design of clock distribution lines. High-speed logic systems typically require tight skew control between clock lines, which means that the clock signal must have short rise/fall times to overcome the effect of noise. Short rise/fall times may create other problems such as signal overshoot/undershoot and signal reflections which may result in distorting the signal at the load end. These problems must be avoided since they create unwanted clock skew.

Reflections and signal overshoot/undershoot can be controlled by designing clock distribution traces as transmission lines. A transmission line accepts and delivers a clock signal without distortion or reflections if its impedance is matched to the line source and load. In system clock line implementation, source impedance is typically controlled but is not practical to control load impedance.

Clock source impedance is matched to the transmission line by using series termination; this involves the addition of a series termination resistor between the output pin and transmission line to, in effect, raise the output buffer impedance to match the line. For example, if the clock output buffer impedance is  $30\Omega$  and the transmission line impedance is  $50\Omega$ , a  $20\Omega$  termination resistor connected between the clock output and transmission line will match the two (the clock buffer impedance becomes  $50\Omega$ ).

The end of the transmission line is usually "open" with the only load being the typically high-resistance capacitive load of the logic input on the device being clocked. This condition causes a reflection to be sent back to the source. If the source is properly matched to line (through series termination), this reflection will be absorbed (a poorly matched source will re-reflect the pulse edge which can cause waveform distortion by mixing a reflected edge with a new clock pulse edge).

It is interesting to note that when a new clock edge is first driven into the transmission line, the voltage level at the input of the line is only one-half the final signal amplitude, assuming a properly matched line. This edge remains at half amplitude for the time it takes for the edge to reach the end of the line and back. The edge travels down the line at a speed of about 0.2 ns per inch of transmission, so for a five-inch line this round-trip takes about 2.0 ns. During that time, the clock source dissipates power at the rate of  $(V_{DD}/2)^2/R$ , where R is the sum resistance of the output buffer and series termination resistor (this assumes the case of a CMOS output driver, as used in the W40C06A, where the clock signal amplitude is equal to  $V_{DD}$ ).

#### W40C06A Clock Driver Advantages

#### Low Output Impedance

The typical CMOS clock buffer device has an output impedance of around 50 $\Omega$ . This means that a typical 60 $\Omega$  transmission line can be properly series terminated with a 10 $\Omega$  matching resistor. However, two 60 $\Omega$  transmission lines could not be driven with series termination (to maintain good waveform integrity) since this presents a 30 $\Omega$  load to the buffer.

The W40C06A exhibits a  $5\Omega$  typical buffer output impedance. The main advantage of the low W40C06A output impedance is that one output can drive more than one transmission line while maintaining proper series termination. For example, if

# W40C06A

driving two  $50\Omega$  lines, the W40C06A buffer output resistance (as seen by each line) will be about  $10\Omega$ , therefore each line can be series terminated with a  $40\Omega$  resistor.

Other advantages are also gained by the W40C06A buffer output impedance being much less than the series termination resistor value. First, output buffer impedance variation will have less effect on total source impedance. A CMOS output buffer can vary as much as  $\pm 20\%$  with changes in process and operating conditions, while variation of the termination resistor is typically less than 5%. Source impedance (with less variation) results in better signal integrity. Second, more power will be dissipated by the series termination resistor than by the output buffer. This can be important when driving many long

transmission lines; the termination resistors are less affected by heating than are CMOS buffer devices.

#### Controlled Output Rise and Fall Time

The W40C06A incorporates internal clock edge rise/fall time control to further improve clock integrity. Rise/fall times that are too fast cause excessive signal overshoot/undershoot due to interactions between the high device impulse current and power supply inductance caused by the device packaging. Rise/fall times that are too slow make it difficult to meet the system clock skew requirement, especially in the presence of system noise.

# **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| Т <sub>В</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

# 3.3V DC Electrical Characteristics: $T_A = 0^{\circ}C$ to +70°C, $V_{DD} = 3.3V \pm 10\%$

| Parameter       | Description         | Description Test Condition                       |      | Тур | Max | Unit |  |

|-----------------|---------------------|--------------------------------------------------|------|-----|-----|------|--|

| I <sub>DD</sub> | Supply Current      | Note 1                                           |      | 50  | 60  | mA   |  |

| I <sub>DD</sub> | Standby Current     | CKEN = 0                                         |      | 7   | 12  | μA   |  |

| V <sub>IL</sub> | Input Low Voltage   | V <sub>DD</sub> = 3.3V                           |      |     | 0.8 | V    |  |

| V <sub>IH</sub> | Input High Voltage  | V <sub>DD</sub> = 3.3V                           | 2.0  |     |     | V    |  |

| V <sub>OL</sub> | Output Low Voltage  | I <sub>OL</sub> = 48 mA, V <sub>DD</sub> = 3.3V  |      |     | 0.4 | V    |  |

| V <sub>OH</sub> | Output High Voltage | I <sub>OH</sub> = -48 mA, V <sub>DD</sub> = 3.3V | 2.4  |     |     | V    |  |

| IL              | Input Low Current   | V <sub>IN</sub> = 0V                             | -2.5 |     | 2.5 | μA   |  |

| I <sub>IH</sub> | Input High Current  | $V_{IN} = V_{DD}$                                | -2.5 |     | 2.5 | μA   |  |

| C <sub>IN</sub> | Input Capacitance   | Except pin TCLK                                  |      | 5   | 9   | pF   |  |

| CL              | Load Capacitance    | Pin TCLK                                         |      | 6   |     | pF   |  |

# 3.3V AC Electrical Characteristics: $T_A = 0^{\circ}C$ to +70°C, $V_{DD} = 3.3V \pm 10\%^{[2]}$

| Parameter        | Description                        | Test Condition               | Min | Тур | Max | Unit <sup>[3]</sup> |

|------------------|------------------------------------|------------------------------|-----|-----|-----|---------------------|

| f <sub>IN</sub>  | Input Frequency                    | TTL clock into TCLK          | 0   |     | 100 | MHz                 |

| Z <sub>OUT</sub> | Active Output Source Impedance     |                              |     | 5.0 |     | Ω                   |

| t <sub>ON</sub>  | Start-up Time to First Clock Cycle | Oscillator initially off     |     |     | 5   | ms                  |

| t <sub>OFF</sub> | Turnoff Time to Standby State      | Oscillator initially running |     |     | 4   | cycles              |

| t <sub>EN</sub>  | Output Enable Time                 | Oscillator already running   |     |     | 4   | cycles              |

| t <sub>DIS</sub> | Output Disable Time                | Oscillator stays running     |     |     | 4   | cycles              |

| t <sub>R</sub>   | Output Rise Edge Rate              | Outputs loaded               | 1   |     | 4   | V/ns                |

| t <sub>F</sub>   | Output Fall Edge Rate              | Outputs loaded               | 1   |     | 4   | V/ns                |

| t <sub>SR</sub>  | Output Skew Rising Edges           | Same package                 |     | 200 | 400 | ps                  |

| t <sub>SF</sub>  | Output Skew Falling Edges          | Same package                 |     | 200 | 500 | ps                  |

| t <sub>D</sub>   | Duty Cycle                         |                              | 45  | 50  | 55  | %                   |

| t <sub>JA</sub>  | Jitter, Absolute                   | Outputs loaded               |     |     | 300 | ps                  |

Notes:

W40C06A with no output loading. All AC tests are performed with 20-pF load on each clock output unless otherwise specified. Threshold voltage for timing measurements is 1.5V. Unit "cycles" implies input clock cycles. 1. 2. 3.

# W40C06A

# **Applications Information**

### **Series Termination**

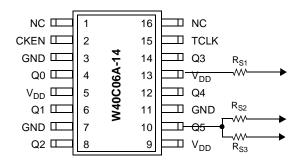

Resistors R<sub>S1</sub>, R<sub>S2</sub>, and R<sub>S3</sub> in *Figure 3* are series termination resistors used for matching the impedance of the output buffer to the impedance of the transmission line. This is accomplished by sizing the series termination resistor value so that when added to the output buffer impedance this value matches the transmission line impedance. The resistors should be placed as close to the output pins as possible.

In *Figure 3*, output Q5 drives one line and Q3 drives two lines (for diagrammatic simplicity not all device pins are connected). As stated previously, the W40C06A exhibits a  $5\Omega$  buffer imped-

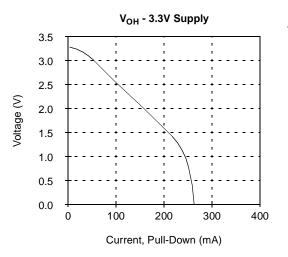

V<sub>OL</sub> - 3.3V Supply 3.5 3.0 2.5 2.0 1.5 1.0 0.5 0.0 0 100 200 300 400

Current, Pull-Up (mA)

ance when driving one  $50\Omega$  transmission line and appears to have an  $8\Omega-12\Omega$  impedance when driving two transmission lines as viewed from each line). Assuming this transmission line impedance, this means that R<sub>S1</sub> needs to be  $45\Omega$  and R<sub>S2</sub>, R<sub>S3</sub> need to be  $40\Omega$  each.

In order to drive the typical capacitive load of a CMOS input, typical transmission line impedance is  $50\Omega$ -100 $\Omega$ .

### **Power Supply Connections**

GND pins should be connected directly to the ground plane. Each  $V_{\text{DD}}$  pin should be connected to the power plane and should include a decoupling capacitor.

# Figure 1. Typical DC Output V/I Characteristics

Figure 2. CKEN Timing Requirements

Figure 3. Application Diagram

## **Ordering Information**

| Ordering Code | Freq. Mask<br>Code | Package<br>Name | Package Type                  |

|---------------|--------------------|-----------------|-------------------------------|

| W40C06A       | -14                | Н               | 16-pin Plastic SSOP (150-mil) |

Pentium is a registered trademark of Intel Corporation. Document #: 30-00810

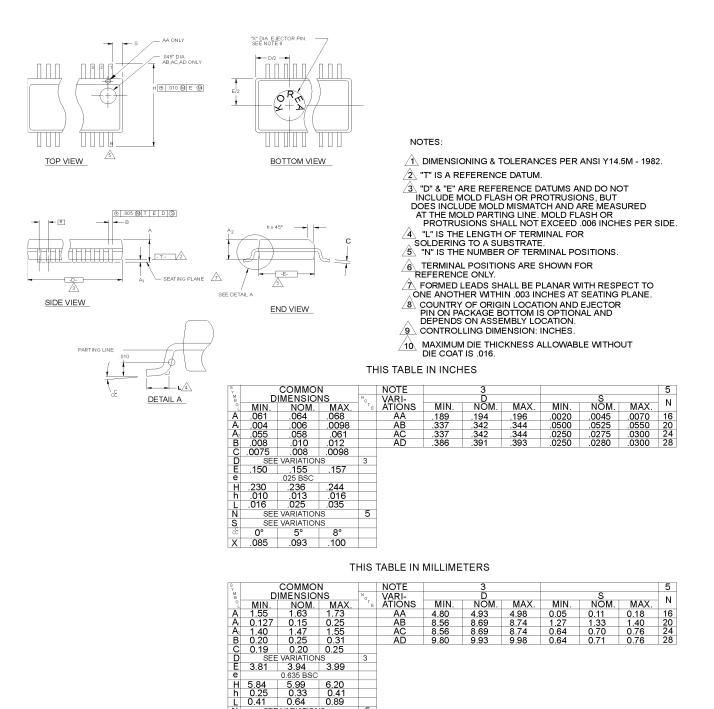

# Package Diagram

# 16-Pin Shrink Small Outline Package (TSSOP, 0.150 inch)

© Cypress Semiconductor Corporation, 1999. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use nductor product. Nor d uitry embodied in a C under patent

8

2.54

5

L N

S

0°

X 2.16

SEE VARIATIONS

SEE VARIATIONS

5°

2.36