查询CY7C331供应商

捷多邦,专业PCB打样工厂,24小时加急出一级 id: 6016

## CY7C331

#### Features

- Twelve I/O macrocells each having:

- One state flip-flop with an XOR sum-of-products input

PRESS

- One feedback flip-flop with input coming from the I/O pin

- Independent (product term) set, reset, and clock inputs on all registers

- Asynchronous bypass capability on all registers under product term control (r = s = 1)

- Global or local output enable on three-state I/O

- Feedback from either register to the array

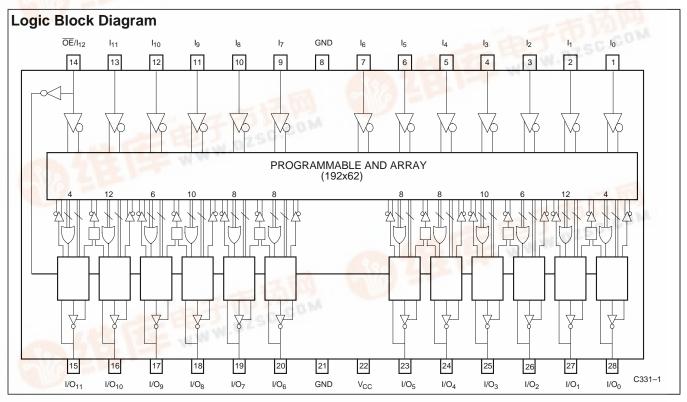

- 192 product terms with variable distribution to macrocells

- 13 inputs, 12 feedback I/O pins, plus 6 shared I/O macrocell feedbacks for a total of 31 true and complementary inputs

- High speed: 20 ns maximum t<sub>PD</sub>

- · Security bit

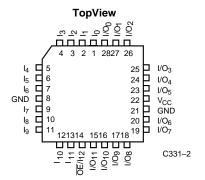

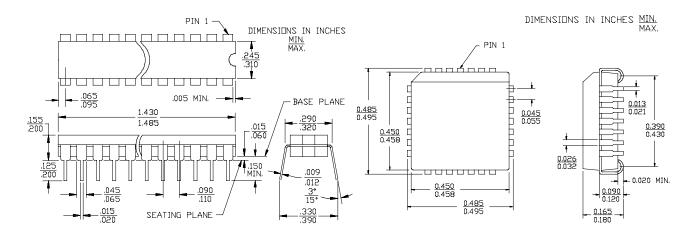

- Space-saving 28-pin slim-line DIP package; also available in 28-pin PLCC

## Asynchronous Registered EPLD

- Low power

- —90 mA typical I<sub>CC</sub> quiescent

- 180 mA I<sub>CC</sub> maximum

- Programming and operation 100% testable

#### **Functional Description**

The CY7C331 is the most versatile PLD available for asynchronous designs. Central resources include twelve full D-type flip-flops with separate set, reset, and clock capability. For increased utility, XOR gates are provided at the D-inputs and the product term allocation per flip-flop is variably distributed.

#### I/O Resources

Pins 1 through 7 and 9 through 14 serve as array inputs; pin 14 may also be used as a global output enable for the I/O macrocell three-state outputs. Pins 15 through 20 and 23 through 28 are connected to I/O macrocells and may be managed as inputs or outputs depending on the configuration and the macrocell OE terms.

#### **Selection Guide**

| Generic Part | I <sub>CC1</sub> | (mA) | t <sub>PD</sub> (ns) |     | s) t <sub>S</sub> (ns) |     | t <sub>S</sub> (ns) |     | t <sub>CO</sub> (ns) |  |

|--------------|------------------|------|----------------------|-----|------------------------|-----|---------------------|-----|----------------------|--|

| Number       | Com'l            | Mil  | Com'l                | Mil | Com'l                  | Mil | Com'l               | Mil |                      |  |

| CY7C331-20   | 130              |      | 20                   |     | 12                     |     | 20                  |     |                      |  |

| CY7C331-25   | 120              | 160  | 25                   | 25  | 12                     | 15  | 25                  | 25  |                      |  |

| CY7C331-30   |                  | 150  |                      | 30  |                        | 15  |                     | 30  |                      |  |

| CY7C331-40   |                  | 150  |                      | 40  |                        | 20  |                     | 40  |                      |  |

### **Pin Configuration**

#### I/O Resources (continued)

It should be noted that there are two ground connections (pins 8 and 21) which, together with  $V_{CC}$  (pin 22) are located centrally on the package. The reason for this placement and dual-ground structure is to minimize the ground-loop noise when the outputs are driving simultaneously into a heavy capacitive load.

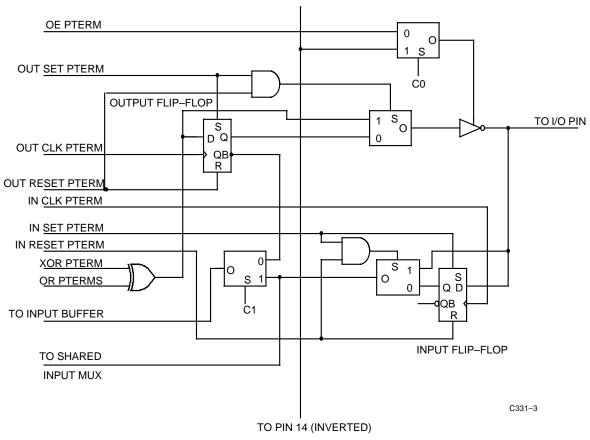

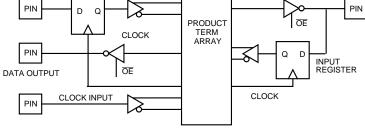

The CY7C331 has twelve I/O macrocells (see *Figure 1*). Each macrocell has two D-type flip-flops. One is fed from the array, and one from the I/O pin. For each flip-flop there are three dedicated product terms driving the R, S, and clock inputs, respectively. Each macrocell has one input to the array and for each pair of macrocells there is one shared input to the array. The macrocell input to the array may be configured to come from the 'Q' output of either flip-flop.

TO PIN 14 (INVERTED)

Figure 1. I/O Macrocell

CY7C331

#### I/O Resources (continued)

The D-type flip-flop that is fed from the array (i.e., the state flip-flop) has a logical XOR function on its input that combines a single product term with a sum(OR) of a number of product terms. The single product term is used to set the polarity of the output or to implement toggling (by including the current output in the product term).

The R and S inputs to the flip-flops override the current setting of the 'Q' output. The S input sets 'Q' true and the R input resets 'Q' (sets it false). If both R and S are asserted (true) at once, then the output will follow the input ('Q' = 'D') (see *Table 1*).

#### Table 1. RS Truth Table

| R | S | Q |

|---|---|---|

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 1 | D |

#### **Shared Input Multiplexer**

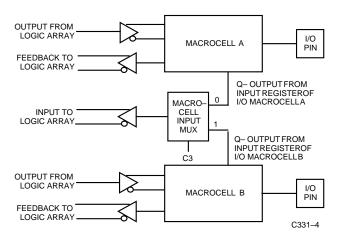

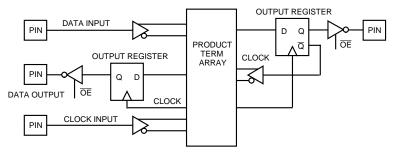

The input associated with each pair of macrocells may be configured by the shared input multiplexer to come from either macrocell; the 'Q' output of the flip-flop coming from the I/O pin is used as the input signal source (see *Figure 2*).

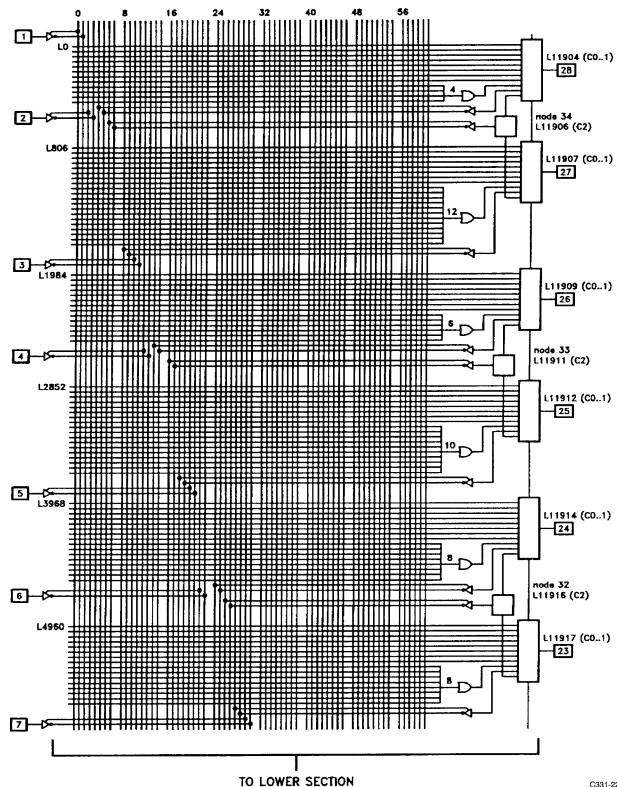

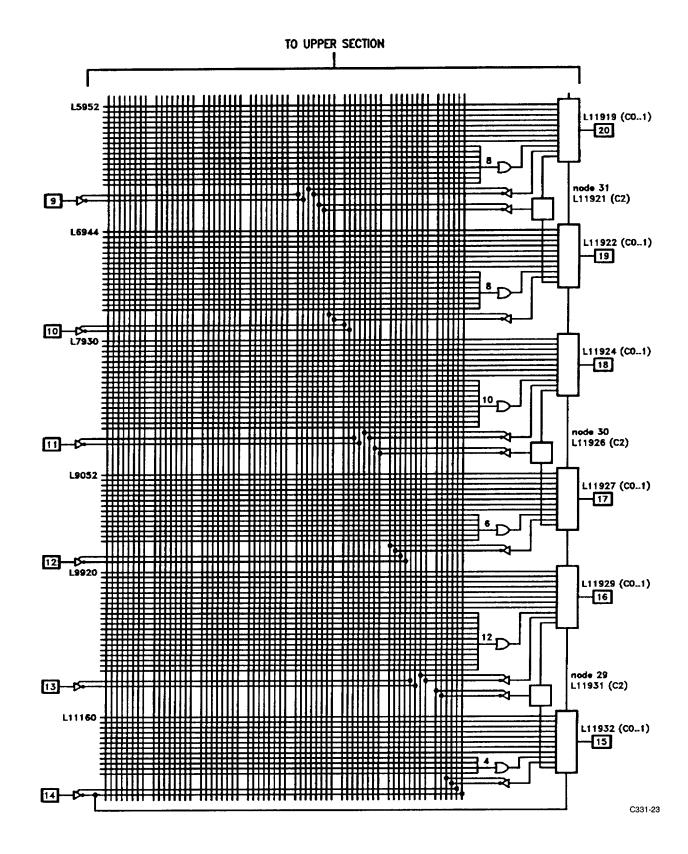

#### **Product Term Distribution**

The product terms are distributed to the macrocells such that 32 product terms are distributed between two adjacent macrocells.

The pairing of macrocells is the same as it is for the shared inputs. Eight of the product terms are used in each macrocell for set, reset, clock, output enable, and the upper part of the XOR gate. This leaves 16 product terms per pair of macrocells to be divided between the sum-of-products inputs to the two state registers. The following table shows the I/O pin pairing for shared inputs, and the product term (PT) allocation to macrocells associated with the I/O pins (see *Table 2*).

| Table 2. | . Product Te | erm Distribution |

|----------|--------------|------------------|

|----------|--------------|------------------|

| Macrocell | Pin Number | Product Terms |

|-----------|------------|---------------|

| 0         | 28         | 4             |

| 1         | 27         | 12            |

| 2         | 26         | 6             |

| 3         | 25         | 10            |

| 4         | 24         | 8             |

| 5         | 23         | 8             |

| 6         | 20         | 8             |

| 7         | 19         | 8             |

| 8         | 18         | 10            |

| 9         | 17         | 6             |

| 10        | 16         | 12            |

| 11        | 15         | 4             |

Figure 2. Shared Input Multiplexer

The CY7C331 is configured by three arrays of configuration bits (C0, C1, C2). For each macrocell, there is one C0 bit and one C1 bit. For each pair of macrocells there is one C2 bit.

There are twelve C0 bits, one for each macrocell. If C0 is programmed for a macrocell, then the three-state enable (OE) will be controlled by pin 14 (the global OE). If C0 is not programmed, then the OE product term for that macrocell will be used.

There are twelve C1 bits, one for each macrocell. The C1 bit selects inputs for the product term (PT) array from either the state register (if the bit is unprogrammed) or the input register (if the bit is programmed).

There are six C2 bits, providing one C2 bit for each pair of macrocells. The C2 bit controls the shared input multiplexer; if the C2 bit is not programmed, then the input to the product term array comes from the upper macrocell (A). If the C2 bit is programmed, then the input comes from the lower macrocell (B).

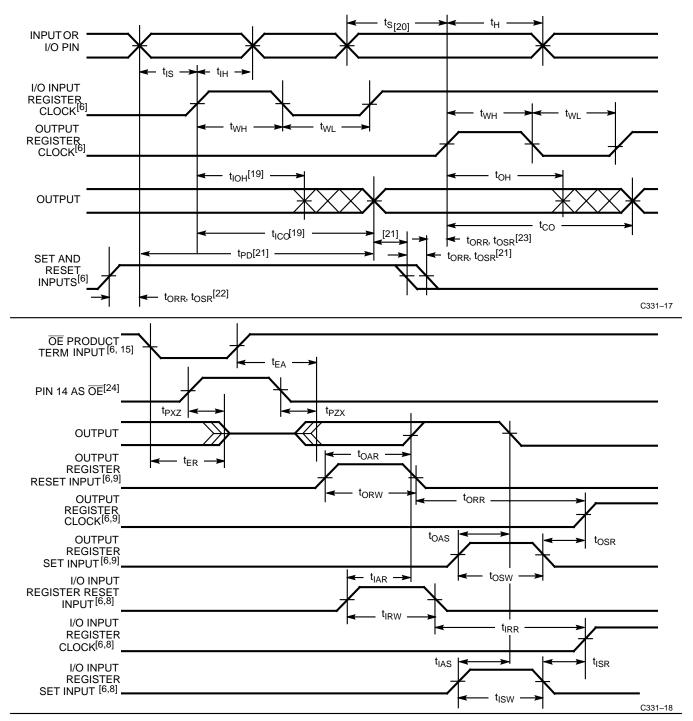

The timing diagrams for the CY7C331 cover state register, input register, and various combinational delays. Since internal clocks are the outputs of product terms, all timing is from the transition of the inputs causing the clock transition.

### **Maximum Ratings**

| (Above which the useful life may be impaired. For user guide-<br>lines, not tested.) |

|--------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                    |

| Ambient Temperature with<br>Power Applied–55°C to +125°C                             |

| Supply Voltage to Ground Potential<br>(Pin 28 to Pin 8 or 21)0.5V to +7.0V           |

| DC Input Voltage3.0V to +7.0V                                                        |

| Output Current into Outputs (LOW)12 mA                                               |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | >1500V  |

|------------------------------------------------------------|---------|

| Latch-Up Current                                           | >200 mA |

| DC Programming Voltage                                     | 13.0 V  |

### **Operating Range**

| Range                   | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ± 10%        |

| Military <sup>[1]</sup> | –55°C to +125°C        | 5V ± 10%        |

### Electrical Characteristics Over the Operating Range<sup>[2]</sup>

| Parameter        | Description                                    | Test Conditions                                                                                                       |              | Min. | Max. | Unit |

|------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|

| V <sub>OH</sub>  | Output HIGH Voltage                            | $V_{CC}$ = Min., $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>$I_{OH}$ = -3.2 mA (Com'I), $I_{OH}$ = -2 mA (MiI)                |              |      |      | V    |

| V <sub>OL</sub>  | Output LOW Voltage                             | $V_{CC} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$I_{OL} = 12 \text{ mA (Com'l), } I_{OL} = 8 \text{ mA (Mil)}$ |              |      | 0.5  | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                             | Guaranteed HIGH Input, all Inputs <sup>[3]</sup>                                                                      |              | 2.2  |      | V    |

| V <sub>IL</sub>  | Input LOW Voltage                              | Guaranteed LOW Input, all Inputs <sup>[3]</sup>                                                                       |              |      | 0.8  | V    |

| I <sub>IX</sub>  | Input Leakage Current                          | $V_{SS} < V_{IN} < V_{CC}$ , $V_{CC} = Max$ .                                                                         |              | -10  | +10  | μA   |

| I <sub>OZ</sub>  | Output Leakage Current                         | $V_{SS} < V_{OUT} < V_{CC}$ , $V_{CC} = Max$ .                                                                        |              | -40  | +40  | μA   |

| I <sub>SC</sub>  | Output Short Circuit<br>Current <sup>[4]</sup> | $V_{CC} = Max., V_{OUT} = 0.5V^{[5]}$                                                                                 |              | -30  | -90  | mA   |

| I <sub>CC1</sub> | Standby Power Supply                           | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND,                                                                        | Com'l –20    |      | 130  | mA   |

|                  | Current                                        | Outputs Open                                                                                                          | Com'l –25    |      | 120  |      |

|                  |                                                |                                                                                                                       | Mil –25      |      | 160  | mA   |

|                  |                                                |                                                                                                                       | Mil –30, –40 |      | 150  |      |

| I <sub>CC2</sub> | Power Supply Current at                        | V <sub>CC</sub> = Max., Outputs Disabled                                                                              | Com'l        |      | 180  | mA   |

|                  | Frequency <sup>[4, 6]</sup>                    | (in High Z State)<br>Device Operating at f <sub>MAX</sub> External (f <sub>MAX1)</sub>                                | Mil          |      | 200  |      |

## Capacitance<sup>[4]</sup>

| Parameter        | Description        | Test Conditions               | Max. | Unit |

|------------------|--------------------|-------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 2.0V$ at f = 1 MHz  | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{OUT} = 2.0V$ at f = 1 MHz | 10   | pF   |

Notes:

T<sub>A</sub> is the "instant on" case temperature. 1.

2. 3. 4. 5.

I<sub>A</sub> is the "instant on" case temperature. See the last page of this specification for Group A subgroup testing information. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included. Tested initially and after any design or process changes that may affect these parameters. Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V<sub>OUT</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation. Because these input signals are controlled by product terms, active input polarity may be of either polarity. Internal active input polarity has been shown for clarity.

6. clarity.

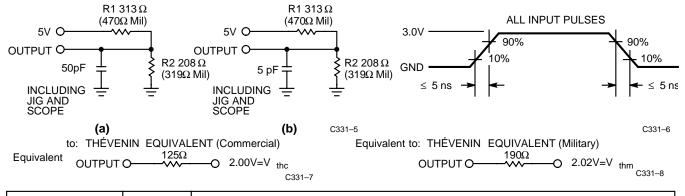

## AC Test Loads and Waveforms

| Parameter           | Vx               |                 | Output Waveform—Measurement | Level           |         |

|---------------------|------------------|-----------------|-----------------------------|-----------------|---------|

| t <sub>PXZ(-)</sub> | 1.5V             | V <sub>OH</sub> | 0.5V                        | V <sub>X</sub>  | C331–9  |

| t <sub>PXZ(+)</sub> | 2.6V             | V <sub>OL</sub> | 0.5                         | V <sub>X</sub>  | C331–10 |

| t <sub>PZX(+)</sub> | V <sub>thc</sub> | V <sub>X</sub>  | 0.5\                        | V <sub>OH</sub> | C331–11 |

| t <sub>PZX(-)</sub> | V <sub>thc</sub> | V <sub>X</sub>  | 0.5V                        | V <sub>OL</sub> | C331–12 |

| t <sub>ER(-)</sub>  | 1.5V             | V <sub>OH</sub> | 0.5V                        | V <sub>X</sub>  | C331–13 |

| t <sub>ER(+)</sub>  | 2.6V             | V <sub>OL</sub> | 0.5                         | V <sub>X</sub>  | C331–14 |

| t <sub>EA(+)</sub>  | V <sub>thc</sub> | V <sub>X</sub>  | 0.5\                        | V <sub>OH</sub> | C331–15 |

| t <sub>EA(-)</sub>  | V <sub>thc</sub> | V <sub>X</sub>  | 0.5                         | V <sub>OL</sub> | C331–16 |

#### (c) Test Waveforms and Measurement Levels

#### Switching Characteristics Over the Operating Range<sup>[2]</sup>

|                  |                                                                      |      | Commercial                  |      |      |      |

|------------------|----------------------------------------------------------------------|------|-----------------------------|------|------|------|

|                  |                                                                      | -    | 2025<br>Min. Max. Min. Max. |      | 25   |      |

| Parameter        | Description                                                          | Min. | Max.                        | Min. | Max. | Unit |

| t <sub>PD</sub>  | Input to Output Propagation Delay <sup>[7]</sup>                     |      | 20                          |      | 25   | ns   |

| t <sub>ICO</sub> | Input Register Clock to Output Delay <sup>[8]</sup>                  |      | 35                          |      | 40   | ns   |

| t <sub>IOH</sub> | Output Data Stable Time from Input Clock <sup>[8]</sup>              | 5    |                             | 5    |      | ns   |

| t <sub>IS</sub>  | Input or Feedback Set-Up Time to Input Register Clock <sup>[8]</sup> | 2    |                             | 2    |      | ns   |

| t <sub>IH</sub>  | Input Register Hold Time from Input Clock <sup>[8]</sup>             | 11   |                             | 13   |      | ns   |

| t <sub>IAR</sub> | Input to Input Register Asynchronous Reset Delay <sup>[8]</sup>      |      | 35                          |      | 40   | ns   |

#### Commercial -20 -25 Parameter Description Min. Max. Min. Max. Unit Input Register Reset Width<sup>[4, 8]</sup> 35 40 t<sub>IRW</sub> ns Input Register Reset Recovery Time<sup>[4, 8]</sup> 40 35 ns t<sub>IRR</sub> Input to Input Register Asynchronous Set Delay<sup>[8]</sup> 35 40 ns t<sub>IAS</sub> Input Register Set Width<sup>[4, 8]</sup> 35 40 ns t<sub>ISW</sub> Input Register Set Recovery Time<sup>[4, 8]</sup> 35 40 ns t<sub>ISR</sub> Input and Output Clock Width HIGH<sup>[8, 9, 10]</sup> 12 15 ns t<sub>WH</sub> Input and Output Clock Width LOW<sup>[8, 9, 10]</sup> 12 15 t<sub>WL</sub> ns Maximum Frequency with Feedback in Input Registered Mode $(1/(t_{ICO}+t_{IS}))^{[11]}$ 27.0 23.8 MHz f<sub>MAX1</sub> Maximum Frequency Data Path in Input Registered Mode (Lowest 28.5 25.0 MHz f<sub>MAX2</sub> of $1/t_{ICO}$ , $1/(t_{WH} + t_{WI})$ , or $1/(t_{IS} + t_{IH})^{[8]}$ Output Data Stable from Input Clock Minus Input Register Input Hold Time for $7C335^{\left[12,\ 13\right]}$ t<sub>IOH</sub>-t<sub>IH</sub>33X 0 0 ns Output Register Clock to Output Delay<sup>[9]</sup> 20 25 ns t<sub>CO</sub> Output Data Stable Time from Output Clock<sup>[9]</sup> 3 3 t<sub>OH</sub> ns Output Register Input Set-Up Time to Output Clock<sup>[9]</sup> 12 12 t<sub>S</sub> ns Output Register Input Hold Time from Output Clock<sup>[9]</sup> 8 8 t<sub>H</sub> ns Input to Output Register Asynchronous Reset Delav<sup>[9]</sup> 20 25 ns t<sub>OAR</sub> Output Register Reset Width<sup>[9]</sup> 20 25 tORW ns Output Register Reset Recovery Time<sup>[9]</sup> 20 25 ns tORR Input to Output Register Asynchronous Set Delay<sup>[9]</sup> 20 25 ns tOAS Output Register Set Width<sup>[9]</sup> 20 25 ns tosw Output Register Set Recovery Time<sup>[9]</sup> 20 25 tOSR ns Input to Output Enable Delay<sup>[14, 15]</sup> 25 25 ns t<sub>EA</sub> Input to Output Disable Delay<sup>[14, 15]</sup> 25 25 ns t<sub>FR</sub> Pin 14 to Output Enable Delay<sup>[14, 15]</sup> 20 20 t<sub>PZX</sub> ns Pin 14 to Output Disable Delav<sup>[14, 15]</sup> 20 20 t<sub>PXZ</sub> ns Maximum Frequency with Feedback in Output Registered Mode $(1/(t_{CO} + t_S))^{[16, 17]}$ 31.2 27.0 MHz f<sub>MAX3</sub> Maximum Frequency Data Path in Output Registered Mode (Lowest 41.6 33.3 MHz f<sub>MAX4</sub> of $1/t_{CO}$ , $1/(t_{WH} + t_{WL})$ , or $1/(t_{S} + t_{H}))^{[9]}$ Output Data Stable from Output Clock Minus Input t<sub>OH</sub>-t<sub>IH</sub>33X 0 0 ns Register Input Hold Time for 7C335<sup>[13, 18]</sup> Maximum Frequency Pipelined Mode<sup>[10, 17]</sup> 35.0 f<sub>MAX5</sub> 30.0 MHz

#### Switching Characteristics Over the Operating Range<sup>[2]</sup> (continued)

Notes:

7

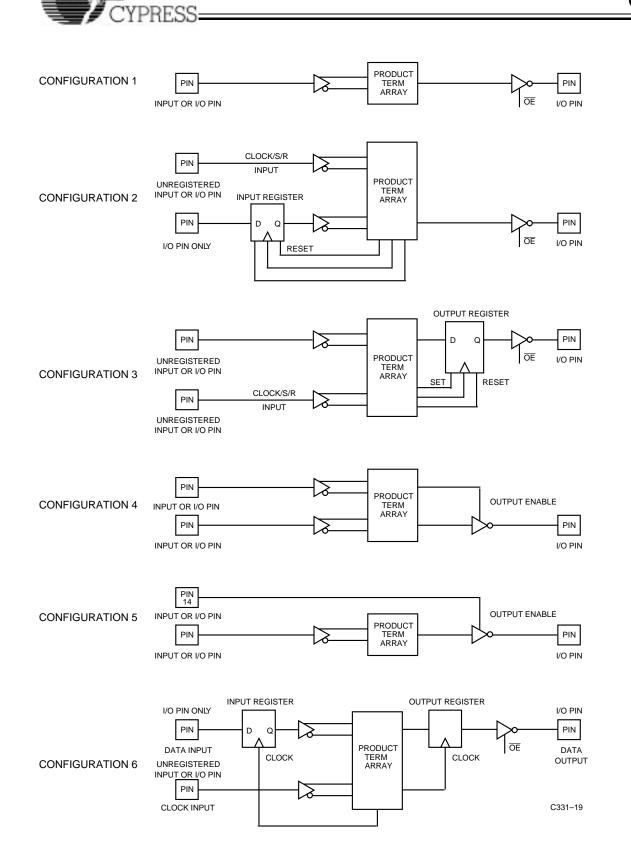

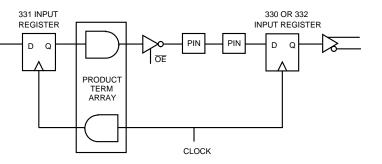

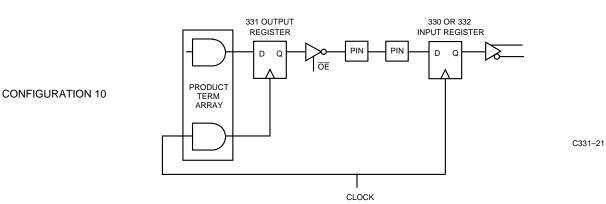

Refer to *Figure 3*, configuration 1. Refer to *Figure 3*, configuration 2. Refer to *Figure 3*, configuration 3. 8.

9. 10.

Refer to *Figure 3*, configuration 6. Refer to *Figure 3*, configuration 7. 11.

12. Refer to Figure 3, configuration 9.

This specification is intended to guarantee interface compatibility of the other members of the CY7C330 family with the CY7C331. This specification is met for the devices noted operating at the same ambient temperature and at the same power supply voltage. These parameters are tested periodically by sampling 13.

of production product. 14. Part (a) of AC Test Loads and Waveforms used for all parameters except t<sub>PZXI</sub>, t<sub>PXZI</sub>, t<sub>PZX</sub>, and t<sub>PXZ</sub>, which use part (b). Part (c) shows the test waveforms and measurement levels.

Refer to Figure 3, configuration 4. 15. 16. Refer to Figure 3, configuration 8.

This specification is intended to guarantee that a state machine configuration created with internal or external feedback can be operated with output register and input register clocks controlled by the same source. These parameters are tested by periodic sampling of production product. 17.

## Switching Characteristics Over the Operating Range<sup>[2]</sup> (continued)

|                                       |                                                                                                                                       |        |      | Mil  | itary |      |      |      |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|------|------|------|--|

|                                       |                                                                                                                                       | -25 -3 |      |      | 30    | _    | 40   | +    |  |

| Parameter                             | Description                                                                                                                           | Min.   | Max. | Min. | Max.  | Min. | Max. | Unit |  |

| t <sub>PD</sub>                       | Input to Output Propagation Delay <sup>[7]</sup>                                                                                      |        | 25   |      | 30    |      | 40   | ns   |  |

| t <sub>ICO</sub>                      | Input Register Clock to Output Delay <sup>[4, 8]</sup>                                                                                |        | 45   |      | 50    |      | 65   | ns   |  |

| t <sub>IOH</sub>                      | Output Data Stable Time from Input Clock <sup>[4, 8]</sup>                                                                            | 5      |      | 5    |       | 5    |      | ns   |  |

| t <sub>IS</sub>                       | Input or Feedback Set-Up Time to Input Register Clock <sup>[8]</sup>                                                                  | 5      |      | 5    |       | 5    |      | ns   |  |

| t <sub>IH</sub>                       | Input Register Hold Time from Input Clock <sup>[4, 8]</sup>                                                                           | 13     |      | 15   |       | 20   |      | ns   |  |

| t <sub>IAR</sub>                      | Input to Input Register Asynchronous Reset Delay <sup>[4, 8]</sup>                                                                    |        | 45   |      | 50    |      | 65   | ns   |  |

| t <sub>IRW</sub>                      | Input Register Reset Width <sup>[8]</sup>                                                                                             | 45     |      | 50   |       | 65   |      | ns   |  |

| t <sub>IRR</sub>                      | Input Register Reset Recovery Time <sup>[8]</sup>                                                                                     | 45     |      | 50   |       | 65   |      | ns   |  |

| t <sub>IAS</sub>                      | Input to Input Register Asynchronous Set Delay <sup>[8]</sup>                                                                         |        | 45   |      | 50    |      | 65   | ns   |  |

| t <sub>ISW</sub>                      | Input Register Set Width <sup>[8]</sup>                                                                                               | 45     |      | 50   |       | 65   |      | ns   |  |

| t <sub>ISR</sub>                      | Input Register Set Recovery Time <sup>[8]</sup>                                                                                       | 45     |      | 50   |       | 65   |      | ns   |  |

| t <sub>WH</sub>                       | Input and Output Clock Width High <sup>[8, 9, 10]</sup>                                                                               | 15     |      | 20   |       | 25   |      | ns   |  |

| t <sub>WL</sub>                       | Input and Output Clock Width Low <sup>[8, 9, 10]</sup>                                                                                | 15     |      | 20   |       | 25   |      | ns   |  |

| f <sub>MAX1</sub>                     | Maximum frequency with Feedback in Input Registered<br>Mode $(1/(t_{ICO} + t_{IS}))^{[11]}$                                           | 20.0   |      | 18.1 |       | 14.2 |      | MHz  |  |

| f <sub>MAX2</sub>                     | Maximum frequency Data Path in Input Registered Mode (Lowest of $1/t_{ICO}$ , $1/(t_{WH} + t_{WL})$ , or $1/(t_{IS} + t_{H})^{[8]}$   | 22.2   |      | 20.0 |       | 15.3 |      | MHz  |  |

| t <sub>IOH</sub> -t <sub>IH</sub> 33X | Output Data Stable from Input Clock Minus Input Register<br>Input Hold Time for 7C335 <sup>[12, 13]</sup>                             | 0      |      | 0    |       | 0    |      | ns   |  |

| t <sub>CO</sub>                       | Output Register Clock to Output Delay <sup>[9]</sup>                                                                                  |        | 25   |      | 30    |      | 40   | ns   |  |

| t <sub>OH</sub>                       | Output Data Stable Time from Output Clock <sup>[9]</sup>                                                                              | 3      |      | 3    |       | 3    |      | ns   |  |

| t <sub>S</sub>                        | Output Register Input Set-Up Time to Output Clock <sup>[9]</sup>                                                                      | 15     |      | 15   |       | 20   |      | ns   |  |

| t <sub>H</sub>                        | Output Register Input Hold Time from Output Clock <sup>[9]</sup>                                                                      | 10     |      | 10   |       | 12   |      | ns   |  |

| t <sub>OAR</sub>                      | Input to Output Register Asynchronous Reset Delay <sup>[9]</sup>                                                                      |        | 25   |      | 30    |      | 40   | ns   |  |

| t <sub>ORW</sub>                      | Output Register Reset Width <sup>[9]</sup>                                                                                            | 25     |      | 30   |       | 40   |      | ns   |  |

| t <sub>ORR</sub>                      | Output Register Reset Recovery Time <sup>[9]</sup>                                                                                    | 25     |      | 30   |       | 40   |      | ns   |  |

| t <sub>OAS</sub>                      | Input to Output Register Asynchronous Set Delay <sup>[9]</sup>                                                                        |        | 25   |      | 30    |      | 40   | ns   |  |

| t <sub>OSW</sub>                      | Output Register Set Width <sup>[9]</sup>                                                                                              | 25     |      | 30   |       | 40   |      | ns   |  |

| t <sub>OSR</sub>                      | Output Register Set Recovery Time <sup>[9]</sup>                                                                                      | 25     |      | 30   |       | 40   |      | ns   |  |

| t <sub>EA</sub>                       | Input to Output Enable Delay <sup>[14, 15]</sup>                                                                                      |        | 25   |      | 30    |      | 40   | ns   |  |

| t <sub>ER</sub>                       | Input to Output Disable Delay <sup>[14, 15]</sup>                                                                                     |        | 25   |      | 30    |      | 40   | ns   |  |

| t <sub>PZX</sub>                      | Pin 14 to Output Enable Delay <sup>[14, 15]</sup>                                                                                     |        | 20   |      | 25    |      | 35   | ns   |  |

| t <sub>PXZ</sub>                      | Pin 14 to Output Disable Delay <sup>[14, 15]</sup>                                                                                    |        | 20   |      | 25    |      | 35   | ns   |  |

| f <sub>MAX3</sub>                     | Maximum Frequency with Feedback in Output Registered Mode $1/(t_{CO} + t_S)^{[16, 17]}$                                               | 25.0   |      | 22.2 |       | 16.6 |      | MHz  |  |

| f <sub>MAX4</sub>                     | Maximum Frequency Data Path in Output Registered<br>Mode (Lowest of $1/t_{CO}$ , $1/(t_{WH} + t_{WL})$ , or $1/(t_{S} + t_{H})^{[9]}$ | 33.3   |      | 25.0 |       | 20.0 |      | MHz  |  |

| t <sub>OH</sub> t <sub>IH</sub> 33X   | Output Data Stable from Output Clock Minus Input Register Input Hold Time for 7C335 <sup>[13, 18]</sup>                               | 0      |      | 0    |       | 0    |      | ns   |  |

| f <sub>MAX5</sub>                     | Maximum Frequency Pipelined Mode <sup>[10, 17]</sup>                                                                                  | 28.0   |      | 23.5 |       | 18.5 |      | MHz  |  |

Note:

18. Refer to Figure 3, configuration 10.

### Switching Waveforms

Notes:

- Output register is set in Transparent mode. Output register set and reset inputs are in a HIGH state. 19.

- Dedicated input or input register set in Transparent mode. Input register set and reset inputs are in a HIGH state. Combinatorial Mode. Reset and set inputs of the input and output registers should remain in a HIGH state at least until the output responds at t<sub>PD</sub>. When 20.

- 21. returning set and reset inputs to a LOW state, one of these signals should go LOW a minimum of t<sub>OSR</sub> (set input) or t<sub>ORR</sub> (reset input) prior to the other. This guarantees predictable register states upon exit from Combinatorial mode. When entering the Combinatorial mode, input and output register set and reset inputs must be stable in a HIGH state a minimum of t<sub>ISR</sub> or t<sub>IRR</sub> and t<sub>OSR</sub> or

- 23 or tORR respectively prior to the application of the register clock input.

- Refer to Figure 3, configuration 5. 24.

<sup>22.</sup>  $t_{ORR}$  respectively prior to application of logic input signals. When returning to the input and/or output Registered mode, register set and reset inputs must be stable in a LOW state a minimum of  $t_{ISR}$  or  $t_{IRR}$  and  $t_{OSR}$

#### **CONFIGURATION 7**

#### **CONFIGURATION 8**

C331-20

**CONFIGURATION 9**

#### Figure 3. Timing Configurations (continued)

## CY7C331 Logic Diagram (Upper Half)

## **Ordering Information**

| I <sub>CC1</sub><br>(mA) | t <sub>PD</sub><br>(ns) | t <sub>S</sub><br>(ns) | t <sub>CO</sub><br>(ns) | Ordering Code | Package<br>Name | Package Type                          | Operating<br>Range |

|--------------------------|-------------------------|------------------------|-------------------------|---------------|-----------------|---------------------------------------|--------------------|

| 130                      | 20                      | 12                     | 20                      | CY7C331-20HC  | H64             | 28-Pin Windowed Leaded Chip Carrier   | Commercial         |

|                          |                         |                        |                         | CY7C331-20JC  | J64             | 28-Lead Plastic Leaded Chip Carrier   |                    |

|                          |                         |                        |                         | CY7C331-20PC  | P21             | 28-Lead (300-Mil) Molded DIP          |                    |

|                          |                         |                        |                         | CY7C331-20WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP     |                    |

| 160                      | 25                      | 15                     | 25                      | CY7C331–25DMB | D22             | 28-Lead (300-Mil) CerDIP              | Military           |

|                          |                         |                        |                         | CY7C331-25HMB | H64             | 28-Pin Windowed Leaded Chip Carrier   | -                  |

|                          |                         |                        |                         | CY7C331–25LMB | L64             | 28-Square Leadless Chip Carrier       |                    |

|                          |                         |                        |                         | CY7C331-25QMB | Q64             | 28-Pin Windowed Leadless Chip Carrier |                    |

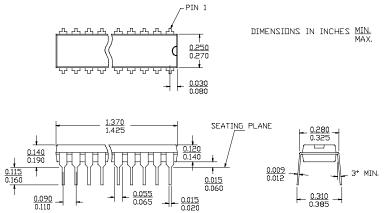

|                          |                         |                        |                         | CY7C331-25TMB | T74             | 28-Lead Windowed Cerpack              |                    |

|                          |                         |                        |                         | CY7C331-25WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP     |                    |

| 120                      | 25                      | 12                     | 25                      | CY7C331-25HC  | H64             | 28-Pin Windowed Leaded Chip Carrier   | Commercial         |

|                          |                         |                        |                         | CY7C331-25JC  | J64             | 28-Lead Plastic Leaded Chip Carrier   |                    |

|                          |                         |                        |                         | CY7C331-25PC  | P21             | 28-Lead (300-Mil) Molded DIP          |                    |

|                          |                         |                        |                         | CY7C331-25WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP     |                    |

| 150                      | 30                      | 15                     | 30                      | CY7C331-30DMB | D22             | 28-Lead (300-Mil) CerDIP              | Military           |

|                          |                         |                        |                         | CY7C331-30HMB | H64             | 28-Pin Windowed Leaded Chip Carrier   |                    |

|                          |                         |                        |                         | CY7C331-30LMB | L64             | 28-Square Leadless Chip Carrier       |                    |

|                          |                         |                        |                         | CY7C331-30QMB | Q64             | 28-Pin Windowed Leadless Chip Carrier |                    |

|                          |                         |                        |                         | CY7C331-30TMB | T74             | 28-Lead Windowed Cerpack              |                    |

|                          |                         |                        |                         | CY7C331-30WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP     |                    |

| 150                      | 40                      | 20                     | 40                      | CY7C331-40DMB | D22             | 28-Lead (300-Mil) CerDIP              | Military           |

|                          |                         |                        |                         | CY7C331-40HMB | H64             | 28-Pin Windowed Leaded Chip Carrier   |                    |

|                          |                         |                        |                         | CY7C331-40LMB | L64             | 28-Square Leadless Chip Carrier       | 1                  |

|                          |                         |                        |                         | CY7C331-40QMB | Q64             | 28-Pin Windowed Leadless Chip Carrier | ]                  |

|                          |                         |                        |                         | CY7C331-40TMB | T74             | 28-Lead Windowed Cerpack              | 1                  |

|                          |                         |                        |                         | CY7C331-40WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP     | ]                  |

## MILITARY SPECIFICATIONS Group A Subgroup Testing

## **DC Characteristics**

| Parameter        | Subgroups |

|------------------|-----------|

| V <sub>OH</sub>  | 1, 2, 3   |

| V <sub>OL</sub>  | 1, 2, 3   |

| V <sub>IH</sub>  | 1, 2, 3   |

| V <sub>IL</sub>  | 1, 2, 3   |

| I <sub>IX</sub>  | 1, 2, 3   |

| I <sub>OZ</sub>  | 1, 2, 3   |

| I <sub>CC1</sub> | 1, 2, 3   |

## **Switching Characteristics**

| Parameter        | Subgroups |

|------------------|-----------|

| t <sub>IS</sub>  | 9, 10, 11 |

| t <sub>IH</sub>  | 9, 10, 11 |

| t <sub>WH</sub>  | 9, 10, 11 |

| t <sub>WL</sub>  | 9, 10, 11 |

| t <sub>CO</sub>  | 9, 10, 11 |

| t <sub>PD</sub>  | 9, 10, 11 |

| t <sub>IAR</sub> | 9, 10, 11 |

| t <sub>IAS</sub> | 9, 10, 11 |

| t <sub>PXZ</sub> | 9, 10, 11 |

| t <sub>PZX</sub> | 9, 10, 11 |

| t <sub>ER</sub>  | 9, 10, 11 |

| t <sub>EA</sub>  | 9, 10, 11 |

| t <sub>S</sub>   | 9, 10, 11 |

| t <sub>H</sub>   | 9, 10, 11 |

Document #: 38-00066-D

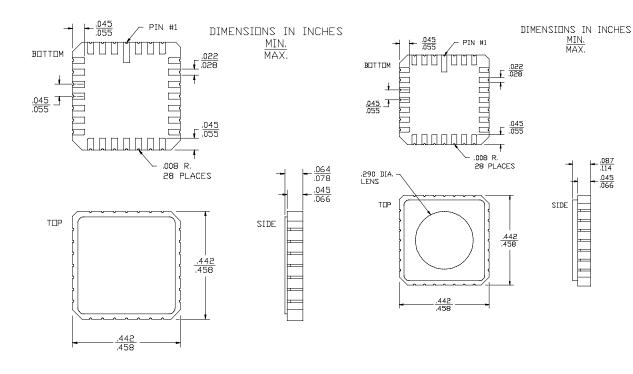

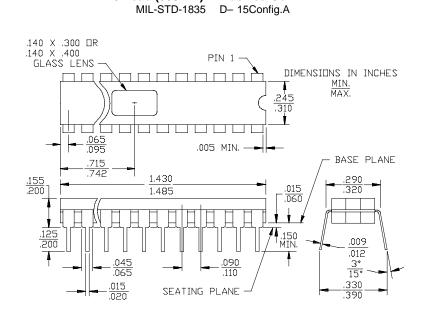

### **Package Diagrams**

#### 28-Lead (300-Mil) CerDIP D22 MIL-STD-1835 D- 15Config.A

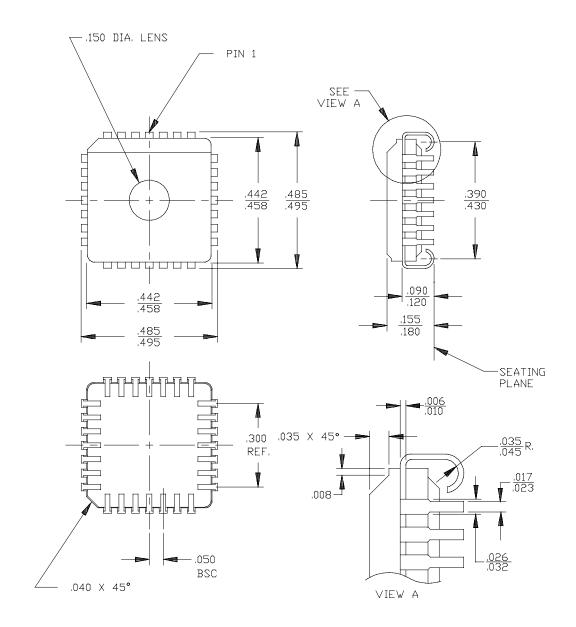

#### 28-Lead Plastic Leaded Chip Carrier J64

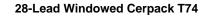

#### 28-Square Leadless Chip Carrier L64 MIL-STD-1835 C-4

#### 28-Pin Windowed Leadless Chip Carrier Q64 MIL-STD-1835 C-4

.087 .114

.045

## Package Diagrams (continued)

### 28-Pin Windowed Leaded Chip Carrier

## Package Diagrams (continued)

# 28-Lead (300-Mil) Molded DIP P21

#### Package Diagrams (continued)

28-Lead (300-Mil) Windowed CerDIP W22

## © Cypress Semiconductor Corporation, 1996. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize