查询DF1704供应商

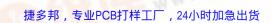

# Sound Stereo, 24-Bit, 96kHz **8X Oversampling Digital Interpolation Filter DIGITAL-TO-ANALOG CONVERTER**

# FEATURES

- COMPANION DIGITAL FILTER FOR THE PCM1704 24-BIT AUDIO DAC

- HIGH PERFORMANCE FILTER: Stopband Attenuation: -115dB Passband Ripple: ±0.00005dB

- AUDIO INTERFACE: Input Data Formats: Standard, Left-Justified, and I<sup>2</sup>S Input Word Length: 16, 20, or 24 Bits

- Output Word Length: 16, 18, 20, or 24 Bits Sampling Frequency: 32kHz to 96kHz

- SYSTEM CLOCK: 256f<sub>S</sub>, 384f<sub>S</sub>, 512f<sub>S</sub>, 768f<sub>S</sub>

- ON-CHIP CRYSTAL OSCILLATOR

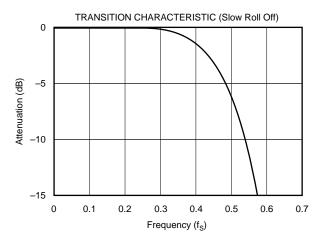

- **PROGRAMMABLE FUNCTIONS:** Hardware or Software Control Modes Sharp or Slow Roll-Off Filter Response Soft Mute Digital De-Emphasis

- Independent Left/Right Digital Attenuation

- +5V SINGLE-SUPPLY OPERATION

- SMALL 28-LEAD SSOP PACKAGE

# DESCRIPTION

The DF1704 is a high performance, stereo, 8X oversampling digital interpolation filter designed for high-end consumer and professional audio applications. The DF1704 supports 24-bit, 96kHz operation and features user-programmable functions, including selectable filter response, de-emphasis, attenuation, and input/output data formats.

The DF1704 is the ideal companion for Burr-Brown's PCM1704 24-bit audio digital-to-analog converter. This combination allows for construction of very high performance audio systems and components. WWW.DZSC.COM

OM International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

All specifications at +25°C,  $V_{\text{DD}}$  = +5V, unless otherwise noted.

| PARAMETER                                                                                                                                                                                                              | CONDITIONS                                                                            | MIN                                                | ТҮР                                                                                          | MAX                                                                                                  | UNITS                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|

| RESOLUTION                                                                                                                                                                                                             |                                                                                       |                                                    | Bits                                                                                         |                                                                                                      |                       |

| INPUT DATA FORMAT<br>Audio Data Interface Format<br>Audio Data Bit Length<br>Audio Data Format<br>Sampling Frequency (f <sub>S</sub> )<br>System Clock Frequency                                                       |                                                                                       | 1<br>MSB-F<br>32                                   | <br>dard/Left-Justified<br>6/20/24 Selectabl<br>First, Two's Binary<br> <br>256/384/512/768f | e<br>Comp<br>  96                                                                                    | kHz                   |

| OUTPUT DATA FORMAT<br>Audio Data Interface Format<br>Audio Data Bit Length<br>Audio Data Format                                                                                                                        |                                                                                       |                                                    | Right-Justified<br>6/20/24 Selectabl<br>st, Binary Two's C                                   |                                                                                                      |                       |

| DIGITAL INPUT/OUTPUT<br>Input Logic Level: V <sub>IH</sub><br>V <sub>IL</sub><br>Output Logic Level: V <sub>OH</sub><br>V <sub>OL</sub>                                                                                | I <sub>OH</sub> = 2mA<br>I <sub>OL</sub> = 4mA                                        | 2.0<br>4.5                                         |                                                                                              | 0.8                                                                                                  | V<br>V<br>V<br>V      |

| $\begin{array}{l} \textbf{CLKO AC CHARACTERISTICS} \\ \text{Rise Time } (t_{\text{R}}) \\ \text{Fall Time } (t_{\text{F}}) \\ \text{Duty Cycle} \end{array}$                                                           | 20% to 80% V <sub>DD</sub> , 10pF<br>80% to 20% V <sub>DD</sub> , 10pF<br>10pF Load   |                                                    | 4<br>3<br>37                                                                                 |                                                                                                      | ns<br>ns<br>%         |

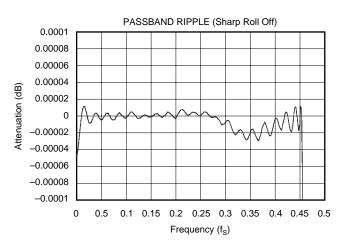

| DIGITAL FILTER PERFORMANCE<br>Filter Characteristics 1 (Sharp Roll-Off)<br>Passband<br>Stopband<br>Passband Ripple<br>Stopband Attenuation<br>Filter Characteristics 2 (Sharp Roll-Off)<br>Passband Ripple<br>Stopband | $\pm 0.00005$ dB<br>-3dB<br>Stopband = 0.546f <sub>S</sub><br>$\pm 0.0001$ dB<br>-3dB | 0.546f <sub>S</sub><br>-115<br>0.732f <sub>S</sub> |                                                                                              | 0.454f <sub>S</sub><br>0.493f <sub>S</sub><br>±0.00005<br>0.254f <sub>S</sub><br>0.460f <sub>S</sub> | dB<br>dB              |

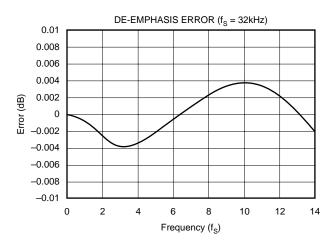

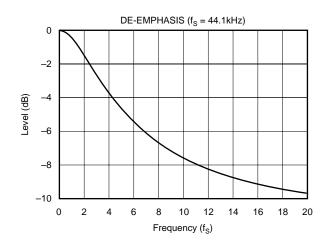

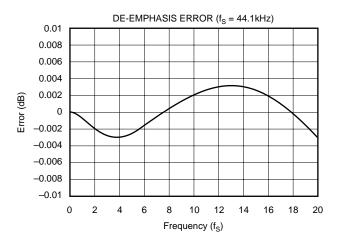

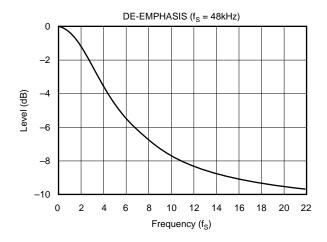

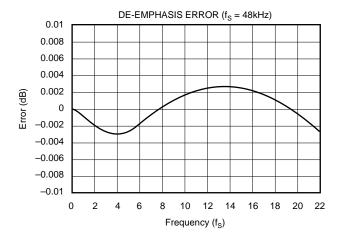

| Passband Ripple<br>Stopband Attenuation<br>Delay Time<br>De-Emphasis Error                                                                                                                                             | Stopband = 0.748f <sub>S</sub>                                                        | -100                                               | 45.125/f <sub>S</sub>                                                                        | ±0.0001<br>±0.003                                                                                    | dB<br>dB<br>sec<br>dB |

| POWER SUPPLY REQUIREMENTS<br>Voltage Range<br>Supply Current: I <sub>DD</sub><br>Power Dissipation                                                                                                                     | V <sub>DD</sub>                                                                       | 4.5                                                | 5<br>20<br>100                                                                               | 5.5<br>30<br>150                                                                                     | VDC<br>mA<br>mW       |

| TEMPERATURE RANGE<br>Operation<br>Storage                                                                                                                                                                              |                                                                                       | -25<br>-55                                         |                                                                                              | +85<br>+100                                                                                          | °C<br>°C              |

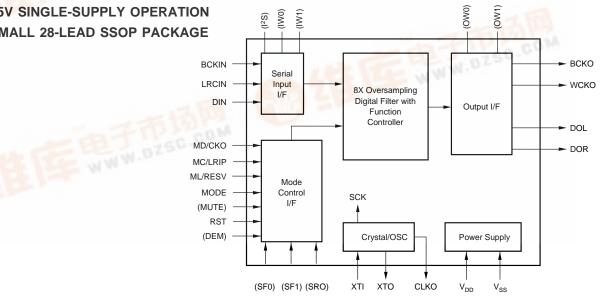

#### **PIN CONFIGURATION**

#### PACKAGE INFORMATION

| PRODUCT | PACKAGE      | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|---------|--------------|------------------------------------------|

| DF1704E | 28-Lead SSOP | 324                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

## **ABSOLUTE MAXIMUM RATINGS**

| $\label{eq:supply Voltage (V_{DD}, V_{CC}1, V_{CC}2R, V_{CC}2L) = +6.5V \\ \mbox{Supply Voltage Differences} = \pm 0.1 \\ \mbox{GND Voltage Differences} = \pm 0.1V \\ \mbox{Digital Input Voltage} = -0.3V to (V_{DD} + 0.3V) \\ \mbox{Input Current (any pins except power supplies)} = \pm 10mA \\ \mbox{Power Dissipation} = 300mW \\ \mbox{Operating Temperature Range} = -25^{\circ}C to +85^{\circ}C \\ \mbox{Storage Temperature (soldering, 5s)} = \pm 26^{\circ}C \\ \mbox{Voltage Temperature (soldering, 5s)} = \pm 26^{\circ}C \\ Voltage $ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lead Temperature (soldering, 5s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### PIN ASSIGNMENTS

| PIN | NAME             | I/O | DESCRIPTION                                                                      |

|-----|------------------|-----|----------------------------------------------------------------------------------|

| 1   | DIN              | IN  | Serial Audio Data Input <sup>(3)</sup>                                           |

| 2   | BCKIN            | IN  | Bit Clock Input for Serial Audio Data <sup>(3)</sup>                             |

| 3   | I <sup>2</sup> S | IN  | Input Audio Data Format Selection <sup>(2, 4)</sup>                              |

| 4   | IW0              | IN  | Input Audio Data Word Selection <sup>(2, 4)</sup>                                |

| 5   | IW1              | IN  | Input Audio Data Word Selection <sup>(2, 4)</sup>                                |

| 6   | XTI              | IN  | Oscillator Input/External Clock Input                                            |

| 7   | хто              | OUT | Oscillator Output                                                                |

| 8   | V <sub>SS</sub>  | _   | Digital Ground                                                                   |

| 9   | CLKO             | OUT | Buffered System Clock Output                                                     |

| 10  | MODE             | IN  | Mode Control Selection (H: Software, L: Hardware) <sup>(1)</sup>                 |

| 11  | MD/CKO           | IN  | Control Data Input/Clock Output Frequency<br>Select <sup>(1, 5)</sup>            |

| 12  | MC/LRIP          | IN  | Control Data Clock/Polarity of LRCK Select <sup>(1, 5)</sup>                     |

| 13  | ML/RESV          | IN  | Control Data Latch/Reserved <sup>(1, 5)</sup>                                    |

| 14  | RST              | IN  | Reset. When this pin is LOW, the digital filter is held in reset. <sup>(1)</sup> |

| 15  | MUTE             | IN  | Mute Control <sup>(1, 4)</sup>                                                   |

| 16  | DEM              | IN  | De-Emphasis Control <sup>(2, 4)</sup>                                            |

| 17  | SF0              | IN  | Sampling Rate Select for De-emphasis <sup>(2, 4)</sup>                           |

| 18  | SF1              | IN  | Sampling Rate Select for De-emphasis <sup>(2, 4)</sup>                           |

| 19  | OW0              | IN  | Output Audio Data Word and Format Select <sup>(2, 4)</sup>                       |

| 20  | OW1              | IN  | Output Audio Data Word and Format Select <sup>(2, 4)</sup>                       |

| 21  | NC               | _   | No Connection                                                                    |

| 22  | V <sub>DD</sub>  | _   | Digital Power, +5V                                                               |

| 23  | DOR              | OUT | Rch, Serial Audio Data Output                                                    |

| 24  | DOL              | OUT | Lch, Serial Audio Data Output                                                    |

| 25  | wcкo             | OUT | Word Clock for Serial Audio Data Output                                          |

| 26  | вско             | OUT | Bit Clock for Serial Audio Data Output                                           |

| 27  | SRO              | IN  | Filter Response Select <sup>(2, 4)</sup>                                         |

| 28  | LRCIN            | IN  | L/R Clock Input ( $f_{S}$ ) for Serial Audio $\text{Data}^{(3)}$                 |

NOTES: (1) Pins 10-15; Schmitt-Trigger input with pull-up resistor. (2) Pins 3-5, 16-20, 27; Schmitt-Trigger input with pull-down resister. (3) Pins 1, 2, 28; Schmitt-Trigger input. (4) Pins 3-5, 15-20, 27; these pins are invalid when MODE (pin 10) is HIGH. (5) Pins 11-13; these pins have different functions corresponding to MODE (pin 10), (HIGH/LOW).

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

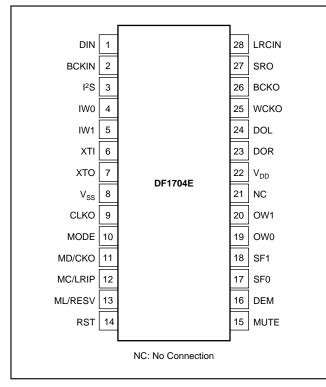

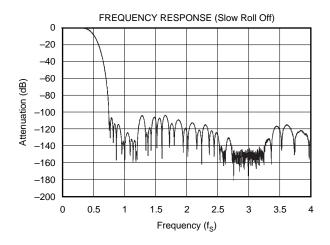

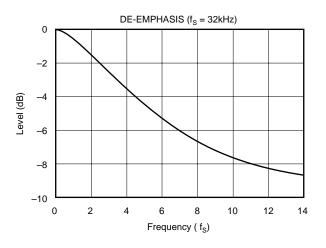

# **TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER**

# DIGITAL FILTER (DE-EMPHASIS OFF, f<sub>s</sub> = 44.1kHz)

# **TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER**

#### SYSTEM CLOCK REQUIREMENTS

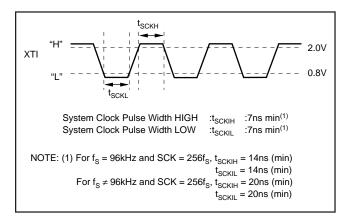

The system clock of the DF1704 can be supplied by either an external clock signal at XTI (pin 6), or by the on-chip crystal oscillator. The system clock rate must run at  $256f_s$ ,  $384f_s$ ,  $512f_s$ , or  $768f_s$ , where  $f_s$  is the audio sampling rate.

It should be noted that a  $768f_S$  system clock cannot be used when  $f_S = 96kHz$ . In addition, the on-chip crystal oscillator is limited to a maximum frequency of 24.576MHz. Table I shows the typical system clock frequencies for selected sample rates.

The DF1704 includes a system clock detection circuit that determines the system clock rate in use. The circuit compares the system clock input (XTI) frequency with the LRCIN input rate to determine the system clock multiplier. Ideally, LRCIN and BCKIN should be derived from the system clock to ensure proper synchronization. If the phase difference between the system clock and LRCIN is larger than  $\pm 6$  bit clock (BCKIN) periods, the synchronization of the system and LRCIN clocks will be performed automatically by the DF1704.

Timing requirements for the system clock input are shown in Figure 1.

FIGURE 1. System Clock Timing.

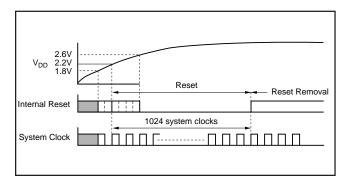

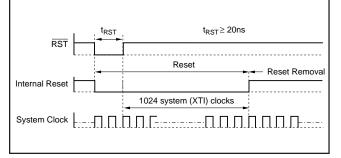

## RESET

The DF1704 has both an internal power-on reset circuit and a reset pin,  $\overline{\text{RST}}$  (pin 14), for providing an external reset signal. The internal power-on reset is performed automatically when power is applied to the DF1704, as shown in Figure 2. The  $\overline{\text{RST}}$  pin can be used to synchronize the DF1704 with a system reset signal, as shown in Figure 3. During the power-on reset period (1024 system clocks), the DF1704 outputs are forced LOW. For an external forced reset, the outputs are forced LOW during the initialization period (1024 system clocks), which occurs after the LOW-to-HIGH transition of the  $\overrightarrow{RST}$  pin as shown in Figure 3.

FIGURE 2. Internal Power-On Reset Timing.

FIGURE 3. External Forces Reset Timing.

## AUDIO INPUT INTERFACE

The audio input interface is comprised of BCKIN (pin 2), LRCIN (pin 28), and DIN (pin 1).

BCKIN is the input bit clock, which is used to clock data applied at DIN into the DF1704's input serial interface. Input data at DIN is clocked into the DF1704 on the rising edge of BCKIN. The left/right clock, LRCIN, is used as a word latch for the audio input data.

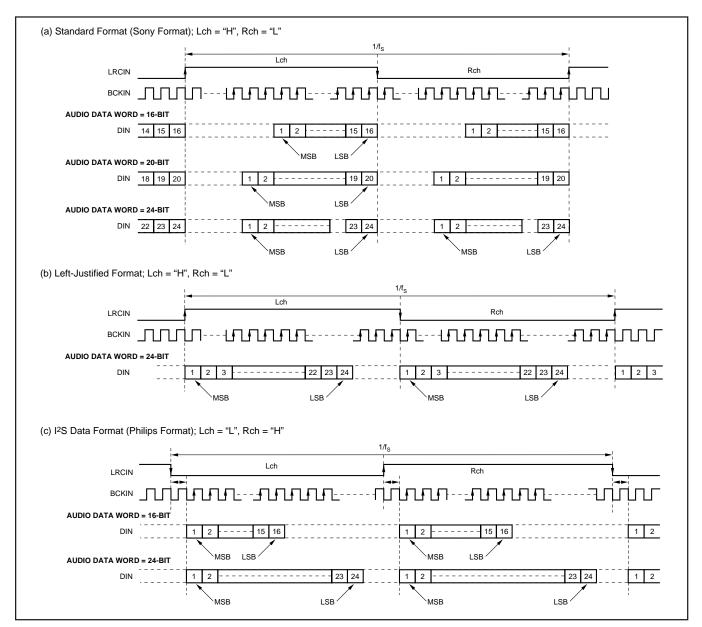

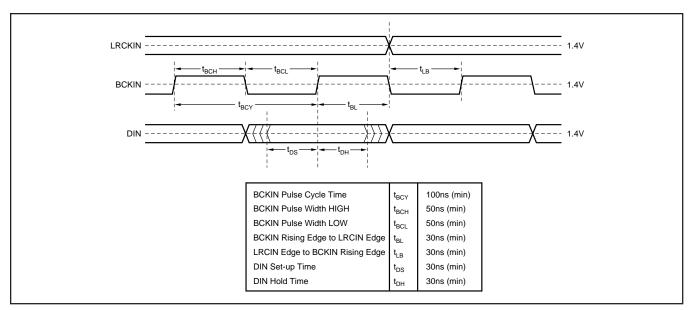

BCKIN can run at  $32f_S$ ,  $48f_S$ , or  $64f_S$ , where  $f_S$  is the audio sample frequency. LRCIN is run at the  $f_S$  rate. Figures 4 (a) through 4 (c) show the input data formats, which are selected by hardware or software controls. Figure 5 shows the audio input interface timing requirements.

|                              | SYSTEM CLOCK FREQUENCY (MHz) |                        |                        |                        |  |  |  |  |

|------------------------------|------------------------------|------------------------|------------------------|------------------------|--|--|--|--|

| SAMPLING RATE FREQUENCY (fs) | 256f <sub>S</sub>            | 384f <sub>S</sub>      | 512f <sub>S</sub>      | 768f <sub>S</sub>      |  |  |  |  |

| 32kHz                        | 8.1920                       | 12.2880                | 16.3840                | 24.5760                |  |  |  |  |

| 44.1kHz                      | 11.2896                      | 16.9340                | 22.5792                | 33.8688(1)             |  |  |  |  |

| 48kHz                        | 12.2880                      | 18.4320                | 24.5760                | 36.8640 <sup>(1)</sup> |  |  |  |  |

| 96kHz                        | 24.5760 <sup>(3)</sup>       | 36.8640 <sup>(1)</sup> | 49.1520 <sup>(1)</sup> | See Notes 1, 2         |  |  |  |  |

NOTES: (1) Maximum crystal oscillator frequency is 24.576MHz and cannot be used for these combinations. (2) 768f<sub>S</sub> system clock cannot be used with 96kHz sampling rate. (3) Use external system clock applied at XTI.

#### TABLE I. Typical System Clock Frequencies.

FIGURE 4. Audio Data Input Formats.

FIGURE 5. Audio Input Interface Timing.

## AUDIO OUTPUT INTERFACE

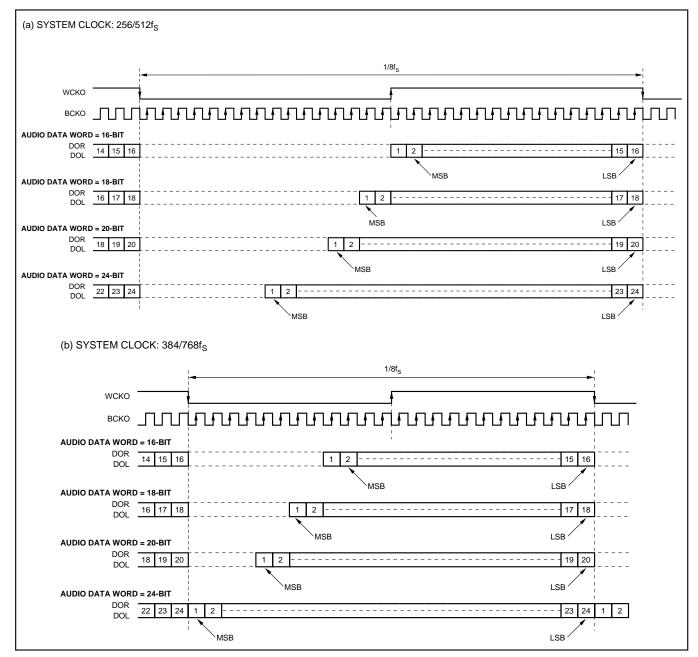

The audio output interface includes BCKO (pin 26), WCKO (pin 25), DOL (pin 24), and DOR (pin 23).

BCKO is the output bit clock and is used to clock data into an audio D/A converter, such as the PCM1704. DOL and DOR are the left and right audio data outputs. WCKO is the output word clock and is used to latch audio data words into an audio D/A converter.

WCKO runs at a fixed rate of  $8f_S$  (8X oversampling) for all system clock rates.

BCKO is fixed at  $256f_{\rm S}$  for system clock rates of  $256f_{\rm S}$  or  $512f_{\rm S}$ .

BCKO is fixed at  $192f_{S}$  for system clock rates of  $384f_{S}$  or  $768f_{S}$ .

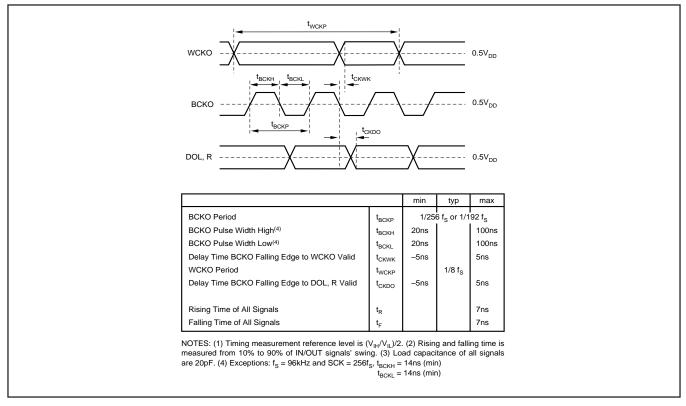

The output data format used by the DF1704 for DOL and DOR is Binary Two's Complement, MSB-first, right-justified audio data. Figures 6(a) and 6(b) show the output data formats for the DF1704. Figure 7 shows the audio output timing.

### **MODE CONTROL**

The DF1704 may be configured using either software or hardware control. The selection is made using the MODE input (pin 10).

| MODE SETTING | MODE CONTROL SELECTION |

|--------------|------------------------|

| MODE = H     | Software Mode          |

| MODE = L     | Hardware Mode          |

TABLE II. MODE Selection.

FIGURE 6. Audio Output Data Format.

FIGURE 7. Audio Output Data Format.

#### **Programmable Functions**

The DF1704 includes a number of programmable features, with most being accessible from either Hardware or Software mode. Table III summarizes the user programmable functions for both modes of operation.

| FUNCTION                                | Software<br>(Mode = H) | Hardware<br>(Mode = L) | RESET<br>DEFAULT<br>(Software Mode) |

|-----------------------------------------|------------------------|------------------------|-------------------------------------|

| Input Data Format Selection             | 0                      | 0                      | Standard Format                     |

| Input Word Length Selection             | 0                      | 0                      | 16 Bits                             |

| Output Word Length Selection            | 0                      | 0                      | 16 Bits                             |

| LRCIN Polarity Selection                | 0                      | 0                      | Left/Right = High/Low               |

| Digital De-Emphasis                     | 0                      | 0                      | OFF                                 |

| Soft Mute                               | 0                      | 0                      | OFF                                 |

| Digital Attenuation                     | 0                      | Х                      | 0dB, Independent L/R                |

| Sample Rate for<br>De-Emphasis Function | 0                      | 0                      | 44.1 kHz                            |

| Filter Roll-Off Selection               | 0                      | 0                      | Sharp Roll-Off Selected             |

| CLKO Output Frequency Selection         | 0                      | 0                      | Same As XTI Input                   |

Legend: 0 = User Programmable, X = Not Available.

TABLE III. User-Programmable Functions for Software and Hardware Mode.

#### **Hardware Mode Controls**

With MODE = L, the DF1704 may be configured by utilizing several user-programmable pins. The following is a brief summary of the pin functions. Table IV provides more details on setting the hardware mode controls.

Pins  $I^2S$ , IW0, and IW1 are used to select the audio data input format and word length.

Pins OW0 and OW1 are used to select the output data word length.

The DEM pin is used to enable and disable the digital deemphasis function. De-emphasis is only available for 32kHz, 44.1kHz, and 48kHz sample rates.

Pins SF0 and SF1 are used to select the sample rate for the de-emphasis function.

The SRO pin is used to select the digital filter response, either sharp or slow roll-off.

The MUTE pin is used to enable or disable the soft mute function.

The CKO pin is used to select the clock frequency seen at the CLKO pin, either XTI or XTI  $\div$  2.

The LRIP pin is used to select the polarity used for the audio input left/right clock, LRCIN.

Finally, the RESV pin is not used by the current DF1704 design, but is reserved for future use.

#### **Software Mode Controls**

With MODE = H, the DF1704 may be configured by programming four internal registers in software mode. ML (pin 13), MC (pin 12), and MD (pin 11) make up the 3-wire software control port, and may be controlled using DSP or microcontroller general purpose I/O pins, or a serial port. Table V provides an overview of the internal registers, labeled MODE0 through MODE3.

| PIN<br>NAME                    | pin<br>Number | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|--------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| RESV                           | 13            | Reserved, Not Used                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| LRIP                           | 12            | LRCIN Polarity<br>LRIP = H: LRCIN= H = Left Channel, LRCIN= L = Right Channel<br>LRIP = L: LRCIN= L = Left Channel, LRCIN = H = Right Channel                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| СКО                            | 11            | CLKO Output Frequency<br>CKO = H: CLKO Frequency = XTI/2<br>CKO = L: CLKO Frequency = XTI                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| MUTE                           | 15            | Soft Mute Control: H = Mute Off, L = Mute On                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| I <sup>2</sup> S<br>IW0<br>IW1 | 3<br>4<br>5   | Input Data Format Controls                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                |               | I <sup>2</sup> S   IW1   IW0   INPUT FORMAT     L   L   16-Bit, Standard, MSB-First, Right-Justified     L   L   H   20-Bit, Standard, MSB-First, Right-Justified     L   H   L   24-Bit, Standard, MSB-First, Right-Justified     L   H   H   24-Bit, Standard, MSB-First, Right-Justified     L   H   H   24-Bit, MSB-First, Left-Justified     H   L   L   16-Bit, I <sup>2</sup> S     H   L   H   24-Bit, I <sup>2</sup> S |  |  |  |  |  |  |

| SRO                            | 27            | Digital Filter Roll-Off: H = Slow, L = Sharp                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| OW0<br>OW1                     | 19<br>20      | Output Data Word Length Controls   OW1 OW0 OUTPUT FORMAT   L 16-Bit, MSB-First   L H 18-Bit, MSB-First   H L 20-Bit, MSB-First   H H 24-Bit, MSB-First                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| SF0<br>SF1                     | 17<br>18      | Sample Rate Selection for the Digital De-Emphasis Control   SF1 SF0 SAMPLING RATE   L L 44.1kHz   L H Reserved, Not Used   H L 48kHz   H H 32kHz                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| DEM                            | 16            | Digital De-Emphasis: H = On, L = Off                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

TABLE IV. Hardware Mode Controls.

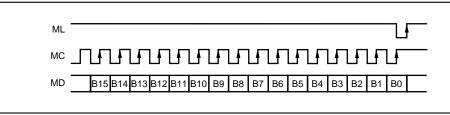

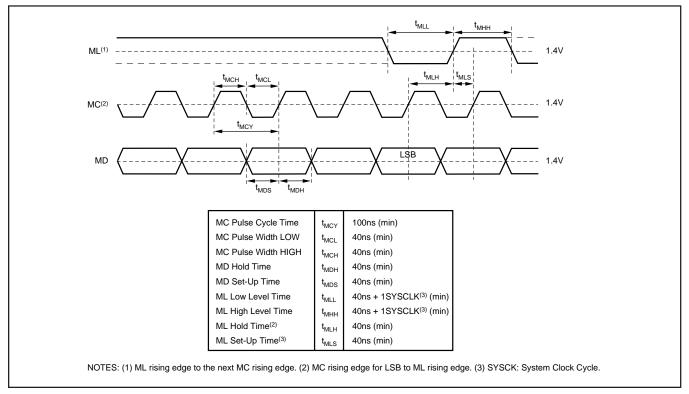

Figures 8 through 10 show more details regarding the control port data format and timing requirements. The data format for the control port is 16-bit, MSB-first, with Bit B15 being the MSB.

| REGISTER<br>NAME | bit<br>Name                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE0            | AL[7:0]<br>LDL<br>A[1:0]<br>res                                          | Attenuation Data for the Left Channel<br>Attenuation Load Control for the Left Channel<br>Register Address<br>Reserved                                                                                                                                                                                                |

| MODE1            | AR[7:0]<br>LDL<br>A[1:0]<br>res                                          | Attenuation Data for the Right Channel<br>Attenuation Load Control for the Right Channel<br>Register Address<br>Reserved                                                                                                                                                                                              |

| MODE2            | MUT<br>DEM<br>IW[1:0]<br>OW[1:0]<br>A[1:0]<br>res                        | Soft Mute Control<br>Digital De-Emphasis Control<br>Input Data Format and Word Length<br>Output Data Word Length<br>Register Address<br>Reserved                                                                                                                                                                      |

| MODE3            | I <sup>2</sup> S<br>LRP<br>ATC<br>SRO<br>CKO<br>SF[1:0]<br>A[1:0]<br>res | Input Data Format (I <sup>2</sup> S or Standard/Left-Justified)<br>LRCIN Polarity<br>Attenuator Control, Dependent or Independent<br>Digital Filter Roll-Off Selection (sharp or slow)<br>CLKO Frequency Selection (XTI or XTI + 2)<br>Sample Rate Selection for De-Emphasis Function<br>Register Address<br>Reserved |

NOTE: All reserved bits should be programmed to 0.

TABLE V. Internal Register Mapping.

### **Register Addressing**

A[1:0], bits B10 and B9 of the 16-bit control data word, are used to indicate the register address to be written to by the current control port write cycle. Table VI shows how to address the internal registers using bits A[1:0] of registers MODE0 through MODE3.

| A1 | A0 | REGISTER SELECTED |

|----|----|-------------------|

| 0  | 0  | MODE0             |

| 0  | 1  | MODE1             |

| 1  | 0  | MODE2             |

| 1  | 1  | MODE3             |

TABLE VI. Internal Register Addressing.

|       | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8  | B7  | B6  | B5  | B4  | B3   | B2    | B1    | B0               |

|-------|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|-----|-----|------|-------|-------|------------------|

| MODE0 | res | res | res | res | res | A1  | A0 | LDL | AL7 | AL6 | AL5 | AL4 | AL3  | AL2   | AL1   | AL0              |

|       |     |     |     |     |     |     |    |     |     | 100 |     |     | 1.50 | 4.5.0 | 1.5.4 | 4.5.0            |

| MODE1 | res | res | res | res | res | A1  | A0 | LDR | AR7 | AR6 | AR5 | AR4 | AR3  | AR2   | AR1   | AR0              |

|       |     |     |     |     |     |     | 1  |     |     |     | 1   |     |      |       |       |                  |

| MODE2 | res | res | res | res | res | A1  | A0 | res | res | OW1 | OW0 | IW1 | IW0  | res   | DEM   | MUT              |

|       |     |     |     |     |     |     |    |     |     |     |     |     |      |       |       |                  |

| MODE3 | res | res | res | res | res | A1  | A0 | res | SF1 | SF0 | СКО | res | SRO  | ATC   | LRP   | I <sup>2</sup> S |

|       |     |     |     |     |     |     |    |     |     |     |     |     |      |       |       |                  |

|       |     |     |     |     |     |     |    |     |     |     |     |     |      |       |       |                  |

FIGURE 8. Internal Mode Control Registers.

FIGURE 9. Software Interface Format.

FIGURE 10. Software Interface Timing Requirements.

### **MODE0** Register

The MODE0 register is used to set the attenuation data for the Left output channel, or DOL (pin 24).

When ATC = 1 (Bit B2 of Register MODE3 = 1), the Left channel attenuation data AL[7:0] is used for both the Left and Right channel attenuators.

When ATC = 0, (Bit B2 of Register MODE3 = 0), Left channel attenuation data is taken from AL[7:0] of register MODE0, and Right channel attenuation data is taken from AR[7:0] of register MODE1.

- AL[7:0] Left Channel Attenuator Data, where AL7 is the MSB and AL0 is the LSB. Attenuation Level is given by:

- $ATTEN = 0.5 \bullet (DATA 255) dB$

For DATA = FFh, ATTEN = -0dB For DATA = FEh, ATTEN = -0.5dB For DATA = 01h, ATTEN = -127.5dB For DATA = 00h, ATTEN = infinity = Mute

LDL Left Channel Attenuation Data Load Control. This bit is used to simultaneously set attenuation levels of both the Left and Right channels.

> When LDL = 1, the Left channel output level is set by the data in AL[7:0]. The Right channel output level is set by the data in AL[7:0], or the most recently programmed data in bits AR[7:0] of register MODE1.

> When LDL = 0, the Left channel output data remains at its previously programmed level.

# **MODE1** Register

The MODE1 register is used to set the attenuation data for the Right output channel, or DOR (pin 23).

When ATC = 1 (Bit B2 of Register MODE3 = 1), the Left channel attenuation data AL[7:0] of register MODE0 is used for both the Left and Right channel attenuators.

When ATC = 0, (Bit B2 of Register MODE3 = 0), Left channel attenuation data is taken from AL[7:0] of register MODE0, and Right channel attenuation data is taken from AR[7:0] of register MODE1.

AR[7:0] Right Channel Attenuator Data, where AR7 is the MSB and AR0 is the LSB. Attenuation Level is given by:

$ATTEN = 0.5 \bullet (DATA - 255) dB$

For DATA = FFh, ATTEN = -0dB For DATA = FEh, ATTEN = -0.5dB For DATA = 01h, ATTEN = -127.5dB For DATA = 00h, ATTEN = infinity = Mute

LDR Right Channel Attenuation Data Load Control. This bit is used to simultaneously set attenuation levels of both the Left and Right channels.

> When LDR = 1, the Right channel output level is set by the data in AR[7:0], or by the data in bits AL[7:0] of register MODE0. The Left channel output level is set to the most recently programmed data in bits AL[7:0] of register MODE0.

> When LDR = 0, the Right channel output data remains at its previously programmed level.

| MODE2 F              | Regist                                                                | ter                             |               | ATC                                       | Attenuator           |                                     |  |  |

|----------------------|-----------------------------------------------------------------------|---------------------------------|---------------|-------------------------------------------|----------------------|-------------------------------------|--|--|

| The MOD              | E2 reg                                                                | gister is u                     | used to p     | rogram various functions:                 |                      | This bit is                         |  |  |

| MUT                  | Soft                                                                  | Mute Fu                         | unction.      |                                           | and Right cl         |                                     |  |  |

|                      | Whe                                                                   | n MUT                           | = 0, Soft     |                                           | channel data         |                                     |  |  |

|                      | Whe                                                                   | Right ch<br>n MUT :<br>Right ch | = 1, Soft     | Mute is OFF for both Left                 |                      | When ATC attenuator d               |  |  |

| DEM                  |                                                                       | Function.                       |               | When ATC attenuators                      |                      |                                     |  |  |

|                      | Whe<br>Whe                                                            | SRO                             | Digital Filte |                                           |                      |                                     |  |  |

| IW[1:0]              | -                                                                     | t Data F                        | ormat an      |                                           | When SRO<br>When SRO |                                     |  |  |

| I <sup>2</sup> S IW1 |                                                                       |                                 | IW0           | Description                               | СКО                  | CLKO Out                            |  |  |

|                      | 0 0 0 16-Bit Data, Standard<br>Format (MSB-First,<br>Right-Justified) |                                 |               |                                           |                      | When CKC<br>same as the<br>When CKO |  |  |

|                      | 0                                                                     | 0                               | 1             | 20-Bit Data, Standard<br>Format           | 0001.01              | the XTI inp                         |  |  |

|                      | 0                                                                     | ,                               |               | 24-Bit Data, Standard<br>Format           | SF[1:0]              | Sampling F<br>phasis Func           |  |  |

|                      | 0                                                                     | 1                               | 1             | 24-Bit Data, MSB-First,<br>Left-Justified |                      | SF1 SF0<br>0 0<br>0 1               |  |  |

|                      | 1                                                                     | 0                               | 0             | 16-Bit Data, I <sup>2</sup> S Format      |                      | 1  0                                |  |  |

|                      | 1                                                                     | 0                               | 1             | 24-Bit Data, I <sup>2</sup> S format      |                      | 1 1                                 |  |  |

|                      | 1                                                                     | 1                               | 0             | Reserved                                  |                      |                                     |  |  |

|                      | 1                                                                     | 1                               | 1             | APPLICATIO                                |                      |                                     |  |  |

OW[1:0] Output Data Word Length.

| 0 0 16-Bit Data, MSB-First | OW1 | OW0 | Description            |

|----------------------------|-----|-----|------------------------|

|                            | 0   | 0   | 16-Bit Data, MSB-First |

| 0 1 18-Bit Data, MSB-First | 0   | 1   | 18-Bit Data, MSB-First |

| 1 0 20-Bit Data, MSB-First | 1   | 0   | 20-Bit Data, MSB-First |

| 1 1 24-Bit Data, MSB-First | 1   | 1   | 24-Bit Data, MSB-First |

# **MODE3** Register

The MODE3 register is used to program various functions.

I<sup>2</sup>S Input Data Format.

When  $I^2S = 0$ , standard or left-justified formats are enabled.

When  $I^2S = 1$ , the  $I^2S$  formats are enabled.

LRP LRCIN Polarity Selection.

When LRP = 0, Left channel is HIGH and Right channel is LOW.

When LRP = 1, Left channel is LOW and Right channel is HIGH.

| ATC                                  | Attenuator Control.<br>This bit is used to determine whether the Left<br>and Right channel attenuators operate with inde-<br>pendent data, or use common data (the Left<br>channel data in bits AL[7:0] of register MODE0). |                     |                          |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|

|                                      | When $ATC = 0$ , the Left and Right channel attenuator data is independent.                                                                                                                                                 |                     |                          |

|                                      | When $ATC = 1$ , the Left and Right channel attenuators use common data.                                                                                                                                                    |                     |                          |

| SRO Digital Filter Roll-Off Select   |                                                                                                                                                                                                                             |                     | Selection.               |

|                                      | When $SRO = 0$ , sharp roll-off is selected.<br>When $SRO = 1$ , slow roll-off is selected.                                                                                                                                 |                     |                          |

| CKO CLKO Output Frequency Selection. |                                                                                                                                                                                                                             |                     | ncy Selection.           |

|                                      | same<br>Whe                                                                                                                                                                                                                 | as the clock at the | LKO frequency is half of |

| SF[1:0]                              | SF[1:0] Sampling Frequency Selection for the I phasis Function.                                                                                                                                                             |                     | Selection for the De-Em- |

|                                      | SF1                                                                                                                                                                                                                         | SF0                 | Description              |

|                                      | 0                                                                                                                                                                                                                           | 0                   | 44.1 kHz                 |

|                                      | 0                                                                                                                                                                                                                           | 1                   | Reserved                 |

|                                      | 1                                                                                                                                                                                                                           | 0                   | 48 kHz                   |

|                                      | 1                                                                                                                                                                                                                           | 1                   | 32 kHz                   |

|                                      |                                                                                                                                                                                                                             |                     |                          |

# APPLICATIONS INFORMATION

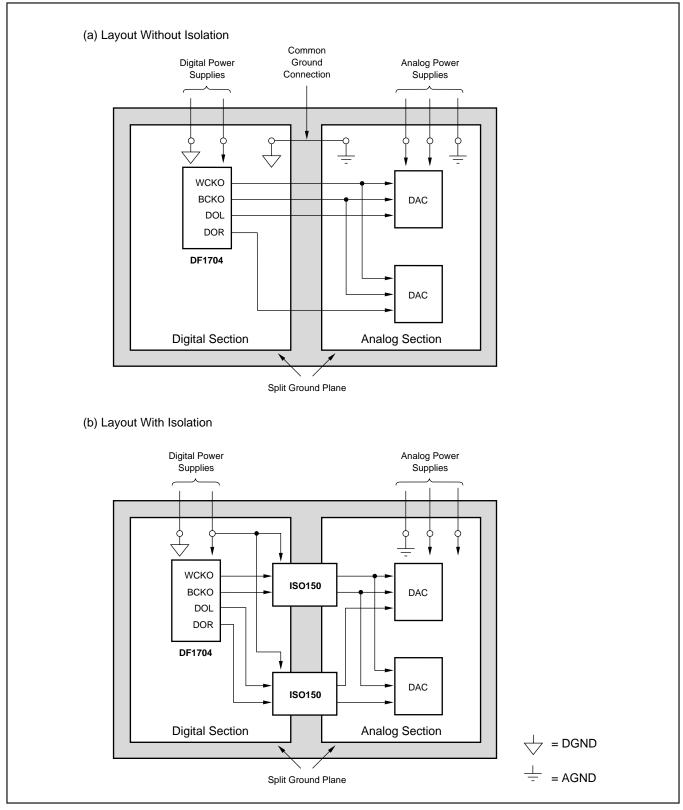

# PCB LAYOUT GUIDELINES

In order to obtain the specified performance from the DF1704 and its associated D/A converters, proper printed circuit board layout is essential. Figure 11 shows two approaches for obtaining the best audio performance.

Figure 11(a) shows a standard, mixed signal layout scheme. The board is divided into digital and analog sections, each with its own ground. The ground areas should be put on a split-plane, separate from the routing and power layers. The DF1704 and all digital circuitry should be placed over the digital section, while the audio DACs and analog circuitry should be located over the analog section of the board. A common connection between the digital and analog grounds is required and is done at a single point as shown.

For Figure 11(a), digital signals should be routed from the DF1704 to the audio DACs using short, direct connections to reduce the amount of radiated high-frequency energy. If necessary, series resistors may be placed in the clock and data signal paths to reduce or eliminate any overshoot or undershoot present on these signals. A value of  $50\Omega$  to  $100\Omega$  is recommended as a starting point, but the designer should experiment with the resistor values in order to obtain the best results.

Figure 11(b) shows an improved method for high performance, mixed signal board layout. This method adds digital isolation between the DF1704 and the audio DACs, and provides complete isolation between the digital and analog sections of the board. The Burr-Brown ISO150 dual digital coupler provides excellent isolation, and operates at speeds up to 80Mbps.

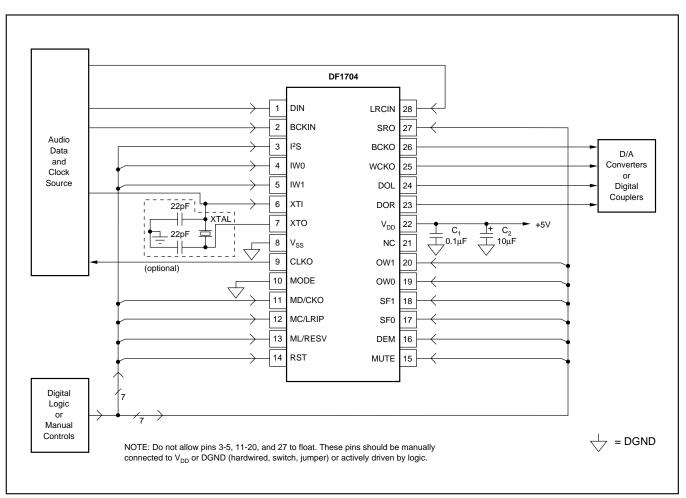

## POWER SUPPLIES AND BYPASSING

The DF1704 requires a single +5V power supply for operation. The power supply should be bypassed by a 10 $\mu$ F and 0.1 $\mu$ F parallel capacitor combination. The capacitors should be placed as close as possible to V<sub>DD</sub> (pin 22). Aluminum electrolytics or tantalum capacitors can be used for the 10 $\mu$ F value, while ceramics may be used for the 0.1 $\mu$ F value.

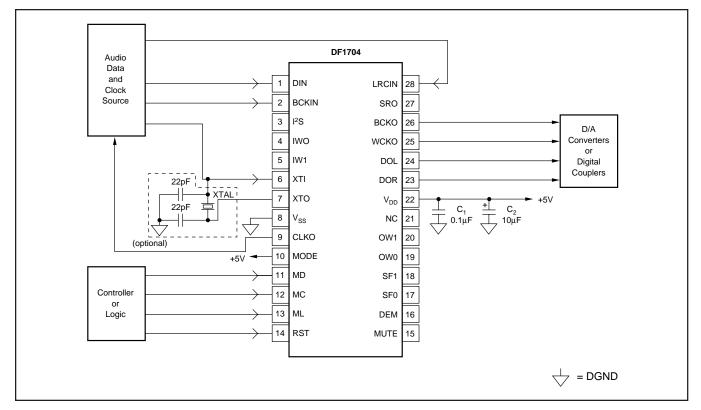

#### **BASIC CIRCUIT CONNECTIONS**

Figures 12 and 13 show basic circuit connections for the DF1704. Figure 12 shows connections for Hardware mode controls, while Figure 13 shows connections for Software mode controls. Notice the placement of  $C_1$  and  $C_2$  in both figures, as they are physically close to the DF1704.

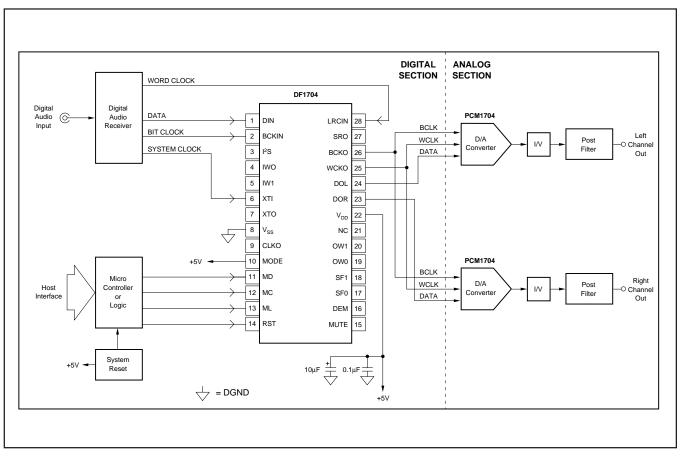

#### **TYPICAL APPLICATIONS**

The DF1704 will typically be used in high performance audio equipment, in conjunction with high performance audio D/A converters. Figure 14 shows a typical application circuit example, employing the DF1704, a digital audio receiver, and two PCM1704 24-bit, 96kHz audio DACs.

FIGURE 11. PCB Layout Model.

FIGURE 12. Basic Circuit Connections, Hardware Control.

FIGURE 13. Basic Circuit Connection, Software Control.

FIGURE 14. DF1704 Typical Application Circuit.