**OPA648**

# **ULTRA-WIDEBAND CURRENT** FEEDBACK OPERATIONAL AMPLIFIER

#### **FEATURES**

- WIDE BANDWIDTH: 1GHz

- LOW DIFFERENTIAL GAIN/PHASE ERRORS: 0.02%/0.02°

- GAIN FLATNESS: 0.1dB to 100MHz

- FAST SLEW RATE: 1200V/us

- CLEAN PULSE RESPONSE

- UNITY GAIN STABLE

#### **APPLICATIONS**

- HIGH-SPEED SIGNAL PROCESSING

- HIGH-RESOLUTION CRT PREAMP

- HIGH-RESOLUTION VIDEO

- PULSE AMPLIFICATION

- IF SIGNAL PROCESSING

- DAC I/V CONVERSION

- ADC BUFFER

#### DESCRIPTION

The OPA648 is an ultra high bandwidth current feedback operational amplifier. The current feedback architecture also allows for a very high slew rate, which gives excellent large signal bandwidth, even at high gains. The high slew rate and well-behaved pulse response allow for superior large signal amplification in a variety of RF, video and other signal processing applications. Fabricated on an advanced complementary bipolar process, the OPA648 offers exceptional performance in monolithic form.

Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 International Airport Industrial Park • Mailing Address: PO Box 11400 Cable: BBRCORP Tel: (520) 746-1111 • Twx: 910-952-1111 • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

#### **ELECTRICAL**

$\rm T_A$  = +25°C,  $\rm V_S$  = ±5V,  $\rm R_L$  = 100 $\Omega$ ,  $\rm C_L$  = 2pF, and  $\rm R_{FB}$  = 243 $\Omega$  unless otherwise noted.

|                                                                                                                                                                                 |                                                                                                                                                                                                                                 | OPA648H, P, U                     |                                                |                          |                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------|--------------------------|----------------------------------------------------|

| PARAMETER                                                                                                                                                                       | CONDITIONS                                                                                                                                                                                                                      | MIN                               | TYP                                            | MAX                      | UNITS                                              |

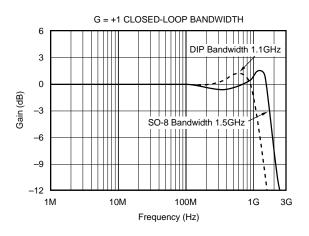

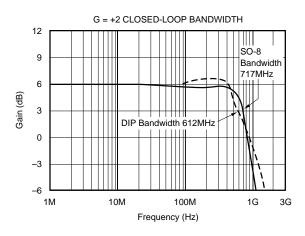

| FREQUENCY RESPONSE Small Signal Bandwidth <sup>(1)</sup> Slew Rate <sup>(2)</sup> Settling Time                                                                                 | G = +1<br>G = +2<br>G = +2, 1V Step                                                                                                                                                                                             |                                   | 1.0<br>600<br>1200                             |                          | GHz<br>MHz<br>V/μs                                 |

| 0.01% 0.1% 1% Spurious Free Dynamic Range Differential Gain, G = +2 Differential Phase, G = +2 Gain Flatness                                                                    | $\begin{array}{c} G=+2, \ 1V \ Step \\ G=+2, \ 1V \ Step \\ G=+2, \ 1V \ Step \\ G=+2, \ f=5.0MHz, \ V_O=2Vp-p \\ G=+2, \ f=20.0MHz, \ V_O=2Vp-p \\ 3.58MHz, \ V_O=1.4Vp-p, \ R_L=150\Omega \\ DC \ to \ 100MHz \\ \end{array}$ |                                   | 20<br>9<br>3<br>60<br>51<br>0.02<br>0.02       |                          | ns<br>ns<br>ns<br>dBc<br>dBc<br>%<br>degrees<br>dB |

| OFFSET VOLTAGE<br>Input Offset Voltage<br>Average Drift<br>Power Supply Rejection Ratio                                                                                         | V <sub>S</sub> = ±4.5 to ±5.5V                                                                                                                                                                                                  | 45                                | ±2<br>±10<br>58                                | ±6                       | mV<br>μV/°C<br>dB                                  |

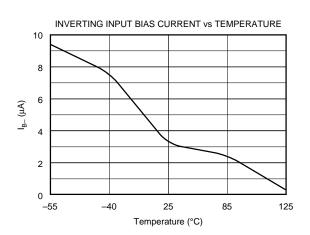

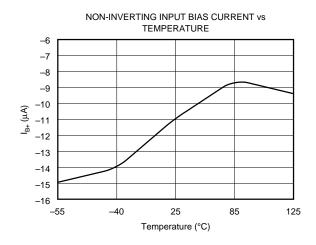

| INPUT BIAS CURRENT Non-Inverting Over Specified Temperature Inverting Over Specified Temperature                                                                                |                                                                                                                                                                                                                                 |                                   | ±12<br>±30<br>±20<br>±50                       | ±65<br>±95<br>±65<br>±95 | μΑ<br>μΑ<br>μΑ<br>μΑ                               |

| NOISE Input Voltage Noise Noise Density, f = 100Hz f = 1kHz f = 10kHz f = 1MHz Voltage Noise, BW = 10Hz to 200MH Input Bias Current Noise Current Noise Density, f = 0.1Hz to 2 |                                                                                                                                                                                                                                 |                                   | 10.4<br>2.3<br>2.3<br>2.3<br>2.3<br>32.5       |                          | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>μVrms      |

| INPUT VOLTAGE RANGE<br>Common-Mode Input Range<br>Common-Mode Rejection                                                                                                         | V <sub>CM</sub> = ±0.5V                                                                                                                                                                                                         | ±2<br>35                          | ±2.25<br>55                                    |                          | V<br>dB                                            |

| INPUT IMPEDANCE<br>Non-inverting<br>Inverting                                                                                                                                   |                                                                                                                                                                                                                                 |                                   | 22    0.75<br>20                               |                          | kΩ    pF<br>Ω                                      |

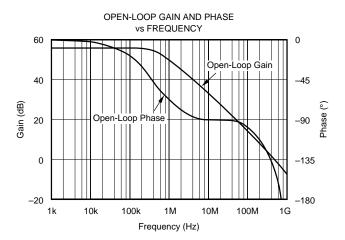

| OPEN-LOOP TRANSIMPEDANCE Open-Loop Transimpedance                                                                                                                               | $V_O = \pm 2V, R_L = 1k\Omega$                                                                                                                                                                                                  | 100                               | 165                                            |                          | kΩ                                                 |

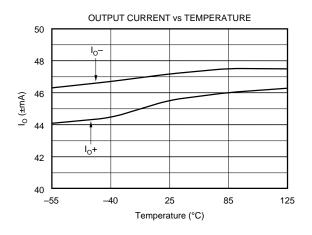

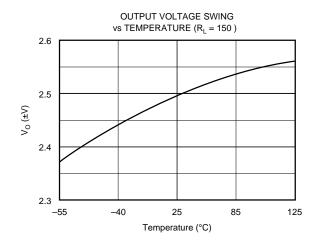

| OUTPUT Current Output Over Specified Temperature Voltage Output Over Specified Temperature Voltage Output Over Specified Temperature Short-Circuit Current Output Resistance    | No Load $R_{L}=150\Omega$ $1 MHz, G=+2 V/V$                                                                                                                                                                                     | 33<br>25<br>±2.75<br>±2.2<br>±2.0 | 45<br>40<br>±3.0<br>±2.5<br>±2.3<br>75<br>0.08 |                          | mA<br>mA<br>V<br>V<br>V<br>mA<br>Ω                 |

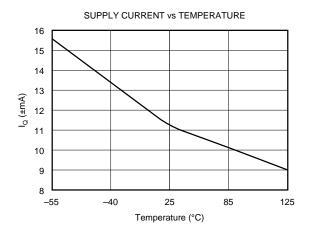

| POWER SUPPLY Specified Operating Voltage Operating Voltage Range Quiescent Current Over Specified Temperature                                                                   | T <sub>MIN</sub> to T <sub>MAX</sub><br>T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                                    | ±4.5                              | ±5<br>±13<br>±15                               | ±5.5<br>±20<br>±23       | V<br>V<br>mA<br>mA                                 |

| TEMPERATURE RANGE Specification Storage Thermal Resistance, $\theta_{\rm JA}$ P U                                                                                               | Ambient<br>Ambient                                                                                                                                                                                                              | -40<br>-55                        | 120<br>170                                     | +85<br>+150              | °C<br>°C/W<br>°C/W                                 |

NOTES: (1) Bandwidth can be degraded by a non-optimal PC board layout. Refer to the DEM-OPA64X datasheet for layout recommendations. (2) Slew rate is the rate of change from 10% to 90% of the output voltage step.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply                                                                                                           | ±5.5VDC                    |  |

|------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| Internal Power Dissipation <sup>(1)</sup>                                                                        | See Thermal Considerations |  |

| Differential Input Voltage                                                                                       | Total V <sub>S</sub>       |  |

| Input Voltage Range                                                                                              | ±5V                        |  |

| Storage Temperature Range: H                                                                                     | –65°C to +150°C            |  |

| P                                                                                                                | 40°C to +125°C             |  |

| Lead Temperature (soldering, 10s)                                                                                | +300°C                     |  |

| (soldering, SO-8 3s)                                                                                             | +260°C                     |  |

| Junction Temperature (T <sub>J</sub> )                                                                           | +175°C                     |  |

| NOTE: (1) Packages must be derated based on specified $\theta_{\rm JA}$ . Maximum T $_{\rm J}$ must be observed. |                            |  |

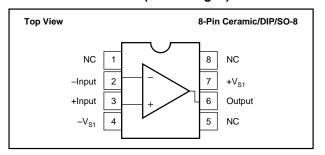

#### **PIN CONFIGURATION (All Packages)**

#### **PACKAGE INFORMATION**

| MODEL   | PACKAGE                       | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|---------|-------------------------------|------------------------------------------|

| OPA648H | 8-Pin Ceramic Sidebraze DIP   | 157                                      |

| OPA648P | 8-Pin Plastic Single-Wide DIP | 006                                      |

| OPA648U | 8-Pin Surface Mount           | 182                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

## ORDERING INFORMATION

| MODEL   | PACKAGE                       | TEMPERATURE<br>RANGE |  |

|---------|-------------------------------|----------------------|--|

| OPA648H | 8-Pin Ceramic Sidebraze DIP   | -40°C to +85°C       |  |

| OPA648P | 8-Pin Plastic Single-Wide DIP | -40°C to +85°C       |  |

| OPA648U | 8-Pin Surface Mount           | -40°C to +85°C       |  |

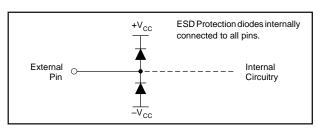

# ELECTROSTATIC DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

ODACAO BURR-BROWN®

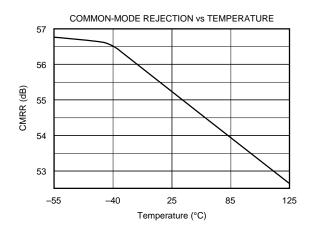

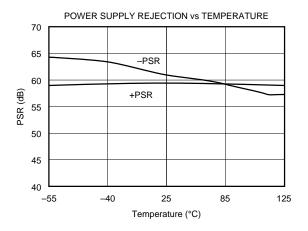

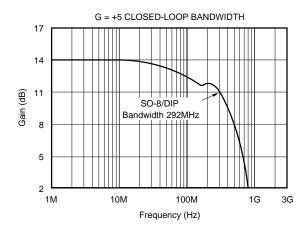

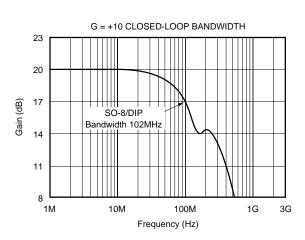

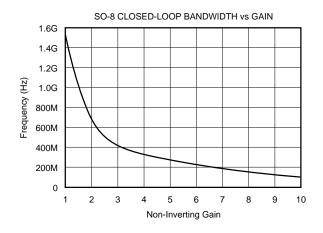

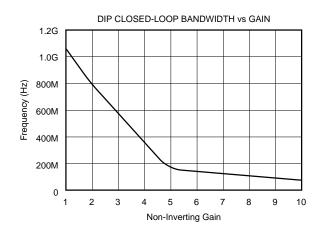

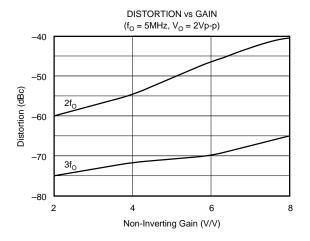

## **TYPICAL PERFORMANCE CURVES**

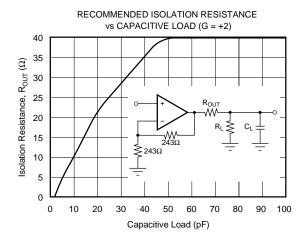

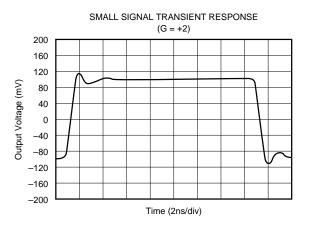

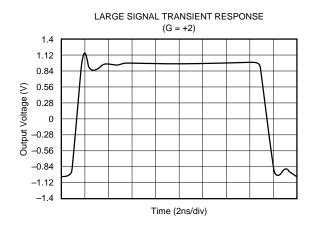

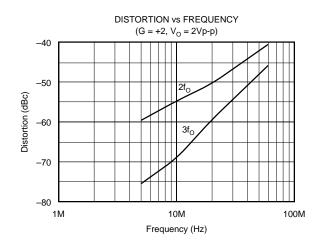

$T_{A}$  = +25°C,  $V_{S}$  =  $\pm5V,~R_{L}$  = 100 $\Omega,~C_{L}$  = 2pF, and  $R_{FB}$  = 243 $\Omega$  unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

$T_A$  = +25°C,  $V_S$  = ±5V,  $R_L$  = 100 $\Omega$ ,  $C_L$  = 2pF, and  $R_{FB}$  = 243 $\Omega$  unless otherwise noted.

BURR - BROWN

# **TYPICAL PERFORMANCE CURVES (CONT)**

$T_{A}$  = +25°C,  $V_{S}$  =  $\pm5V,~R_{L}$  = 100 $\Omega,~C_{L}$  = 2pF, and  $R_{FB}$  = 243 $\Omega$  unless otherwise noted.

## TYPICAL PERFORMANCE CURVES (CONT)

$T_A$  = +25°C,  $V_S$  = ±5V,  $R_L$  = 100 $\Omega$ ,  $C_L$  = 2pF, and  $R_{FB}$  = 243 $\Omega$  unless otherwise noted.

## **APPLICATIONS INFORMATION**

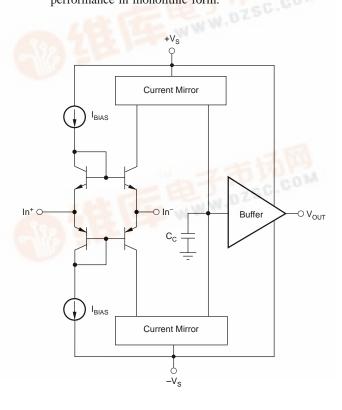

#### THEORY OF OPERATION

This current feedback architecture offers the following important advantages over voltage feedback architectures: (1) the high slew rate allows the large signal performance to approach the small signal performance, and: (2) there is less bandwidth degradation at higher gain settings.

#### DC GAIN TRANSFER CHARACTERISTICS

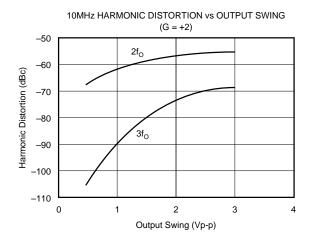

The circuit in Figure 1 shows the equivalent circuit for calculating the DC gain. When operating the device in the inverting mode, the input signal error current (I<sub>F</sub>) is amplified by the open-loop transimpedance gain  $(T_0)$ . The output signal generated is equal to  $T_{\rm O} \; X \; I_{\rm E}.$  Negative feedback is applied through RFB such that the device operates at a gain equal to  $-R_{FB}/R_{FF}$ .

FIGURE 1. Equivalent Circuit.

For non-inverting operation, the input signal is applied to the non-inverting (high impedance buffer) input. The output (buffer) error current (I<sub>E</sub>) is generated at the low impedance inverting input. The signal generated at the output is fed back to the inverting input such that the overall gain is (1 +  $R_{FB}/R_{FF}$ ).

Where a voltage-feedback amplifier has two symmetrical high impedance inputs, a current feedback amplifier has a low inverting (buffer output) impedance and a high noninverting (buffer input) impedance.

The closed-loop gain for the OPA648 can be calculated using the following equations:

Inverting Gain =

$$\frac{-\left(\frac{R_{FB}}{R_{FF}}\right)}{1 + \frac{1}{Loop Gain}}$$

(1)

Non-Inverting Gain =

$$\frac{\left[1 + \frac{R_{FB}}{R_{FF}}\right]}{1 + \frac{1}{\text{Loop Gain}}}$$

(2)

where Loop Gain =

$$\left[ \frac{T_O}{R_{FB} + R_S \left( 1 + \frac{R_{FB}}{R_{FF}} \right)} \right]$$

At higher gains the small value inverting input impedance causes an apparent loss in bandwidth. This can be seen from the equation:

$$f_{\text{ACTUAL}} \text{BW} = \frac{f_{\text{IDEAL}} \text{BW}}{\left[1 + \left(\frac{R_{\text{S}}}{R_{\text{FB}}}\right) \times \left(1 + \frac{R_{\text{FB}}}{R_{\text{FF}}}\right)\right]}$$

(3)

This loss in bandwidth at high gains can be corrected without affecting stability by lowering the value of the feedback resistor from the specified value of  $243\Omega$ .

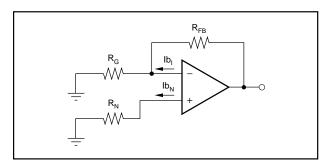

#### **OFFSET VOLTAGE AND NOISE**

The output offset is the algebraic sum of the input voltage and current sources that influence DC operation. The output offset is calculated by the following equation:

Output Offset Voltage =

$$\pm Ib_N \times R_N (1 + R_{FB}/R_G) \pm V_{IO}$$

(4)

$(1 + R_{FB}/R_G) \pm Ib_I \times R_{FB}$

If all terms are divided by the gain  $(1 + R_F/R_G)$ , it can be observed that input referred offsets improve as gain increases.

The effective noise at the output of the amplifier can be determined by taking the root sum of the squares of equation 4 and applying the spectral noise values found in the Typical Performance Curve–graph section. This applies to noise from the op amp only. Note that both the noise figure and equivalent input offset voltages improve as the closed-loop gain increases (by keeping  $R_{\rm F}$  fixed and reducing  $R_{\rm I}$  with  $R_{\rm N}=0\Omega).$

FIGURE 2. Output Offset Voltage Equivalent Circuit.

#### WIRING PRECAUTIONS

Maximizing the OPA648's capability requires some wiring precautions and high-frequency layout techniques. Oscillation, ringing, poor bandwidth and settling, gain peaking, and instability are typical problems plaguing all high-speed amplifiers when they are improperly used. In general, all printed circuit board conductors should be wide to provide low resistance, low impedance signal paths. They should also be as short as possible. The entire physical circuit should be as small as practical. Stray capacitances should be minimized, especially at high impedance nodes, such as the amplifier's input terminals. Stray signal coupling from the output or power supplies to the inputs should be minimized. All circuit element leads should be no longer than 1/4 inch (6mm) to minimize lead inductance, and low values of resistance should be used. This will minimize time constants formed with the circuit capacitances and will eliminate stray, parasitic circuits.

Grounding is the most important application consideration for the OPA648, as it is with all high-frequency circuits. Oscillations at high frequencies can easily occur if good grounding techniques are not used. A heavy ground plane (1oz. copper recommended) should connect all unused areas on the component side. Good ground planes can reduce stray signal pickup, provide a low resistance, low inductance common return path for signal and power, and can conduct heat from active circuit package pins into ambient air by convection.

Supply bypassing is extremely critical and must *always* be used, especially when driving high current loads. Both power supply leads should be bypassed to ground as close as possible to the amplifier pins. Tantalum capacitors (2.2µF) with very short leads are recommended. A parallel 0.1µF ceramic must also be added. Surface-mount bypass capacitors will produce excellent results due to their low lead inductance. Additionally, suppression filters can be used to isolate noisy supply lines. Properly bypassed and modulation-free power supply lines allow full amplifier output and optimum settling time performance.

#### Points to Remember

- 1) Making use of all four power supply pins will lower the effective power supply inductance seen by the input and output stages. This will improve the AC performance including lower distortion. The lowest distortion is achieved when running separated traces to  $V_{S1}$  and  $V_{S2}$ . Power supply bypassing with 0.01µF and 2.2µF surface mount capacitors is recommended. It is essential to keep the 0.1µF capacitor very close to the power supply pins. Refer to the demonstration board figure in the DEM-OPA64X datasheet for the recommended layout and component placements. (2) Whenever possible, use surface mount. Don't use pointto-point wiring as the increase in wiring inductance will be detrimental to AC performance. However, if it must be used, very short, direct signal paths are required. The input signal ground return, the load ground return, and the power supply common should all be connected to the same physical point to eliminate ground loops, which can cause unwanted feedback.

- 3) Surface mount on the backside of the PC Board. Good component selection is essential. Capacitors used in critical locations should be a low inductance type with a high quality dielectric material. Likewise, diodes used in critical locations should be Schottky barrier types, such as HP5082-2835 for fast recovery and minimum charge storage. Ordinary diodes will not be suitable in RF circuits.

- 4) Whenever possible, solder the OPA648 directly into the PC board without using a socket. Sockets add parasitic capacitance and inductance, which can seriously degrade AC performance or produce oscillations.

- 5) Use a small feedback resistor (usually  $243\Omega$ ) in unitygain voltage follower applications for the best performance. For gain configurations, resistors used in feedback networks should have values of a few hundred ohms for best performance. Shunt capacitance problems limit the acceptable resistance range to about  $1k\Omega$  on the high end and to a value that is within the amplifier's output drive limits on the low end. Metal film and carbon resistors will be satisfactory, but wirewound resistors (even "non-inductive" types) are abso-

lutely *unacceptable* in high-frequency circuits. Feedback resistors should be placed directly between the output and the inverting input on the backside of the PC board. This placement allows for the shortest feedback path and the highest bandwidth. A longer feedback path than this will decrease the realized bandwidth substantially. Refer to the demonstration board layout at the end of the datasheet.

- 6) Surface-mount components (chip resistors, capacitors, etc.) have low lead inductance and are therefore strongly recommended. Circuits using all surface-mount components with the OPA648U (SO-8 package) will offer the best AC performance. The parasitic package impedance for the SO-8 is lower than the both the 8-pin Ceramic and 8-pin Plastic DIP.

- 7) Avoid overloading the output. Remember that output current must be provided by the amplifier to drive its own feedback network as well as to drive its load. Lowest distortion is achieved with high impedance loads.

- 8) Don't forget that these amplifiers use  $\pm 5V$  supplies. Although they will operate perfectly well with +5V and -5.2V, use of  $\pm 15V$  supplies will destroy the part.

- 9) Standard commercial test equipment has not been designed to test devices in the OPA648's speed range. Benchtop op amp testers and ATE systems will require a special test head to successfully test these amplifiers.

- 10) Terminate transmission line loads. Unterminated lines, such as coaxial cable, can appear to the amplifier to be a capacitive or inductive load. By terminating a transmission line with its characteristic impedance, the amplifier's load then appears purely resistive.

- 11) Plug-in prototype boards and wire-wrap boards will not be satisfactory. A clean layout using RF techniques is essential; there are no shortcuts.

#### **INPUT PROTECTION**

Static damage has been well recognized for MOSFET devices, but any semiconductor device deserves protection from this potentially damaging source. The OPA648 incorporates on-chip ESD protection diodes as shown in Figure 3. This eliminates the need for the user to add external protection diodes, which can add capacitance and degrade AC performance.

FIGURE 3. Internal ESD Protection.

All pins on the OPA648 are internally protected from ESD by means of a pair of back-to-back reverse-biased diodes to either power supply as shown. These diodes will begin to conduct when the input voltage exceeds either power supply

by about 0.7V. This situation can occur with loss of the amplifier's power supplies while a signal source is still present. The diodes can typically withstand a continuous current of 30mA without destruction. To insure long term reliability, however, diode current should be externally limited to 10mA or so whenever possible.

The OPA648 utilizes a fine geometry high speed process that withstands 500V using the Human Body Model and 100V using the machine model. However, static damage can cause subtle changes in amplifier input characteristics without necessarily destroying the device. In precision operational amplifiers, this may cause a noticeable degradation of offset voltage and drift. Therefore, static protection is strongly recommended when handling the OPA648.

#### **OUTPUT DRIVE CAPABILITY**

The OPA648 has been optimized to drive  $75\Omega$  and  $100\Omega$  resistive loads. This high-output drive capability makes the OPA648 an ideal choice for a wide range of RF, IF, and video applications. In many cases, additional buffer amplifiers are unneeded.

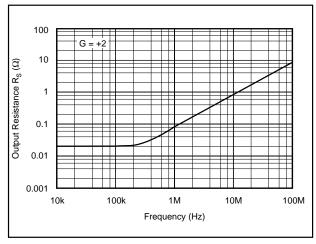

Many demanding high-speed applications such as ADC/DAC buffers require op amps with low wideband output impedance. For example, low output impedance is essential when driving the signal-dependent capacitances at the inputs of flash A/D converters. As shown in Figure 4, the OPA648 maintains very low closed-loop output impedance over frequency. Closed-loop output impedance increases with frequency since loop gain is decreasing with frequency.

FIGURE 4. Output Resistance vs Frequency.

#### THERMAL CONSIDERATIONS

The OPA648 does not require a heat sink for operation in most environments. At extreme temperatures and under full load conditions a heat sink may be necessary.

The internal power dissipation is given by the equation  $P_D = P_{DQ} + P_{DL}$ , where  $P_{DQ}$  is the quiescent power dissipation and  $P_{DL}$  is the power dissipation in the output stage due to the load. (For  $\pm V_S = \pm 5V$ ,  $P_{DQ} = 10V \times 23mA = 230mW$ ,

max). For the case where the amplifier is driving a grounded load  $(R_L)$  with a DC voltage  $(\pm V_{OUT})$ , the maximum value of  $P_{DL}$  occurs at  $\pm V_{OUT}=\pm V_S/2$ , and is equal to  $P_{DL}$ , max =  $(\pm V_S)^2/4R_L$ . Note that it is the voltage across the output transistor, and not the load, that determines the power dissipated in the output stage.

The short-circuit condition represents the maximum amount of internal power dissipation that can be generated. The variation of output current with temperature is shown in the Typical Performance Curves.

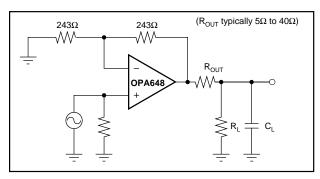

#### **CAPACITIVE LOADS**

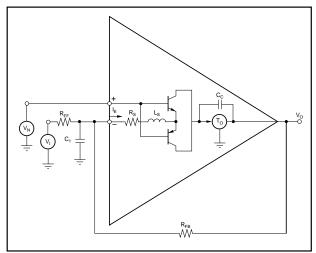

The OPA648's output stage has been optimized to drive low resistive loads. Capacitive loads, however, will decrease the amplifier's phase margin which may cause high frequency peaking or oscillations. Capacitive loads greater than 5pF should be buffered by connecting a small resistance, usually  $5\Omega$  to  $40\Omega$ , in series with the output as shown in Figure 5. This is particularly important when driving high capacitance loads such as flash A/D converters.

FIGURE 5. Driving Capacitive Loads.

In general, capacitive loads should be minimized for optimum high frequency performance. Coax lines can be driven if the cable is properly terminated. The capacitance of coax cable (29pF/foot for RG-58) will not load the amplifier when the coaxial cable or transmission line is terminated in its characteristic impedance.

#### **COMPENSATION**

The OPA648 is internally compensated and is stable in unity gain with a phase margin of approximately  $68^{\circ}$ . (Note that, from a stability standpoint, an inverting gain of -1V/V is equivalent to a noise gain of 2.) Gain and phase response for other gains are shown in the Typical Performance Curves.

The high-frequency response of the OPA648 in a good layout is very flat with frequency.

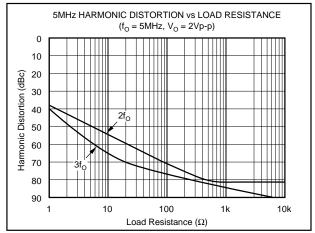

#### DISTORTION

The OPA648's harmonic distortion characteristics into a  $100\Omega$  load are shown vs frequency and power output in the Typical Performance Curves. Distortion can be further improved by increasing the load resistance as illustrated in

Figure 6. Remember to include the contribution of the feedback resistance when calculating the effective load resistance seen by the amplifier.

FIGURE 6. 5MHz Harmonic Distortion vs Load Resistance.

#### **DIFFERENTIAL GAIN AND PHASE**

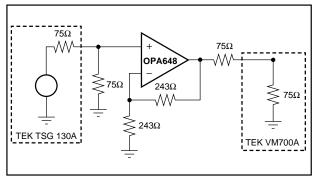

Differential Gain (DG) and Differential Phase (DP) are among the more important specifications for video applications. DG is defined as the percent change in closed-loop gain over a specified change in output voltage level. DP is defined as the change in degrees of the closed-loop phase over the same output voltage change. Both DG and DP are specified at the NTSC sub-carrier frequency of 3.58MHz and the PAL subcarrier of 4.43MHz. All NTSC measurements were performed using a Tektronix model VM700A Video Measurement Set.

DG and DP of the OPA648 were measured with the amplifier in a gain of +2V/V with  $75\Omega$  input impedance and the output back-terminated in  $75\Omega$ . The input signal selected from the generator was a 0V to 1.4V modulated ramp with sync pulse. With these conditions the test circuit shown in Figure 7 delivered a 100IRE modulated ramp to the  $75\Omega$  input of the video analyzer. The signal averaging feature of the analyzer was used to establish a reference against which the performance of the amplifier was measured. Signal averaging was also used to measure the DG and DP of the test signal in order to

FIGURE 7. Configuration for Testing Differential Gain/Phase.

----

eliminate the generator's contribution to measured amplifier performance. Typical performance of the OPA648 is 0.02% differential gain and 0.02% differential phase to both NTSC and PAL standards.

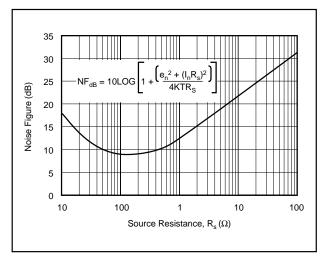

#### **NOISE FIGURE**

For RF applications, Noise Figure (NF) is often the preferred noise specification instead of Noise Spectral Density since it allows system noise performance to be more easily calculated. The OPA648's Noise Figure vs Source Resistance is shown in Figure 8.

FIGURE 8. Noise Figure vs Source Resistance.

#### **SPICE MODELS**

Computer simulation using SPICE is often useful when analyzing the performance of analog circuits and systems. This is particularly true for video and RF amplifier circuits where parasitic capacitance and inductance can have a major effect on circuit performance. SPICE Macromodels using PSpice are available for the OPA648. Contract Burr-Brown applications departments to receive a SPICE Diskette.

#### **DEMONSTRATION BOARDS**

Demonstration boards to speed prototyping are available. Refer to the DEM-OPA64X (LI-445) data sheet for details.

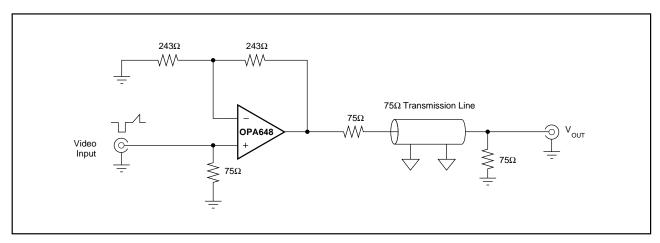

### **APPLICATIONS**

FIGURE 9. Low Distortion Video Amplifier.

BURR-BROWN

OD4640