查询OPA678供应商

### **FEATURES**

- FAST SETTLING: 11ns (1%)

- WIDE BANDWIDTH: 200MHz

- TWO LOGIC SELECTABLE INPUTS

- LOW OFFSET VOLTAGE: ±380μV

- FAST INPUT SWITCHING: 4ns

- ACCEPTS TTL/ECL SWITCHING SIGNALS

- UNITY GAIN STABLE

- 16-PIN DIP AND SO-16 PACKAGES

## APPLICATIONS

- VIDEO AMPLIFICATION AND SWITCHING

- FAST 2-INPUT MULTIPLEXER

- PULSE/RF AMPLIFIERS

- PROGRAMMABLE-GAIN AMPLIFIER

捷多邦,专业PCB打样工厂,24小时加急出货

**OPA678**

- ACTIVE FILTERS

- SYNCHRONOUS DEMODULATOR

- LOW COST REPLACEMENT FOR OPA675/676

## DESCRIPTION

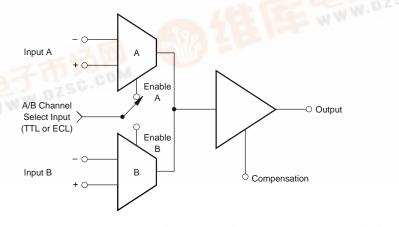

The OPA678 is a wideband monolithic operational amplifier with two independent differential inputs. Either input can be selected by an external TTL or ECL logic signal. The amplifier is externally compensated and features a very fast input selection speed, 4ns for either ECL or TTL. This amplifier features fully symmetrical differential inputs due to its "classical" operational amplifier circuit architecture. Unlike "current-feedback" amplifier designs, the OPA678 may be used in all op amp applications requiring high speed and precision.

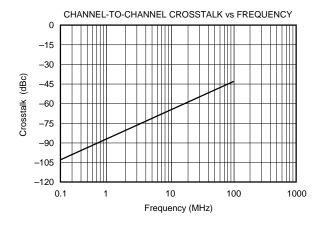

Low distortion and crosstalk make this amplifier suitable for RF and video applications.

The OPA678 is available in plastic DIP and SO-16 packages.

nternational Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

#### ELECTRICAL

At V<sub>CC</sub> = ±5VDC, R<sub>L</sub> = 150 $\Omega$ , C<sub>COMP</sub> = 5pF, and T<sub>A</sub> = +25°C, unless otherwise noted.

|                                                                                                                                                                                               |                                                                                                                                                                                                                                                     | OPA678AP, AU                |                                                            |                                                              |                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                     | CONDITIONS                                                                                                                                                                                                                                          | MIN                         | TYP                                                        | MAX                                                          | UNITS                                                                                                              |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                          | R <sub>S</sub> = 0Ω                                                                                                                                                                                                                                 |                             | 55<br>21<br>7.8<br>4.9<br>18<br>2.1                        |                                                              | $\begin{array}{c} nV/\sqrt{Hz}\\ nV/\sqrt{Hz}\\ nV/\sqrt{Hz}\\ nV/\sqrt{Hz}\\ \mu Vrms\\ pA/\sqrt{Hz} \end{array}$ |

| OFFSET VOLTAGE <sup>(1)</sup><br>Input Offset Voltage<br>Offset Voltage Drift<br>Supply Rejection                                                                                             | $\label{eq:VCM} \begin{array}{l} V_{CM} = 0 VDC \\ T_A = T_{MIN} \mbox{ to } T_{MAX} \\ \pm V_{CC} = 4.5 V \mbox{ to } 5.5 V \end{array}$                                                                                                           | 65                          | ±380<br>±3<br>71                                           | ±1.5mV<br>±15                                                | μV<br>μV/°C<br>dB                                                                                                  |

| BIAS CURRENT <sup>(1)</sup><br>Input Bias Current                                                                                                                                             | V <sub>CM</sub> = 0VDC                                                                                                                                                                                                                              |                             | 14                                                         | 50                                                           | μΑ                                                                                                                 |

| OFFSET CURRENT <sup>(1)</sup><br>Input Offset Current                                                                                                                                         | V <sub>CM</sub> = 0VDC                                                                                                                                                                                                                              |                             | 0.2                                                        | 2                                                            | μΑ                                                                                                                 |

| INPUT IMPEDANCE <sup>(1)</sup><br>Differential<br>Common-Mode                                                                                                                                 |                                                                                                                                                                                                                                                     |                             | 25k    2<br>10 <sup>6</sup>    5                           |                                                              | Ω    pF<br>Ω    pF                                                                                                 |

| INPUT VOLTAGE RANGE <sup>(1)</sup><br>Common-Mode Input Range<br>Common-Mode Rejection                                                                                                        | $V_{IN} = \pm 0.5 VDC, V_O = \pm 1.25 V$                                                                                                                                                                                                            | 2.0<br>75                   | ±2.5<br>85                                                 |                                                              | V<br>dB                                                                                                            |

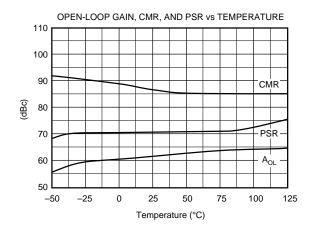

| OPEN-LOOP GAIN, DC <sup>(1)</sup><br>Open-Loop Voltage Gain                                                                                                                                   |                                                                                                                                                                                                                                                     | 50                          | 60                                                         |                                                              | dB                                                                                                                 |

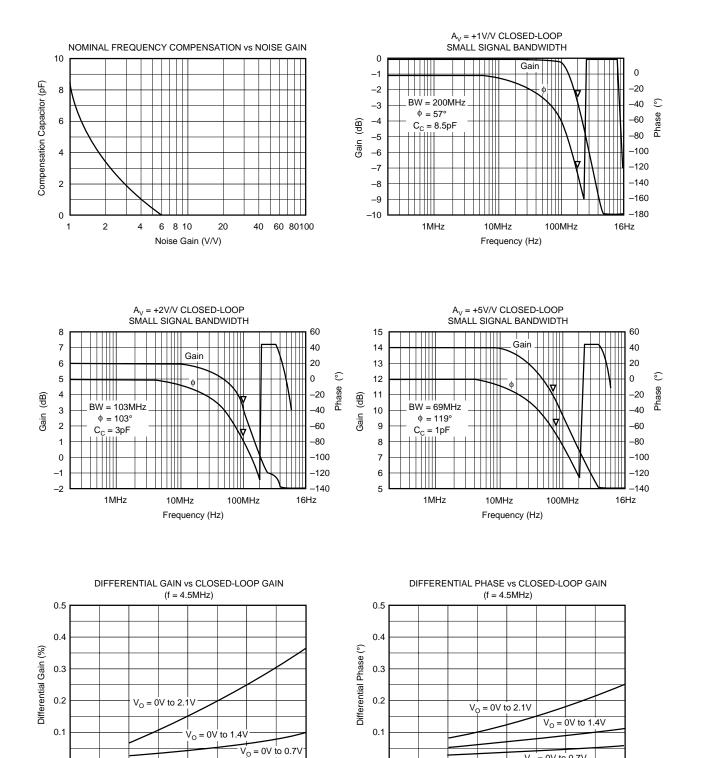

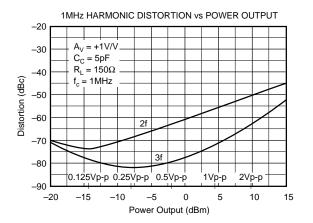

| FREQUENCY RESPONSE<br>Closed-Loop Bandwidth<br>Crosstalk<br>Harmonic Distortion: 5MHz                                                                                                         | $ \begin{array}{l} Gain = +1V/V, \ C_C = 9pF \\ Gain = +2V/V, \ C_C = 7pF \\ Gain = +5V/V, \ C_C = 1pF \\ Gain = +1V/V, \ f = 100kHz \\ f = 10MHz \\ f = 10MHz \\ f = 100MHz \\ G = +1V/V, \ R_l = 150\Omega, \ V_Q = 0.25Vp\text{-}p \end{array} $ | 140                         | 200<br>100<br>70<br>-102<br>-83<br>-64<br>-44              |                                                              | MHz<br>MHz<br>dBC <sup>(2)</sup><br>dBC<br>dBC<br>dBC                                                              |

| Large Signal Response <sup>(4)</sup><br>Slew Rate<br>Settling Time: 1%<br>0.1%<br>0.01%<br>Differential Gain (0V to 0.7V)<br>Differential Phase (0V to 0.7V)                                  | Second Harmonic<br>Third Harmonic<br>$V_0 = 2.5Vp$ -p, Gain = +1V/V<br>Gain = +1V/V<br>Gain = -1V/V, 1V <sub>OUT</sub> Step<br>4.5MHz, Gain = +2V/V, C <sub>C</sub> = 2.2pF<br>4.5MHz, Gain = +2V/V, C <sub>C</sub> = 2.2pF                         | 32<br>250                   | -71<br>-82<br>45<br>350<br>11<br>22<br>30<br>0.02<br>0.02  |                                                              | dBC <sup>(3)</sup><br>dBC<br>MHz<br>V/µs<br>ns<br>ns<br>ns<br>%<br>Degrees                                         |

| INPUT SELECTION <sup>(5)</sup><br>Transition Time<br>50% In to 50% Out                                                                                                                        | ECL: Operation<br>TTL: Operation                                                                                                                                                                                                                    |                             | 4 4                                                        | 8<br>8                                                       | ns<br>ns                                                                                                           |

| $\begin{array}{c} \textbf{DIGITAL INPUT} \\ \textbf{TTL Logic Levels: } V_{IL} \\ V_{IH} \\ I_{IL} \\ I_{IH} \\ \textbf{ECL Logic Levels: } V_{IL} \\ V_{IH} \\ I_{IL} \\ I_{IH} \end{array}$ | Logic "LO"<br>Logic "HI"<br>Logic "CO", $V_{IL} = 0V$<br>Logic "HI", $V_{IH} = +2.7V$<br>Logic "LO"<br>Logic "HI"<br>Logic "HI"<br>Logic "HI", $V_{IL} = -1.6V$<br>Logic "HI", $V_{IH} = -1.0V$                                                     | 0<br>+2.0<br>-1.81<br>-1.15 | -0.05<br>1<br>-50<br>-50                                   | +0.8<br>+5<br>-0.2<br>20<br>-1.475<br>- 0.88<br>-100<br>-100 | V<br>V<br>mA<br>μA<br>V<br>V<br>μA                                                                                 |

| RATED OUTPUT<br>Voltage Output<br>Current Output<br>Output Resistance<br>Load Capacitance Stability<br>Short Circuit Current                                                                  | $\begin{array}{c} R_L = 150\Omega \\ R_L = 50\Omega \end{array}$ 1MHz, Open-Loop, C <sub>C</sub> = 5pF<br>R_F = 100\Omega, Gain = +1V/V, C <sub>C</sub> = 10pF Continuous to Gnd                                                                    | ±2.5<br>±1.7<br>±30         | $\pm 3.75$<br>$\pm 2.2$<br>$\pm 44$<br>5<br>17<br>$\pm 45$ |                                                              | V<br>V<br>mA<br>Ω<br>pF<br>mA                                                                                      |

## **SPECIFICATIONS** (CONT)

#### ELECTRICAL

At V<sub>CC</sub> =  $\pm$ 5VDC, R<sub>L</sub> = 150 $\Omega$ , C<sub>COMP</sub> = 5pF, and T<sub>A</sub> = +25°C, unless otherwise noted.

|                                                                            |                                               |     | OPA678AP, A | J         |                    |

|----------------------------------------------------------------------------|-----------------------------------------------|-----|-------------|-----------|--------------------|

| PARAMETER                                                                  | CONDITIONS                                    | MIN | TYP         | MAX       | UNITS              |

| POWER SUPPLY<br>Rated Voltage<br>Derated Performance<br>Current, Quiescent | $\pm V_{CC}$<br>$\pm V_{CC}$<br>$I_O = 0mADC$ | 4.5 | 5<br>26     | 5.5<br>30 | VDC<br>VDC<br>mA   |

| TEMPERATURE RANGE<br>Specification<br>Thermal Impedance<br>AP<br>AU        | Ambient Temp AP, AU<br>Junction-to-Ambient    | -40 | 90<br>100   | +85       | °C<br>∾C/W<br>°C/W |

NOTES: (1) Specifications are for both inputs (A and B). (2) dBC = Level referred to carrier-input signal. (3) Harmonic distortion will typically be improved significantly in the inverting mode. (4) Large Signal Response is calculated from the formula LSBW =  $\frac{SR}{2\pi V_{PEAK}}$ . (5) Switching time from application of digital logic signal to input signal selection.

#### ELECTRICAL (FULL TEMPERATURE RANGE SPECIFICATIONS)

At V<sub>CC</sub> = ±5VDC, R<sub>L</sub> = 150Ω, C<sub>COMP</sub> = 5pF, and T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.

|                                                                                                                                                                                           |                                                                                                                                                                                                 | OPA678AP, AU                |                          |                                             |                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|---------------------------------------------|------------------------------------|

| PARAMETER                                                                                                                                                                                 | CONDITIONS                                                                                                                                                                                      | MIN                         | ТҮР                      | МАХ                                         | UNITS                              |

| TEMPERATURE RANGE<br>Specification                                                                                                                                                        | Ambient Temp AP/AU                                                                                                                                                                              | -40                         |                          | +85                                         | °C                                 |

| OFFSET VOLTAGE<br>Input Offset Voltage<br>Offset Voltage Drift<br>Supply Rejection                                                                                                        | $T_{A} = T_{MIN} \text{ to } T_{MAX}$<br>$T_{A} = T_{MIN} \text{ to } T_{MAX}$<br>$\pm V_{CC} = 4.5 \text{V to } 5.5 \text{V}$                                                                  | 60                          | 600<br>±3<br>70          | ±2.4mV<br>±15                               | μV<br>μV/°C<br>dB                  |

| BIAS CURRENT<br>Input Bias Current                                                                                                                                                        | V <sub>CM</sub> = 0VDC                                                                                                                                                                          |                             | 15                       | 85                                          | μA                                 |

| OFFSET CURRENT<br>Input Offset Current                                                                                                                                                    | V <sub>CM</sub> = 0VDC                                                                                                                                                                          |                             | 0.5                      | 5                                           | μΑ                                 |

| INPUT VOLTAGE RANGE<br>Common-Mode Input Range<br>Common-Mode Rejection                                                                                                                   | $V_{IN} = \pm 0.5$ VDC, $V_{O} = \pm 1.25$ V                                                                                                                                                    | ±2.0<br>60                  | ±2.5<br>80               |                                             | V<br>dB                            |

| OPEN-LOOP GAIN, DC<br>Open-Loop Voltage Gain                                                                                                                                              |                                                                                                                                                                                                 | 50                          | 60                       |                                             | dB                                 |

| $\begin{array}{c} \textbf{DIGITAL INPUT} \\ \text{TTL Logic Levels: } V_{IL} \\ V_{IH} \\ I_{IL} \\ I_{IH} \\ \text{ECL Logic Levels: } V_{IL} \\ V_{IL} \\ I_{IL} \\ I_{IH} \end{array}$ | Logic "LO"<br>Logic "HI"<br>Logic "HI", $V_{IL} = 0V$<br>Logic "HI", $V_{IH} = +2.7V$<br>Logic "LO"<br>Logic "HI"<br>Logic "HI"<br>Logic "HI", $V_{IL} = -1.6V$<br>Logic "HI", $V_{IH} = -1.0V$ | 0<br>+2.0<br>-1.81<br>-1.15 | -0.08<br>5<br>-50<br>-50 | +0.8<br>+5<br>-0.4<br>50<br>-1.475<br>-0.88 | V<br>V<br>μΑ<br>V<br>V<br>μΑ<br>μΑ |

| RATED OUTPUT<br>Voltage Output<br>Output Current                                                                                                                                          | $R_L = 150\Omega$<br>$R_L = 50\Omega$                                                                                                                                                           | ±2.5<br>±1.5                | ±3.75<br>±2.0<br>44      |                                             | V<br>V<br>mA                       |

| POWER SUPPLY<br>Current, Quiescent                                                                                                                                                        | I <sub>O</sub> = 0mADC                                                                                                                                                                          |                             | 25                       | 35                                          | mA                                 |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

004070

#### **ABSOLUTE MAXIMUM RATINGS**

| Γ | Supply±7VDC                                                 |

|---|-------------------------------------------------------------|

| l | Differential Input Voltage                                  |

| l | Input Voltage Range (Analog and Digital)                    |

| l | Storage Temperature Range65°C to +150°C                     |

| l | Lead Temperature (soldering, 10s) +300°C                    |

| l | Output Short Circuit to Ground (+25°C) Continuous to ground |

| l | Junction Temperature +175°C                                 |

|   |                                                             |

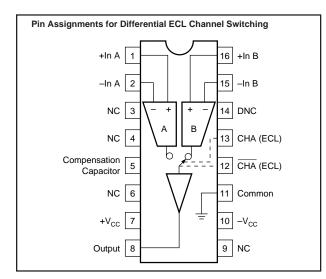

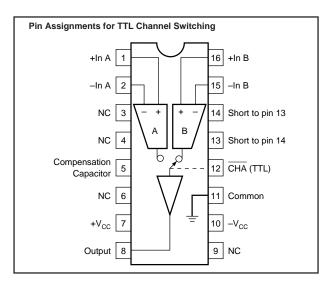

#### PACKAGE INFORMATION

| PRODUCT  | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|------------------------------------------|

| OPA678AP | 16-Pin Plastic DIP | 180                                      |

| OPA678AU | 16-Pin SOIC        | 211                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

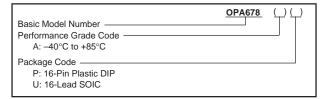

#### **ORDERING INFORMATION**

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

Closed-Loop Gain

NOTE: For the gain of +2V/V,  $C_C = 2.2pF$ ; for the gain of +5V/V,  $C_C = 0$ .

$V_{O} = 0V$  to 0.7V

Closed-Loop Gain

NOTE: For the gain of +2V/V,  $C_C = 2.2pF$ ; for the gain of +5V/V,  $C_C = 0$ .

# **TYPICAL PERFORMANCE CURVES (CONT)**

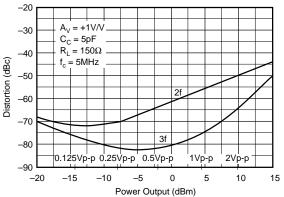

5MHz HARMONIC DISTORTION vs POWER OUTPUT

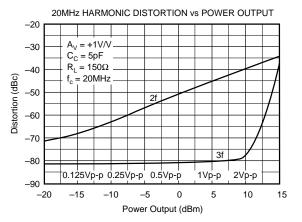

10MHz HARMONIC DISTORTION vs POWER OUTPUT -20  $A_V = +1V/V$ -30  $C_{C} = 5pF$  $R_L = 150\Omega$ -40  $f_c = 10MHz$ Distortion (dBc) -50 2f -60 3f -70 -80 0.125Vp-p 0.25Vp-p 0.5Vp-p 1Vp-p 2Vp-p -90 -15 -20 -10 -5 0 5 10 15 Power Output (dBm)

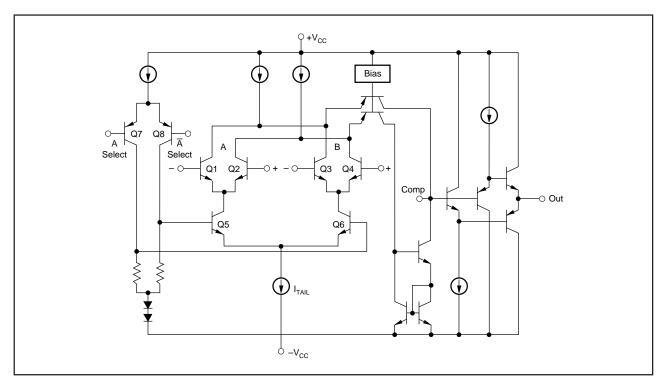

### THEORY OF OPERATION

The simplified circuit of the ECL compatible OPA678 is shown in Figure 1. It is a "classical" high-speed op amp architecture with one important exception-the amplifier has two ECL logic selectable differential input stages. An appropriate differential ECL logic signal on A and  $\overline{A}$  will turn on either Q5 or Q6, steering operating (tail) current to either differential input pair Q1 and Q2 or Q3 and Q4. The input pair receiving the tail current operates as a conventional op-amp input stage while the de-selected input pair receiving no tail current appears as an open circuit. The deselected inputs have only a few pF parasitic capacitance and in the off condition exhibit only a very low leakage (bias) current of about 100pA. Two feedback networks can be connected to each input separately allowing a wide range of circuit applications. The feedback network connected to the selected input operates in a normal op amp fashion while the feedback network connected to the de-selected input is totally inactive, appearing only as an additional load to the amplifier's output stage.

For TTL operation, "A select" is held to an internal reference level by tying pins 13 and 14 together. This allows " $\overline{A}$ " to become the single-ended TTL input.

Standard TTL and ECL logic levels may be applied to each input selection circuit but only 350mV is typically required to switch between inputs. This logic input sensitivity allows simpler high-speed logic driver circuitry and it minimizes digital noise coupling into adjacent wideband analog circuitry and allows single ended ECL inputs to be used with  $V_{BB}$  applied to the other input.

The OPA678 is designed to be frequency compensated by a single capacitor connected from pin 5 to ground. Recommended compensation is shown in the Typical Performance Curve section. A small variable capacitor may be trimmed for best bandwidth, settling time, and gain peaking. Closed-loop gain/phase (Bode) plots are shown in the Typical Performance Curves.

#### OFFSET TRIM

The laser trimmed input offset voltage is low enough for many video and RF applications. Independent control of input offset will require that trim adjust current be summed into one or both inputs.

FIGURE 1. OPA678 Simplified Circuit Diagram.

### **APPLICATION TIPS**

Wideband amplifier circuits require good layout techniques to be successful. The use of short, direct signal paths and heavy (2oz copper recommended) ground planes are absolutely necessary to achieve the performance level inherent in the OPA678. Oscillation, ringing, poor bandwidth and settling, gain peaking, and instability are typical problems that plague all high-speed amplifiers when they are used in poor layouts. The OPA678 is no different in this respect—any amplifier with a gain bandwidth product of a few GHz requires some care be taken in its application.

Points to remember:

- 1. Use a heavy copper ground plane on the component side of your PC board. This provides a low inductance ground and it also conducts heat from active circuit package pins into ambient air by convection.

- 2. Bypass power supply pins directly at the active device. The use of monoblock or tantalum capacitors with very short leads is highly recommended. A  $0.1\mu$ F in parallel with a  $1.0\mu$ F will be optimum in most applications. The  $0.1\mu$ F should be placed directly at the device's power supply leads.

- 3. When using the OPA678 in the unity gain voltage follower configuration it is recommended that a  $100\Omega$  resistor be connected from the output to the inverting input for optimum performance.

- 4. Signal paths should be short and direct. Feedback resistors, compensation capacitors, termination resistors, etc. should have lead lengths no longer than 1/4 inch (6cm).

- 5. Surface mount components (chip resistors, capacitors, etc.) have low inductance and are therefore recommended. Parasitic inductance and capacitance should be avoided if best performance is to be achieved.

- 6. Resistors used in feedback networks should have values of a few hundred ohms for best performance. Shunt capacitance problems limit the acceptable range to about  $1k\Omega$  or on the high resistance end and to a value that is within the amplifier's output drive limits on the low end. Metal film and carbon compensation resistors will be satisfactory.

- 7. Wirewound resistors (even "noninductive" types) are absolutely unacceptable in high frequency circuits.

- Avoid overloading the output. Remember that output current must be provided by the amplifier to drive its own feedback network as well as to drive its "load." Lowest distortion is achieved with high impedance loads.

- 9. PC board traces for signal and power lines should be wide to reduce impedance or inductance.

- 10. Don't forget that these amplifiers use  $\pm 5V$  supplies. Although they will operate perfectly well with  $\pm 5V$  and  $\pm 5.2V$ , the use of  $\pm 15V$  supplies will result in destruction.

- 11. Standard commercial test equipment has not been designed to test devices in the OPA678 speed range. Benchtop op amp testers and ATE systems will require a special test head to successfully test these amplifiers.

- 12. High-speed amplifiers can drive only a limited amount of capacitance. If the load exceeds 10 to 20pF consider using a fast buffer or a small resistor to isolate the capacitance from the amplifier's output. Capacitive loads will cause loop instability if not compensated for.

- 13. Terminate transmission line loads. Unterminated lines, such as coaxial cable, can appear to the amplifier to be a capacitive or inductive load. By terminating a transmission line with its characteristic impedance, the amplifier's load then appears as a purely resistive impedance.

- 14. For clean, fast input selection the logic input pins should be terminated with appropriate resistors. Resistors should be connected from input selection pins to ground plane with short leads. Failure to terminate long lines will result in ringing and poor high frequency switching.

- 15. Plug-in prototype boards and wire-wrap boards will not be satisfactory. A clean layout using RF techniques is required; there is no shortcut.

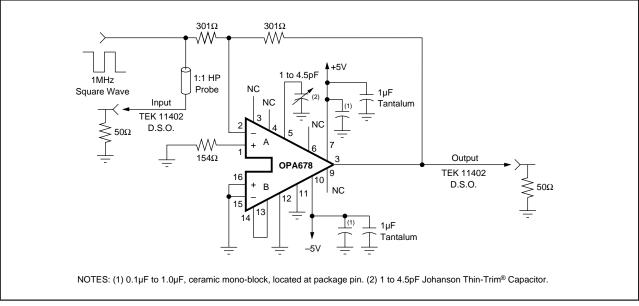

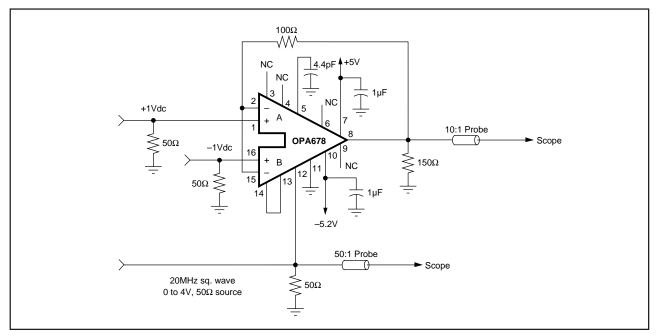

FIGURE 2. OPA678 Settling Time Test Circuit.

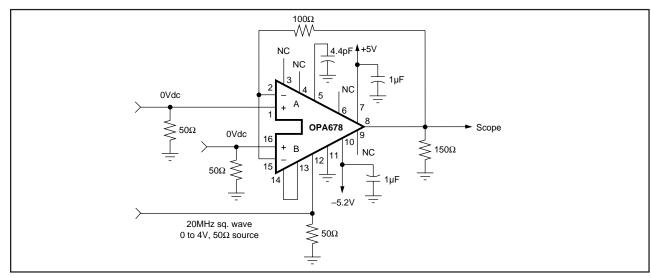

FIGURE 3. OPA678 (TTL) Input Selection Transition Time Test Circuit.

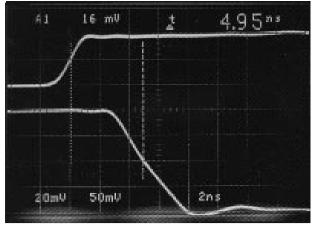

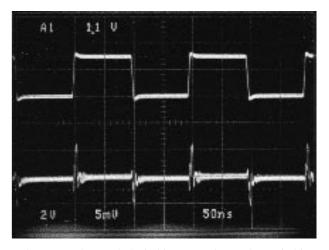

FIGURE 4. OPA678 (TTL) Input Selection Time. Input A to B. Larger output voltages will have slightly slower switching times due to more slewing of the op amp.

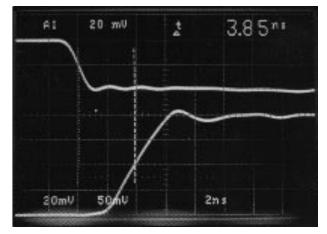

FIGURE 5. OPA678 (ECL) Input Selection Time. Input A to B. Larger output voltages will have slightly slower switching times due to more slewing of the op amp.

FIGURE 6. Channel Select Switching Transient Test Schematic.

FIGURE 7. OPA678 Switching Transient. The switching transient levels will be lower for switching signals with slower rising edges.

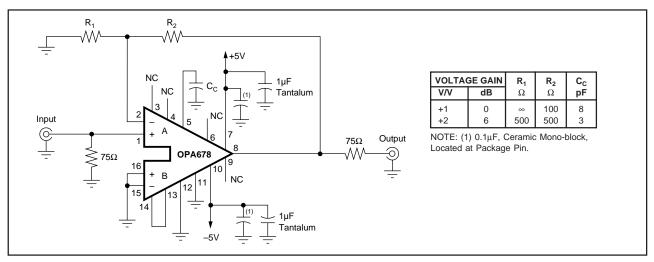

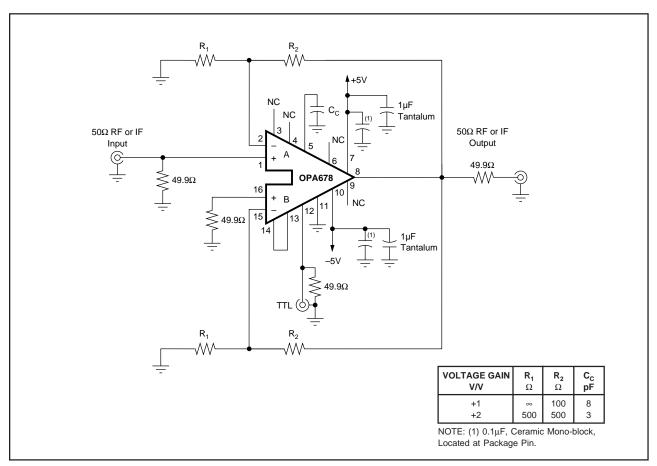

FIGURE 8. OPA678 used as Conventional Op Amp. A wideband video amplifier with 75Ω input and output impedance.

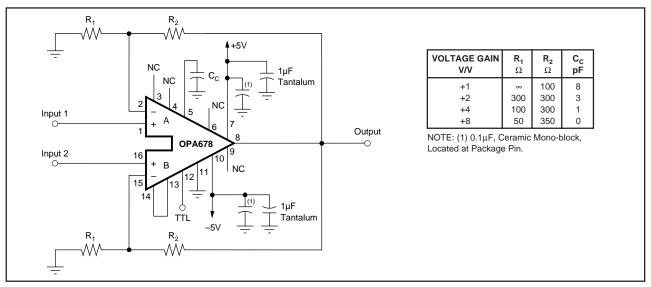

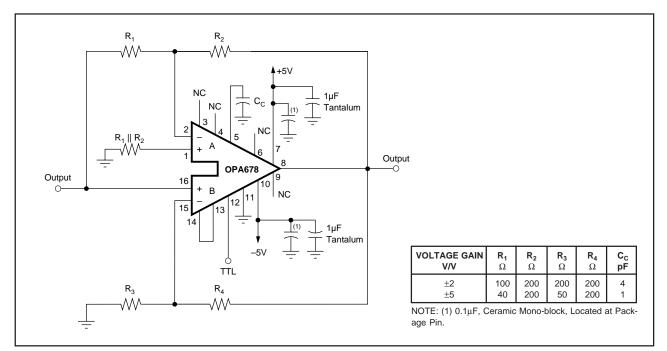

FIGURE 9. Two Input Multiplexer with Gain. This circuit can be used to multiplex I & Q signals into one sampling ADC.

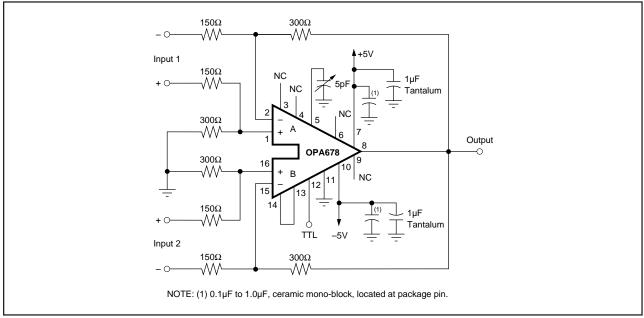

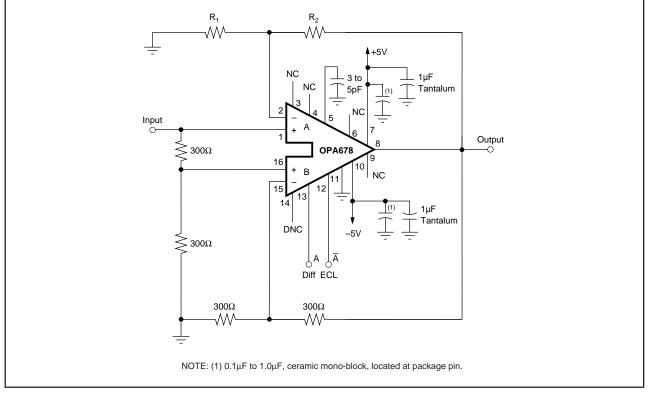

FIGURE 10. Differential Input Multiplexer with Gain of +2V/V.

FIGURE 11. Receiver Noise Blanker: A Wideband Gated Video Amplifier.

FIGURE 12. Synchronous Modulator/Demodulator (with Gain).

FIGURE 13. Very Fast Programmable Gain Amplifier with Voltage Gains of +1V/V and +2V/V (0dB and 6dB).

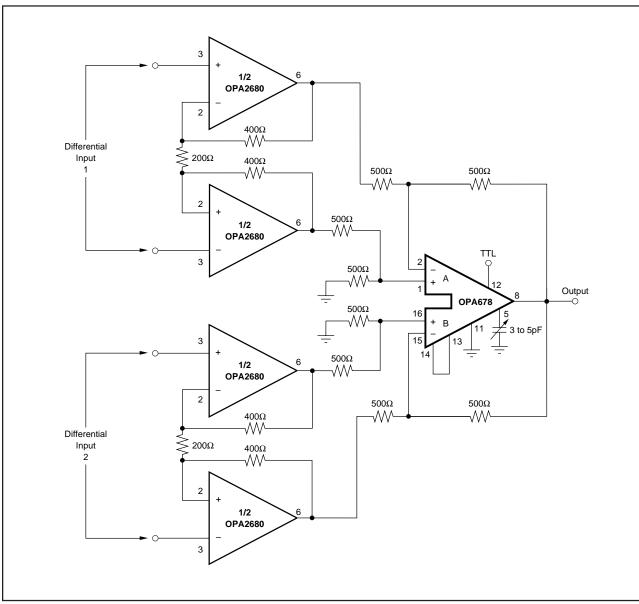

FIGURE 14. High Input Impedance Differential Input Multiplexer with Gain of 5V/V (14dB).