#### 查询\$N74ACT2228供应商

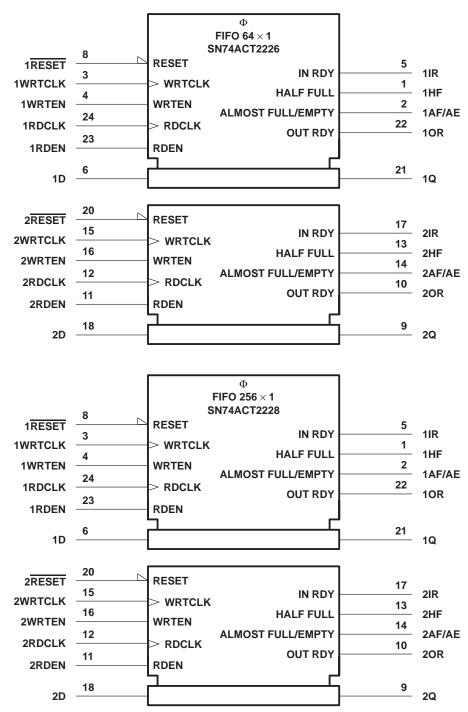

#### 捷多邦,专业PCB扩**SNI74AC和2226**。SNI74ACT2228 DUAL 64 × 1, DUAL 256 × 1 CLOCKED FIRST-IN, FIRST-OUT MEMORIES SCAS219C – JUNE 1992 – REVISED OCTOBER 1997

- Dual Independent FIFOs Organized as: 64 Words by 1 Bit Each – SN74ACT2226 256 Words by 1 Bit Each – SN74ACT2228

- Free-Running Read and Write Clocks Can Be Asynchronous or Coincident on Each FIFO

- Input-Ready Flags Synchronized to Write Clocks

- Output-Ready Flags Synchronized to Read Clocks

- Half-Full and Almost-Full/Almost-Empty

Flags

- Support Clock Frequencies up to 22 MHz

- Access Times of 20 ns

- Low-Power Advanced CMOS Technology

- Packaged in 24-Pin Small-Outline Integrated-Circuit Package

#### **DW PACKAGE** (TOP VIEW) 24 1RDCLK 1HF 1AF/AE 23 IRDEN 2 22 0 1OR 1WRTCLK 21 1Q **1WRTEN** 4 20 20 2RESET 1IR 5 1D 6 19 V<sub>CC</sub> GND 7 18 2D 1RESET 8 $17\Pi 2IR$ 2Q [] 9 16 2WRTEN 2OR 10 15 2WRTCLK 2RDEN 14 2AF/AE 11 13 2HF 2RDCLK 112 WWW.DZSC.COM

#### description

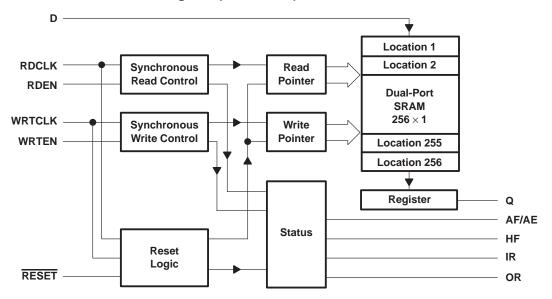

The SN74ACT2226 and SN74ACT2228 are dual FIFOs suited for a wide range of serial-data buffering applications, including elastic stores for frequencies up to T2 telecommunication rates. Each FIFO on the chip is arranged as  $64 \times 1$  (SN74ACT2226) or  $256 \times 1$  (SN74ACT2228) and has control signals and status flags for independent operation. Output flags for each FIFO include input ready (1IR or 2IR), output ready (1OR or 2OR), half full (1HF or 2HF), and almost full/almost empty (1AF/AE or 2AF/AE).

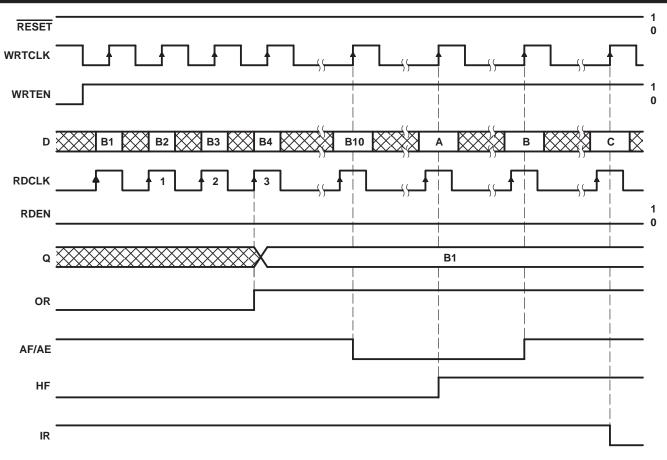

Serial data is written into a FIFO on the low-to-high transition of the write-clock (1WRTCLK or 2WRTCLK) input when the write-enable (1WRTEN or 2WRTEN) input and input-ready flag (1IR or 2IR) output are both high. Serial data is read from a FIFO on the low-to-high transition of the read-clock (1RDCLK or 2RDCLK) input when the read-enable (1RDEN or 2RDEN) input and output-ready flag (1OR or 2OR) output are both high. The read and write clocks of a FIFO can be asynchronous to one another.

Each input-ready flag (1IR or 2IR) is synchronized by two flip-flop stages to its write clock (1WRTCLK or 2WRTCLK), and each output-ready flag (1OR or 2OR) is synchronized by three flip-flop stages to its read clock (1RDCLK or 2RDCLK). This multistage synchronization ensures reliable flag-output states when data is written and read asynchronously.

A half-full flag (1HF or 2HF) is high when the number of bits stored in its FIFO is greater than or equal to half the depth of the FIFO. An almost-full/almost-empty flag (1AF/AE or 2AF/AE) is high when eight or fewer bits are stored in its FIFO and when eight or fewer empty locations are left in the FIFO. A bit present on the data output is not stored in the FIFO.

The SN74ACT2226 and SN74ACT2228 are characterized for operation from -40°C to 85°C.

For more information on this device family, see the application report *FIFOs With a Word Width of One Bit* (literature number SCAA006).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### logic symbols<sup>†</sup>

<sup>†</sup> These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

**D** -▼ Location 1 RDCLK -Location 2 Synchronous Read Read Control Pointer RDEN -**Dual-Port** SRAM  $64 \times 1$ WRTCLK -Synchronous Write Write Control Pointer WRTEN -Location 63 Location 64 ╈ Register - Q - AF/AE Status HF Reset IR Logic RESET -OR

#### SN74ACT2226 functional block diagram (each FIFO)

SN74ACT2228 functional block diagram (each FIFO)

| TERMIN                   | TERMINAL |   |                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|--------------------------|----------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME NO.                 |          |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 1AF/AE<br>2AF/AE         | 2<br>14  | ο | Almost-full/almost-empty flag. AF/AE is high when the memory is eight locations or less from a full or empty state. AF/AE is set high after reset.                                                                                                                                                                                     |  |  |  |  |  |

| 1D<br>2D                 | 6<br>18  | I | Data input                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GND                      | 7        |   | Ground                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 1HF<br>2HF               | 1<br>13  | 0 | Half-full flag. HF is high when the number of bits stored in memory is greater than or equal to half the FIFO depth. HF is set low after reset.                                                                                                                                                                                        |  |  |  |  |  |

| 1IR<br>2IR               | 5<br>17  | 0 | Input-ready flag. IR is synchronized to the low-to-high transition of WRTCLK. When IR is low, the FIFO is full and writes are disabled. IR is set low during reset and is set high on the second low-to-high transition of WRTCLK after reset.                                                                                         |  |  |  |  |  |

| 1OR<br>2OR               | 22<br>10 | 0 | Output-ready flag. OR is synchronized to the low-to-high transition of RDCLK. When OR is low, the FIFO is empty and reads are disabled. Ready data is present on the data output when OR is high. OR is set low during reset and set high on the third low-to-high transition of RDCLK after the first word is loaded to empty memory. |  |  |  |  |  |

| 1Q<br>2Q                 | 21<br>9  | 0 | Data outputs. After the first valid write to empty memory, the first bit is output on the third rising edge of RDCLK. OR for the FIFO is asserted high to indicate ready data.                                                                                                                                                         |  |  |  |  |  |

| 1RDCLK<br>2RDCLK         | 24<br>12 | I | Read clock. RDCLK is a continuous clock and can be independent of any other clock on the device. A low-to-high transition of RDCLK reads data from memory when the FIFO RDEN and OR are high. OR is synchronous with the low-to-high transition of RDCLK.                                                                              |  |  |  |  |  |

| 1RDEN<br>2RDEN           | 23<br>11 | I | Read enable. When the RDEN and OR of a FIFO are high, data is read from the FIFO on the low-to-high transition of RDCLK.                                                                                                                                                                                                               |  |  |  |  |  |

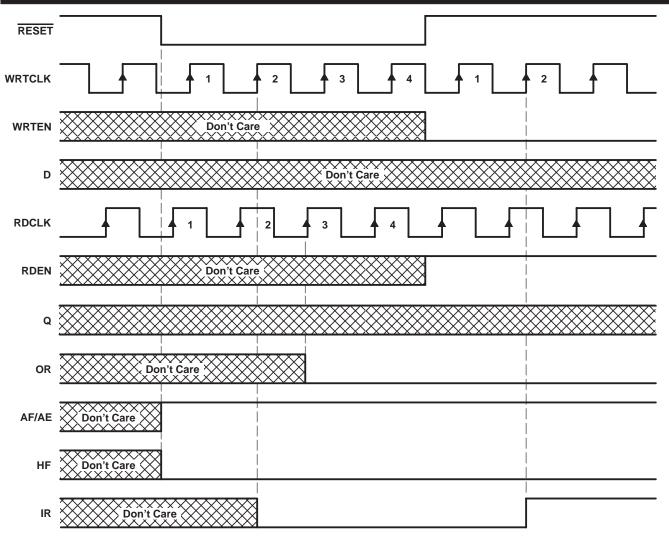

| 1 <u>RESET</u><br>2RESET | 8<br>20  | I | Reset. To reset the FIFO, four low-to-high transitions of RDCLK and four low-to-high transitions of WRTCLK must occur while RESET is low. This sets HF, IR, and OR low and AF/AE high. Before it is used, a FIFO must be reset after power up.                                                                                         |  |  |  |  |  |

| VCC                      | 19       |   | Supply voltage                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 1WRTCLK<br>2WRTCLK       | 3<br>15  | I | Write clock. WRTCLK is a continuous clock and can be independent of any other clock on the device. A low-to-high transition of WRTCLK writes data to memory when WRTEN and IR are high. IR is synchronous with the low-to-high transition of WRTCLK.                                                                                   |  |  |  |  |  |

| 1WRTEN<br>2WRTEN         | 4<br>16  | I | Write enable. When WRTEN and IR are high, data is written to the FIFO on a low-to-high transition of WRTCLK.                                                                                                                                                                                                                           |  |  |  |  |  |

#### **Terminal Functions**

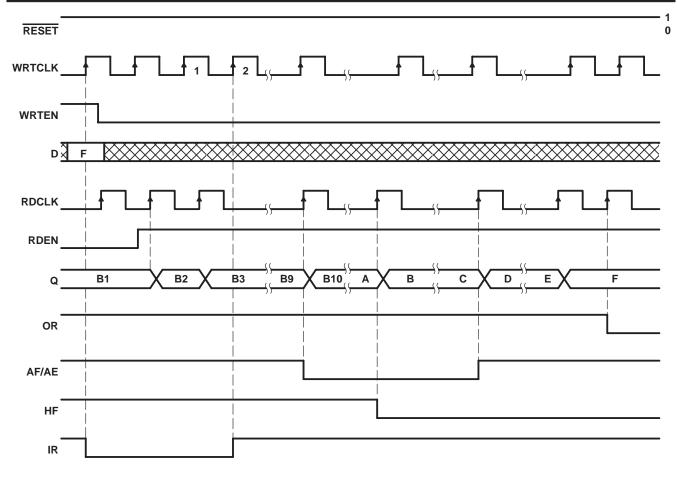

Figure 1. FIFO Reset

#### DATA BIT NUMBER BASED ON FIFO DEPTH

|   | DEVICE      | DATA BIT |      |      |  |  |

|---|-------------|----------|------|------|--|--|

|   | DEVICE      | Α        | В    | С    |  |  |

| ſ | SN74ACT2226 | B33      | B57  | B65  |  |  |

|   | SN74ACT2228 | B129     | B249 | B257 |  |  |

Figure 2. FIFO Write

#### DATA BIT NUMBER BASED ON FIFO DEPTH

| DEVICE      |      | DATA BIT |      |      |      |      |  |

|-------------|------|----------|------|------|------|------|--|

| DEVICE      | Α    | В        | С    | D    | Е    | F    |  |

| SN74ACT2226 | B33  | B34      | B56  | B57  | B64  | B65  |  |

| SN74ACT2228 | B129 | B130     | B248 | B249 | B256 | B257 |  |

Figure 3. FIFO Read

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, $V_{CC}$<br>Input voltage range, $V_I$ (see Note 1)<br>Output voltage range, $V_O$ (see Note 1)<br>Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ )<br>Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ )<br>Continuous output current, $I_O$ ( $V_O = 0$ to $V_{CC}$ )<br>Continuous current through $V_{CC}$ or GND<br>Package thermal impedance, $\theta_{JA}$ (see Note 2) | $\begin{array}{c} -0.5 \ \text{V to } \ \text{V}_{\text{CC}} + 0.5 \ \text{V} \\ -0.5 \ \text{V to } \ \text{V}_{\text{CC}} + 0.5 \ \text{V} \\ \pm 20 \ \text{mA} \\ \pm 50 \ \text{mA} \\ \pm 50 \ \text{mA} \\ \pm 200 \ \text{mA} \\ \end{array}$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package thermal impedance, $\theta_{JA}$ (see Note 2)<br>Storage temperature range, $T_{stg}$                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                       |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                       |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded provided that the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51.

#### recommended operating conditions

|                |                                            | MIN | MAX | UNIT |

|----------------|--------------------------------------------|-----|-----|------|

| VCC            | V <sub>CC</sub> Supply voltage             |     |     | V    |

| VIH            | High-level input voltage                   | 2   |     | V    |

| VIL            | Low-level input voltage                    |     | 0.8 | V    |

| ЮН             | High-level output current Q outputs, flags |     | -8  | mA   |

| 1.01           | Q outputs                                  |     | 16  | A    |

| IOL            | Low-level output current Flags             |     |     | mA   |

| Т <sub>А</sub> | Operating free-air temperature             | -40 | 85  | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PA    | RAMETER   |                              | TEST CONDITIONS                                     | MIN | TYP‡ | MAX | UNIT |  |

|-------|-----------|------------------------------|-----------------------------------------------------|-----|------|-----|------|--|

| VOH   |           | $V_{CC} = 4.5 V,$            | I <sub>OH</sub> = -8 mA                             | 2.4 |      |     | V    |  |

| Vei   | Flags     | $V_{CC} = 4.5 V,$            | I <sub>OL</sub> = 8 mA                              |     |      | 0.5 | v    |  |

| VOL   | Q outputs | V <sub>CC</sub> = 4.5 V,     | I <sub>OL</sub> = 16 mA                             |     |      | 0.5 | v    |  |

| Ц     |           | $V_{CC} = 5.5 V,$            | $V_{I} = V_{CC} \text{ or } 0$                      |     |      | ±5  | μΑ   |  |

| loz   |           | $V_{CC} = 5.5 V,$            | $V_{O} = V_{CC} \text{ or } 0$                      |     |      | ±5  | μΑ   |  |

| ICC   |           | $V_{I} = V_{CC} - 0.2 V_{O}$ | or 0                                                |     |      | 400 | μA   |  |

| ∆ICC§ |           | V <sub>CC</sub> = 5.5 V,     | One input at 3.4 V, Other inputs at $V_{CC}$ or GND |     |      | 1   | mA   |  |

| Ci    |           | $V_{I} = 0,$                 | f = 1 MHz                                           |     | 4    |     | pF   |  |

| Co    |           | $V_{O} = 0,$                 | f = 1 MHz                                           |     | 8    |     | pF   |  |

<sup>‡</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

This is the supply current when each input is at one of the specified TTL voltage levels rather than 0 V or V<sub>CC</sub>.

### timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figures 1 through 3)

|                 |                 |                                                                                                                                    | MIN | MAX | UNIT |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| fclock          | Clock frequency |                                                                                                                                    |     | 22  | MHz  |

|                 | Pulse duration  | 1WRTCLK, 2WRTCLK high or low                                                                                                       | 15  |     | ns   |

| tw              | Fuise duration  | 1RDCLK, 2RDCLK high or low                                                                                                         | 15  |     | 115  |

|                 |                 | 1D before 1WRTCLK <sup>↑</sup> and 2D before 2WRTCLK <sup>↑</sup>                                                                  | 6   |     |      |

|                 |                 | 1WRTEN before 1WRTCLK $\uparrow$ and 2WRTEN before 2WRTCLK $\uparrow$                                                              | 6   |     |      |

| t <sub>su</sub> | Setup time      | 1RDEN before 1RDCLK <sup>↑</sup> and 2RDEN before 2RDCLK <sup>↑</sup>                                                              | 6   |     | ns   |

|                 |                 | $1\overline{\text{RESET}}$ low before $1WRTCLK^{\uparrow}$ and $2\overline{\text{RESET}}$ low before $2WRTCLK^{\uparrow \uparrow}$ | 6   |     |      |

|                 |                 | 1RESET low before 1RDCLK $\uparrow$ and 2RESET low before 2RDCLK $\uparrow\uparrow$                                                | 6   |     |      |

|                 |                 | 1D after 1WRTCLK <sup>↑</sup> and 2D after 2WRTCLK <sup>↑</sup>                                                                    | 0   |     |      |

|                 |                 | 1WRTEN after 1WRTCLK <sup>↑</sup> and 2WRTEN after 2WRTCLK <sup>↑</sup>                                                            | 0   |     |      |

| t <sub>h</sub>  | Hold time       | 1RDEN after 1RDCLK <sup>↑</sup> and 2RDEN after 2RDCLK <sup>↑</sup>                                                                | 0   |     | ns   |

|                 |                 | 1RESET low after 1WRTCLK↑ and 2RESET low after 2WRTCLK↑†                                                                           | 6   |     |      |

|                 |                 | 1RESET low after 1RDCLK $\uparrow$ and 2RESET low after 2RDCLK $\uparrow\uparrow$                                                  | 6   |     |      |

<sup>†</sup>Requirement to count the clock edge as one of at least four needed to reset a FIFO

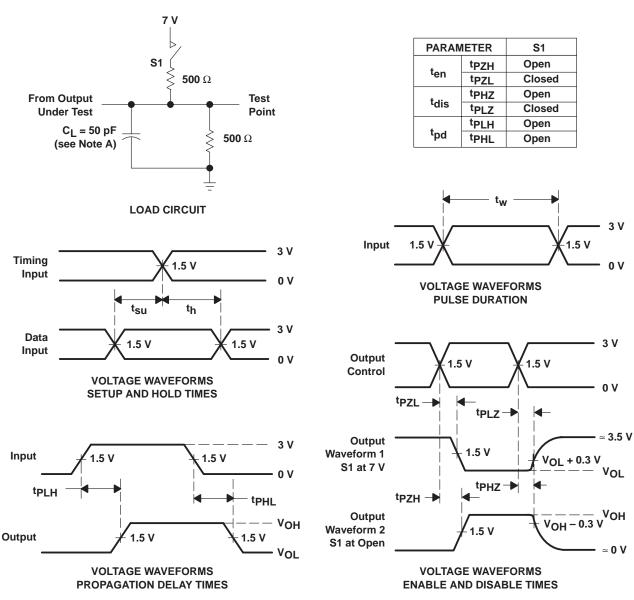

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $C_L = 50 \text{ pF}$ (unless otherwise noted) (see Figure 4)

| PARAMETER        | FROM<br>(INPUT)                             | TO<br>(OUTPUT) | MIN | МАХ | UNIT |

|------------------|---------------------------------------------|----------------|-----|-----|------|

| fmax             | 1WRTCLK, 2WRTCLK,<br>or 1RDCLK, 2RDCLK      |                | 22  |     | MHz  |

|                  | 1RDCLK <sup>↑</sup> , 2RDCLK <sup>↑</sup>   | 1Q, 2Q         | 2   | 20  |      |

|                  | 1WRTCLK <sup>↑</sup> , 2WRTCLK <sup>↑</sup> | 1IR, 2IR       | 1   | 20  |      |

| <sup>t</sup> pd  | 1RDCLK $\uparrow$ , 2RDCLK $\uparrow$       | 10R, 20R       | 1   | 20  | ns   |

|                  | 1WRTCLK <sup>↑</sup> , 2WRTCLK <sup>↑</sup> | 1AF/AE, 2AF/AE | 3   | 20  |      |

|                  | 1RDCLK $\uparrow$ , 2RDCLK $\uparrow$       |                | 3   | 20  |      |

| <sup>t</sup> PLH | 1WRTCLK <sup>↑</sup> , 2WRTCLK <sup>↑</sup> | 1HF, 2HF       | 2   | 20  | 20   |

| <sup>t</sup> PHL | 1RDCLK $\uparrow$ , 2RDCLK $\uparrow$       | 1пг, 2пг       | 3   | 20  | ns   |

| <sup>t</sup> PLH | 1RESET, 2RESET low                          | 1AF/AE, 2AF/AE | 1   | 20  | ns   |

| <sup>t</sup> PHL | INLOLI, ZRESET IOW                          | 1HF, 2HF       | 1   | 20  | 115  |

#### PARAMETER MEASUREMENT INFORMATION

Figure 4. Load Circuit and Voltage Waveforms

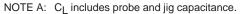

#### **TYPICAL CHARACTERISTICS**

Figure 5

#### calculating power dissipation

Data for Figure 5 is taken with one FIFO active and one FIFO idle on the device. The active FIFO has both writes and reads enabled with its read clock (RDCLK) and write clock (WRTCLK) operating at the rate specified by  $f_{clock}$ . The data input rate and data output rate are half the  $f_{clock}$  rate, and the data output is disconnected. A close approximation of the total device power can be found by using Figure 5, determining the capacitive load on the data output and determining the number of SN74ACT2226/2228 inputs driven by TTL high levels.

With  $I_{CC(f)}$  taken from Figure 5, the maximum power dissipation (P<sub>T</sub>) of one FIFO on the SN74ACT2226 or SN74ACT2228 can be calculated by:

$$\mathsf{P}_{\mathsf{T}} = \mathsf{V}_{\mathsf{C}\mathsf{C}} \times [\mathsf{I}_{\mathsf{C}\mathsf{C}(\mathsf{f})} + (\mathsf{N} \times \Delta \mathsf{I}_{\mathsf{C}\mathsf{C}} \times \mathsf{d}\mathsf{c})] + (\mathsf{C}_{\mathsf{L}} \times \mathsf{V}_{\mathsf{C}\mathsf{C}}^2 \times \mathsf{f}_{\mathsf{o}})$$

where:

N = number of inputs driven by TTL levels

- $\Delta I_{CC}$  = increase in power-supply current for each input at a TTL high level

- dc = duty cycle of inputs at a TTL high level of 3.4 V

- C<sub>L</sub> = output capacitive load

- $f_0$  = switching frequency of an output

### **APPLICATION INFORMATION**

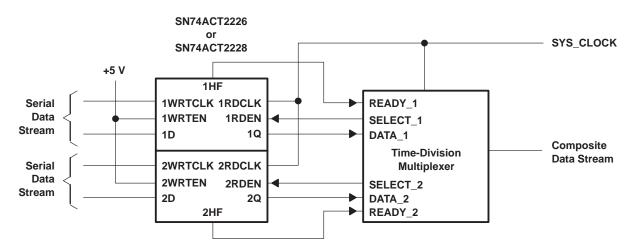

An example of concentrating two independent serial-data signals into a single composite data signal with the use of an SN74ACT2226 or SN74ACT2228 device is shown in Figure 6. The input data to the FIFOs share the same average (mean) frequency and the mean frequency of the SYS\_CLOCK is greater than or equal to the sum of the individual mean input rates. A single-bit FIFO is needed for each additional input data signal that is time-division multiplexed into the composite signal.

The FIFO memories provide a buffer to absorb clock jitter generated by the transmission systems of incoming signals and synchronize the phase-independent inputs to one another. FIFO half-full (HF) flags are used to signal the multiplexer to start fetching data from the buffers. The state of the flags also can be used to indicate when a FIFO read should be suppressed to regulate the output flow (pulse-stuffing control). The FIFO almost-full/almost-empty (AF/AE) flags can be used in place of the half-full flags to reduce transmission delay.

Figure 6. Time-Division Multiplexing Using the SN74ACT2226 or SN74ACT2228

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated