# TUSB2140B Data Manual

4-Port Hub With an Embedded Function for the Universal Serial Bus

SLLS313A March 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

# **Contents**

| Section                                                                   | n litle                                                                                                                                                            | Page                                                        |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1 Int<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                                  | 1.1.1 Hub 1.1.2 Embedded Function 1.1.3 General Characteristics 2 Terminal Assignments 3 Terminal Functions 4 Device-Numbering Convention and Ordering Information | 1–1 1–2 1–2 1–2 1–3 1–5                                     |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.7<br>2.8<br>2.1<br>2.1<br>2.1<br>2.1 | USB Transceiver Clock Generator Serial Interface Engine (SIE) SIE Interface Logic Hub Command Decoder Frame Timer Suspend/Resume Logic                             | 2–1 2–1 2–1 2–2 2–2 2–2 2–2 2–2 2–3 2–3                     |

| 3 Int<br>3.1<br>3.2                                                       | 7.00.000                                                                                                                                                           | 3-2<br>3-4<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-8<br>3-9 |

|     |          | 3.2.11 Endpoint 0 Receive Control Register 3.2.12 Endpoint 0 Receive Status Register 3.2.13 Endpoint 0 Receive FIFO Flags Register 3.2.14 Endpoint 1 Transmit FIFO 3.2.15 Endpoint 1 Transmit Byte Count Register 3.2.16 Endpoint 1 Transmit Control Register 3.2.17 Endpoint 1 Transmit Status Register 3.2.18 Endpoint 1 Transmit FIFO Flags Register 3.2.19 PID Low-Byte Register 3.2.20 PID High-Byte Register 3.2.21 VID Low-Byte Register 3.2.22 VID High-Byte Register | 3-11<br>3-12<br>3-12<br>3-13<br>3-13<br>3-15<br>3-15<br>3-16<br>3-16 |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| 4   |          | ce Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

|     |          | Device Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

|     |          | Embedded Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

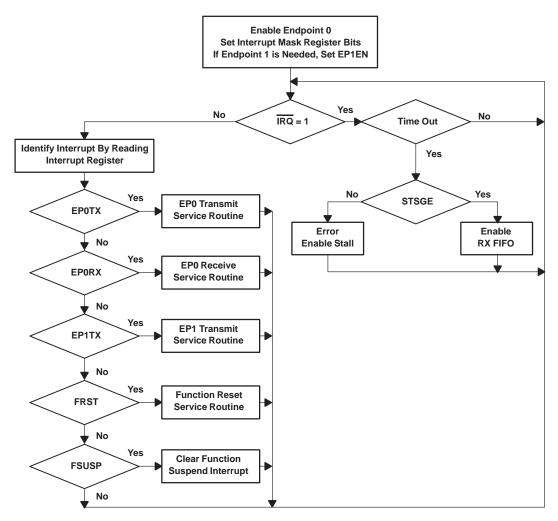

|     | 4.5      | 4.3.1 Interrupt Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|     |          | 4.3.2 Function Reset and USB Reset                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

|     |          | 4.3.3 Enumeration                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

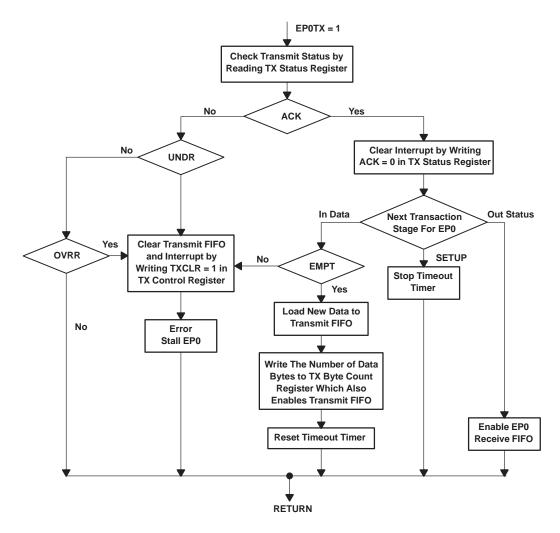

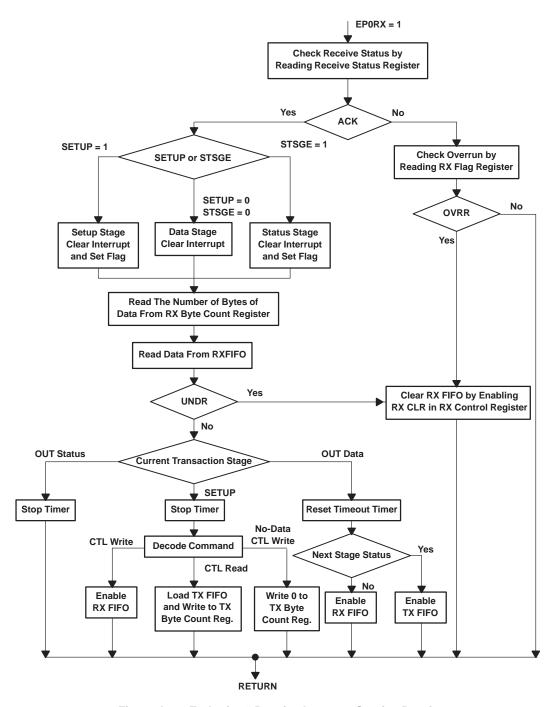

|     |          | 4.3.4 Control Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4–2                                                                  |

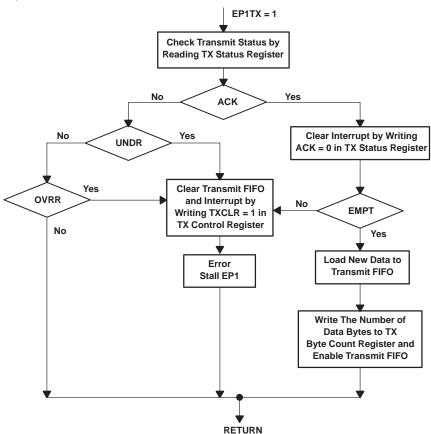

|     |          | 4.3.5 Interrupt Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|     |          | 4.3.6 Suspend and Remote Wake-Up                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

|     |          | 4.3.7 I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

|     |          | Over-Current Detection and Power Switching                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|     |          | Clock Output Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|     | 4.0      | Power Supply Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-0                                                                  |

| 5   |          | rical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

|     |          | Absolute Maximum Ratings Over Operating Free-air Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

|     | 5.2      | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5–1                                                                  |

|     | 5.3      | Electrical Characteristics Over Recommended Ranges of Operating Free-air                                                                                                                                                                                                                                                                                                                                                                                                      | F 0                                                                  |

|     | 5.4      | Temperature and Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

|     | 5.4      | 5.4.1 Timing Characteristics for USB Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

|     |          | 5.4.2 Timing Characteristics for I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

|     |          | 5.4.3 Timing Characteristics for Remote Wake-Up                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| 6   | HED      | Overview Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6 1                                                                  |

| U   |          | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|     |          | Bus-Powered Hub, Ganged Port Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

|     |          | Self-Powered Hub, Ganged Port Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

|     |          | Self-Powered Hub, Individual Port Power Management                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| Anı | oendi    | x A Firmware Development                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Δ_1                                                                  |

|     |          | x B Firmware Example                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

|     |          | x C Flow Chart for the Firmware Sample Code                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

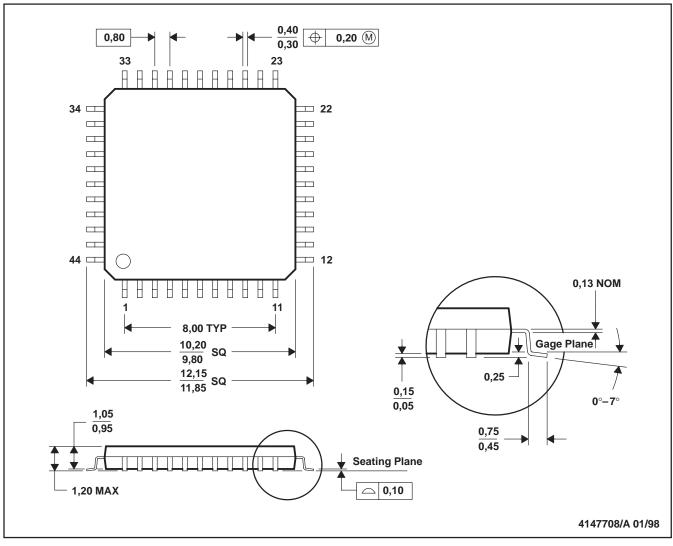

|     |          | x D. Mechanical Data                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D_1                                                                  |

| AIN | JE-11(11 | X D. WEGHAUKAL DAIA                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 /                                                                  |

# **List of Illustrations**

| F | igure                                         | Title                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                 |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

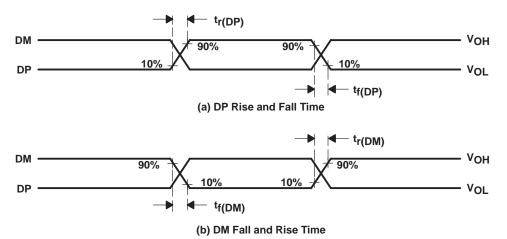

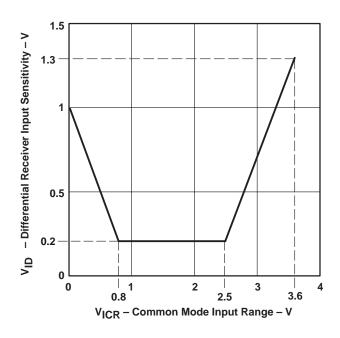

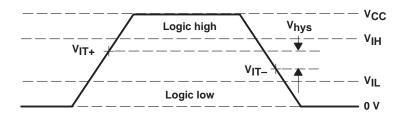

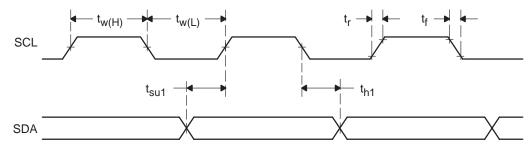

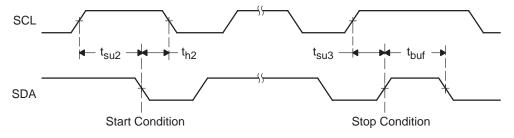

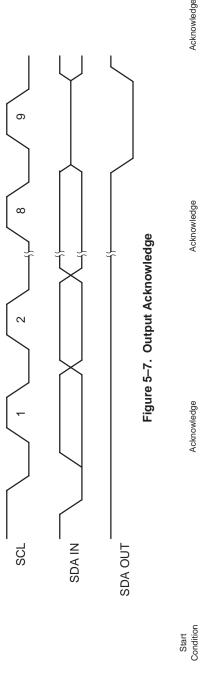

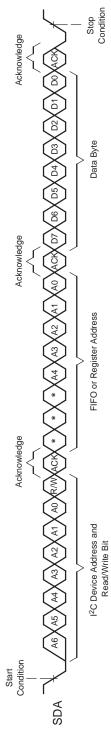

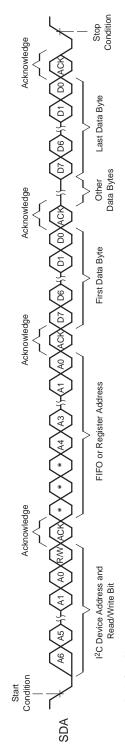

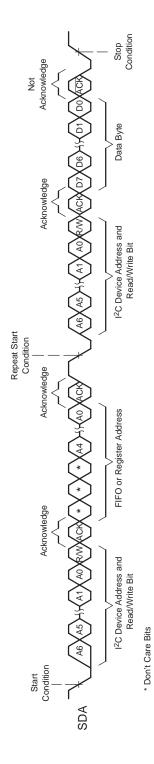

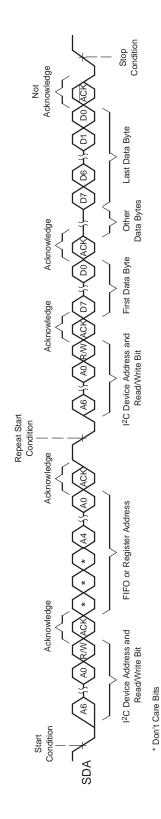

|   | 5–11                                          | Differential Driver Switching Load USB Data Signal Rise and Fall Times Differential Receiver Input Sensitivity vs Common Mode Input Range Single-Ended Receiver Input Signal Parameter Definitions SCL and SDA Timing Start and Stop Conditions Output Acknowledge Single Byte Write Transfer Multiple Byte Write Transfer Single Byte Read Transfer Multiple Byte Read Transfer Remote Wake-Up | 5-4<br>5-5<br>5-5<br>5-5<br>5-6<br>5-6<br>5-7<br>5-7 |

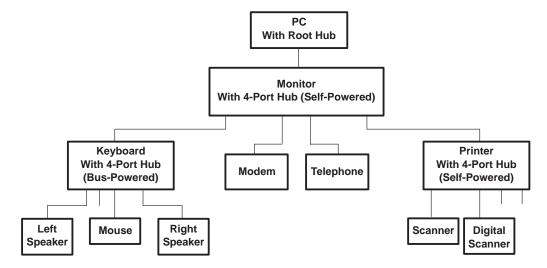

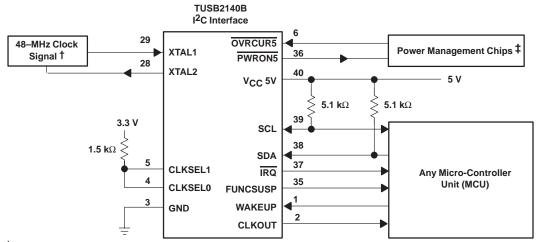

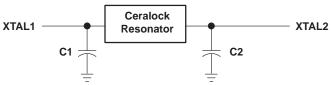

|   | 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7 | USB Tiered Configuration Example Typical I <sup>2</sup> C Interface Connection to a Microcontroller Resonator Clock Circuit Crystal Tuning Circuit TUSB2140B Bus-Powered Hub, Ganged Port Power Management Application . TUSB2140B Self-Powered Hub, Ganged Port Power Management Application . TUSB2140B Self-Powered Hub, Individual-Port Power Management Application . Application          | 6–2<br>6–3<br>6–4<br>6–5                             |

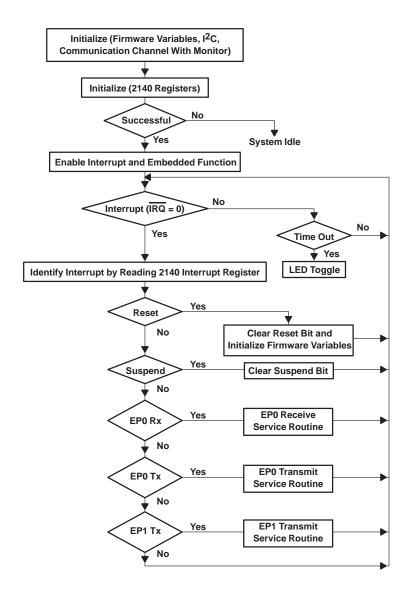

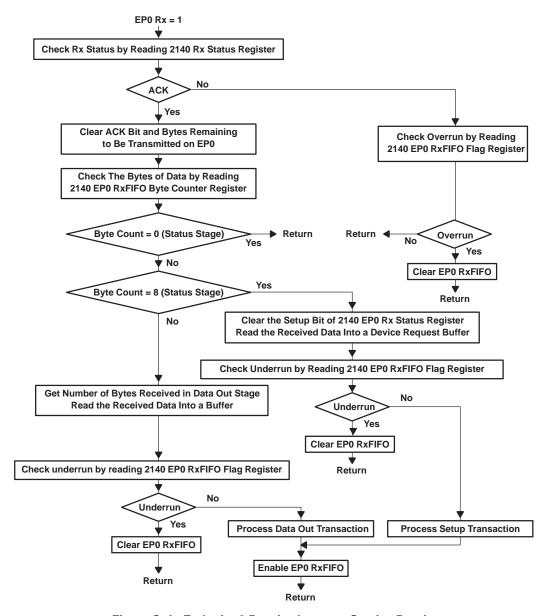

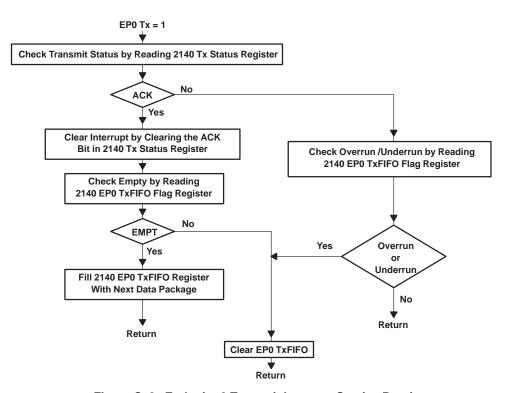

|   | A-1<br>A-2<br>A-3<br>A-4                      | Flow Chart for TUSB2140B Firmware  Endpoint 0 Transmit Interrupt Service Routine  Endpoint 0 Receive Interrupt Service Routine  Endpoint 1 Transmit Interrupt Service Routine                                                                                                                                                                                                                   | A-2<br>A-3<br>A-5                                    |

|   | C-2                                           | Flow Chart for TUSB2140B Firmware (Sample Code) Endpoint 0 Receive Interrupt Service Routine                                                                                                                                                                                                                                                                                                    | C-2                                                  |

### 1 Introduction

The TUSB2140B is a compound USB device that provides an external 4-port hub and an embedded function that is virtually connected to an internal fifth hub port. The TUSB2140B is fully compatible with the USB, version 1.0, specification and the embedded function is fully compatible with the USB display-device class specification. The USB hub has a control endpoint and an interrupt endpoint. The embedded function also includes a control endpoint and an interrupt endpoint to support USB data transfers. The FIFOs and control registers associated with the endpoints are fully integrated within the device. An Inter IC(I<sup>2</sup>C), 2-wire serial bus provides an interface for any local micro-controller unit (MCU) to access the FIFOs and control registers.

The TUSB2140B hub has the default power-on vendor ID (VID) of 0451H and a product ID (PID) of 2140H for the hub which will be displayed as *General-Purpose USB Hub* during enumeration. When custom vendor and product ID's are desired for the external 4-port USB hub, the default VID/PID values can be replaced with custom values that are firmware based. When new VID/PID values are desired, they must be down-loaded through the I<sup>2</sup>C interface before the MCU connects the embedded function. The VID and PID for the embedded functions are always firmware based.

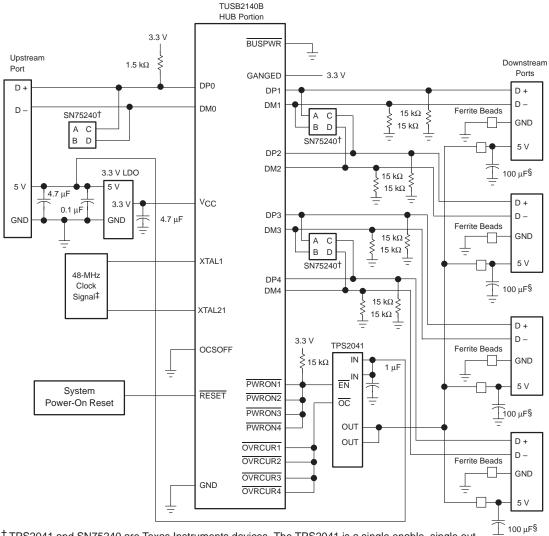

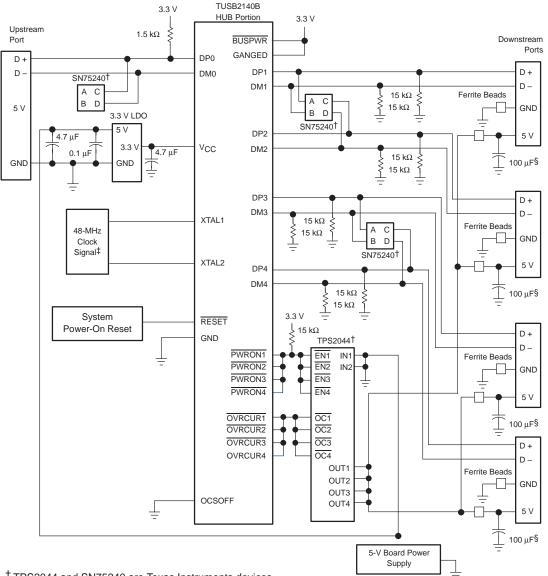

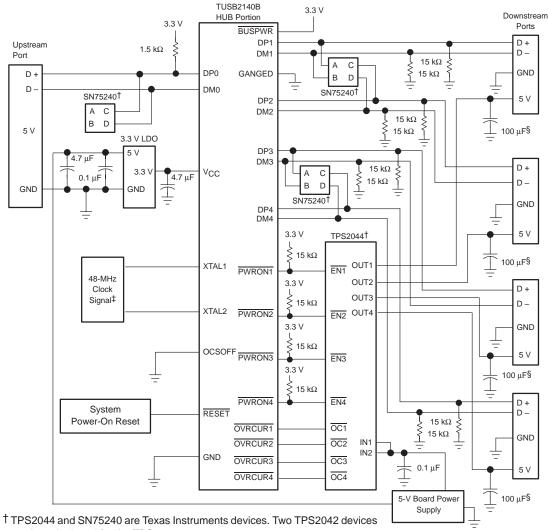

The TUSB2140B hub supports power switching to the downstream ports for either individual or ganged power management modes. External power-management devices are required to switch power and to detect over-current conditions. See *Application Information* in Section 6. The TUSB2140B provides the required inputs and outputs needed for the power-management devices to control power switching and to monitor any over-current conditions. In the ganged mode, all PWRON signals switch simultaneously and all OVRCUR inputs should be tied together and driven by the same signal.

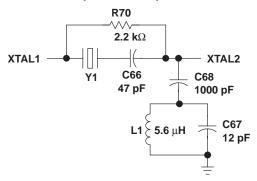

The TUSB2140B requires a 48-MHz clock signal to sample data from the upstream port and to generate a synchronized 12-MHz USB clock signal. The hub supports the flexibility to use either a 48-MHz oscillator, a 48-MHz resonator, or a crystal tuned to 48-MHz. When an oscillator is used, the oscillator output must be connected to the XTAL1 terminal and the XTAL2 terminal should remain open. An oscillator with a TTL level output may be used if the output does not exceed 3.6-V maximum. When an oscillator is used, the TUSB2140B device will not be able to go into low-power suspend mode because the oscillator will always drive a 48-MHz clock signal into the TUSB2140B. A better implementation is to use a passive device such as a resonator or a crystal because when the TUSB2140B suspends, the resonator and crystal will also stop operation. For a resonator or crystal implementation, the XTAL1 terminal should be used as the input and the XTAL2 terminal should be used as the feedback path. See Figure 6–3 for resonator connection. Because the crystal is required to resonate at 48-MHz, a tuning circuit may be required such as shown in Figure 6–4.

USB-compatible transceivers are provided for all upstream and downstream ports. All external downstream ports support both full-speed and low-speed connections by automatically setting the slew rate according to the speed of the device attached to the port.

#### 1.1 Features

The main features of the TUSB2140B hub and embedded function are listed in the following sections.

#### 1.1.1 Hub

- Universal Serial Bus (USB) Version 1.0 Compatible

- Includes Serial Interface Engine (SIE)

- All Four External Downstream Ports Support Full-Speed and Low-Speed Operations

- Integrated USB Transceivers

- Power Switching and Over-Current Conditions are Reported for Per Port or Ganged Modes

- Supports default or custom Product ID (PID) and Vendor ID (VID)

### 1.1.2 Embedded Function

- USB Display Class Compatible

- Supports both Control and Interrupt Data Transfers

- Integrated FIFOs and Control/Status Registers

- Supports Interrupt Driven Operation to Minimize Local Micro-Controller Polling

- Supports USB Remote Wake-Up

- Supports Custom Product ID (PID) and Vendor ID (VID)

#### 1.1.3 General Characteristics

- Low-Power CMOS Technology

- Generates a Clock Output With a Frequency of 12 MHz, 8 MHz, 6 MHz, or 4 MHz

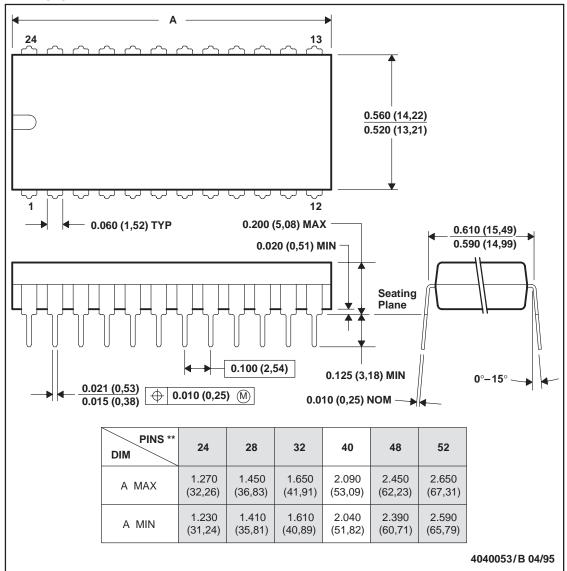

- Available in a 40-Pin Dip Package or a 44-Pin LQFP Package

- Requires a 48-MHz Crystal, a 48-MHz Resonator, or 48-MHz Oscillator Input

- Uses a 3.3 V and 5 V Power Supply

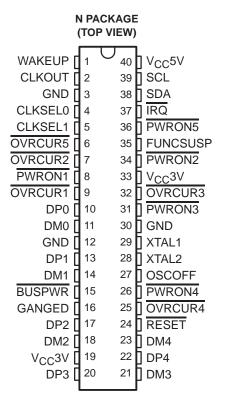

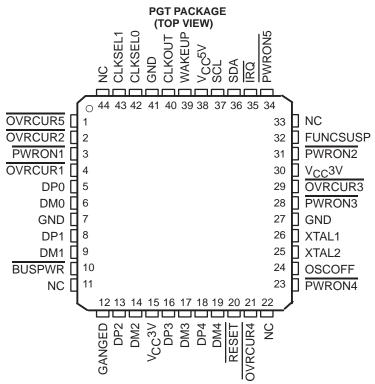

### 1.2 Terminal Assignments

NC - No internal connection

### 1.3 Terminal Functions

| TE        | RMINAL           |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------|------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | PGT<br>NO.       | N<br>NO.          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                       |  |

| BUSPWR    | 10               | 15                | I   | Port power indicator. BUSPWR is an active low input that indicates whether the ports and the hub source power from the USB bus or are self-powered by the local power supply. When a microcontroller is connected to the TUSB2140B, the hub must be self-powered and it is mandatory for this pin to be connected to 3.3 V. This standard TTL input must not change dynamically during operation. |  |

| CLKOUT    | 40               | 2                 | 0   | Clock output. Depending on the configuration of CLKSEL0 and CLKSEL1, CLKOUT is a selected clock output of 12 MHz, 8 MHz, 6 MHz, or 4 MHz.                                                                                                                                                                                                                                                         |  |

| DM1 – DM4 | 9, 14,<br>17, 19 | 14, 18,<br>21, 23 | I/O | Data minus USB differential data pairs. DM1 – DM4 support up to fou negative-signal downstream USB ports.                                                                                                                                                                                                                                                                                         |  |

| DP1 – DP4 | 8, 13,<br>16, 18 | 13, 17,<br>20, 22 | I/O | Data plus USB differential data pairs. DP1 – DP4 support up to four positive-signal downstream USB ports.                                                                                                                                                                                                                                                                                         |  |

| DM0       | 6                | 11                | I/O | Data minus USB differential data. DM0 is used for the upstream USB port cable pair and negative signal.                                                                                                                                                                                                                                                                                           |  |

| DP0       | 5                | 10                | I/O | Data plus USB differential data. DP0 is used for the upstream USB port cable pair and positive signal.                                                                                                                                                                                                                                                                                            |  |

# 1.3 Terminal Functions (continued)

| TE                   | ERMINAL                 |                         | Ì   |                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------|-------------------------|-------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                 | PGT<br>NO.              | N<br>NO.                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |  |  |

| FUNCSUSP             | 32                      | 35                      | 0   | Function port suspend. FUNCSUSP is an active high output that indicates if the port that connects to the embedded function has been selectively suspended. See <i>Suspend and Remote Wake-Up</i> in section 4.3.6 for further information.                                                                                               |  |  |

| GANGED               | 12                      | 16                      | I   | Power switch/over-current detection mode select. GANGED selects between gang or per port switching for over-current detection of the downstream ports. This pin should be set dependent upon how the external power management devices are configured. This standard TTL input must not change dynamically during operation.             |  |  |

| GND                  | 7, 27,<br>41            | 3, 12,<br>30            |     | Ground. All terminals must be tied to ground for proper operation.                                                                                                                                                                                                                                                                       |  |  |

| ĪRQ                  | 35                      | 37                      | 0   | Interrupt. IRQ is an active low output to the micro-controller that indicates an interrupt condition has occurred.                                                                                                                                                                                                                       |  |  |

| OSCOFF               | 24                      | 27                      | I   | Oscillator off. OSCOFF disables the internal oscillator for quiescent current draw (I <sub>CC</sub> Q) testing. OSCOFF must be tied low for normal operation.                                                                                                                                                                            |  |  |

| OVRCUR1 –<br>OVRCUR5 | 4, 2, 29,<br>21, 1      | 9, 7, 32,<br>25, 6      | I   | Over-current indicators. OVRCUR1 – OVRCUR5 are active low, standard TTL inputs. One over-current indicator is available for each of the four downstream ports. These inputs are internally gated when port power switching is ganged. The unused terminals must be tied high.                                                            |  |  |

| PWRON1 –<br>PWRON5   | 3, 31,<br>28, 23,<br>34 | 8, 34,<br>31, 26,<br>36 | 0   | Power on/off control switches. PWRON1 – PWRON5 are active low, open-drain outputs. One power on/off control switch is used for each of the four downstream ports. All outputs are switched together when the port power switching is ganged.                                                                                             |  |  |

| RESET                | 20                      | 24                      | I   | Reset. RESET is a TTL input with hysteresis and must be asserted power up for conformance to USB. RESET is an active low and must be asserted for at least 250 ns for all logic to be properly re-initialize However, asserting the RESET for longer than 5 ms could cause the TUSB2140B to NAK too long and be ignored by the USB host. |  |  |

| SCL                  | 37                      | 39                      | I   | Serial clock. SCL is the clock signal for the $I^2C$ serial interface and is 5-V tolerant.                                                                                                                                                                                                                                               |  |  |

| SDA                  | 36                      | 38                      | I/O | Serial data. SDA is the bidirectional data signal for the I <sup>2</sup> C serial interface and is 5-V tolerant. SDA uses an open-drain output driver.                                                                                                                                                                                   |  |  |

| VCC3V                | 15, 30                  | 19, 33                  |     | 3.3-V supply voltage                                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>CC</sub> 5V   | 38                      | 40                      |     | 5-V supply voltage                                                                                                                                                                                                                                                                                                                       |  |  |

| WAKEUP               | 39                      | 1                       | I   | Function port remote wake-up. WAKEUP is an active high input used by the micro-controller to initiate a remote wake-up from a suspended mode. WAKEUP is 5-V tolerant. See <i>Suspend and Remote Wake-Up</i> in section 4.3.6 for further information.                                                                                    |  |  |

| XTAL1                | 26                      | 29                      | I   | Crystal 1. XTAL1 is a 48-MHz clock input. Operation at 48-MHz is four times the USB full-speed bit rate of 12 Mbps.                                                                                                                                                                                                                      |  |  |

| XTAL2                | 25                      | 28                      | 0   | Crystal 2. XTAL2 is a 48-MHz feedback output for crystals and resonators. Operation at 48-MHz is four times the USB full-speed bit rate of 12 Mbps.                                                                                                                                                                                      |  |  |

| CLKSEL0,<br>CLKSEL1  | 42, 43                  | 4, 5                    | I   | Clock select inputs. CLKSEL0 and CLKSEL1 determine the CLKOUT frequency (See Table 4–2).                                                                                                                                                                                                                                                 |  |  |

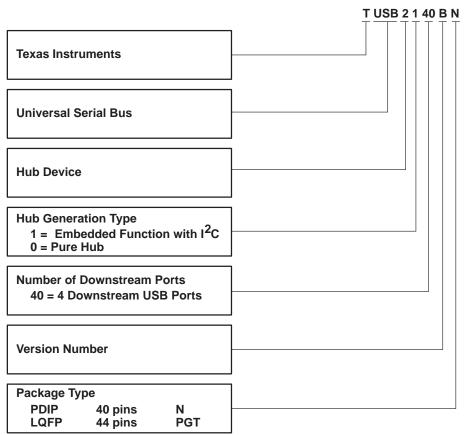

# 1.4 Device-Numbering Convention and Ordering Information

### 1.5 Related Documents Referenced

- Universal Serial Bus Specification version 1.0 dated January 19, 1996.

- Inter IC (I<sup>2</sup>C) Specification

# 2 Functional Description

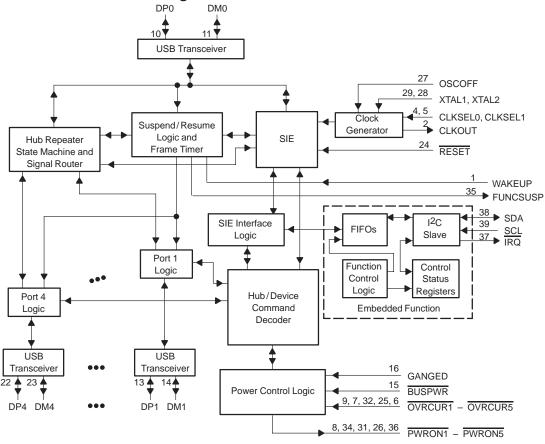

The functional block diagram for the TUSB2140B is shown in Section 2.1. The description for the function blocks follow Section 2.1. For additional information, including USB signaling specifications, packet protocol, and hub functionality, please refer to the Universal Serial Bus Specification version 1.0 dated January 19, 1996.

### 2.1 Functional Block Diagram

NOTE A: Terminal numbers shown are for the N package

### 2.2 USB Transceiver

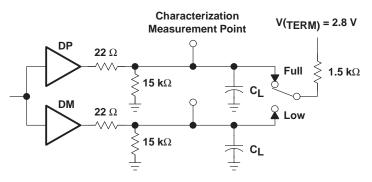

The TUSB2140B provides integrated transceivers for all the USB ports. The transceivers include a differential output driver, a differential input receiver and two single ended inputs. The transceiver for each port connects to the appropriate DP and DM differential signal pair.

#### 2.3 Clock Generator

Utilizing the 48-MHz input signal, the clock generator logic generates the CLKOUT output signal in addition to the various internal clock signals. The TUSB2140B internal clocks consist of the 48-MHz clock, a 12-MHz clock, and a USB clock. The USB clock also has a frequency of 12-MHz. The USB clock is the same as the 12-MHz clock when the TUSB2140B is transmitting data and is derived from the data when the TUSB2140B is receiving data.

### 2.4 Serial Interface Engine (SIE)

The serial interface engine logic manages the USB packet protocol requirements for the packets being received and transmitted by the TUSB2140B. For packets being received, the SIE decodes the packet identifier field (PID) to determine the type of packet being received and ensures the PID is valid. For token packets and data packets being received, the SIE calculates the packet CRC and compares the value to the CRC contained in the packet to verify that the packet was not corrupted during transmission. For token packets and data packets being transmitted, the SIE generates the CRC that is transmitted with the packet. For packets being transmitted, the SIE also generates the synchronization field (SYNC) which is the eight bit field at the beginning of each packet. In addition, the SIE generates the correct PID for all packets being transmitted. Another major function of the SIE is the overall serial-to-parallel conversion of the data packets being received and the parallel-to-serial conversion of the data packets being transmitted.

### 2.5 SIE Interface Logic

The SIE interface logic provides the control logic that interfaces the SIE to the hub control logic and the embedded function control logic. One of the major functions of the SIE interface logic is to decode the function address from the SIE to determine if either the hub or embedded function is being addressed. In addition, the endpoint address field is decoded to determine which particular endpoint of the hub or embedded function is being addressed. The SIE interface logic also managers the multiplexing of the byte-wide transmit data signals and other control signals from the hub control logic and embedded function control logic.

#### 2.6 Hub Command Decoder

The hub command decoder logic manages the overall control of the hub including the decode and execution of host initiated control commands, as well as the status change endpoint. During USB interrupt transfers, the USB host uses the status change endpoint to acquire hub status and port status change information.

#### 2.7 Frame Timer

The frame timer logic generates the end of frame (EOF) signal which is used mainly to ensure that all downstream traffic is completed during each frame period. In addition, since the frame timer counts 1.0 ms periods, the EOF signal is used by other logic that needs to time events based on multiples of 1.0 ms periods. The hub frame timer logic is locked to the host frame timer logic by the host generated Start of Frame (SOF) packets.

### 2.8 Suspend/Resume Logic

The suspend/resume logic is used to detect the suspend/resume states and to generate the signals used to control the overall device during the suspend/resume states. See *Suspend and Remote Wake-Up* in section 4.3.6 for further information.

### 2.9 Hub Repeater

The hub repeater logic manages the connectivity of the root port and the downstream ports on a per-packet basis. The data flow of the USB packets through the TUSB2140B from the root port to the downstream ports and vice-a-versa is totally asynchronous.

### 2.10 Port Logic

The port logic manages the overall state of a particular downstream port. Each downstream port has unique port logic which controls the connect/disconnect, enable/disable, suspend/resume and reset states of the port.

### 2.11 Power Control Logic

The power control logic generates the PWRON1 thru PWRON5 output signals based on the GANGED, BUSPWR, and OVRCUR input signals.

### 2.12 Embedded Function Control Logic

The Function control logic (FCL) manages communication between the local microcontroller Unit (MCU) and the Serial interface engine (SIE). The local MCU directs the operation of the FCL through the control and status registers. One of the major functions performed by the FCL is to move data to and from the internal FIFOs during the control and interrupt endpoint transfer operations.

### 2.13 Embedded Function Control/Status Registers

The control and status registers allow the local MCU to control and monitor transfer operations done by the TUSB2140B. A separate set of registers is used to control the transmit and receive operations for the control endpoint which is endpoint 0. In addition, a separate set of registers is provided for the interrupt endpoint transmit operations, which is endpoint 1. Also, an interrupt and interrupt mask register is provided to control the conditions that generate the IRQ output signal.

### 2.14 Embedded Function FIFOs

The TUSB2140B internal FIFOs provide a buffer between the SIE and the local MCU. There are three 8-byte by 8-bit FIFOs provided. There is a separate transmit and receive FIFO provided for the control endpoint, which is endpoint 0. In addition, there is a transmit FIFO provided for the interrupt endpoint, which is endpoint 1.

### 2.15 Embedded Function I<sup>2</sup>C Interface

The I<sup>2</sup>C Interface logic provides a two-wire serial interface that is used by a local MCU or device needing serial access to the TUSB2140B control/status registers and FIFOs. The interface allows single byte read and writes to the registers and multiple byte read and writes to the FIFOs. Note that the transmit FIFOs are write only and the receive FIFOs are read only from the local MCU side.

# 3 Internal Registers

The TUSB2140B provides a set of control and status registers to be used by the local microcontroller unit to control the overall operation of the embedded function. The control and status registers allow the local MCU to control and monitor USB transfers to both the control endpoint and the interrupt endpoint of the embedded function. There is a separate set of registers provided for the control endpoint transmit and receive operations. In addition, there is a separate set of registers provided for the transmit operations of the interrupt endpoint. Also, an interrupt and interrupt mask register is provided to control the conditions that generate the IRQ output signal.

3.1 Address Map

| ADDRESS  |         | _       |         |         |         |         | _      |        |                                    |

|----------|---------|---------|---------|---------|---------|---------|--------|--------|------------------------------------|

|          | 7       | 9       | 5       | 4       | 3       | 2       | 1      | 0      | NAME                               |

| 00h      |         |         |         | FSUSP   | FRST    | EP1TX   | EPORX  | EPOTX  | Interrupt Register                 |

| 01h      |         |         |         | FSUSP   | FRST    | EP1TX   | EP0RX  | EP0TX  | Interrupt Mask Register            |

| 02h FE   | HEN     | FA6     | FA5     | FA4     | FA3     | FA2     | FA1    | FA0    | Function Address Register          |

| 03h      |         |         |         |         |         |         |        |        |                                    |

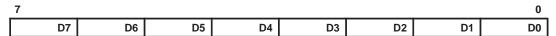

| 04h D7   | _       | 9Q      | D5      | D4      | D3      | D2      | D1     | 00     | EP0 TX FIFO                        |

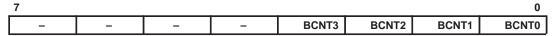

| 05h      |         |         |         |         | BCNT3   | BCNT2   | BCNT1  | BCNT0  | EP0 TX Byte Count Register         |

| 06h T    | TXCLR   |         |         |         | TXSTL   |         | TXFEN  | TXEN   | EP0 TX Control Register            |

| (T 470   | TXSEQ   |         |         | STSGE   | STALL   | NACK    | ERROR  | ACK    | EP0 TX Status Register             |

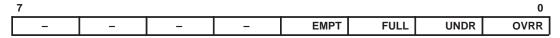

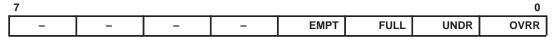

| 08h      |         |         |         |         | EMPT    | FULL    | UNDR   | OVRR   | EP0 TX FIFO Flags Register         |

| 09h D7   | _       | D6      | D5      | D4      | D3      | D2      | D1     | 00     | EP0 RX FIFO                        |

| 0Ah      |         |         |         |         | BCNT3   | BCNT2   | BCNT1  | BCNT0  | EP0 RX Byte Count Register         |

| OBh R3   | RXCLR   |         |         |         | RXSTL   |         | RXFEN  | RXEN   | EP0 RX Control Register            |

| OCh R    | RXSEQ   | SETUP   | RXFSW   | STSGE   | STALL   | NACK    | ERROR  | ACK    | EP0 RX Status Register             |

| 0Dh      |         |         |         |         | EMPT    | FULL    | UNDR   | OVRR   | EP0 RX FIFO Flags Register         |

| 0Eh      |         |         |         |         |         |         |        |        |                                    |

| 0Fh      |         |         |         |         |         |         |        |        |                                    |

| 10h D7   |         | 90      | D5      | D4      | D3      | D2      | D1     | 00     | EP1 TX FIFO                        |

| 11h      |         |         |         |         | BCNT3   | BCNT2   | BCNT1  | BCNT0  | EP1 TX Byte Count Register         |

| 12h T    | TXCLR   | TXSOW   |         |         | TXSTL   |         | TXFEN  | TXEN   | EP1 TX Control Register            |

| 13h   T> | TXSEQ   |         |         |         | STALL   | NACK    | ERROR  | ACK    | EP1 TX Status Register             |

| 14h      |         |         |         |         | EMPT    | FULL    | UNDR   | OVRR   | EP1 TX FIFO Flags Register         |

| 15h PI   | PID(7)  | PID(6)  | PID(5)  | PID(4)  | PID(3)  | PID(2)  | PID(1) | PID(0) | Hub Product ID, Low Byte Register  |

| 16h PI   | PID(15) | PID(14) | PID(13) | PID(12) | PID(11) | PID(10) | PID(9) | PID(8) | Hub Product ID, High Byte Register |

| 17h VI   | VID(7)  | (9) OIA | VID(5)  | VID(4)  | VID(3)  | VID(2)  | VID(1) | (0)QIA | Hub Vendor ID, Low Byte Register   |

| 18h   VI | VID(15) | VID(14) | VID(13) | VID(12) | VID(11) | VID(10) | (6)QIA | VID(8) | Hub Vendor ID, High Byte Register  |

| 19h      |         |         |         |         |         |         |        |        |                                    |

LSB 0 7 က 4 3.1 Address Map (continued)

ADDRESS MSB 6 5 14h 16h 16h 17h 17h

### 3.2 Register Functional Description

The following sections contain the functional descriptions for each register and the individual register bits. Note that firmware should write a 0 to reserved bits and ignore any value read from reserved bits.

### 3.2.1 Interrupt Register

The interrupt register bits are used to indicate when an interrupt condition is pending. If one or more of the interrupt bits are set, the TUSB2140B interrupt output signal (IRQ) will be asserted until the interrupt condition(s) is cleared. One or more of the interrupt bits can be masked by setting the corresponding bit in the interrupt mask register. If the interrupt mask bit is set, the corresponding interrupt bit will still be set when an interrupt condition occurs. However, the IRQ output signal will not be asserted. This feature is provided for systems that detect pending interrupt conditions with a polling scheme rather than by monitoring the IRQ output signal.

| 7 |   |   |       |      |       |       | 0     |

|---|---|---|-------|------|-------|-------|-------|

| _ | _ | _ | FSUSP | FRST | EP1TX | EP0RX | EP0TX |

| BIT | MNEMONIC | NAME                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|----------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | -        | Reserved                         | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | FSUSP    | Function suspend                 | The function suspend interrupt bit is set in response to the hub suspend logic detecting a global suspend condition or a selective suspend condition for the embedded function. To enable the TUSB2140B to enter a low–power suspend state which includes disabling the clocks, this bit must be cleared by the local MCU. This bit is cleared by writing a 1 to this register. This bit is read/write and is cleared by power-on reset.                                                                                                                                          |

| 3   | FRST     | Function reset                   | The function reset interrupt bit is set in response to the host initiating a port reset on the function port. To enable the function reset, this bit must be cleared by the local MCU. When a function reset occurs, all of the Function Interface logic within the TUSB2140B will be reset except the endpoint 0 receive enable bit (RXEN), the endpoint 0 transmit enable bit (TXEN), the function reset interrupt bit (FRST) and all of the interrupt mask bits. This bit is cleared by writing a 1 to this register. This bit is read/write and is cleared by power-on reset. |

| 2   | EP1TX    | Endpoint 1<br>transmit interrupt | The endpoint 1 transmit interrupt bit is set in response to the endpoint 1 transmit acknowledge status bit (ACK), the endpoint 1 transmit FIFO over-run flag bit (OVRR), or the endpoint 1 transmit FIFO under-run flag bit (UNDR) being set. This bit is cleared by clearing the corresponding status or FIFO flag bit that caused the interrupt. This bit is read-only and is cleared by power-on reset.                                                                                                                                                                        |

| 1   | EPORX    | Endpoint 0 receive interrupt     | The endpoint 0 receive interrupt bit is set in response to the endpoint 0 receive acknowledge status bit (ACK), the endpoint 0 receive FIFO over-run flag bit (OVRR), or the endpoint 0 receive FIFO under-run flag bit (UNDR) being set. This bit is cleared by clearing the corresponding status or FIFO flag bit that caused the interrupt. This bit is read-only and is cleared by power-on reset.                                                                                                                                                                            |

| 0   | EPOTX    | Endpoint 0<br>transmit interrupt | The endpoint 0 transmit interrupt bit is set in response to the endpoint 0 transmit acknowledge status bit (ACK), the endpoint 0 transmit FIFO over-run flag bit (OVRR), or the endpoint 0 transmit FIFO under-run flag bit (UNDR) being set. This bit is cleared by clearing the corresponding status or FIFO flag bit that caused the interrupt. This bit is read-only and is cleared by power-on reset.                                                                                                                                                                        |

# 3.2.2 Interrupt Mask Register

The interrupt mask register bits are used to mask the corresponding interrupt bits.

| 7 |   |   |       |      |       |       | 0     |

|---|---|---|-------|------|-------|-------|-------|

| - | _ | - | FSUSP | FRST | EP1TX | EP0RX | EP0TX |

| BIT | MNEMONIC | NAME                               | DESCRIPTION                                                                                                                                                 |

|-----|----------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | -        | Reserved                           | Reserved for future use                                                                                                                                     |

| 4   | FSUSP    | Function suspend interrupt mask    | The function suspend interrupt mask bit is set to enable the function suspend interrupt bit. This bit is read/write and is cleared by power–on reset.       |

| 3   | FRST     | Function reset interrupt mask      | The function reset interrupt mask bit is set to enable the function reset interrupt bit. This bit is read/write and is cleared by power-on reset.           |

| 2   | EP1TX    | Endpoint 1 transmit interrupt mask | The endpoint 1 transmit interrupt mask bit is set to enable the endpoint 1 transmit interrupt bit. This bit is read/write and is cleared by power-on reset. |

| 1   | EP0RX    | Endpoint 0 receive interrupt mask  | The endpoint 0 receive interrupt mask bit is set to enable the endpoint 0 receive interrupt bit. This bit is read/write and is cleared by power-on reset.   |

| 0   | EPOTX    | Endpoint 0 transmit interrupt mask | The endpoint 0 transmit interrupt mask bit is set to enable the endpoint 0 transmit interrupt bit. This bit is read/write and is cleared by power-on reset. |

## 3.2.3 Function Address Register

The function address register contains the current setting of the USB device address assigned to the function. During enumeration of the function, the function address is loaded into this register automatically by the TUSB2140B Function Control Logic when a Set Address request is received from the USB host. This register is read only and is used only for diagnostic purposes.

| 7   |     |     |     |     |     |     | 0   |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| FEN | FA6 | FA5 | FA4 | FA3 | FA2 | FA1 | FA0 |  |

| BIT | MNEMONIC | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | FEN      | Function enabled | The function enabled bit is set when the embedded function port has been enabled by the host with a set port feature request. This bit is read-only and is cleared by power-on reset.                                                                                                                                                                                                                                       |

| 6:0 | FA(6:0)  | Function address | The function address register value is set to the current device address assigned to the function. These bits are read/write-able and are cleared by power-on reset. The function address is updated when the MCU receives a set-address control transfer for the embedded function from the host. The MCU will then update the function address from the micro-controller firmware through the I <sup>2</sup> C interface. |

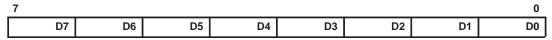

# 3.2.4 Endpoint 0 Transmit FIFO

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| BIT | MNEMONIC | NAME                  | DESCRIPTION                                                                                                       |

|-----|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| 7:0 | D(7:0)   | Transmit<br>FIFO data | Endpoint 0 transmit FIFO data is written to the transmit FIFO on a byte-to-byte basis. These bits are write-only. |

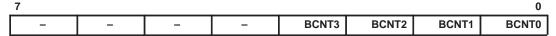

# 3.2.5 Endpoint 0 Transmit Byte Count Register

| 7 |   |   |   |       |       |       | 0     |

|---|---|---|---|-------|-------|-------|-------|

| _ | _ | _ | _ | BCNT3 | BCNT2 | BCNT1 | BCNT0 |

| BIT | MNEMONIC  | NAME                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | _         | Reserved               | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3:0 | BCNT(3:0) | Transmit<br>byte count | The transmit byte count register should be loaded with the number of bytes to be transmitted. The byte count should be the number of bytes in the data packet that was loaded into the transmit FIFO. When the local MCU writes to the byte count register, the EPO transmit FIFO enable bit (TXFEN) will automatically be set. Also, the byte count register does not decrement as data is transmitted. These bits are read/write and are cleared by power-on reset. |

# 3.2.6 Endpoint 0 Transmit Control Register

The transmit control register is used to store bits which control various functions and operating modes of the function interface logic within the TUSB2140B.

| 7     |   |   |   |       |   |       | 0    |

|-------|---|---|---|-------|---|-------|------|

| TXCLR | _ | _ | - | TXSTL | - | TXFEN | TXEN |

| BIT | MNEMONIC | NAME                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-----|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | TXCLR    | Transmit<br>clear          | The transmit clear bit is set to reset the transmit FIFO pointers and flags. This bit should be set in response to a transmit FIFO over—run or under-run condition. After the FIFO pointers are reset, this bit will be automatically cleared. In addition, the FIFO empty flag will be set and the other FIFO flags will be cleared upon completion of the FIFO reset. This bit is read/write and is cleared by power-on reset.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 6   | -        | Reserved                   | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 5   | _        | Reserved                   | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 4   | _        | Reserved                   | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 3   | TXSTL    | Transmit<br>stall          | The transmit stall bit is set to enable a STALL handshake to be returned in response to the next valid In Transaction. This bit is automatically cleared if a new Setup Stage Transaction is successfully received. This bit is read/write and is cleared by power-on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 2   | _        | Reserved                   | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 1   | TXFEN    | Transmit<br>FIFO<br>enable | The transmit FIFO enable bit is set to enable the transmission of data in the transmit FIFO when the next valid in transaction occurs. This bit is automatically set when the local MCU writes to the EP0 transmit byte count register and is automatically cleared when the EP0 transmit acknowledge status bit (ACK) is set. This bit is also automatically cleared if a new setup stage transaction is successfully received or the EP0 transmit clear bit (TXCLR) is set. If the transmit enable bit is not set, the device returns a NACK handshake. If the transmit stall control bit (TXSTL) is set, a STALL handshake is returned instead of a NACK handshake. This bit is read/write and is cleared by power-on reset. |  |  |  |  |

| 0   | TXEN     | Transmit<br>enable         | The transmit enable bit is set to enable the transmit endpoint. For endpoint 0, the control endpoint, both a receive and transmit endpoint are required. Therefore, the transmit enable and receive enable bits must both be set before the device will be enumerated. If either of these bits is not set, the function port will remain in the disconnected state. This bit is read/write and is cleared by power-on reset.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

# 3.2.7 Endpoint 0 Transmit Status Register

The transmit status register is used to store bits which report status information about the operating conditions of the function control logic within the TUSB2140B.

| 7     |   |   |       |       |      |       | 0   |

|-------|---|---|-------|-------|------|-------|-----|

| TXSEQ | _ | - | STSGE | STALL | NACK | ERROR | ACK |

| BIT   | MNEMONIC | NAME                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | TXSEQ    | Transmit<br>sequence | The transmit sequence bit value determines the data packet PID to be used for the next data packet to be transmitted for the next In data stage transaction. This bit is automatically set at the end of a successful setup stage transaction and is automatically toggled at the end of each successful in data stage transaction. If this bit is a 0, a DATA0 PID is sent in the data packet. If this bit is a 1, a DATA1 PID is sent in the data packet. This bit is read only and is cleared by power-on reset.              |

| 6     | _        | Reserved             | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5     | _        | Reserved             | Reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4     | STSGE    | In status stage      | The in status stage bit is set when the function control logic detects the status stage transaction of a control transfer. This bit will be automatically cleared at the beginning of the next setup stage transaction. This bit is read-only and is cleared by power-on reset.                                                                                                                                                                                                                                                  |