查询UCC3946供应商

UCC1946 UCC2946 UCC3946

# Microprocessor Supervisor with Watchdog Timer FEATURES DESCRIPTION

- Fully Programmable Reset Threshold

- Fully Programmable Reset Period

JNITRODE

- Fully Programmable Watchdog Period

- 2% Accurate Reset Threshold

- VDD Can Go as Low as 2V

- 18μA Maximum IDD

- Reset Valid Down to 1V

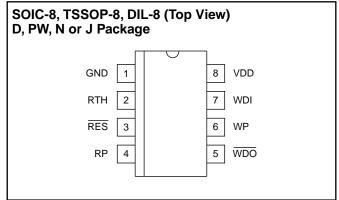

The UCC3946 is designed to provide accurate microprocessor supervision, including reset and watchdog functions. During power up, the IC asserts a reset signal RES with VDD as low as 1V. The reset signal remains asserted until the VDD voltage rises and remains above the reset threshold for the reset period. Both reset threshold and reset period are programmable by the user. The IC is also resistant to glitches on the VDD line. Once RES has been deasserted, any drops below the threshold voltage need to be of certain time duration and voltage magnitude to generate a reset signal. These values are shown in Figure 1. An I/O line of the microprocessor may be tied to the watchdog input (WDI) for watchdog functions. If the I/O line is not toggled within a set watchdog period, programmable by the user, WDO will be asserted. The watchdog function will be disabled during reset conditions.

The UCC3946 is available in 8-pin SOIC(D), 8-pin DIP (N or J) and 8-pin TSSOP(PW) packages to optimize board space.

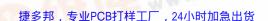

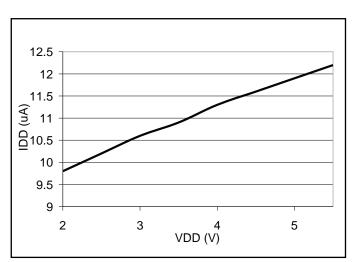

# BLOCK DIAGRAM

# **ABSOLUTE MAXIMUM RATINGS**

| VIN                                         |  |

|---------------------------------------------|--|

| Storage Temperature65°C to +150°C           |  |

| Junction Temperature55°C to +150°C          |  |

| Lead Temperature (Soldering, 10 sec.)+300°C |  |

Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the Databook for thermal limitations and considerations of packages.

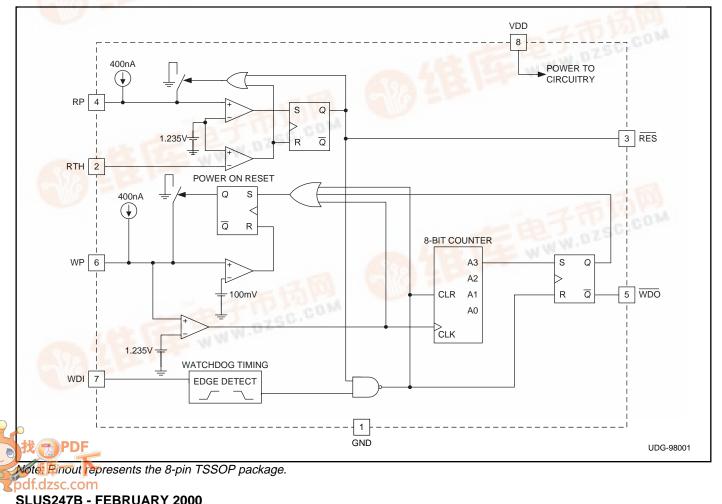

# **CONNECTION DIAGRAM**

**ELECTRICAL CHARACTERISTICS:** Unless otherwise specified, VDD = 2.1V to 5.5V for UCC1946 and UCC2946; VDD = 2V to 5.5V for UCC3946; TA =  $0^{\circ}$ C to  $70^{\circ}$ C for UCC3946,  $-40^{\circ}$ C to  $95^{\circ}$ C for UCC2946, and  $-55^{\circ}$ C to  $125^{\circ}$ C for UCC1946; TA = T<sub>J</sub>

| PARAMETERS           | TEST CONDITIONS             | MIN         | TYP     | MAX         | MIN          | TYP               | MAX         | UNITS |  |

|----------------------|-----------------------------|-------------|---------|-------------|--------------|-------------------|-------------|-------|--|

|                      |                             | ι           | UCC3946 |             |              | UCC1946 & UCC2946 |             |       |  |

| Operating Voltage    |                             | 2.0         |         | 5.5         | 2.1          |                   | 5.5         | V     |  |

| Supply Current       |                             |             | 10      | 18          |              | 12                | 18          | μA    |  |

| Minimum VDD          | (Note 1)                    |             |         | 1           |              |                   | 1.1         | V     |  |

| Reset Section        |                             |             |         |             |              |                   |             |       |  |

| Reset Threshold      | VDD Rising                  | 1.210       | 1.235   | 1.260       | 1.170        | 1.235             | 1.260       | V     |  |

| Threshold Hysteresis |                             |             | 15      |             |              | 15                |             | mV    |  |

| Input Leakage        |                             |             |         | 5           |              |                   | 5           | nA    |  |

| Output High Voltage  | ISOURCE = 2mA               | Vdd - 0.3   |         |             | Vdd –<br>0.3 |                   |             | V     |  |

| Output Low Voltage   | ISINK = 2mA                 |             |         | 0.1         |              |                   | 0.1         | V     |  |

|                      | VDD = 1V, ISINK = 20uA      |             |         | 0.2         |              |                   | 0.4         | V     |  |

| VDD to Output Delay  | $VDD = -1mV/\mu s$ (Note 2) |             | 120     |             |              | 120               |             | μs    |  |

| Reset Period         | CRP = 64nF                  | 160         | 200     | 260         | 140          | 200               | 320         | ms    |  |

| Watchdog Section     |                             |             |         |             |              |                   |             |       |  |

| WDI Input High       |                             | 0.7•<br>Vdd |         |             | 0.7.<br>Vdd  |                   |             | V     |  |

| WDI Input Low        |                             |             |         | 0.3.<br>Vdd |              |                   | 0.3.<br>Vdd | V     |  |

| Watchdog Period      | CWP = 64nF                  | 1.12        | 1.60    | 2.08        | 0.96         | 1.60              | 2.56        | s     |  |

| Watchdog Pulse Width |                             | 50          |         |             | 50           |                   |             | ns    |  |

| Output High Voltage  | ISOURCE = 2mA               | Vdd - 0.3   |         |             | Vdd -<br>0.3 |                   |             | V     |  |

| Output Low Voltage   | Isinк = 2mA                 |             |         | 0.1         |              |                   | 0.1         | V     |  |

Note 1: This is the minimum supply voltage where  $\overline{\text{RES}}$  is considered valid. Note 2: Guaranteed by design. Not 100% tested in production.

# **PIN DESCRIPTIONS**

GND: Ground reference for the IC.

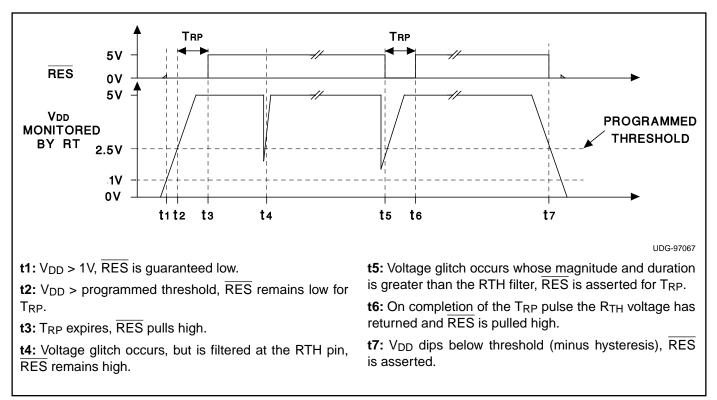

**RES:** This pin is high only if the voltage on the RTH has risen above 1.235V. Once RTH rises above the threshold, this pin remains low for the reset period. This pin will also go low and remain low if the RTH voltage dips below 1.235V for an amount of time determined by Figure 1.

**RTH:** This input compares its voltage to an internal 1.25V reference. By using external resistors, a user can program any reset threshold he wishes to achieve.

**RP:** This pin allows the user to program the reset period by adjusting an external capacitor.

VDD: Supply voltage for the IC.

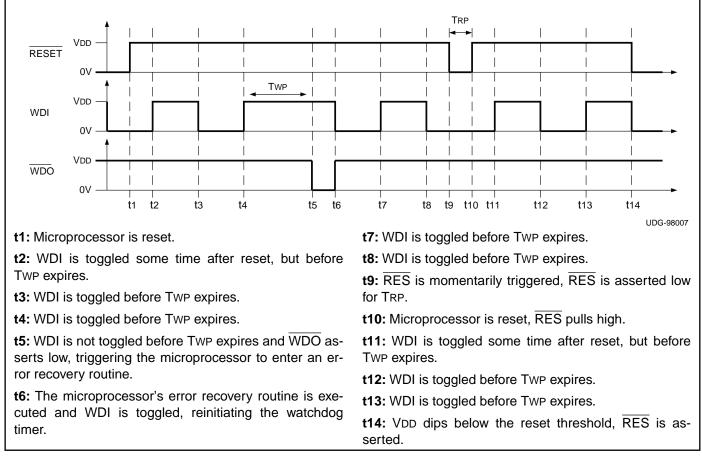

**WDI:** This pin is the input to the watchdog timer. If this pin is not toggled or strobed within the watchdog period, WDO is asserted.

**WDO:** This pin is the watchdog output. This pin will be asserted low if the WDI pin is not strobed or toggled within the watchdog period.

**WP:** This pin allows the user to program the watchdog period by adjusting an external capacitor.

# **APPLICATION INFORMATION**

The UCC3946 supervisory circuit provides accurate reset and watchdog functions for a variety of microprocessor applications. The reset circuit prevents the microprocessor from executing code during undervoltage conditions, typically during power-up and power-down. In order to prevent erratic operation in the presence of noise, voltage "glitches" whose voltage amplitude and time duration are less than the values specified in Fig. 1 are ignored.

The watchdog circuit monitors the microprocessor's activity, if the microprocessor does not toggle WDI during the programmable watchdog period  $\overline{WDO}$  will go low, alerting the microprocessor's interrupt of a fault. The  $\overline{WDO}$  pin is typically connected to the non-maskable input of the microprocessor so that an error recovery routine can be executed.

Figure 1. Overdrive voltage vs. delay to output low on RESB.

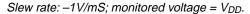

Figure 2. Typical RTH threshold vs. temperature.

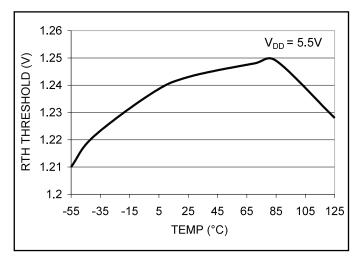

Figure 3. Typical IDD vs VDD.

# **APPLICATION INFORMATION (cont.)**

Figure 4. Typical application diagram.

### Programming the Reset Voltage and Reset Period

The UCC3946 allows the reset trip voltage to be programmed with two external resistors. In most applications VDD is monitored by the reset circuit, however, the design allows voltages other than VDD to be monitored. Referring to Fig. 4, the voltage below which reset will be asserted is determined by:

$$V_{RESET} = 1.235 \bullet \frac{R1 + R2}{R2}$$

In order to keep quiescent currents low, resistor values in the megaohm range can be used for R1 and R2. A manual reset can be easily implemented by connecting a momentary push switch in parallel with R2. RES is guaranteed to be low with VDD voltages as low as 1V.

Once VDD rises above the programmed threshold,  $\overline{\text{RES}}$  remains low for the reset period defined by:

TRP = 3.125 • CRP

where TRP is time in milliseconds and CRP is capacitance in nanofarads. CRP is charged with a precision current source of 400nA, a high quality, low leakage capacitor (such as an NPO ceramic) should be used to maintain timing tolerances. Fig. 5 illustrates the voltage levels and timings associated with the reset circuit.

# **Programming the Watchdog Period**

The watchdog period is programmed with CWP as follows:

$$TWP = 25 \bullet CWP$$

where TWP is in milliseconds and CWP is in nanofarads. A high quality, low leakage capacitor should be used for CWP. The watchdog input WDI must be toggled with a high/low or low/high transition within the watchdog period to prevent WDO from assuming a logic level low. WDO will maintain the low logic level until WDI is toggled or RES is asserted. If at any time RES is asserted, WDO will assume a high logic state and the watchdog period will be reinitiated. Fig. 6 illustrates the timings associated with the watchdog circuit.

# **APPLICATION INFORMATION (cont.)**

# Connecting WDO to RES

In order to provide design flexibility, the reset and watchdog circuits in the UCC3946 have separate outputs. Each output will independently drive high or low, depending on circuit conditions explained previously.

In some applications, it may be desirable for either the  $\overline{\text{RES}}$  or  $\overline{\text{WDO}}$  to reset the microprocessor. This can be done by connecting  $\overline{\text{WDO}}$  to  $\overline{\text{RES}}$ . If the pins try to drive to different output levels, the low output level will dominate. Additional current will flow from VDD to GND during these states. If the application cannot support additional current (during fault conditions),  $\overline{\text{RES}}$  and  $\overline{\text{WDO}}$  can be connected to the inputs of an OR gate whose output is connected to the microprocessor's reset pin.

## Layout Considerations

A  $0.1\mu$ F capacitor connected from VDD to GND is recommended to decouple the UCC3946 from switching transients on the VDD supply rail.

Since RP and WP are precision current sources, capacitors CRP and CWP should be connected to these pins with minimal trace length to reduce board capacitance. Care should be taken to route any traces with high voltage potential or high speed digital signals away from these capacitors.

Resistors R1 and R2 generally have a high ohmic value, traces associated with these parts should be kept short in order to prevent any transient producing signals from coupling into the high impedance RTH pin.

Figure 5. Reset circuit timings.

# **APPLICATION INFORMATION (cont.)**

Figure 6. Watchdog circuit timings.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated