# MOS INTEGRATED CIRCUIT **μPD6453**

## CMOS LSI FOR 12 lines × 24 columns CHARACTER DISPLAY ON SCREEN

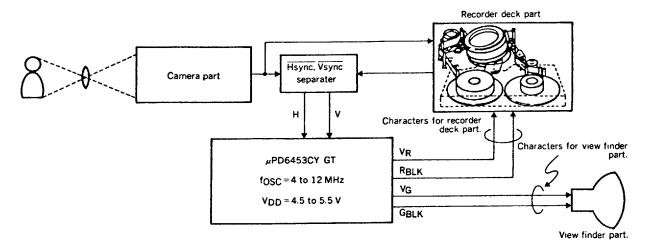

The µPD6453 is a CMOS LSI device for on-screen character displays designed to display characters such as the time of day, channel numbers, and chapter numbers on a TV screen when used in a TV or video disk in combination with a microcomputer. By using this IC in a video camera or VCR, the time of day and date can also be recorded over video signals.

Each character is in a 12 x 18 dot pattern and by combining two or more characters, Chinese characters (Kanji) or graphics may be displayed. By using a character RAM for 16 characters, a character or graphic pattern can be changed while it is being displayed.

In addition, thanks to its Power ON Reset function, Video RAM All Reset command and other built-in functions, the μPD6453 helps lighten a burden on the microcomputer.

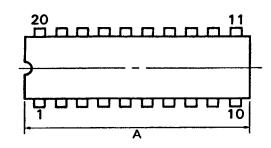

NEC offers two types of devices μPD6453CY-001 and μPD6453GT-101 as standard products. Both the μPD6453CY-001 and µPD6453GT-101 have the same character specifications, but the former is housed in a 20-pin plastic DIP (Dual In-line Package) and the latter in a 20-pin plastic SOP (Small Out-line Package).

### **FEATURES**

No. of Display Characters

Types of Characters

Character Size

Character Colors

Background

**Dot Matrix**

Smooth function

**Blinking Control**

Mask Pulse (Code Option)

Adaptability to Progressive Scan TV

Video RAM Data Clear

Interface with Microcomputer

Power Supply Construction

: 12 lines x 24 columns

256 types (ROM: 240 types; RAM: 16 types.)

: Any one of 1H, 2H, 3H, and 4H per dot can be selected.

: Any one of 8 different colors can be selectable for each character.

One of "No background", "Square background" and "Solid background" is selectable per screen, together with fringe ON/OFF function. Any of eight different colors is selectable as the background color and together with the fringe color (black or

white) selectable per screen.

: 12 x 18 pattern without spacing between characters

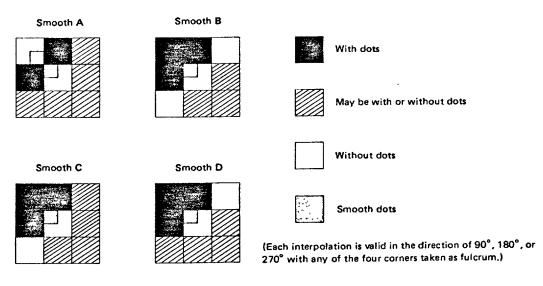

Two different interpolations are available for selection per line with characters two

to four times the normal size.

Blinking ON/OFF can be specified per character. The ON/OFF time ratio of blinking

is 1:1 with a blinking frequency selectable from among about 2 Hz, about 1 Hz, and

: To be output in vertical direction for each line.

Vertical and horizontal directions can be specified independently of each other.

Video RAM data can be reset with either the Video RAM All Clear command or the

Power ON Clear function.

Variable-length serial input format in units of 8 bits

+5 V single power supply

CMOS low power consumption

### **ORDERING INFORMATION**

| PART NUMBER   | PACKAGE                      | QUALITY GRADE |

|---------------|------------------------------|---------------|

| μPD6453CY-001 | 20-pin plastic DIP (400 mil) | Standard      |

| μPD6453GT-101 | 20-pin plastic SOP (375 mil) | Standard      |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number 1EI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

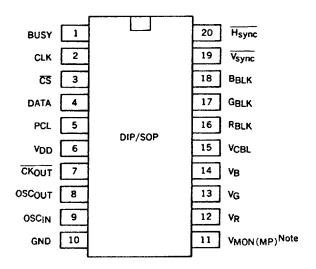

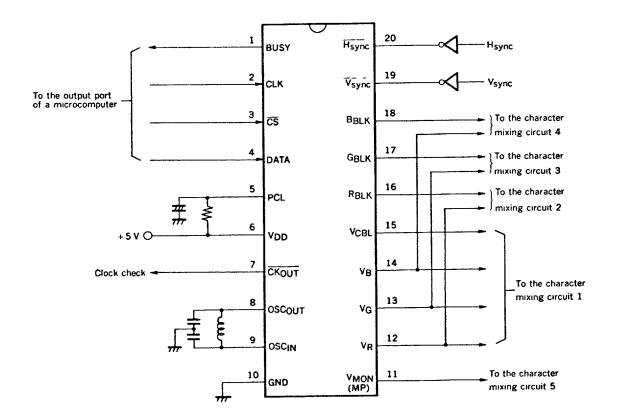

### **CONNECTION DIAGRAM (Top View)**

$\mu$ PD6453CY,  $\mu$ PD6453GT

Note: Pin 10 (μPD6453CY/μPD6453GT) within parentheses is the mask code option to be used as the mask pulse.

However, μPD6453CY-001/μPD6453GT-101 does not use the mask pulse, so pin 11 is used as monitor output VMON.

### PIN DESCRIPTION

| SYMBOL                                                   | PIN NAME                                     | FUNCTION                                                                                                                                                                                                                              |

|----------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>                                          | Power supply terminal                        | This terminal supplies +5 V power.                                                                                                                                                                                                    |

| V <sub>SS</sub>                                          | Grounding terminal                           | This is connected to the system GND.                                                                                                                                                                                                  |

| DATA                                                     | Serial data input terminal                   | This terminal inputs control data. It reads data synchronizing with the clock input to the CLK terminal.                                                                                                                              |

| CLK                                                      | Clock input terminal                         | This terminal inputs the clock for reading data. At the rise of this clock, the data input to the DATA terminal is read.                                                                                                              |

| CS                                                       | Chip select terminal                         | Normal operation is performed when this is Low.                                                                                                                                                                                       |

| OSC <sub>IN</sub><br>OSC <sub>OUT</sub>                  | Oscillation terminals                        | These terminals are connected to the oscillation capacitor or coil.                                                                                                                                                                   |

| H <sub>SYNC</sub>                                        | Horizontal synchronous signal input terminal | This terminal inputs the horizontal synchronizing signal.  The oscillator oscillates when this signal is high, synchronizing with the rise of the signal. Be sure to input the horizontal synchronizing signal when it is active low. |

| V <sub>SYNC</sub>                                        | Vertical synchronizing signal input terminal | This terminal inputs the vertical synchronizing signal. Be sure to input this signal when it is active low.                                                                                                                           |

| V <sub>R</sub><br>V <sub>G</sub><br>V <sub>B</sub>       | Character signal output terminals            | These terminals output the character signal corresponding to R, G, and B.                                                                                                                                                             |

| V <sub>BLK</sub>                                         | Blanking signal output terminal              | This terminal outputs the blanking signal to cut the video signal.                                                                                                                                                                    |

| R <sub>BLK</sub><br>G <sub>BLK</sub><br>B <sub>BLK</sub> | Blanking signal output terminal              | These terminals output the blanking signal which correspond to character signal ( $V_R$ , $V_G$ , $V_B$ ).                                                                                                                            |

| PCL                                                      | Power ON reset terminal                      | The state will be initialize by this terminal Low to High when Power is ON.                                                                                                                                                           |

| CK <sub>OUT</sub>                                        | Clock output terminal                        | This is the inverted output of OSC <sub>OUT</sub> . To connect another type of on-screen IC in parallel, be sure to connect this terminal to OSC <sub>IN</sub> of the IC.                                                             |

| BUSY                                                     | Data input enable terminal                   | Output terminal to notify the microcomputer that data is enabled or disabled for input. Data can be input at a low level.                                                                                                             |

| V <sub>MON</sub> Note                                    | Character signal output monitor terminal     | If any of character signal outputs $V_R$ , $V_G$ , and $V_B$ is High, the high-level signal is output.                                                                                                                                |

Note: The mask code option enables this terminal to be used as the mask pulse output terminal.

However, µPD6453CY-001/µPD6453GT-101 does not use the mask pulse, so pin 11 is used as monitor output VMON.

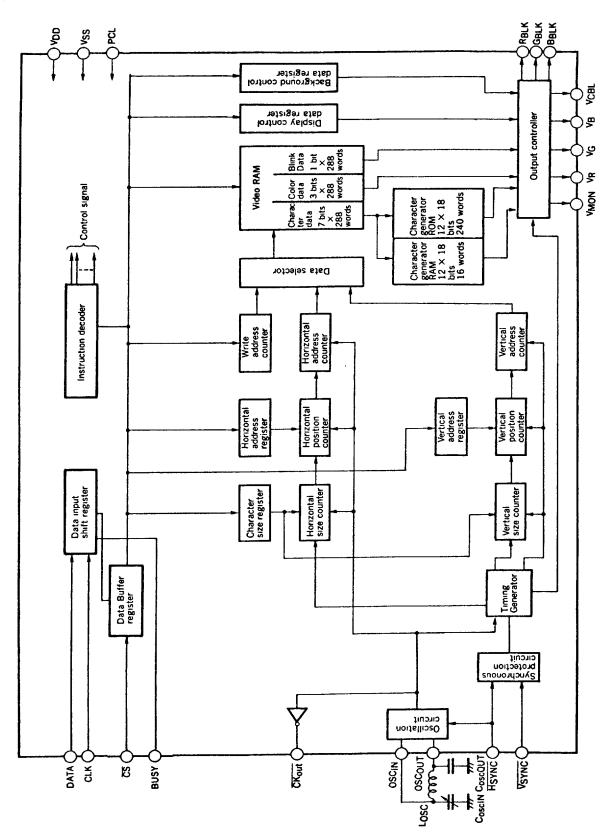

### **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C)

| Supply Voltage        | $V_{DD} - V_{SS}$ | 7.0                                     | V  |

|-----------------------|-------------------|-----------------------------------------|----|

| Înput Voltage         | VIN               | $V_{DD} + 0.3 > V_{IN} > V_{SS} - 0.3$  | V  |

| Output Voltage        | Vout              | $V_{DD} + 0.3 > V_{OUT} > V_{SS} - 0.3$ | V  |

| Output Current        | lo                | ±5                                      | mΑ |

| Operating Temperature | Topt              | -20 to +75                              | °C |

| Storage Temperature   | T <sub>stg</sub>  | -40 to +125                             | °C |

### RECOMMENDED OPERATING RANGE

| ITEM                  | SYMBOL                            | MIN. | TYP, | MAX. | UNIT |

|-----------------------|-----------------------------------|------|------|------|------|

| Supply Voltage        | V <sub>DD</sub> – V <sub>SS</sub> | 4.5  | 5.0  | 5.5  | V    |

| Oscillation Frequency | fosc                              | 4.0  | 7.0  | 12   | MHz  |

## ELECTRICAL CHARACTERISTICS $(T_a = 25 \, ^{\circ}\text{C}, V_{DD} = 5.0 \, \text{V}, V_{SS} = 0 \, \text{V})$

| CHARACTERISTIC                              | SYMBOL                            | MIN.     | TYP. | MAX. | UNIT | TEST CONDITION            |

|---------------------------------------------|-----------------------------------|----------|------|------|------|---------------------------|

| Supply Voltage                              | V <sub>DD</sub> - V <sub>SS</sub> | 4.5      | 5.0  | 5.5  | V    |                           |

| Current Consumption                         | IDD                               |          |      | 15   | mA   |                           |

| Control Input High Level Voltage            | VCIH                              | 2.4      |      |      | V    |                           |

| Control Input Low Level Voltage             | VCIL                              | 1        |      | 0.8  | V    |                           |

| Synchronous Signal Input High Level Voltage | VSIH                              | 2.4      |      |      | V    |                           |

| Synchronous Signal Input Low Level Voltage  | VSIL                              |          |      | 0.8  | V    |                           |

| Signal Output High Level Voltage            | Voн                               | 4.5      |      |      | V    | I <sub>OH</sub> = -1.0 mA |

| Signal Output Low Level Voltage             | VOL                               | 1        | 1    | 0.5  | V    | IOL = 1.0 mA              |

| Clock Output High Level Voltage             | Vскн                              | 4.5      |      |      | V    | ICKH = -0.5 mA            |

| Clock Output Low Level Voltage              | VCKL                              | <b>T</b> | 1    | 0.5  | V    | ICKL = 0.5 mA             |

Note: Control input . . . . . . . . . . . . . DATA, CLK, CS, PCL

### **COMMAND FORMATS**

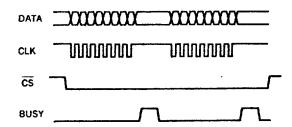

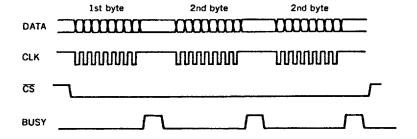

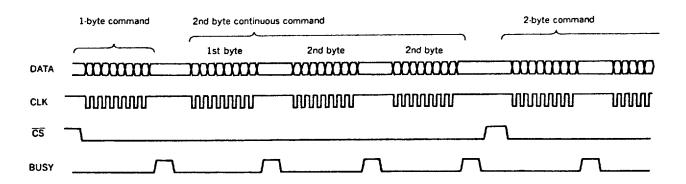

All control commands are in a variable-length serial input format in units of eight bits. These commands are available in three types: 1-byte (8-bit) command consisting of an instruction part and data; 2-byte (16-bit) command consisting of an instruction part and data and 2nd byte continuous command which consists of two or more bytes and can be input in an abbreviated format.

Each of these commands can be input while the  $\overline{CS}$  signal is in the Low (active) state and is followed by the BUSY signal on input of each 8-bit serial data. Please input datas from MSB.

### **Command Input Methods**

O To input one 1-byte command

CLK MMMM

CS

BUSY

O To input one 2-byte command

O To input one 2nd byte continuous command

The internal data processing is performed on input of every one byte (8 bits). (See the paragraph "Recommended Timing" on page 17 for  $\overline{\text{CS}}$  and BUSY.)

### **Method of Continuous Command Input**

A 1-byte command, a 2-byte command, or a 2nd byte continuous command can be input continuously either individually or in combination with the other commands while keeping the  $\overline{CS}$  signal in the Low state (without setting the signal to the High state for delimiting each command input) with the exception of the case indicated below.

### **Restriction on Continuous Command Input**

At the input of a 2nd byte continuous command, set the  $\overline{CS}$  signal to High (inactive) once and then to Low (active) and then enter the 1-byte or 2-byte command following the 2nd byte continuous command.

Example: Continuous input of 1-byte command, 2nd byte continuous command, and 2-byte command

### $\mu$ PD6453CY-XXX/ $\mu$ PD6453GT-XXX Command List

### 1. 1-byte command

| •                        | (MSB) |    |    |    |    |      |            |     |  |  |  |

|--------------------------|-------|----|----|----|----|------|------------|-----|--|--|--|

| Content                  | D7    | D6 | D5 | D4 | D3 | D2   | D1         | DO  |  |  |  |

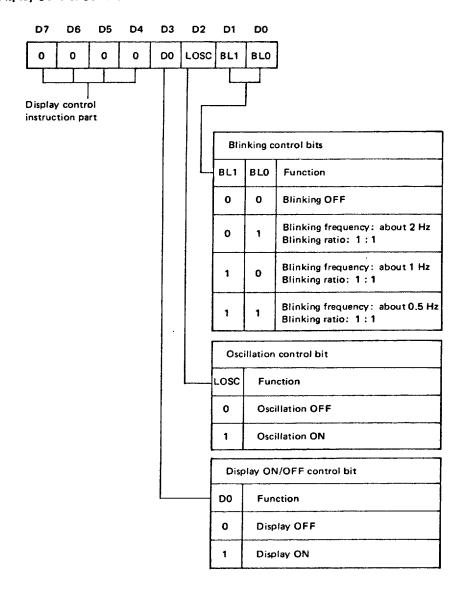

| Display control          | 0     | 0  | 0  | 0  | DO | LOSC | BL1        | BLO |  |  |  |

| Background control       | 0     | 1  | 0  | 0  | 0  | BS1  | B\$0       | Eg  |  |  |  |

| Background color control | 0     | 0  | 0  | 1  | Rb | Gь   | <b>B</b> b | Egc |  |  |  |

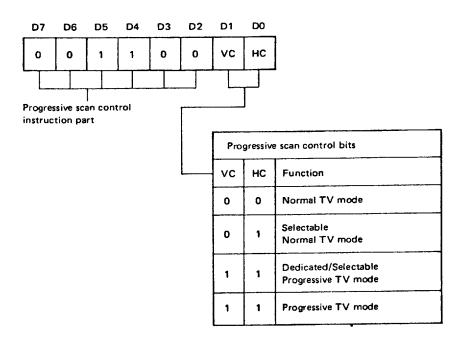

| Progressive scan control | 0     | 0  | 1  | 1  | 0  | 0    | VC         | нс  |  |  |  |

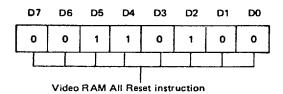

| Video RAM all reset      | 0     | 0  | 1  | 1  | 0  | 1    | 0          | 0   |  |  |  |

### 2. 2-byte command

| Content                                    | D15 | D14 | D13 | D12 | D11  | D10  | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  |

|--------------------------------------------|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Display position control                   | 1   | 0   | 0   | 0   | 0    | 0    | V4  | V3  | V2  | V1  | VO  | H4  | нз  | H2  | Н1  | НО  |

| Character write address control            | 1   | 0   | 0   | 0   | 0    | 1    | 0   | AR3 | AR2 | AR1 | AR0 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Character RAM write address control        | 1   | 0   | 0   | 0   | 0    | 1    | 1   | RW3 | RW2 | RW1 | RW0 | RL4 | RL3 | RL2 | RL1 | RL0 |

| Character size, smooth, mask pulse control | 1   | 0   | 0   | 0   | 1    | МР   | S1  | so  | o   | 0   | SM1 | SMO | AR3 | AR2 | AR1 | AR0 |

| Character RAM write data control           | 1   | 0   | 0   | 1   | CR11 | CR10 | CR9 | CR8 | CR7 | CR6 | CR5 | CR4 | CR3 | CR2 | CR1 | CRO |

| Test mode control: (don't use)             | 1   | 0   | 1   | 0   | 0    | 0    | 0   | 0   | T7  | Т6  | T5  | T4  | ТЗ  | T2  | T1  | TO  |

### 3. 2nd byte continuous command

|                           | ,   |     | ,   |     |     |     | <del></del> |       |    |    |    | r  |    |    |    |    | ı |

|---------------------------|-----|-----|-----|-----|-----|-----|-------------|-------|----|----|----|----|----|----|----|----|---|

| Content                   | D15 | D14 | D13 | D12 | D11 | D10 | D9          | D8    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | ı |

| Display character control | 1   | 1   | 0   | 0   | R   | G   | В           | Blink | C7 | C6 | C5 | C4 | C3 | C2 | C1 | CO | ı |

#### **POWER ON RESET**

At the time of power on, the internal states of this IC are indefinite (unknown). For this reason, be sure to perform the Power ON Reset operation to set the IC to the initialized states by turning the voltage level of the PCL pin from Low to High. The commands to be set by this Power ON Reset operation are as follows:

- The contents of the character RAM are all Reseted to "0" (without dot).

- The word address and line address values of the character RAM are initialized to the first word and first line, respectively.

- The Progressive scan Control command is initialized to "Normal TV mode" (VC bit, HC bit = 0, 0).

- O Test mode is released.

The time required for POWER ON RESET can be obtained from the following expression:

- t = tPCLL + Video RAM Reset time

- = 10 ( $\mu$ s) + 12/ $f_{osc}$  (MHz) x 288

- Video RAM related parameters are also initialized. For details, see the paragraph "Video RAM All Reset Command" below.

### Video RAM All Reset Command

When this command is executed, Display OFF, Losc Oscillation ON, and Video RAM Write mode are automatically set and these settings remain unchanged until execution of other commands even after the Video RAM All Reset command.

The commands to be set by the Video RAM All Reset command are as follows:

- O All the character data of the video RAM are Reseted to "EFH" (namely, they become display OFF data).

- The line and column address values of the video RAM are set to "0".

- The character color and blinking control specifications are set to "Black" and "OFF" respectively.

- The character size specification is set to "1 H" (normal size) with respect to all lines.

- The smooth function specification is set to "OFF" with respect to all lines.

- O The mask pulse data of all lines are reset, inhibiting any mask pulse from being output.

With respect to the character RAM, the data stored and the line address and word address values will remain unchanged.

### OSCILLATION CONTROL

With this IC, oscillation ON/OFF control can be effected with the Display Control command and thus power can be saved by stopping oscillation while characters are not being displayed on the screen. Even if oscillation is stopped by the oscillation OFF function, characters may or may not be output. So, be sure to use this function in conjunction with the Display OFF function.

Neither the video RAM nor the character RAM can be rewritten with oscillation being stopped.

Note: When display is ON, the oscillation synchronizes  $H_{sync}$ , so the oscillation is stopping at the low level term of  $H_{sync}$ . When display is OFF, the oscillation keeps on irrespective of  $H_{sync}$ .

### CHARACTER BLINKING

With this IC, blinking can be effected for each character by executing the Display Control command.

The character to blink must be specified with the Display Character, Blinking, and Character Data Control commands.

The blinking ON/OFF ratio (the ratio of the blink ON time to the blink OFF time) is 1:1 and the blinking frequency is selectable from among about 2 Hz, about 1 Hz, and about 0.5 Hz.

### **Display Control Command**

Note: The Display ON/OFF function is activated in synchronization with the Low-to-High transition of the H<sub>sync</sub> signal.

### PROGRESSIVE SCAN CONTROL

Progressive scan can be specified independently in the vertical and horizontal directions. By combining the Progressive scan Control command with oscillation frequency  $f_{\rm osc}$ , character design may be changed.  $\mu PD6453$  builds in 1/2 cycle dividers. So it is possible to indicate the same size characters on normal and progressive scan TV screen in according to switching by command.

### **Progressive scan Control Command**

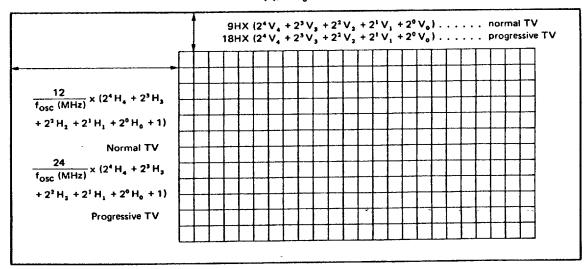

## Conceptual Diagram of Character Design (TV mode/fosc/ Command)

| ·  |    |                                                     | DS/Normal sele                                              | ectable TV mode                                       |

|----|----|-----------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|

| vc | нс | Normal TV mode<br>f <sub>osc</sub> = f <sub>x</sub> | Double-speed TV mode<br>f <sub>osc</sub> = 2 f <sub>x</sub> | Normal TV mode<br>f <sub>osc</sub> = 2 f <sub>x</sub> |

| 0  | 0  |                                                     |                                                             |                                                       |

| 0  | 1  |                                                     |                                                             |                                                       |

| 1  | O  |                                                     |                                                             |                                                       |

| 1  | 1  |                                                     |                                                             |                                                       |

- O When using this IC in Normal TV mode only, use  $f_{osc} = f_x$  with (VC, HC = 0, 0).

- 0 When using this IC in Progressive scan TV mode only, use  $f_{osc} = 2 f_x$  with (VC, HC = 1, 0).

- O When using this IC in Normal TV and Progressive scan TV modes selectively for EDTV system, use

$f_{osc}$  = 2  $f_x$  with (VC, HC = 0, 1) in Normal TV mode

$f_{osc} = 2 f_x$  with (VC, HC = 0, 1) in Progressive scan mode

$f_{\boldsymbol{x}}$ : oscillation frequency for normal scan TV.

$2f_x$ : oscillation frequency for progressive scan TV.

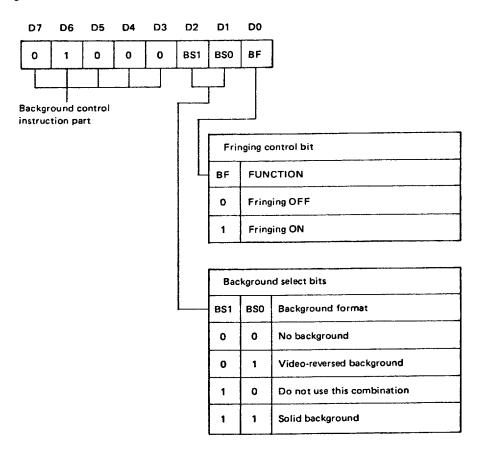

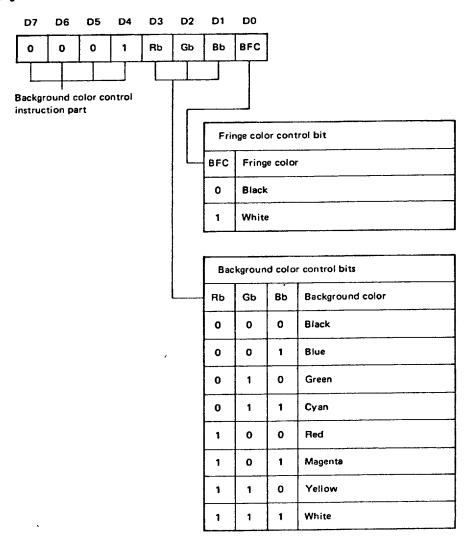

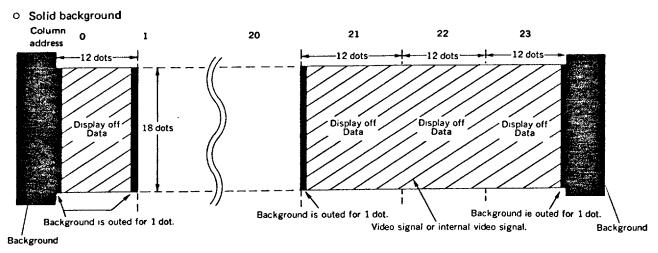

### **BACKGROUND SPECIFICATION**

The type of background (no background, Square background, or solid background) and the background fringing ON/OFF function can be specified for each screen with the Background Control command. Background fringing is carried out irrespective of the character size and is effective only for one dot which is the minimum size.

### **Background Control Command**

### **BACKGROUND COLOR SPECIFICATION**

The background color (black, blue, green, cyan, red, magenta, yellow, or white) can be specified for each character and the background fringe color (black or white) can be specified for each screen. Both colors can be set at the same time by using the Background Color Control command.

### **Background Color Control Command**

Note: The background color and background fringe color specifications are valid only when "Solid background" or "Square background" and "Fringe ON" have been specified with the Background Control command.

## NEC

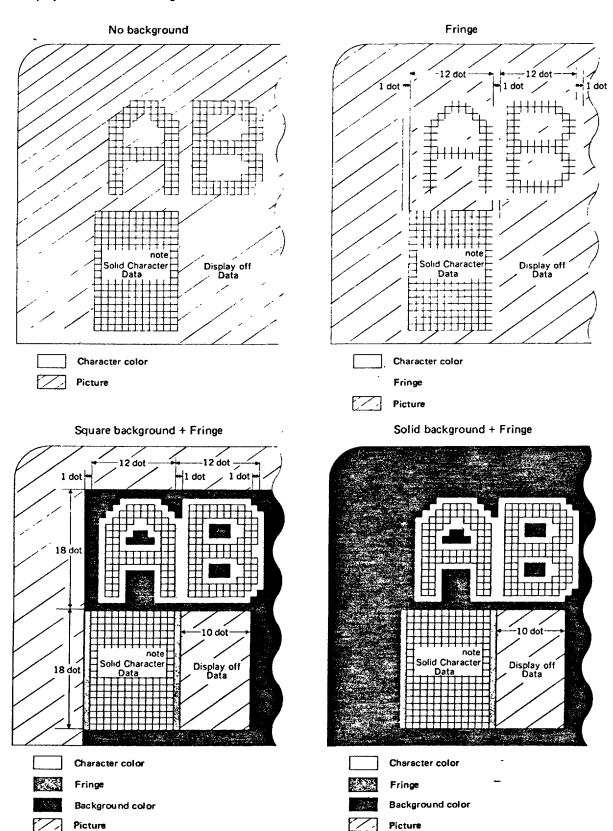

### Display format in Each Background Mode

Note: The solid character data means the data of character code 1  $F_H$  (Standard type of NEC). It is possible to establish the background and the fringe at the same time.

### 1. No background

Only characters are displayed.

### 2. Fringe

Characters with black fringe are displayed. Black fringe of a character which is used the edge of dot-matrix (right and left) is displayed in neighbor character area for 1 dot.

The fringe is the dot of the smallest character size and irrespective of character size.

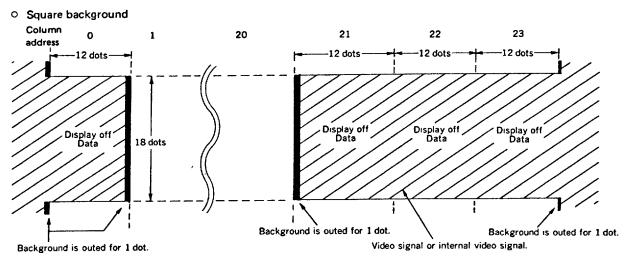

### 3. Square background

The black square background is displayed in character display area.

In this case, the background is displayed in outside of character display area (right and left) for 1 dot.

In case of using "Display OFF data", the background is displayed in the inside edge of "Display OFF data" for 1 dot.

### 4. Solid background

The black solid background is displayed in the all area of screen.

In case of using "Display OFF data", the background is displayed in the inside edge of "Display OFF data" for 1 dot.

## In case of using "Display OFF data".

Note: The "1 dot" is the dot of the smallest character size and irrespective of character size.

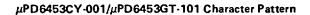

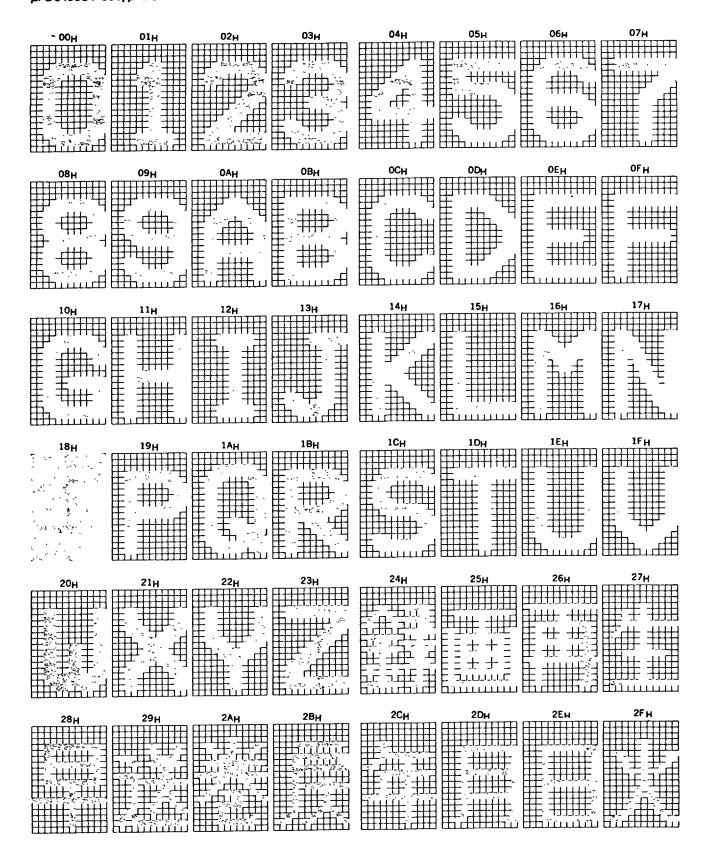

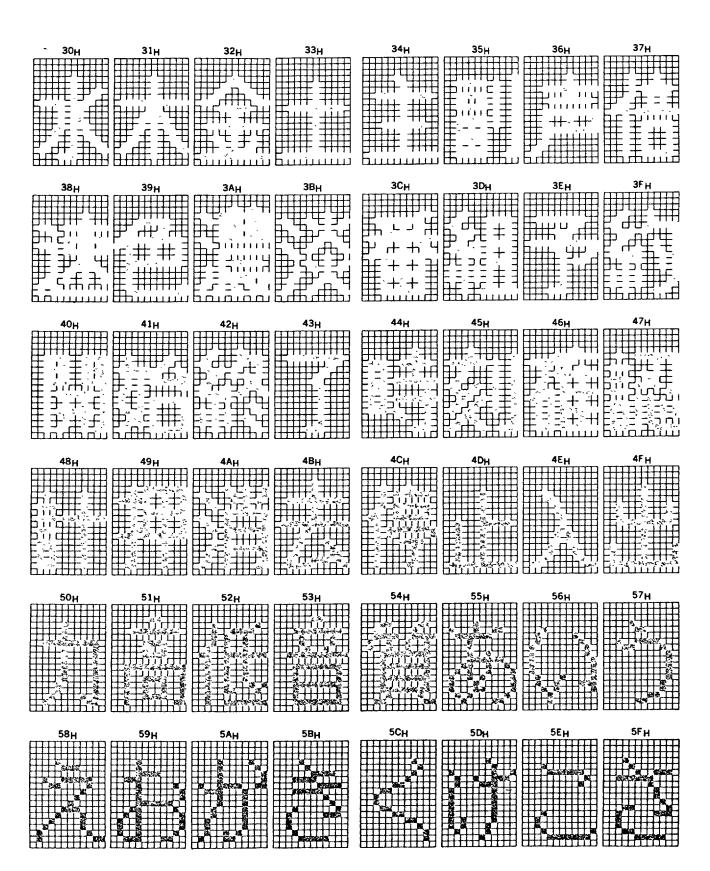

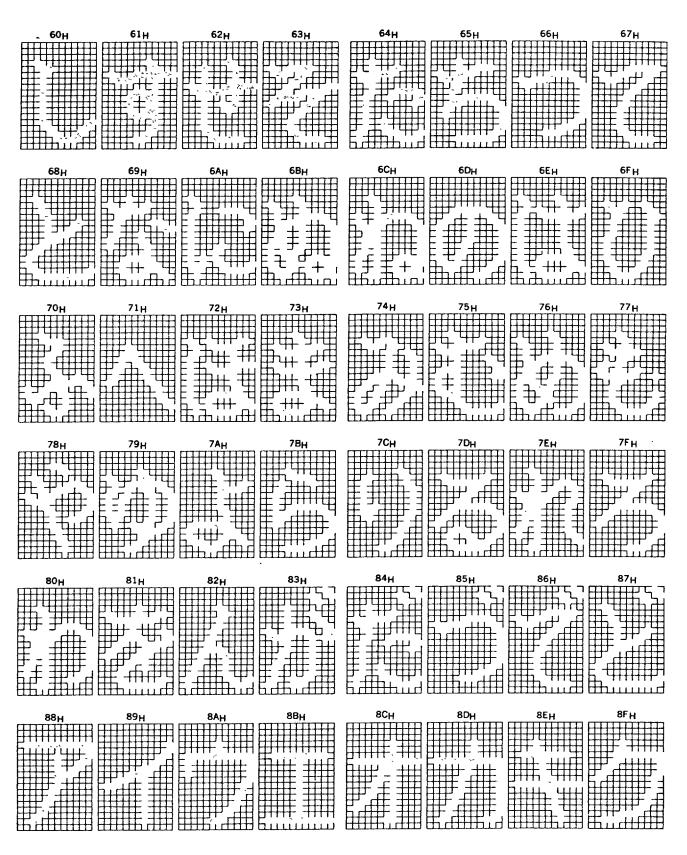

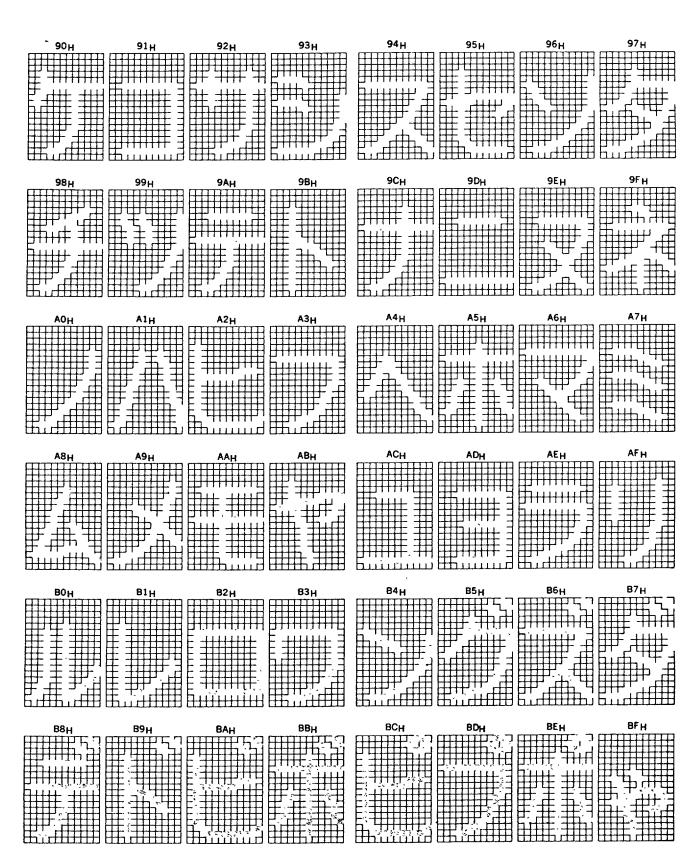

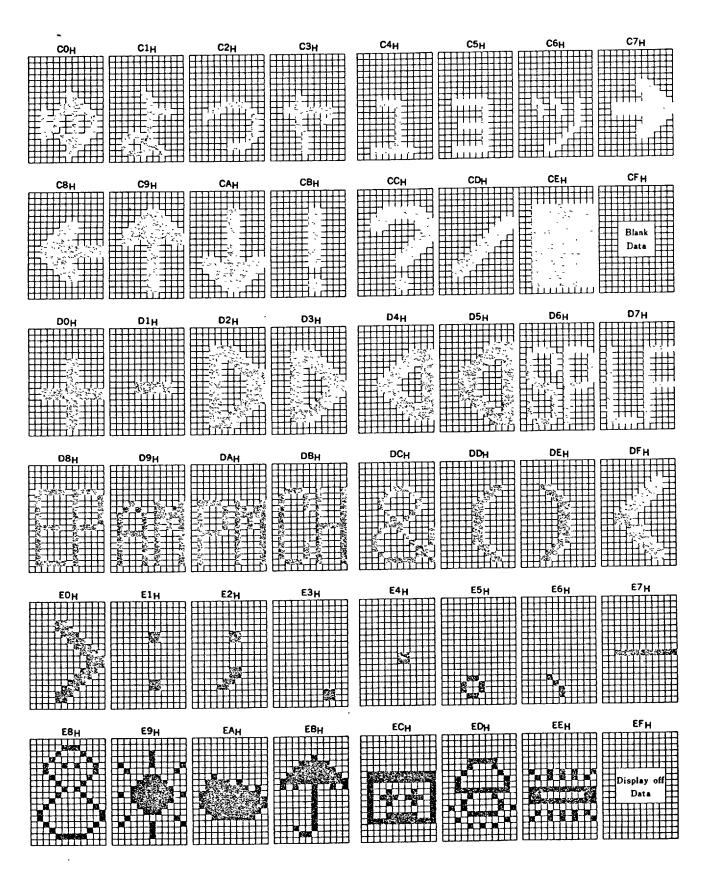

As shown in the following,  $\mu$ PD6453CY-001/ $\mu$ PD6453GT-101 enables display of 240 character generator ROM patterns and 16 patterns to be set in the character generator RAM by the CRAM write data command. The 240 character generator ROM patterns can be changed by the mask code option. However, character code "EFH" is fixed to the display OFF code so that no character pattern can be input to this code.

$\mu$ PD6453CY-001 and  $\mu$ PD6453GT-101 have the same character patterns in the character generator ROM though their packages are different.

## NIFE.

## μPD6453CY-001, μPD6453GT-101 Character Pattern

<sup>\*\*</sup> Character generator RAM area (The character patterns are set in this area with the data sent from the microcomputer.)

### **Character Display**

The number of characters displayed is 12 lines x 24 columns; that is, 288 as shown below:

| AC4,AC3,AC2              | AC1,AC0 | 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 | 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 | 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

|--------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                          | 0000    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| AR3<br>AR2<br>AR1<br>AR0 | 0001    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| ARO                      | 0010    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| Ī                        | 0011    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                          | 0100    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                          | 0101    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                          | 0110    |       |       |       |       |       |       |       |       |       |       |       |       |       | L     |       |       |       |       |       |       |       |       |       |       |

|                          | 0111    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                          | 1000    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| Ī                        | 1001    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                          | 1010    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                          | 1011    |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

The write address is incremented automatically after the display character data is input.

Column address counter AC<sub>4</sub>, AC<sub>3</sub>, AC<sub>2</sub>, AC<sub>1</sub>, AC<sub>0</sub>

Line address counters AR<sub>3</sub>, AR<sub>2</sub>, AR<sub>1</sub>, AR<sub>0</sub>

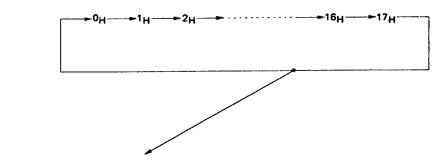

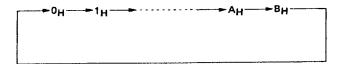

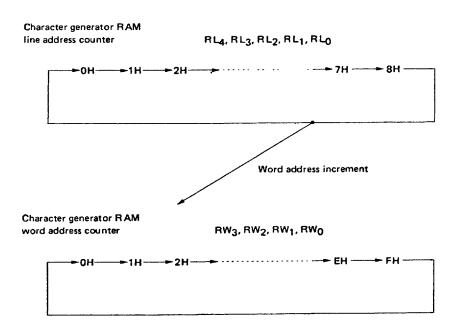

### CHARACTER RAM WRITE ADDRESS CONTROL

The write word address and write line address of the character RAM can be specified with the Character RAM Write Address Control command.

Each time data is input, both the line address and word address are automatically incremented by 1. For the method of writing data into the character RAM, see the paragraph "Character RAM Write Data Control" on the next page.

### Character RAM Write Address Control Command

(Because this command is a 2-byte command, 16 bits must be fully input for this command at the time of continuous command input.)

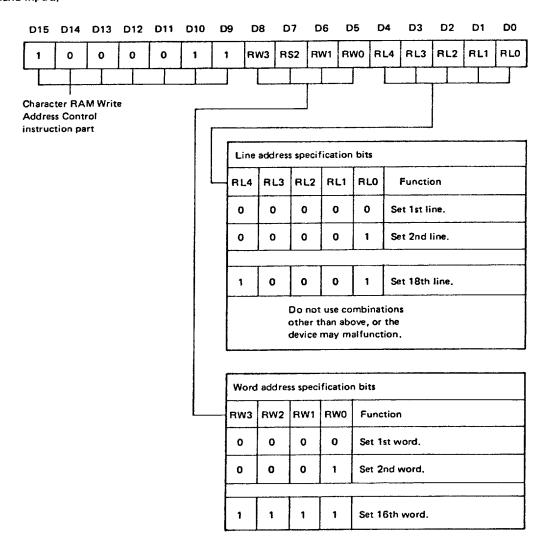

Input data for writing into the character RAM can be specified with the Character RAM Write Data Control command. This command is valid only when the word address and line address of the character RAM have been specified with the Character RAM Write Address Control command. This command must be input with the Lose being set in the Oscillation ON state.

As long as the CS signal remains Low (active), both the line address and word address of the character RAM are automatically incremented by 1 each time the data for one command is input.

### Character RAM Write Data Control Command

(Because this command is a 2-byte command, 16 bits must be fully input for this command at the time of continuous command input.)

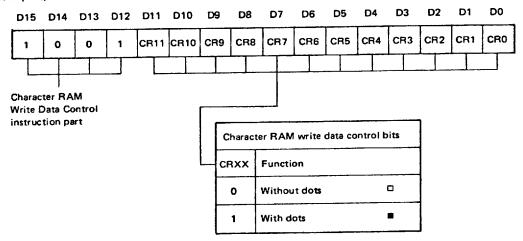

Correspondence of Character RAM Data with Character Pattern

CR2 CR1 CR0 CR4 CR3 CR5 CR11 CR10 CR9 CR8 CR7 CR6 0 0000 (RL4. 3.2.1.0) 0 0001 0 0010 0 0011 0 0100 0 0101 0 0110 0 0111 0 1000 0 1001 0 1010 0 1011 0 1100 0 1101 0 1110 0 1111 1 0000 1 0001

### Writing of Character Generator RAM Data

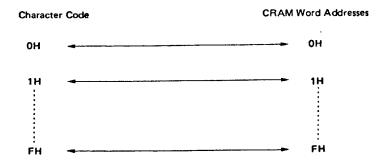

As shown in the section for the character patterns, any character patterns can be set in 16 character codes EO<sub>H</sub> through EF<sub>H</sub>. The character patterns for character generator RAM are set as shown below:

### Character Generator RAM Data Setting Method

Set the word and line address using Character RAM write address control command

Set the character pattern using the Character RAM write data control command

Both the CRAM word address and line address are incremented by the STB signal as shown below. Therefore, this address may be set only once to write 16 characters continuously.

Correspondence between Character Codes and CRAM Word Addresses

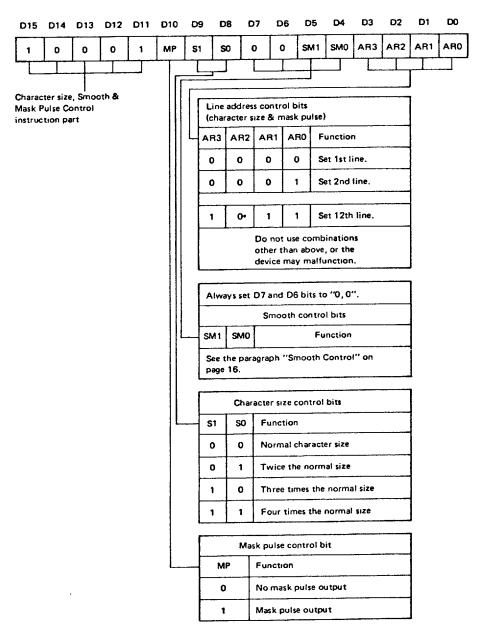

## CHARACTER SIZE, SMOOTH, & MASK PULSE CONTROL

Character size, smooth function (in Character Enlarged mode), and mask pulse (Mask code option) can be specified with the Character Size, Smooth, and Mask Pulse Control command.

A character size common to both the vertical and horizontal directions is selectable in units of lines from among 1H (normal size) to 4H (four times the normal size).

For the method of writing character data, see the paragraph "Display Character Control" on page 33.

### Character Size, Smooth, & Mask Pulse Control Command

(Because this command is a 2-byte command, 16 bits must be fully input for this command at the time of continuous command input.)

Note: The MP (mask pulse) control bit is valid only when the mask pulse function has been selected with the Mask code option. If this function has not been selected, set the MP bit to "0".

The horizontal size of one character depends on the oscillation frequency ( $f_{OSC}$ ), and the vertical size of one character depends on the number of scanning lines. In case of the smallest character size, one horizontal dot size is  $1/f_{OSC}$ , and one vertical dot size is two scanning lines (in the frame).

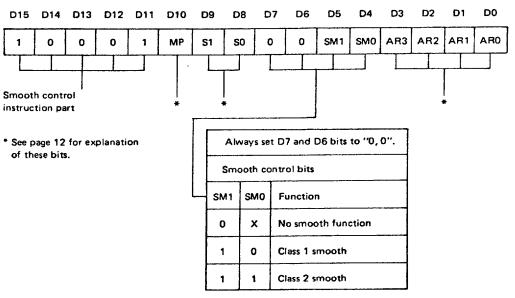

### SMOOTH (INTERPOLATION) CONTROL

In the Character Enlarged mode (two to four times the normal size), the smooth function can be set in units of lines to smooth each displayed character.

### **Smooth Control Command**

(Because this command is a 2-byte command, 16 bits must be fully input for this command at the time of continuous command input.)

X: Don't care.

### Description of each smooth type

Class I smooth = Smooth A + Smooth B

Class II smooth = Smooth A + Smooth B + Smooth C + Smooth D

## An Example of Smooth

With dots

Smooth dats

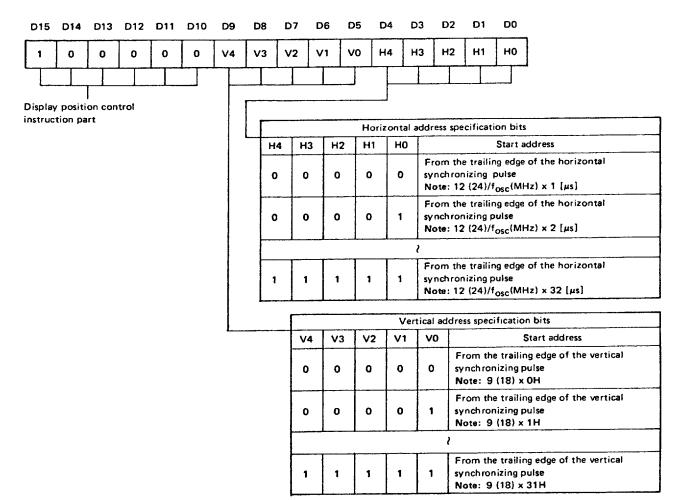

### **DISPLAY POSITION CONTROL**

It is possible to set 32 steps for vertical and horizontal direction.

### **Display Position Control Command**

(Because the command is a 2-byte command, 16 bits must be fully input for this command at the time of continuous command input.)

( ): Progressive TV

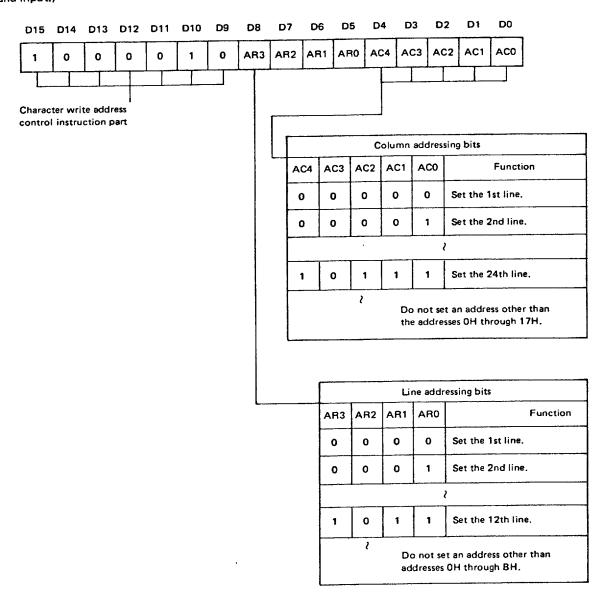

### **Character Write Address Control**

Line and column address of VRAM which is written the character data can be specified with the character write address control command.

Please refer to the section of Display Character Control command about writing the character data.

### Character Write Address Control Command

(Because this command is a 2-byte command, 16 bits must be fully input for this command at the time of continuous command input.)

## NEC

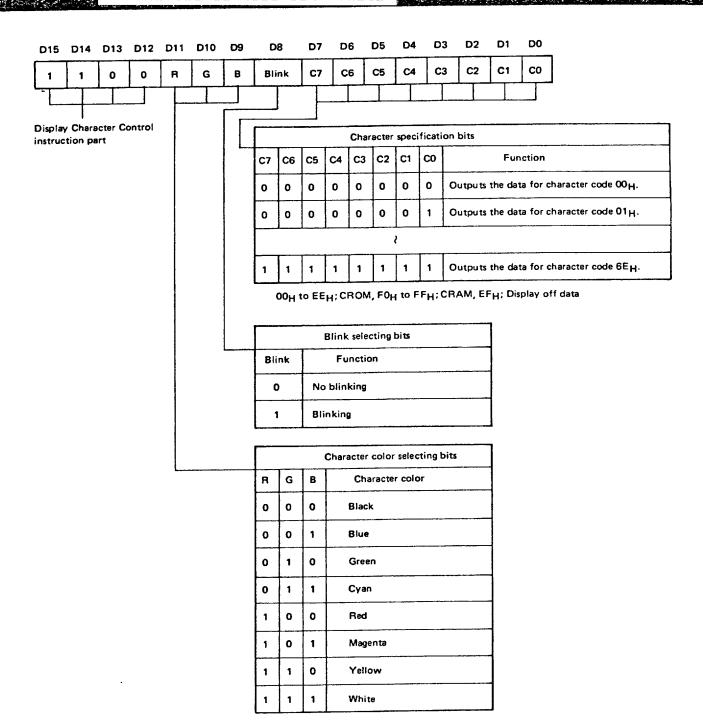

### WRITING DISPLAY CHARACTER DATA, CHARACTER COLOR, AND BLINKING DATA

The write address of data can be set directly in the address counter by using the Character Write Address Control command. After the write address has been set, the display character data must be entered. The character color and blinking data are written into the video RAM and at the same time retained in the internal registers. The display character data is written into the video RAM and the write address is automatically incremented by 1.

When character data is to be input without changing the character color and blinking data, the Display Character Control command can be input in an abbreviated format by entering only its low-order 8 bits (character address) while the CS signal is being held in the Low state. After the command input, the write address is automatically incremented by 1.

The character data, character color, and blinking data can be setwith the Display Character Control command.

### **Display Character Control Command**

As mentioned above, the character data, character color, and blinking data to be written into the video RAM can be specified with the Display Character Control command. This command must be input with the Losc being set in the Oscillation ON state. When characters are to be input successively without changing the character color and blinking data, only the low-order 8 bits of this command need to be input for the second and subsequent characters, because this command is a 2nd byte continuous command.

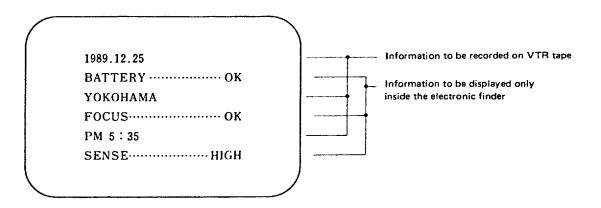

### Mask Pulse Function (Mask Code Option)

When used in a VCR camera, the on-screen ICs provide two types of information; information to be recorded on VCR tape, such as the date and title, and information to be displayed only inside the electronic view finder, such as the battery, focus, sensitivity, and mode. For proper use of these two types of information, the mask option allows the V<sub>MON</sub> terminal to be used as the character-by-character signal output terminal.

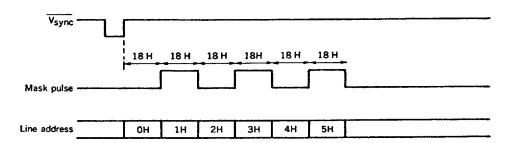

Example: The mask pulse is to be output to line addresses 1 H, 3 H, and 5 H with vertical address 0 H and a character size of 1 H/dot.

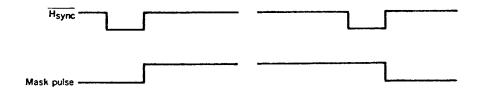

The leading and trailing edges of the mask pulse are synchronized with the trailing edge of HSYNC.

## RECOMMENDED CONDITIONS FOR OPERATION TIMING

$(T_a = 25 \,^{\circ}C, V_{DD} - V_{SS} = 5.0 \, V)$

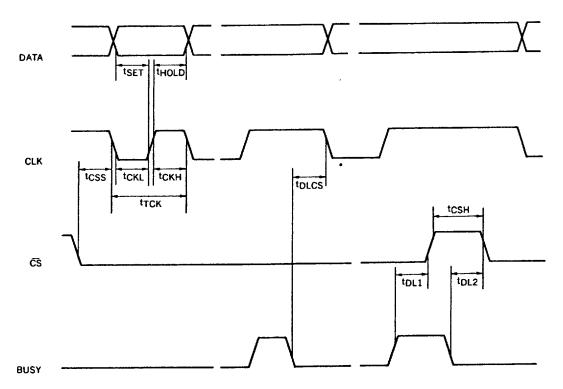

| ITEM                              | SYMBOL           | CONDITION | MIN. | TYP. | MAX.     | UNIT |

|-----------------------------------|------------------|-----------|------|------|----------|------|

| Minimum Setup Time                | <sup>t</sup> SET |           | 400  |      |          | กร   |

| Minimum Hold Time                 | tHOLD            |           | 400  |      |          | ns   |

| Minimum Clock Width at Low Level  | tCKL             |           | 400  |      |          | ns   |

| Minimum Clock Width at High Level | †CKH             |           | 400  |      |          | ns   |

| Clock Cycle                       | <sup>t</sup> TCK |           | 1.0  |      |          | μς   |

| CS Minimum Setup Time             | tCSS             |           | 400  |      |          | ns   |

| CS Minimum Hold Time              | tCSH             |           | 400  |      |          | ns   |

| Delay Time 1 (from BUSY rising)   | tDL1             |           | 400  |      |          | ns   |

| Delay Time 2 (from BUSY falling)  | tDL2             |           | 400  |      |          | ns   |

| Minimum Busy to CLK Time          | tDLCS            |           | 400  |      | <u> </u> | ns   |

| Minimum VSYNC Width at Low Level  | t∨WL             |           | 4    |      |          | μς   |

| Minimum HSYNC Width at High Level | tHWL             |           | 4    |      |          | μs   |

For format data, the BUSY signal goes low after the internal state is completely established. It also goes low when writing data into the VRAM is finished.

When writing data into the VRAM extends to the horizontal flyback time, the BUSY signal lasts longer than usual. (This is because oscillation is off and data cannot be written into the VRAM during the horizontal flyback time.)

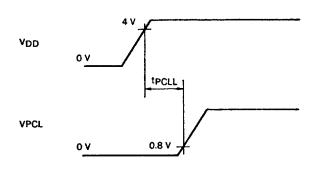

### **Power ON Reset**

| ITEM                                  | SYMBOL | CONDITION | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------|--------|-----------|------|------|------|------|

| PCL terminal Minimum Low<br>Hold Time | tPCLL  |           | 10   |      |      | μς   |

### Application of µPD6453

μPD6453 has 3 blanking signals output terminals. These terminals (R<sub>BLK</sub>, G<sub>BLK</sub>, B<sub>BLK</sub>) outputs the blanking signals which correspond to all character signals output (V<sub>R</sub>, V<sub>G</sub>, V<sub>B</sub>).

This diagram shows application of  $\mu PD6453$  for camera recorder.

For example,  $V_G$  and  $G_{BLK}$  terminals are connected to the view finder part,  $V_R$  and  $R_{BLK}$  terminals are connected to the recorder deck part.

It is possible to indicate characters only on view finder part by specifying character color G, and it is possible to indicate characters on both parts (the view finder part and the recorder deck part) by specifiing character color R + G.

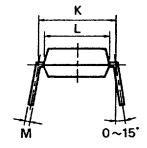

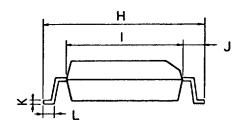

### μPD6453CY-001

20-pin plastic DIP (400 mil)

P20C-100-400B

### **NOTES**

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS           | INCHES                  |

|------|-----------------------|-------------------------|

| Α    | 27.94 MAX.            | 1.100 MAX.              |

| В    | 2.54 MAX.             | 0.100 MAX.              |

| С    | 2.54 (T.P.)           | 0.100 (T.P.)            |

| D    | 0.50 <sup>±0</sup> 10 | 0.020-888               |

| F    | 1.2 MIN.              | 0.047 MIN.              |

| G    | 3.5 ±0 3              | 0.138 <sup>±0 012</sup> |

| н    | 0.51 MIN.             | 0.020 MIN.              |

| 1    | 4.31 MAX.             | 0.170 MAX.              |

| J    | 5.72 MAX.             | 0 226 MAX.              |

| κ    | 10.16 (T.P.)          | 0.400 (T.P.)            |

| L    | 8.6                   | 0.339                   |

| М    | 0.25-8 65             | 0.010 -0 003            |

| N    | 0.25                  | 0.01                    |

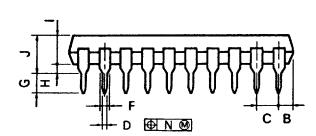

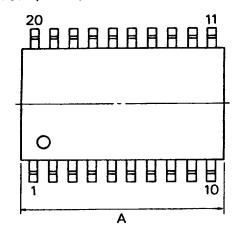

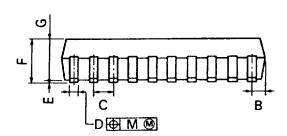

## μPD6453GT-101

## 20-pin plastic SOP (375 mil)

P20GM-50-375B-2

### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS          | INCHES       |

|------|----------------------|--------------|

| Α    | 13.00 MAX.           | 0.512 MAX.   |

| В    | 0.78 MAX.            | 0.031 MAX.   |

| С    | 1.27 (T.P.)          | 0.050 (T.P.) |

| D    | 0.40 -0 05           | 0.016-0.003  |

| Е    | 0.1 <sup>± 0 1</sup> | 0.004 ±0 004 |

| F    | 2.9 MAX.             | 0.115 MAX.   |

| G    | 2.50                 | 0.098        |

| н    | 10.3 10.3            | 0.406-8813   |

| ı    | 7.2                  | 0.283        |

| J    | 1.6                  | 0.063        |

| К    | 0.15 8 6             | 0.006 -0 004 |

| L    | 0.8 <sup>±0</sup> 2  | 0.031 -0 008 |

| М    | 0.12                 | 0.005        |