Differential合mpyfier集应音

WWW.DZ

急出货

## CA3040

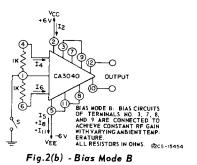

# Video and Wide-band Amplifier

For Industrial and Commercial Equipment at Frequencies up to 200 MHz

### Features:

- High differential push-pull voltage gain - 37 dB typ.

- Single-ended voltage gain -31 dB typ.

- Wide [3dB] bandwidth -55 MHz typ.

- Balanced input and output

- NWW.DZSG.COM High input resistance – 150 kΩ typ.

The RCA CA3040 is a monolithic silicon integrated circuit designed to meet the requirements of a wide variety of applications requiring high gain and wide bandwidth. The cascode-connected differential amplifier achieves a double-ended gain of 37 dB with a typical 3 dB bandwidth of 55 MHz. Emitter-Follower input and output stages provide the desirable high input impedance and output impedance for coupling to other circuits.

The CA3040 includes two biasing options, allowing the user to optimize his design over the entire military temperature range of -55 to +125° C. Bias Mode A vields a substantially constant voltage at the output terminals for applications using DC coupling to succeeding stages or requiring maximum dynamic range over the temperature range. DC output voltage varies less than 0.1 volt (typically) over the entire temperature range while gain varies  $\pm$  2 dB. Bias Mode B

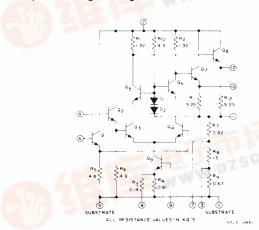

Fig. 1 - Schematic Diagram for CA3040.

#### Applications

- Video amplifier

- Schmitt trigger

- Modulator

- IF Amplifier Mixer

- DC Amplifier

- Sense Amplifier

provides extremely stable gain over the temperature range. Gain variation is 0 dB (typically) in this Bias Mode. DC variation is  $\pm$  0.8 volt.

Provisions are also made for stabilizing the operating point for either single or split power supplies.

The resistance values included on the schematic diagram have been supplied as a convenience to assist Equipment Manufac-turers in optimizing the selection of "outboard" components of equipment designs. The values shown may vary as much as  $\pm 30\%$ .

RCA reserves the right to make any changes in the Resistance Values provided such changes do not adversely affect the published performance characteristics of the device.

# CA3040

## ABSOLUTE-MAXIMUM RATINGS

| DISSIPATION *                                                                |

|------------------------------------------------------------------------------|

| Operating -55°C to +125°C   Storage -65°C to +150°C                          |

| LEAD TEMPERATURE (During Soldering):                                         |

| At distance 1/16 ± 1/32 inch (1.59 ± 0.79mm)<br>from case for 10 seconds max |

| * Limitation imposed by the thermal resistance of package.                   |

## MAXIMUM VOLTAGE RATINGS at TA = 25°C

The following chart gives the range of voltages which can be applied to the terminals listed vertically with respect to the terminals listed horizontally. For example, the voltage range of the vertical terminal 2 with respect to terminal 11 is 0 tc +14 volts.

### MAXIMUM CURRENT RATINGS

IOUT

mΑ

5

-

5

0.1

\_

0.1

5

5

0.1

10

---

10

|                      |   |          |   |          |          |          |              | - |          |          |                |          |   |                      |                       |

|----------------------|---|----------|---|----------|----------|----------|--------------|---|----------|----------|----------------|----------|---|----------------------|-----------------------|

| TERM-<br>INAL<br>No. | 1 | 2        | 3 | 4        | 5*       | 6        | 7            | 8 | 9        | 10       | 11*            | 12       |   | TERM-<br>INAL<br>No. | I <sub>IN</sub><br>mA |

| 1                    |   | 0<br>-14 | * | *        | +14<br>0 | *        | + 10<br>- 10 | * | *        | *        | +14<br>0       | *        |   | 1                    | 5                     |

| 2                    |   |          | * | +14<br>0 | +14<br>0 | +14<br>0 | *            | * | *        | +14<br>0 | +14<br>0       | +14<br>0 |   | 2                    | -                     |

| 3                    |   |          |   | *        | +5<br>-3 | *        | *            | * | *        | *        | +5<br>-3       | *        | ] | 3                    | 5                     |

| 4                    |   |          |   |          | *        | +3<br>-3 | *            | * | *        | *        | *              | *        |   | 4                    | 1                     |

| 5▲                   |   |          |   |          | *        | *        | +10<br>-3    | * | +3<br>+7 | *        | 0<br>Note<br>1 | *        |   | 5                    | -                     |

| 6                    |   |          |   |          |          |          | *            | * | *        | *        | *              | *        |   | 6                    | 1                     |

| 7                    |   |          |   |          |          |          |              | * | *        | *        | +10<br>-3      | *        |   | 7                    | 5                     |

| 8                    |   |          |   |          |          |          |              |   | +3<br>-3 | *        | *              | *        |   | 8                    | 5                     |

| 9                    | _ |          |   |          |          |          |              |   |          | *        | +7<br>-3       | *        |   | 9                    | 1                     |

| 10                   |   |          |   |          |          |          |              |   |          |          | *              | *        |   | 10                   | -                     |

| 11*                  |   |          |   |          |          |          |              |   |          |          | •              | *        |   | 11                   | -                     |

| 12                   |   |          |   |          |          |          |              |   |          |          |                |          |   | 12                   | -                     |

### ▲ Reference Substrate

Note 1: External connection required for proper operation.

\* Voltages are not normally applied between these terminals. Voltages appearing between these terminals will be safe if the specified limits between all other terminals are not exceeded.

# CA3040

# ELECTRICAL CHARACTERISTICS AT $T_A = 25^{\circ}C$ Unless Otherwise Specified

|                                                                  | Symbols                                  | Test<br>Circuits |                                             |          | Limits |          | Units              | Typical<br>Characteristics<br>Çurves |  |

|------------------------------------------------------------------|------------------------------------------|------------------|---------------------------------------------|----------|--------|----------|--------------------|--------------------------------------|--|

| Characteristics                                                  |                                          |                  | Special Test Conditions                     |          | CA3040 |          |                    |                                      |  |

|                                                                  |                                          | Fig.             |                                             | Min.     | Тур.   | Max.     |                    | Fig.                                 |  |

| STATIC CHARACTERISTICS                                           | $V_{CC} = +6V, V_{E}$                    | E = -6V          |                                             |          |        | r        |                    |                                      |  |

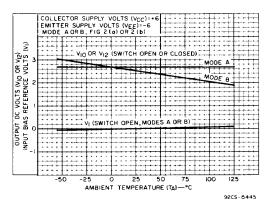

| Output Voltage                                                   | $V_{10}$ or $V_{12}$                     | 2(a)<br>2(b)     | Bias Mode Switch<br>A or B: Closed          | 1.4      | 2.7    | 3.7      | v                  | 9                                    |  |

| Base Bias Voltage                                                | Vq                                       | 2(a)             | Bias Mode A<br>Switch Closed                | -        | -1.7   | -        | V                  | -                                    |  |

|                                                                  |                                          | 2(b)             | Bias Mode B<br>Switch Closed                | -        | - 1.7  | -        | V                  | -                                    |  |

| Input Bias Reference Voltage                                     | v1                                       | 2(a)<br>2(b)     | Bias Mode Switch<br>A or B: Open            | -1       | -      | +1       | V                  | 9                                    |  |

| Input Bias Current                                               | I4, I6                                   | 2(a)<br>2(b)     | Bias Mode Switch<br>A or B: Closed          | -        | 15     | 45       | μA                 | -                                    |  |

| Input Unbalance Current                                          | I <sub>6</sub> -I <sub>4</sub>           | 2(a)<br>2(b)     | Bias Mode Switch<br>A or B: Closed          | -        | -      | 6        | μ <b>A</b>         | -                                    |  |

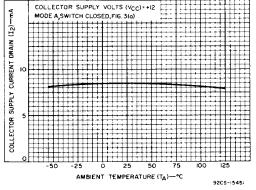

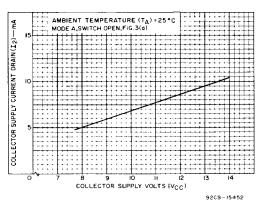

|                                                                  | I 2 or<br>I 5 + I 11                     | 2(a)             | Mode A<br>Switch open or closed             | 4.7      | 8.5    | 15.5     | mA                 | 10                                   |  |

| Power Supply Current Drain                                       | I2 or<br>I5 + I8 + I11                   | 2(b)             | Mode B<br>Switch open or closed             | 4.7      |        |          |                    |                                      |  |

| DYNAMIC CHARACTERISTICS                                          | VCC = +12V, V                            | 'EE = 0, S       | plit Voltage Supply (Optiona                | al) = +6 | SV .   |          |                    |                                      |  |

| Differential Voltage Gain                                        |                                          |                  |                                             |          |        |          |                    | -                                    |  |

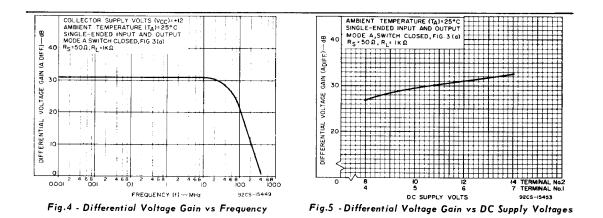

| Single-Ended Input<br>Differential Output                        | A <sub>DIFF(DE)</sub>                    | 3(a)             | f = 1 MHz<br>$R_s = 50 \Omega$              | 34       | 37     | -        | dB                 | -                                    |  |

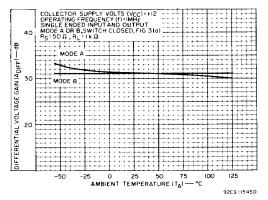

| Single-Ended Input<br>and Output                                 | A <sub>DIFF(SE)</sub>                    | 3(a)             | f = 1  MHz<br>$R_s = 50 \Omega$             | 28       | 31     | -        | dB                 | 4,5                                  |  |

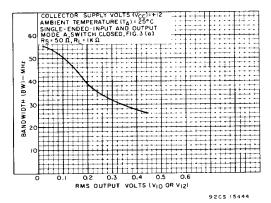

| -3dB Bandwidth                                                   | BW                                       | 3(a)             | $R_s = 50 \Omega$                           | 40       | 55     |          | MHz                | 4,7                                  |  |

| Differential Voltage Gain Balance                                | ADIFF(SE)10                              | 3(a)             | f = 1 MHz                                   | -1       | 0      | +1       | dB                 | -                                    |  |

| Output Voltage Swing                                             | V <sub>8</sub> or V <sub>10</sub><br>RMS | 3(a)             | f = 1 MHz<br>$R_s = 50 \Omega$              | -        | 0.5    | -        | VRMS               | 7                                    |  |

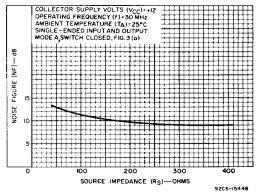

| Noise Figure                                                     | NF                                       | 3(a)             | (Note 1) f = 30 MHz<br>$R_{s} = 400 \Omega$ | -        | 7.5    | 9        | dB                 | 8                                    |  |

| Parallel Input Resistance                                        | R <sub>1</sub>                           | 3(a)             |                                             | -        | 150    | -        | kΩ                 | -                                    |  |

| Parallel Input Capacitance                                       | Ci                                       | 3(a)             | f≃1MHz                                      | -        | 2.2    |          | pF                 | -                                    |  |

| Output Resistance                                                | Ro                                       | 3(a)             |                                             | -        | 125    | -        | Ω                  | -                                    |  |

| TEMPERATURE DEPENDENT CHA<br>Temperature coefficients for ambien | RACTERISTICS                             | 5°C_≤TA          | ≤+ 125°ົ                                    |          | ·      |          |                    |                                      |  |

|                                                                  | ∆V10 or ∆V12                             |                  | Bias Mode A                                 | -        | 0      | -        | mV/ºC              | 9                                    |  |

| Output Voltage                                                   | °C                                       | 3(b)             | Bias Mode B                                 | - 6.4    |        | -        | mV/ºC              | Ļ                                    |  |

| Power Supply Current Drain                                       | ∆I₂/°C                                   | 3(a)             | Bias Mode A                                 | -        | 5      | -        | μΑ/ <sup>0</sup> C | 11                                   |  |

| Differential Voltage Gain                                        | A <sub>DIFF</sub> / <sup>o</sup> C       | 3(a)             | Bias Mode A                                 | -        | 0.0166 | -        | dB∕⁰C              | 12                                   |  |

|                                                                  |                                          | 3(b)             | Bias Mode B                                 |          | L      | <u> </u> |                    | L                                    |  |

Note 1: Replace 1-k $\Omega$  resistors between Term. 1 and 4 and Te  $_{\odot}$ . 1 and 6 with suitable chokes so that reactance at 30 MHz exceeds 5k $\Omega$

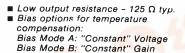

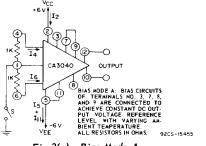

### STATIC CHARACTERISTICS TEST CIRCUITS FOR CA3040

Fig.2(a) - Bias Mode A

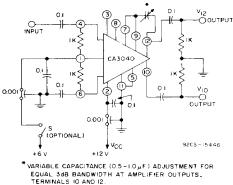

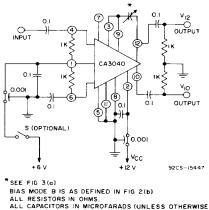

### DYNAMIC CHARACTERISTICS TEST CIRCUITS FOR CA3040

ALL RESISTORS IN OHMS ALL CAPACITORS IN MICROFARADS (UNLESS OTHERWISE

INDICATED). BIAS MODE A IS AS DEFINED IN FIG. 2 (a)

Fig.3(a) - Bias Mode A

INDICATED)

Fig.3(b) - Rias Mode B

# CA3040

#### OPERATING CONSIDERATIONS

#### General

The CA3040 is designed to provide flexibility in the selection of power supply configurations and to provide the circuit designer the choice between two modes of temperature-compensated performance. Mode A, which provides constant DC output voltage, is recommended for most applications. The control of the operating point provided by this mode maintains the dynamic range of the device while gain variation over most of the range is less than  $\pm 1$  dB. Mode B provides constant gain for applications where this consideration is critical, but will exhibit a reduction of dynamic range at the temperature extremes.

#### **Power Supply Considerations**

Figures 2 and 3 illustrate the use of the CA3040 with balanced dual supplies and single power supplies, respectively. Both figures demonstrate that the inputs may be directly referenced to the center point of the supply (ground in Fig.2) by closing the included switch. This is the natural connection in Fig.2. This connection is optional, however, and need not be made. Use of this connection in Fig.3 implies the presence of another DC supply or a "stiff" bleeder. If such a source is present its use is suggested in order to maintain maximum common mode range. Dynamic performance and dynamic range of the output circuit are unaffected by the choice of biasing scheme used so that in most cases direct connection of Terminal No.1 to the center point of the supply is not required. Where direct connection is not used, Terminals No.4 and No.6 must be biased from Terminal No.1 for proper operation.

#### **High-Frequency Considerations**

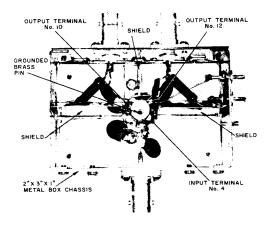

Stable high-frequency operation requires that proper high-frequency construction techniques be followed. The photograph of Fig.6 illustrates the precautions taken in the construction of the test circuit of Fig.3.

Extreme caution is required because of the extended gain bandwidth capability of the device. Oscillations have been observed in the 400-to-800 MHz range when precautions were not taken. In addition to normal considerations of shielding, parts layout, and isolation, the following specific suggestions are made:

- 1. Use sockets only when necessary. Sockets, when used, must provide shielding within the pin circle. The socket shown in the chassis of Fig.6 is a Barnes MG-1201, or equivalent, modified by drilling a 1/8" hole in the center and inserting a grounded brass pin.

- 2. Do not bypass Terminal No.9 in normal operation. Fig.3 shows the use of neutralization between Terminal No.9 and one output to balance the amplifier at high frequencies. Experience shows that stable operation, while possible, is difficult to achieve if Terminal No.9 is bypassed to ground.

- 3. In DC testing,  $1 \ k\Omega$ , 1/4 W carbon resistors should be soldered directly to the socket Terminals No.4 and No.6 to suppress parasitic oscillations. All current carrying connections are made at the other end of the resistors. Direct sensing of Terminal No.4 or No.6 voltage should not be attempted.

Fig.6 - Test Circuit Layout

### **Differential Amplifiers**

## CA3040

Fig.7 -3dB Bandwidth vs Single-Ended Output Voltage

Fig.9 - Output Volts or Input Bias Reference Volts vs Ambient Temperature

Fig.11 - Collector Supply Current Drain (12) vs Ambient Temperature

Fig.8 - Noise Figure (NF) vs Source Impedance

Fig.10 - Collector Supply Current Drain (12) vs Collector Supply Voltage (VCC)

Fig.12 - Single-Ended Differential Voltage Gain vs Ambient Temperature