WWW.DZS

MM1103 1024-bit fully decoded dynamic random access read/write memory

#### general description

The MM1103 fully decoded dynamic 1024 word x 1-bit per word read/write random access memory is a monolithic MOS integrated circuit using silicon. gate low threshold technology. This device provides a non-destructive read out memory cell with chip enable for easy selection when many outputs are "OR"ed. Low power is achieved by the use of dynamic logic and power dissipation occurs primarily during precharge. The MM1103 is used for main memory applications where large bit storage, high performance and low cost are important.

Refresh cycle

Fully decoded Easy memory expansion

Device protection

Chip enable input All I/O lines have protection against static charge

"OR"ing output capability

Low power dissipation Small package size

250 mW 18 pin DIP

2 ms

#### features

- Fast access time

- Fast cycle time

300 ns max

480 ns read cycle 580 ns write cycle

- applications Mainframe memory

- Large buffer memory

### connection diagram

WW.DZSC.COM Dual-In-Line Package

### absolute maximum ratings

All Input or Output Voltages With Respect

+0.3V to -25V to the Most Positive Supply Voltage VSS Supply Voltage Vop and Vas With +0.3V to -25V Respect to V<sub>SS</sub> 500 mW Power Dissipation at Room Temperature

-25°C to +70°C Operating Temperature Range -65°C to +160°C Storage Temperature Range 300°C Lead Temperature (Soldering, 10 sec)

# dc operating characteristics /6 × 19.5

| PARAMETER                                                  | CONDITIONS                                                                             | MIN                  | TYP | MAX                  | - |

|------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------|-----|----------------------|---|

| Input Load Current (All<br>Input Pins) (I <sub>1-1</sub> ) | V <sub>IN</sub> OV                                                                     |                      |     | 1                    |   |

| Output Leakage Current (ILo)                               | Vour - av                                                                              |                      |     | 100                  |   |

| Ves Supply Current (ise)                                   | 1                                                                                      |                      |     | 20                   |   |

| Average Supply Current (I <sub>OD AV</sub> )               | Cycle Time - 580 is precharge width<br>- 240 ns, T <sub>A</sub> - 25°C                 |                      |     | "                    |   |

| Standby Supply Current                                     | Precharge = V <sub>SS</sub> , Chip Enable = V <sub>SS</sub> ,<br>T <sub>A</sub> = 25°C |                      |     | 100                  |   |

| Input LOW Voltage (Vit.)                                   | 1 7                                                                                    | V <sub>SS</sub> - 17 |     | V <sub>SS</sub> - 15 |   |

| Input HIGH Voltage (V <sub>IH</sub> )                      | ĺ                                                                                      | V <sub>SS</sub> - 1  |     | V <sub>SS</sub> + 1  | l |

| Output HIGH Current (I <sub>DH</sub> )                     | TA = 25°C RL - 10012                                                                   | 600                  |     | 4000                 | l |

| Output HIGH Voltage (VOH)                                  | TA - 25°C RL = 10062                                                                   | 60                   |     | 400                  | i |

### ac operating characteristics TA = 0.7C to 70°C, V<sub>SS</sub> = 16 + 5%, (V<sub>BB</sub> = V<sub>SS</sub>) + 3.0V to 4.0V, V<sub>DD</sub> - 0V

READ, WRITE, AND READ/WRITE CYCLE TYP CONDITIONS MAX PARAMETER Time Between Refresh (IRE) Address to Conable Set Up Time (t<sub>AC</sub>) Note 1

| PARAMETER                                     | CONDITIONS | MIN | TYP | MAX | ١.  |

|-----------------------------------------------|------------|-----|-----|-----|-----|

|                                               |            |     |     |     |     |

| READ CYCLE                                    |            |     |     | Υ   | ,   |

| Precharge & Cenable Overlap, HIGH (tovi)      |            |     | L   | 140 | L., |

| Cenable to Precharge Delay (I <sub>CP</sub> ) | i          | 85  | ļ   | ١   | 1   |

| Precharge & Cenable Overlap, LOW (LOV)        |            | 25  | Į   | 75  |     |

| Precharge to Cenable Delay Itec   Note 1      | 1          | 125 |     |     |     |

| and the second second                         |            |     |     |     |     |

#### t<sub>1</sub> : 20 ns C<sub>LOAD</sub> = 100 pF B<sub>LOAD</sub> = 100Ω V<sub>REF</sub> = 40 mV + Ipomas + 21<sub>T</sub> End of Precharge to Output Delay (teo) 300 ~ Address to Output Access (tACC.) Note 1 tecmen + lovemen Precharge to Output Access (tACC2) Note 1 WRITE OR READ/WRITE CYCLE TYP MAX CONDITIONS MIN PARAMETER 580 t<sub>t</sub> = 20 ns Write Cycle (1wc) Note 1 ty = 20 ns Read/Write Cycle (Inwc) Note 1 165 500 Precharge to Read/Write Delay (tpw) 80 Read/Write Pulse Width (twp) 80 Read/Write Set Up Time (tw) 105

$C_{\rm COAD} + 100~\mu\text{F}$

R<sub>1 O A D</sub> 10012 V<sub>HEF</sub> · 40 mV

10

0

120

Note 1. These times will degrade by 40 ns (worst case) if the maximum values for  $V_{1L}$  (for precharge canable and read/write inputs) go to  $V_{SS}$  - 14 2V ± 0. C and  $V_{SS}$  - 14 5V  $\not\in$  70. C.

Data Set Up Time (tow)

Time to Nex1 Precharge (tp)

End of Precharge to Output Delay (teg)

Data Hold Time (ton)

#### ac operating characteristics (con't)

CAPACITANO

| PARAMETER                                  | CONDITIONS                                                                                                  | MIN | TYP | MAX | UNITS |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Address Capacitance (Card)                 | V., V. 3                                                                                                    |     | 5   | 7   | ρF    |

| Precharge Capacitance (Cop)                | V <sub>iti</sub> V <sub>vi</sub>                                                                            |     | 15  | 18  | pF    |

| Conable Capacitance (C <sub>1.4.</sub> )   | V.5, V.,                                                                                                    |     | 15  | 25  | ρF    |

| Read/Write Capacitance (Chw)               | V <sub>IN</sub> V <sub>S</sub> 1 1 MHz                                                                      |     | 11  | 15  | ρF    |

| Data Input Capacitance (C <sub>IN1</sub> ) | Cenable OV All Unusert                                                                                      | - 1 | 4   | 5   | рF    |

| Data Imput Capacitance (C <sub>IN2</sub> ) | V <sub>IN</sub> V <sub>SS</sub> at AC GND<br>Conable V <sub>SS</sub> ,<br>V <sub>IN</sub> V <sub>IS</sub> , |     | 2   | 4   | рF    |

| Data Output Capacitance (COUT)             | V <sub>OU1</sub> OV                                                                                         | - } | 2   | 3   | ρF    |

<sup>\*</sup>This parameter is periodically sampled and is not 100% tested. They are magazed at worst case operating conditions. Capacitance are for plastic packages only.

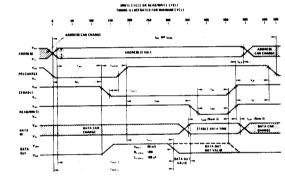

#### switching time waveforms

typo mod

Note  $-1 = V_{SD} + 2V_{T}$  t<sub>1</sub> is defined as the fransitions between these two points. Note  $-2 \le V_{SD} + 2V_{T}$  t<sub>1</sub> is defined as the fransitions between these two points.

### Figure 3: Channel Matching

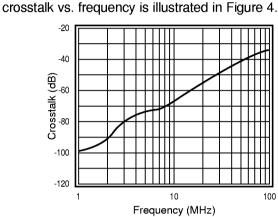

The CLC417's channel-to-channel isolation is better than 70dB for input frequencies of 4MHz. Input referred

Figure 4: Input Referred Crosstalk vs. Frequency

## **Driving Cables and Capacitive Loads**

When driving cables, double termination is used to prevent reflections. For capacitive load applications, a small series resistor at the output of the CLC417 will The R<sub>s</sub> vs. Capacitive Load improve stability. plot, in the Typical Performance section, gives the recommended series resistance value for optimum flatness at various capacitive loads.

### **Power Dissipation**

The power dissipation of an amplifier can be described in two conditions:

- Quiescent Power Dissipation -P<sub>O</sub> (No Load Condition)

- Total Power Dissipation -P<sub>T</sub> (with Load Condition)

The following steps can be taken to determine the power consumption for each CLC417 amplifier:

where: T<sub>amb</sub> = Ambient temperature (°C)

$\theta_{1\Delta}$  = Thermal resistance, from ju

ambient, for a given package

### **Layout Considerations**

and characterization.

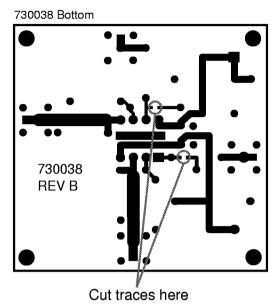

A proper printed circuit layout is essentiate high frequency performance. evaluation boards for the CLC417 (CLC CLC730036 - SOIC) and suggests their for high frequency layout and as an aid for

$P = \frac{(175^{\circ} - Tamb)}{\theta_{1\Delta}}$

Natio

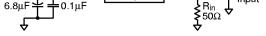

Supply bypassing is required for best per bypass capacitors provide a low imp current path at the supply pins. They al frequency filtering on the power supply

layout factors play a major role in I

performance. The following are recomme

1. Include 6.8μF tantalum and 0.1μF

capacitors on both supplies. 2. Place the 6.8µF capacitors within of the power pins.

for high frequency layout:

- 3. Place the 0.1µF capacitors less th inches from the power pins.

- 4. Remove the ground plane near th and output pins to reduce parasition capacitance.

- 5. Minimize all trace lengths to reduce inductances.

Additional information is included in the e literature.

Special Evaluation Board Consideration To optimize off-isolation of the CLC417,

on both the 730038 and 730036 evaluation cut minimizes capacitive feedthrough be and output. Figure 5 indicates tl recommended to improve off-isolation.

Figure 5: Optional Evaluation Board Alterations

#### **SPICE Models**

SPICE models provide a means to evaluate amplifier designs. Free SPICE models are available for National's monolithic amplifiers that:

- Support Berkeley SPICE 2G and its many derivatives

- Reproduce typical DC, AC, Transient, and Noise performance

- Support room temperature simulations

The *readme* file that accompanies the diskette lists released models, and provides a list of modeled parameters. The application note OA-18, Simulation SPICE Models for National's Op Amps, contains schematics and a reproduction of the *readme* file.

Figure 6: Typical Cable Driver

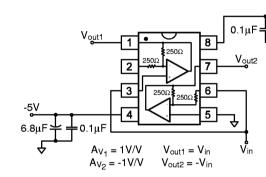

#### Single to Differential Line Driver

The topology in Figure 7 accomplishes a sing differential conversion with no external conversion, the value of Vin is lir common mode input range of the CLC417.

Figure 7: Single to Differential Line I