MOTOROLA 查询MC68HC11A0供应商 SEMICONDUCTOR TECHNICAL DATA

# MC68HC11E20

by MC68HC11E20TS/D

捷多邦,专业PCB打样工厂,24小时QR会出货Is document

# Technical Summary 8-Bit Microcontroller

The MC68HC11E20 high-performance microcontroller unit (MCU) is an enhanced member of the M68HC11 E series of microcontrollers. These devices combine a multiplexed bus with highly sophisticated on-chip peripheral functions and are characterized by high speed and low power consumption. Their fully static design allows these devices to operate at frequencies from 3 MHz to dc.

This document contains information concerning both the ROM-based (MC68HC11E20) and the EPROM-based (MC68HC711E20) versions of this MCU. ROM/EPROM refers to ROM for ROM-based devices and refers to EPROM for EPROM-based devices. Custom-ROM devices have a ROM array that is programmed at the factory to customer specifications. The diagrams for these devices are combined also and differences are noted where necessary.

### Features

- M68HC11 CPU

- 20 Kbytes of On-Chip ROM or EPROM

- 512 Bytes of On-Chip Electrically-Erasable Programmable Read-Only Memory (EEPROM)

- 768 Bytes of On-Chip RAM, All Saved During Standby

- Power Saving STOP and WAIT Modes

- Multiplexed Address/Data Bus

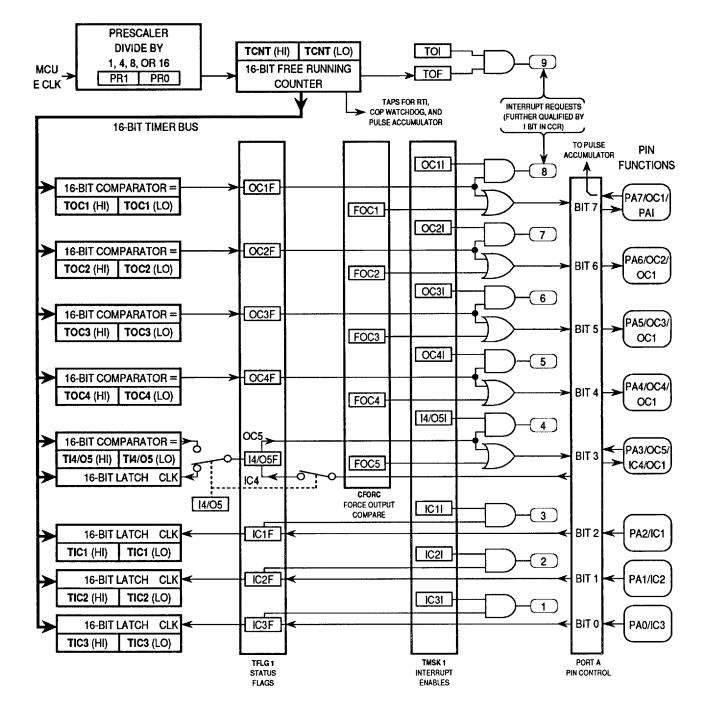

- 16-Bit Timer System

- Three Input Capture (IC) Channels

- Four Output Compare (OC) Channels

- One Additional Channel, Software Selectable as Fourth IC or Fifth OC

- 8-Bit Pulse Accumulator

- Real-Time Interrupt Circuit

- Computer Operating Properly (COP) Watchdog

- Block Protect on EEPROM for Added Security

- Asynchronous Nonreturn to Zero (NRZ) Serial Communications Interface (SCI)

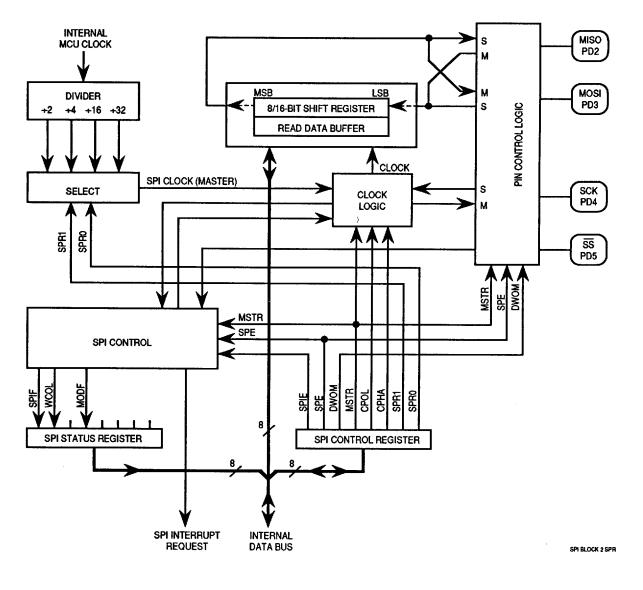

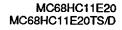

- Synchronous Serial Peripheral Interface (SPI)

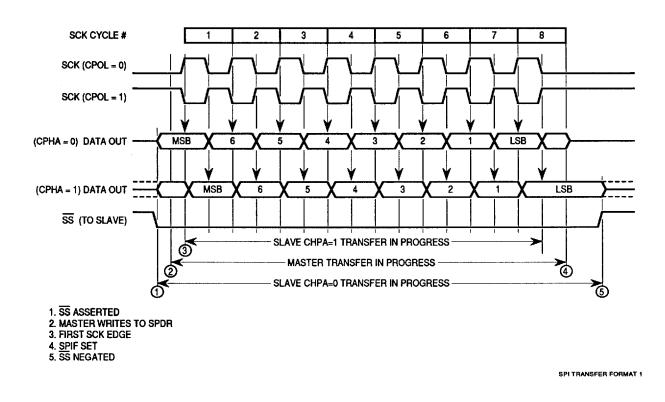

- Eight-Channel 8-Bit Analog-to-Digital (A/D) Converter

- Five Input/Output (I/O) Ports (38 Pins)

- 16 Bidirectional Pins

- -11 Input Only Pins

MOTOROLA-INC., 1993

- 11 Output Only Pins

- Available in 52-Pin Plastic Leaded Chip Carrier (PLCC), 52-Pin Windowed Ceramic Leaded Chip Carrier (CLCC), and 64-Pin Plastic Quad Flat Pack (QFP)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

₩₩°6367248 0137121 488

# **Table of Contents**

| Features1                                                    |   |

|--------------------------------------------------------------|---|

| Register Index                                               | , |

| Ordering Information4                                        | , |

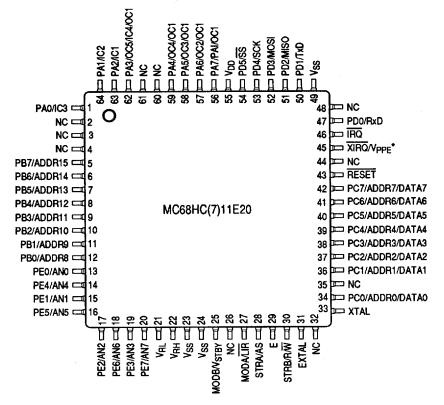

| Pin Assignments for 64-Pin Quad Flat Pack5                   | r |

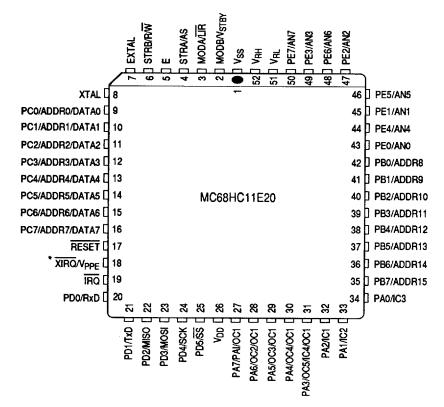

| Pin Assignments for 52-Pin PLCC/CLCC                         | į |

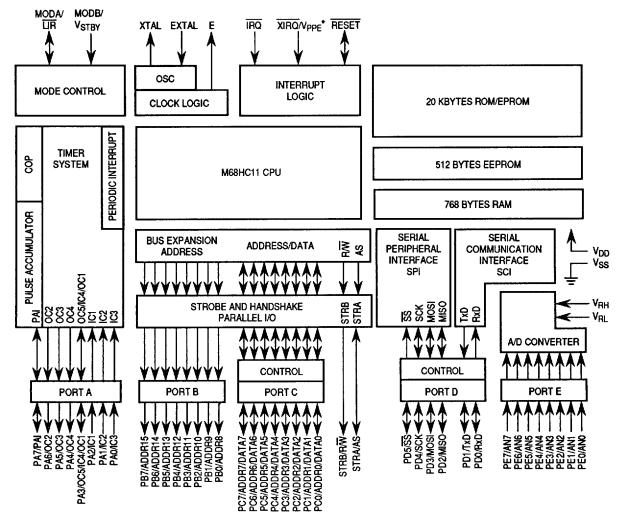

| Block Diagram7                                               | • |

| Operating Modes8                                             |   |

| Single-Chip Mode                                             |   |

| Bootstrap Mode8                                              |   |

| Special Test Mode8                                           |   |

| Expanded Operating Mode8                                     |   |

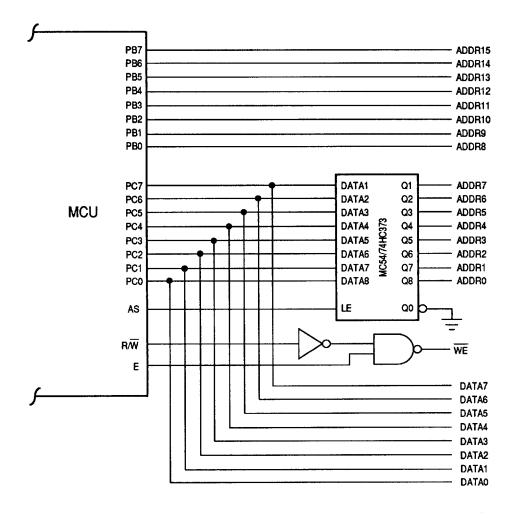

| Address/Data Demultiplexing9                                 |   |

| Mode Selection                                               |   |

| On-Chip Memory11                                             |   |

| Memory Map Diagram11                                         |   |

| MC68HC11E20 Register and Control Bit Assignments12           | • |

| RAM14                                                        | , |

| ROM/EPROM15                                                  | į |

| Electrically Erasable Programmable Read-Only Memory (EEPROM) | , |

| EEPROM Security Feature19                                    |   |

| Configuration Control Register (CONFIG)                      | I |

| Parallel Input/Output                                        |   |

| Resets and Interrupts27                                      |   |

| Main Timer                                                   |   |

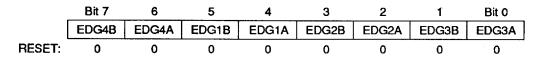

| Pulse Accumulator41                                          |   |

| Serial Communications Interface                              |   |

| Serial Peripheral Interface                                  |   |

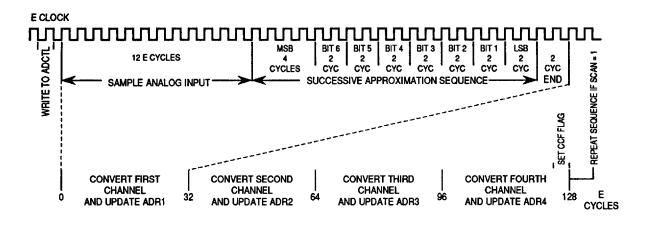

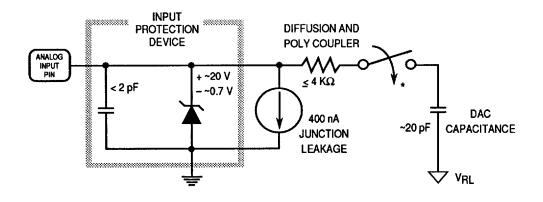

| Analog-to-Digital Converter                                  |   |

MC68HC11E20 MC68HC11E20TS/D

🖿 6367248 0137122 314 🛤

# **Register Index**

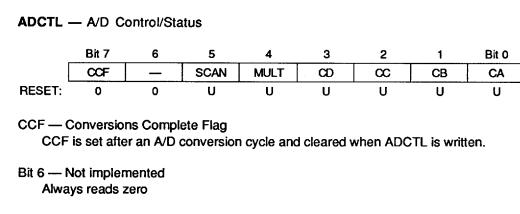

| ADCTL     | A/D Control/Status                                 | \$1030  | .57  |

|-----------|----------------------------------------------------|---------|------|

|           | A/D Results\$1031                                  | -       |      |

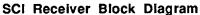

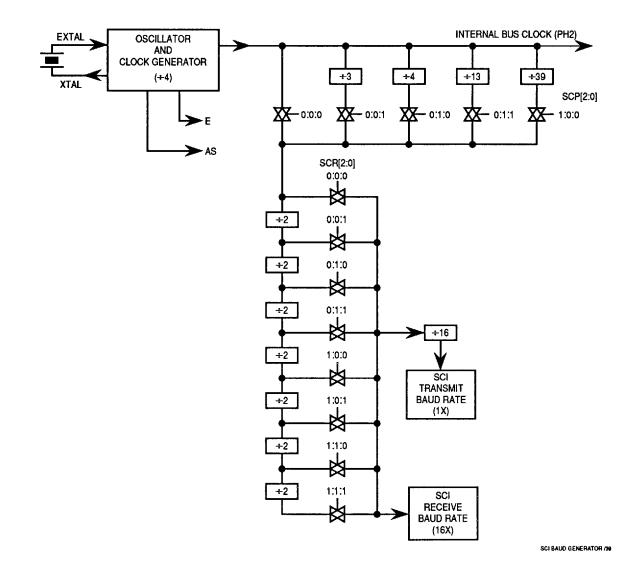

|           | Baud Rate Control Register                         |         |      |

|           | Block Protect                                      |         |      |

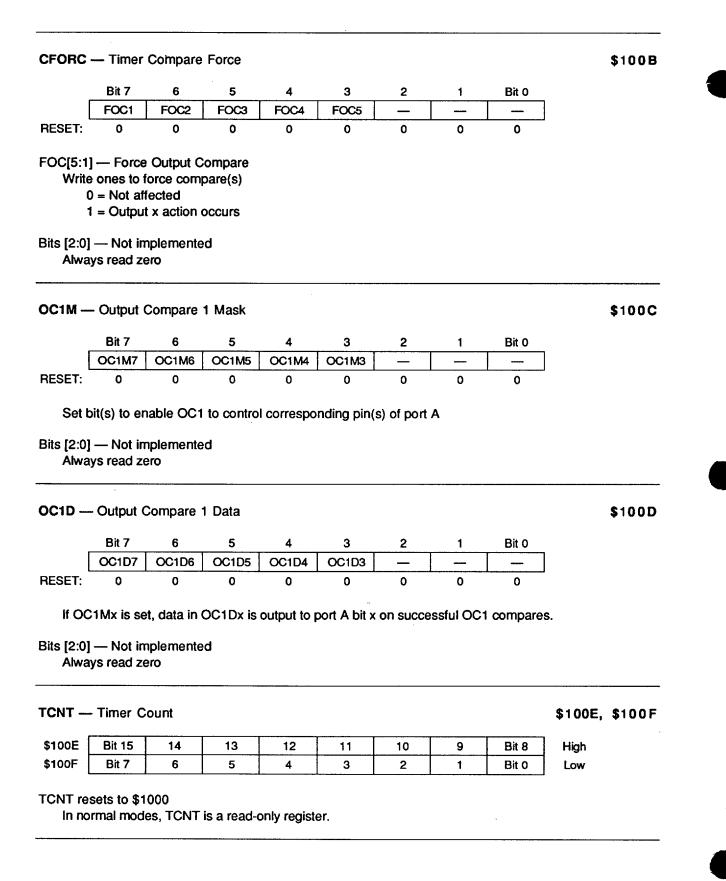

| CFORC     | Timer Compare Force                                | \$100B  | 34   |

|           | System Configuration Register                      |         |      |

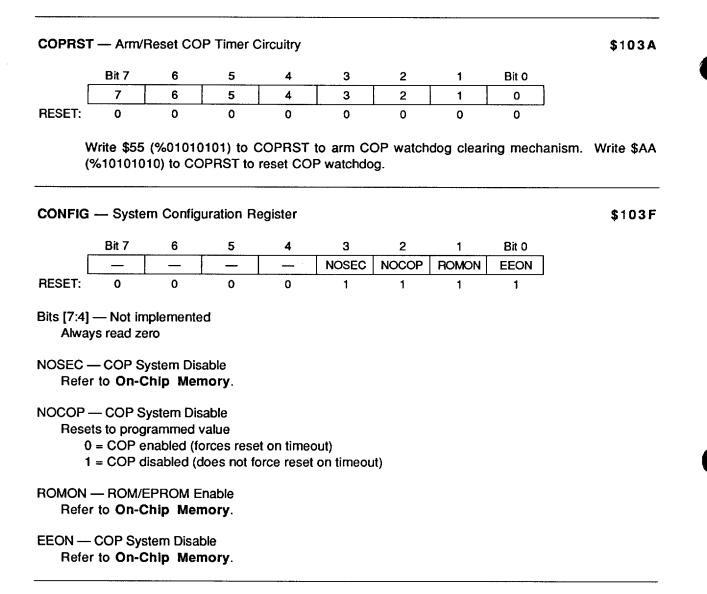

|           | Arm/Reset COP Timer Circuitry                      |         |      |

|           | Data Direction Register for Port C                 |         |      |

|           | Data Direction Register for Port D                 |         |      |

| EPROG     | EPROM Programming Control                          | .\$1036 | . 16 |

|           | Highest Priority I-Bit Interrupt and Miscellaneous |         |      |

|           | RAM and Register Mapping                           |         |      |

|           | Output Compare 1 Data                              |         |      |

|           | Output Compare 1 Mask                              |         |      |

|           | System Configuration Options                       |         |      |

|           | Pulse Accumulator Counter                          |         |      |

|           | Pulse Accumulator Control                          |         |      |

|           | Parallel I/O Control                               |         |      |

| PORTA     | Port A Data                                        | .\$1000 | . 23 |

|           | Port B Data                                        | •       |      |

| PORTC     | Port C Data                                        | .\$1003 | . 25 |

| PORTCL    | Port C Latched Data                                | .\$1005 | . 25 |

| PORTD     | Port D Data                                        | .\$1008 | 26   |

| PORTE     | Port E Data                                        | .\$100A | 26   |

| PPROG     | EEPROM Programming Control                         | .\$103B | 18   |

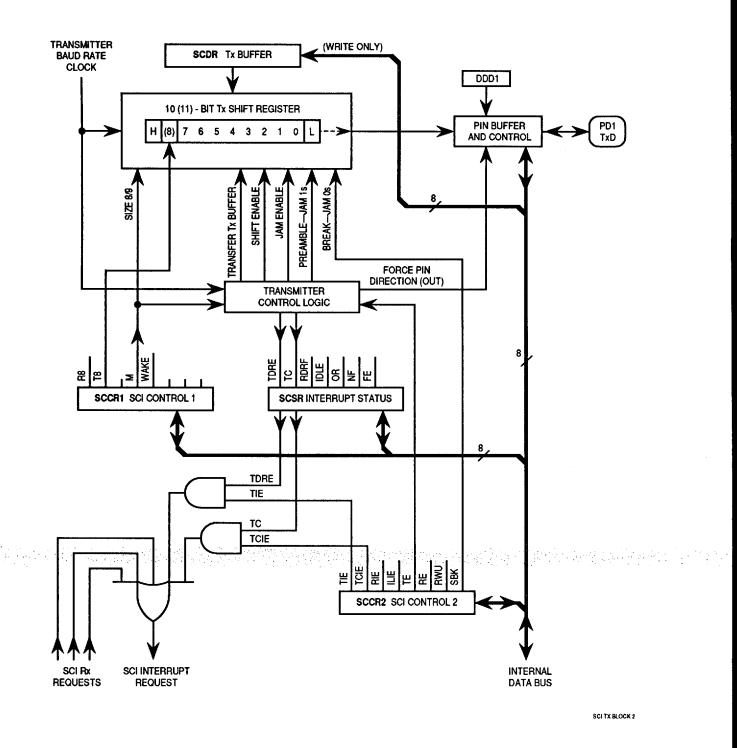

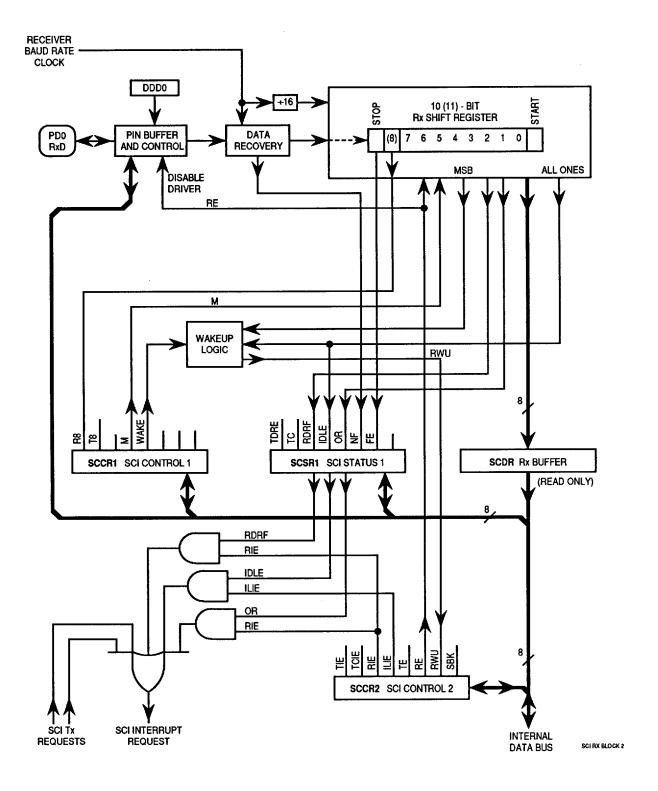

| SCCR1     | SCI Control Register 1                             | .\$102C | 49   |

| SCCR2     | SCI Control Register 2                             | .\$102D | 50   |

| SCDR      | SCI Data Register                                  | .\$102F | . 51 |

| SCSR      | SCI Status Register                                | .\$102E | 50   |

| SPCR      | SPI Control Register                               | .\$1028 | 53   |

|           | SPI Data Register                                  |         |      |

|           | SPI Status Register                                |         |      |

|           | Timer Count\$100E                                  |         |      |

|           | Timer Control 1                                    |         |      |

|           | Timer Control 2                                    |         |      |

|           | Timer Interrupt Flag 1                             |         |      |

|           | Timer Interrupt Flag 2                             |         |      |

|           | Timer Input Capture 4/Output Compare 5 \$101E      |         |      |

|           | Timer Input Capture\$1010                          |         |      |

|           | Timer Interrupt Mask 1                             |         |      |

|           | Timer Interrupt Mask 2                             |         |      |

| TOC1-TOC4 | Timer Output Compare\$1016-                        | -\$101D | 35   |

| Package     | Description | CONFIG | Frequency | Temperature       | MC Order Number  |  |  |                   |                  |               |                 |                   |                  |

|-------------|-------------|--------|-----------|-------------------|------------------|--|--|-------------------|------------------|---------------|-----------------|-------------------|------------------|

| 64-Pin QFP  | OTPROM      | \$0F   | 2 MHz     | - 40° to + 85° C  | MC68HC711E20CFU2 |  |  |                   |                  |               |                 |                   |                  |

|             |             |        |           | - 40° to + 105° C | MC68HC711E20VFU2 |  |  |                   |                  |               |                 |                   |                  |

|             |             |        |           | - 40° to + 125° C | MC68HC711E20MFU2 |  |  |                   |                  |               |                 |                   |                  |

|             |             |        | 3 MHz     | 0° to + 70° C     | MC68HC711E20FU3  |  |  |                   |                  |               |                 |                   |                  |

|             |             |        |           | - 40° to + 85° C  | MC68HC711E20CFU3 |  |  |                   |                  |               |                 |                   |                  |

| 52-Pin PLCC | OTPROM      | \$0F   | 2 MHz     | – 40° to + 85° C  | MC68HC711E20CFN2 |  |  |                   |                  |               |                 |                   |                  |

|             |             |        |           |                   |                  |  |  |                   |                  |               |                 | - 40° to + 105° C | MC68HC711E20VFN2 |

|             |             |        |           |                   |                  |  |  | - 40° to + 125° C | MC68HC711E20MFN2 |               |                 |                   |                  |

|             |             |        |           |                   |                  |  |  |                   | 3 MHz            | 0° to + 70° C | MC68HC711E20FN3 |                   |                  |

|             |             |        |           | - 40° to + 85° C  | MC68HC711E20CFN3 |  |  |                   |                  |               |                 |                   |                  |

| 52-Pin CLCC | EPROM       | \$0F   | 2 MHz     | - 40° to + 85° C  | MC68HC711E20CFS2 |  |  |                   |                  |               |                 |                   |                  |

| (Windowed)  |             |        |           | - 40° to + 105° C | MC68HC711E20VFS2 |  |  |                   |                  |               |                 |                   |                  |

|             |             |        |           | - 40° to + 125° C | MC68HC711E20MFS2 |  |  |                   |                  |               |                 |                   |                  |

|             |             |        | 3 MHz     | 0° to + 70° C     | MC68HC711E20FS3  |  |  |                   |                  |               |                 |                   |                  |

|             |             |        |           | - 40° to + 85° C  | MC68HC711E20CFS3 |  |  |                   |                  |               |                 |                   |                  |

# Standard Device Ordering Information

# Custom ROM Device Ordering Information

| Package     | Description      | Frequency | Temperature       | MC Order Number |

|-------------|------------------|-----------|-------------------|-----------------|

| 64-Pin QFP  | Custom ROM 2 MHz |           | - 40° to + 85° C  | MC68HC11E20CFU2 |

|             |                  |           | - 40° to + 105° C | MC68HC11E20VFU2 |

|             |                  |           | -40° to + 125° C  | MC68HC11E20MFU2 |

|             |                  | 3 MHz     | 0° to + 70° C     | MC68HC11E20FU3  |

|             |                  |           | - 40° to + 85° C  | MC68HC11E20CFU3 |

| 52-Pin PLCC | Custom ROM       | 2 MHz     | - 40° to + 85° C  | MC68HC11E20CFN2 |

|             |                  |           | - 40° to + 105° C | MC68HC11E20VFN2 |

|             |                  |           | -40° to + 125° C  | MC68HC11E20MFN2 |

|             |                  | 3 MHz     | 0° to + 70° C     | MC68HC11E20FN3  |

|             |                  |           | - 40° to + 85° C  | MC68HC11E20CFN3 |

\* VPPE APPLIES ONLY TO DEVICES WITH EPROM.

E20 84 PIN OFP

### Pin Assignments for 64-Pin Quad Flat Pack

MC68HC11E20 MC68HC11E20TS/D 63672480137125023 🎟

MOTOROLA 5

\* VPPE APPLIES ONLY TO DEVICES WITH EPROM.

E20 52 PIN PLCC

### Pin Assignments for 52-Pin PLCC/CLCC

MOTOROLA 6

6367248 OJ37J26 T6T 🔳

MC68HC11E20 MC68HC11E20TS/D

\* VPPE APPLIES ONLY TO DEVICES WITH EPROM.

E20 BLOCK

MC68HC11E20 Block Diagram

### **Operating Modes**

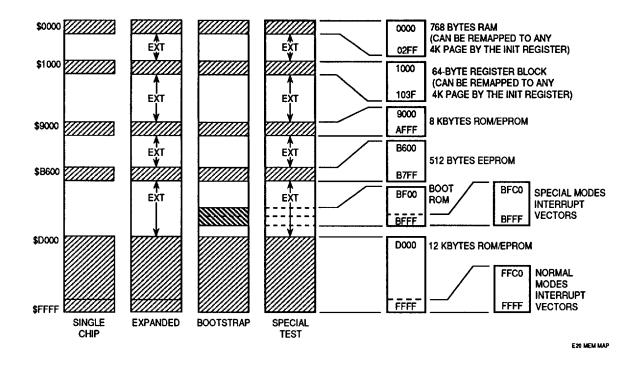

The MC68HC11E20 has four modes of operation. These modes directly affect the address space and the memory map differs for each of them. Refer to the memory map diagram.

### Single-Chip Mode

In single-chip operating mode, the MC68HC11E20 is a stand-alone microcontroller with no external address or data bus. Although the CPU can access the full 64-Kbyte address space, addressing is limited to on-chip resources. Portions of the 64-Kbyte space that are not occupied by the on-chip resources cannot be utilized. Refer to the memory map diagram.

### **Bootstrap Mode**

Bootstrap mode is a special variation of the single-chip mode. Bootstrap mode allows specialpurpose programs to be entered into internal RAM. When boot mode is selected at reset, a small bootstrap ROM becomes present in the memory map. Reset and interrupt vectors are located in this ROM at \$BFC0-\$BFFF. The bootstrap ROM contains a small program which initializes the SCI and allows the user to download a program of up to 768 bytes into on-chip RAM. After a fourcharacter delay, or after receiving the character for address \$02FF, control passes to the loaded program at \$0000. Refer to the memory map diagram.

#### **Special Test Mode**

Special test mode is used primarily for factory testing. In this operating mode, ROM/EPROM is removed from the address space and vectors are located at \$BFC0-\$BFFF.

### Expanded Operating Mode

In expanded operating mode, the MCU can access the full 64-Kbyte address space. The space includes the same on-chip memory addresses used for single-chip mode as well as addresses for external peripherals and memory devices. The expansion bus is made up of ports B and C, and control signals AS and R/W. The R/W (read/write) and AS (address strobe) allow the low-order address and the 8-bit data bus to be multiplexed on the same pins. During the first half of each bus cycle address information is present. During the second half of each bus cycle the pins become the bidirectional data bus. AS is an active-high latch enable signal for an external address latch. Address information is allowed through the transparent latch while AS is high and is latched when AS drives low. The address, R/W, and AS signals are active and valid for all bus cycles, including accesses to internal memory locations. The E-clock is used to enable external devices to drive data onto the internal data bus during the second half of a read bus cycle (E clock high). R/W controls the direction of data transfers. R/W drives low when data is being written to the internal data bus. R/W will remain low during consecutive data bus write cycles, such as when a double-byte store occurs. Notice that the write enable signal for an external memory is the NAND of the E clock and the inverted R/W signal. Refer to the example diagram of address and data demultiplexing.

ADDR/DATA DEMUX

#### Address/Data Demultiplexing

#### Mode Selection

Operating modes are selected by a combination of logic levels applied to two input pins (MODA and MODB) during reset. The logic level present (at the rising edge of reset) on these inputs is reflected in bits in the HPRIO register. After reset, the operating mode may be changed according to the table contained in the following description of the HPRIO register.

The function of internal read visibility/not E is determined by the state of the IRVNE bit and the mode selected at reset. When enabled, internal read visibility (IRV) causes the data from internal reads to be driven out the data bus. The user must be cautioned that even though the  $R/\overline{W}$  line suggests that the data bus is in a high-impedance state, data will be driven out each time an internal read occurs. The not E clock (NE) function of this bit determines whether the E clock is on or off. Refer to the description of IRVNE in HPRIO register.

| HPRIO - | HPRIO Highest Priority I-Bit Interrupt and Miscellaneous |       |                                         |        |       |       |       |       | \$103C       |

|---------|----------------------------------------------------------|-------|-----------------------------------------|--------|-------|-------|-------|-------|--------------|

|         | Bit 7                                                    | 6     | 5                                       | 4      | 3     | 2     | 1     | Bit 0 |              |

|         | RBOOT*                                                   | SMOD* | MDA*                                    | IRVNE* | PSEL3 | PSEL2 | PSEL1 | PSEL0 |              |

| RESET:  | 0                                                        | 0     | 0                                       | 0      | 0     | 1     | 1     | 0     | Single Chip  |

|         | 0                                                        | 0     | 1                                       | 0      | 0     | 1     | 1     | 0     | Expanded     |

|         | 1                                                        | 1     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 0      | 0     | 1     | 1     | 0     | Bootstrap    |

|         | 0                                                        | 1     | 1                                       | 0      | 0     | 1     | 1     | 0     | Special Test |

\*The reset values of RBOOT, SMOD, and MDA depend on the mode selected at power up.

#### RBOOT --- Read Bootstrap ROM

Valid only when SMOD is set (bootstrap or special test mode). Can only be written in special modes.

0 = Bootloader ROM disabled and not in map

1 = Bootloader ROM enabled and in map at \$BE00-\$BFFF

#### SMOD and MDA --- Special Mode Select and Mode Select A

The initial value of SMOD is the inverse of the logic level present on the MODB pin at the rising edge of reset. The initial value of MDA equals the logic level present on the MODA pin at the rising edge of reset. These two bits can be read at any time. They can be written anytime in special modes. MDA can only be written once in normal modes. SMOD cannot be set once it has been cleared.

| Inp  | uts  | Latched at Reset |      |     |  |  |

|------|------|------------------|------|-----|--|--|

| MODB | MODA | Mode             | SMOD | MDA |  |  |

| 1    | 0    | Single Chip      | 0    | 0   |  |  |

| 1    | 1    | Expanded         | 0    | 1   |  |  |

| 0    | 0    | Bootstrap        | 1    | 0   |  |  |

| 0    | 1    | Special Test     | 1    | 1   |  |  |

IRVNE — Internal Read Visibility/Not E

IRVNE can be written once in any mode. In expanded modes, IRVNE determines whether IRV is on or off. In special test mode, IRVNE is reset to one. In all other modes, IRVNE is reset to zero.

0 = No internal read visibility on external bus

1 = Data from internal reads is driven out the external data bus.

In single-chip modes this bit determines whether the E clock drives out from the chip.

0 = E is driven out from the chip.

1 = E pin is driven low. Refer to the following table.

| Mode         | IRVNE Out<br>of Reset | E Clock Out<br>of Reset | IRV Out of<br>Reset | IRVNE<br>Affects Only | IRVNE Can<br>Be Written |

|--------------|-----------------------|-------------------------|---------------------|-----------------------|-------------------------|

| Single Chip  | 0                     | On                      | Off                 | E                     | Once                    |

| Expanded     | 0                     | On                      | Off                 | IRV                   | Once                    |

| Bootstrap    | 0                     | On                      | Off                 | E                     | Once                    |

| Special Test | 1                     | On                      | On                  | IRV                   | Once                    |

PSEL[3:0] — Priority Select Bits [3:0]

Refer to Resets and Interrupts.

MC68HC11E20 MC68HC11E20TS/D

### **On-Chip Memory**

The MC68HC11E20 has 768 bytes RAM, 512 bytes EEPROM, and 20 Kbytes ROM. The MC68HC711E20 has EPROM replacing ROM. The following paragraphs describe the memory systems of these two MCUs.

### Memory Map and Register Block

The INIT and CONFIG registers control the presence and location of the registers, RAM, EEPROM, and ROM/EPROM in the 64 Kbyte CPU address space. The 64-byte register block originates at \$1000 after reset and can be placed at any 4K boundary (\$x000) by writing an appropriate value to the INIT register. The INIT register can be written only in the first 64 cycles after reset. Refer to the memory map diagram.

#### MC68HC11E20/MC68HC711E20 Memory Map

| The r                  | egister blo<br>Bit 7 | ock begins<br>6 | s at \$1000<br>5 | out of res | set and ca | in be rema<br>2 | apped to a  | iny 4K boi<br>Bit 0 | undary.       |

|------------------------|----------------------|-----------------|------------------|------------|------------|-----------------|-------------|---------------------|---------------|

| \$1000                 | PA7                  | PA6             | PA5              | PA4        | PA3        | PA2             | PA1         | PA0                 | PORTA         |

| \$1001                 |                      |                 |                  |            |            |                 |             |                     | Reserved      |

| \$1002                 | STAF                 | STAI            | CWOM             | HNDS       | OIN        | PLS             | EGA         | INVB                | PIOC          |

| \$1003                 | PC7                  | PC6             | PC5              | PC4        | PC3        | PC2             | PC1         | PC0                 | PORTC         |

| \$1004                 | PB7                  | PB6             | PB5              | PB4        | PB3        | PB2             | PB1         | PB0                 | PORTB         |

| \$1005                 | PCL7                 | PCL6            | PCL5             | PCL4       | PCL3       | PCL2            | PCL1        | PCL0                | PORTCL        |

| \$1006                 | Reserved             |                 |                  |            |            |                 |             |                     |               |

| \$1007                 | DDC7                 | DDC6            | DDC5             | DDC4       | DDC3       | DDC2            | DDC1        | DDC0                | DDRC          |

| \$1008                 | —                    |                 | PD5              | PD4        | PD3        | PD2             | PD1         | PD0                 | PORTD         |

| \$1009                 | _                    | _               | DDD5             | DDD4       | DDD3       | DDD2            | DDD1        | DDD0                | DDRD          |

| \$100A                 | PE7                  | PE6             | PE5              | PE4        | PE3        | PE2             | PE1         | PE0                 | PORTE         |

| \$100B                 | FOC1                 | FOC2            | FOC3             | FOC4       | FOC5       |                 |             |                     | CFORC         |

| \$100C                 | OC1M7                | OC1M6           | OC1M5            | OC1M4      | OC1M3      |                 | —           | _                   | OC1M          |

| \$100D                 | OC1D7                | OC1D6           | OC1D5            | OC1D4      | OC1D3      | _               | <del></del> | _                   | OC1D          |

| \$100E                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TCNT (High)   |

| \$100F                 | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TCNT (Low)    |

| \$1010                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TIC1 (High)   |

| <b>\$1</b> 01 <b>1</b> | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TIC1 (Low)    |

| <b>\$1</b> 012         | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TIC2 (High)   |

| <b>\$1</b> 013         | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TIC2 (Low)    |

| \$1014                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TIC3 (High)   |

| \$1015                 | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TIC3 (Low)    |

| \$1016                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TOC1 (High)   |

| <b>\$1</b> 017         | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TOC1 (Low)    |

| \$1018                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TOC2 (High)   |

| \$1019                 | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TOC2 (Low)    |

| \$101A                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TOC3 (High)   |

| \$101B                 | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TOC3 (Low)    |

| \$101C                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TOC4 (High)   |

| <b>\$1</b> 01D         | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TOC4 (Low)    |

| \$101E                 | Bit 15               | 14              | 13               | 12         | 11         | 10              | 9           | Bit 8               | TI4/O5 (High) |

| \$101F                 | Bit 7                | 6               | 5                | 4          | 3          | 2               | 1           | Bit 0               | TI4/O5 (Low)  |

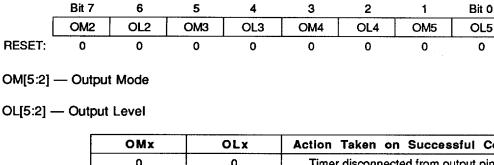

| \$1020                 | OM2                  | OL2             | OM3              | OL3        | OM4        | OL4             | OM5         | OL5                 | TCTL1         |

# MC68HC11E20 Register and Control Bit Assignments (1 of 2)

|                |          |       | •     |       |        | •     | •     | •            |          |

|----------------|----------|-------|-------|-------|--------|-------|-------|--------------|----------|

|                | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        |          |

| <b>\$1</b> 021 | EDG4B    | EDG4A | EDG1B | EDG1A | EDG2B  | EDG2A | EDG3B | EDG3A        | TCTL2    |

| \$1022         | OC1I     | OC2I  | OC3I  | OC4I  | 14/051 | IC1I  | IC2I  | IC3I         | TMSK1    |

| \$1023         | OC1F     | OC2F  | OC3F  | OC4F  | 14/05F | IC1F  | IC2F  | IC3F         | TFLG1    |

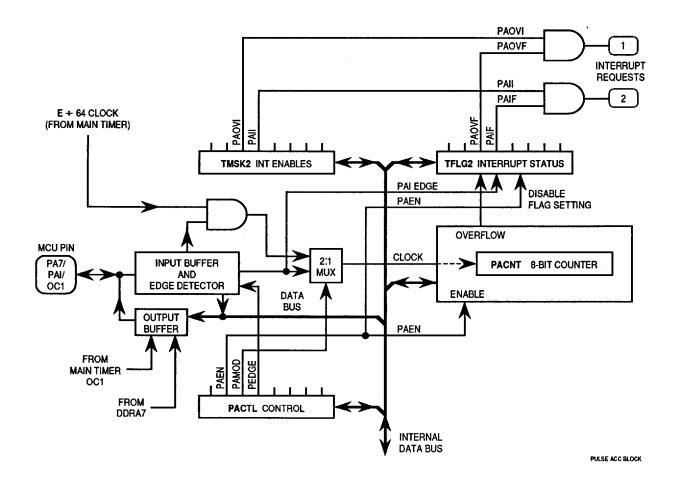

| \$1024         | ΤΟΙ      | RTII  | PAOVI | PAII  | _      |       | PR1   | PR0          | TMSK2    |

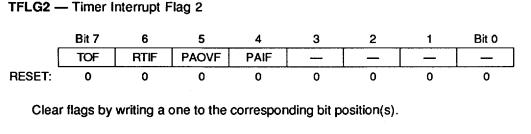

| \$1025         | TOF      | RTIF  | PAOVF | PAIF  |        | —     |       |              | TFLG2    |

| \$1026         | DDRA7    | PAEN  | PAMOD | PEDGE | DDRA3  | I4/05 | RTR1  | RTR0         | PACTL    |

| \$1027         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | PACNT    |

| \$1028         | SPIE     | SPE   | DWOM  | MSTR  | CPOL   | CPHA  | SPR1  | SPR0         | SPCR     |

| \$1029         | SPIF     | WCOL  | _     | MODF  |        | -     |       | —            | SPSR     |

| \$102A         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | SPDR     |

| \$102B         | TCLR     | SCP2  | SCP1  | SCP0  | RCKB   | SCR2  | SCR1  | SCR0         | BAUD     |

| \$102C         | R8       | T8    |       | М     | WAKE   |       |       | _            | SCCR1    |

| \$102D         | TIE      | TCIE  | RIE   | ILIE  | ΤE     | RE    | RWU   | SBK          | SCCR2    |

| \$102E         | TDRE     | тс    | RDRF  | IDLE  | OR     | NF    | FE    | _            | SCSR     |

| \$102F         | R7/T7    | R6/T6 | R5/T5 | R4/T4 | R3/T3  | R2/T2 | R1/T1 | R0/T0        | SCDR     |

| \$1030         | CCF      |       | SCAN  | MULT  | CD     | 30    | CB    | CA           | ADCTL    |

| \$1031         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | ADR1     |

| \$1032         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | ADR2     |

| \$1033         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | ADR3     |

| \$1034         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | ADR4     |

| \$1035         | _        | _     | —     | PTCON | BPRT3  | BPRT2 | BPRT1 | <b>BPRT0</b> | BPROT    |

| \$1036         | MBE      | _     | ELAT  | EXCOL | EXROW  | T1    | T0    | PGM          | EPROG*   |

| \$1037         |          |       |       |       |        |       |       |              | Reserved |

| \$1038         |          |       |       |       |        |       |       |              | Reserved |

| \$1039         | ADPU     | CSEL  | IRQE  | DLY   | CME    |       | CR1   | CR0          | OPTION   |

| \$103A         | Bit 7    | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0        | COPRST   |

| \$103B         | ODD      | EVEN  | _     | BYTE  | ROW    | ERASE | EELAT | EEPGM        | PPROG    |

| \$103C         | RBOOT    | SMOD  | MDA   | IRVNE | PSEL3  | PSEL2 | PSEL1 | PSEL0        | HPRIO    |

| \$103D         | RAM3     | RAM2  | RAM1  | RAM0  | REG3   | REG2  | REG1  | REG0         | INIT     |

| \$103E         | TILOP    | _     | OCCR  | CBYP  | DISR   | FCM   | FCOP  | TCON         | TEST1    |

| <b>\$1</b> 03F |          | _     |       |       | NOSEC  | NOCOP | ROMON | EEON         | CONFIG   |

| * MC68H        | IC711E20 | only. |       |       |        |       |       |              |          |

# MC68HC11E20 Register and Control Bit Assignments (2 of 2)

\* MC68HC711E20 only.

#### RAM

The 768 bytes of on-chip RAM are located at \$0000 after reset. If RAM and registers are both mapped to the same 4K boundary, the register block starts at \$x000, and RAM starts at \$x040. In this case, registers overlap the first \$3F RAM addresses and that portion of RAM becomes inaccessible. Remapping is accomplished by writing appropriate values to the INIT register.

When power is removed from the MCU, RAM contents may be preserved using the MODB/V<sub>STBY</sub> pin. A 5-volt nominal power source applied to this pin protects all 768 bytes of RAM.

### **INIT** — RAM and Register Mapping

|        | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|-------|------|------|------|------|------|------|-------|

|        | RAM3  | RAM2 | RAM1 | RAM0 | REG3 | REG2 | REG1 | REG0  |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

Can be written only once in first 64 cycles out of reset in normal modes or at any time in special mode.

#### RAM[3:0] — Internal RAM Map Position

These bits determine the upper four bits of the RAM address. At reset RAM is mapped to \$0000. Refer to the memory map diagram.

### REG[3:0] — 128-Byte Register Block Map Position

These bits determine the upper four bits of the register space address. At reset registers are mapped to \$1000. Refer to the memory map diagram.

\$103D

#### **ROM/EPROM**

The MC68HC711E20 has 20 Kbytes of ultraviolet-erasable EPROM (OTPROM in a nonwindowed package). The MC68HC11E20 has 20 Kbytes of mask-programmed ROM. The ROMON control bit in the CONFIG register controls the presence of ROM/EPROM in the memory map. In special test, bootstrap, and single-chip modes, ROMON = 1 out of reset and the 20 Kbytes of ROM/EPROM is enabled and located in two blocks. The two blocks are 8 Kbytes and 12 Kbytes in size. The 8-Kbyte block is located at \$9000–AFFF and the 12-Kbyte block is located at \$D000–FFFF. In single-chip mode the ROM/EPROM is enabled, regardless of the value in the CONFIG register. To use the ROM/EPROM in expanded mode, begin in single-chip mode, then change to expanded mode by setting the MDA bit in HPRIO register.

EPROM can be programmed in any operating mode — special test, bootstrap, expanded, or single chip. Programming is accomplished through the EPROG register. Programming EPROM requires an external 12.25 volt nominal power supply (VPPE).

To program the EPROM, complete the following steps using the EPROG register:

- 1. Set the ELAT bit in EPROG register.

- 2. Write data to the desired address.

- 3. Turn on programming voltage by setting the PGM bit in EPROG register.

- 4. Delay for 10 ms or more, as appropriate.

- 5. Clear the PGM bit in EPROG to turn off the programming voltage.

- 6. Clear the EPROG register to reconfigure the EPROM address and data buses for normal operation.

Although the external 12.25 V programming voltage must be applied to the XIRQ/VPPE pin during EPROM programming, it should be equal to  $V_{DD}$  before verifying the data that was just programmed. It should equal  $V_{DD}$  during normal operation also. The XIRQ/VPPE pin has a high voltage detect circuit that inhibits assertion of the ELAT bit when programming voltage is at low levels.

### CAUTION

If the MCU is used in any operating mode while high voltage (12.25 V nominal) is present on the XIRQ/VPPE pin, the IRQ/CE pin must be pulled high to avoid accidental programming or corruption of EPROM contents. After programming an EPROM location, IRQ/CE must also be pulled high before the address and data are changed to program the next location.

| EPROG       | — Eproi    | M Progra                | amming Co              | ontrol                     |                                            |            |         |            | \$1036                                     |

|-------------|------------|-------------------------|------------------------|----------------------------|--------------------------------------------|------------|---------|------------|--------------------------------------------|

|             | Bit 7      | 6                       | 5                      | 4                          | 3                                          | 2          | 1       | Bit 0      |                                            |

|             | MBE        |                         | ELAT                   | EXCOL                      | EXROW                                      | <b>T</b> 1 | то      | PGM        | ]                                          |

| RESET:      | 0          | 0                       | 0                      | 0                          | 0                                          | 0          | 0       | 0          | ,                                          |

| Whe<br>with | address bi | -byte pro<br>it 5 = 0 a | ogramming<br>nd addres | g is enable<br>s bit 5 = 1 | ed, address<br>both get pr<br>an only be v | ogramm     | ed. MBE | can be rea | t care so that bytes<br>ad in any mode and |

- 0 = EPROM array configured for normal programming

- 1 = Program two bytes with the same data

- Bit 6 Not Implemented

Always reads zero

### ELAT --- EPROM Latch Control

When ELAT = 1, writes to EPROM cause address and data to be latched and the EPROM cannot be read. ELAT can be read any time. ELAT can be written any time except when PGM = 1; then the write to ELAT will be disabled.

- 0 = EPROM address and data bus configured for normal reads

- 1 = EPROM address and data bus configured for programming

### EXCOL — Select Extra Columns

- 0 = User array selected

- 1 = User array is disabled and extra columns are accessed at bits [7:0]. Addresses use bits [13:5] and bits [4:0] are don't care. EXCOL can only be read in special modes and always returns zero in normal modes. EXCOL can be written in special modes only.

### EXROW - Select Extra Rows

- 0 = User array selected

- 1 = User array is disabled and two extra rows are available. Addresses use bits [7:0] and bits [13:8] are don't care. EXROW can only be read in special modes and always returns zero in normal modes. EXROW can be written in special modes only.

### T[1:0] — EPROM Test Mode Select Bits

| <b>T1</b> | T2 | Function Selected |  |  |  |  |

|-----------|----|-------------------|--|--|--|--|

| 0         | 0  | Normal Mode       |  |  |  |  |

| 0         | 1  | Reserved          |  |  |  |  |

| 1         | 0  | Gate Stress       |  |  |  |  |

| 1         | 1  | Drain Stress      |  |  |  |  |

These bits allow selection of either gate stress or drain stress test modes. They can be read only in special modes and always read zero in normal modes. T[1:0] can only be written in special modes.

### PGM — EPROM Programming Voltage Enable

0 = Programming voltage to EPROM array disconnected

1 = Programming voltage to EPROM array connected

PGM can be read any time and can only be written when ELAT = 1.

MOTOROLA 16

6367248 0137136 909 🖿

MC68HC11E20 MC68HC11E20TS/D

### Electrically Erasable Programmable Read-Only Memory (EEPROM)

The 512 bytes of EEPROM in the MC68HC711E20 are located at \$B600 through \$B7FF. The EEON bit in the CONFIG register controls whether the EEPROM is present in the memory map. When EEON =1 (erased state), the EEPROM is enabled; when EEON = 0, the EEPROM is disabled and not present in the memory map. EEON is reset to the value last programmed into CONFIG.

An on-chip charge pump develops the high voltage required for programming and erasing. When the frequency of the E clock is less than 1 MHz, select the internal clock source to drive the EEPROM charge pump by writing one to the CSEL bit in the OPTION register.

Programming and erasing the EEPROM is controlled by the PPROG register, and dependent upon the block protect (BPROT) register value.

To erase the EEPROM, ensure that the proper bits of the BPROT register are cleared, then complete the following steps using the PPROG register:

- 1. Set the ERASE, EELAT, and appropriate BYTE and ROW bits in PPROG register.

- 2. Write to the appropriate EEPROM address with any data. Row erase only requires a write to any location in the row. Bulk erase is done by writing to any location in the array.

- 3. Set the ERASE, EELAT, EEPGM, and appropriate BYTE and ROW bits in PPROG register.

- 4. Delay for 10 ms or more, as appropriate.

- 5. Clear the EEPGM bit in PPROG to turn off the programming voltage.

- Clear the PPROG register to reconfigure the EEPROM address and data buses for normal operation.

To program the EEPROM, ensure the proper bits of the BPROT register are cleared and use the PROG register to complete the following steps:

- 1. Set the EELAT bit in PPROG register.

- 2. Write data to the desired address.

- 3. Set EEPGM bit in PPROG.

- 4. Delay for 10 ms or more, as appropriate.

- 5. Clear the EEPGM bit in PPROG to turn off the programming voltage.

- 6. Clear the PPROG register to reconfigure the EEPROM address and data buses for normal operation.

#### CAUTION

Since it is possible to perform other operations while the EEPROM program/erase operation is in progress, it is common to start the operation and then return to the main program until the 10 ms is completed. When the EELAT bit is set at the beginning of a program/erase operation, the EEPROM is electronically removed from the memory map; thus, it is not accessible during the program/erase cycle. Care must be taken to ensure that EEPROM resources will not be needed by any routines in the code during the 10 ms program/erase time.

| PPROG — EEPROM Programming Control                                                                   |                                     |      |   |      |     |       |       |       |  |  |

|------------------------------------------------------------------------------------------------------|-------------------------------------|------|---|------|-----|-------|-------|-------|--|--|

|                                                                                                      | Bit 7                               | 6    | 5 | 4    | 3   | 2     | 1     | Bit 0 |  |  |

|                                                                                                      | ODD                                 | EVEN | — | BYTE | ROW | ERASE | EELAT | EEPGM |  |  |

| RESET: 0 0 0 0 0 0 0 0                                                                               |                                     |      |   |      |     |       |       |       |  |  |

| ODD — Program Odd Rows in Half of EEPROM (TEST)<br>EVEN — Program Even Rows in Half of EEPROM (TEST) |                                     |      |   |      |     |       |       |       |  |  |

| Bit 5 — Not implemented<br>Always reads zero                                                         |                                     |      |   |      |     |       |       |       |  |  |

| BYTE -                                                                                               | BYTE — Byte/Other EEPROM Erase Mode |      |   |      |     |       |       |       |  |  |

ROW - Row/All EEPROM Erase Mode

| BYTE | ROW | Action                     |

|------|-----|----------------------------|

| 0    | 0   | Bulk Erase (All 512 Bytes) |

| 0    | 1   | Row Erase (16 Bytes)       |

| 1    | 0   | Byte Erase                 |

| 1    | 1   | Byte Erase                 |

ERASE — Erase/Normal Control for EEPROM

0 = Normal read or program mode

1 = Erase mode

EELAT - EEPROM Latch Control

- 0 = EEPROM address and data bus configured for normal reads

- 1 = EEPROM address and data bus configured for programming or erasing

EEPGM — EEPROM Programming Voltage Enable

- 0 = Programming voltage to EEPROM array disconnected

- 1 = Programming voltage to EEPROM array connected

MC68HC11E20 MC68HC11E20TS/D

### \$103B

**BPROT** — Block Protect

|        | Bit 7 | 6 | 5 | 4     | 3     | 2     | 1     | Bit 0        |

|--------|-------|---|---|-------|-------|-------|-------|--------------|

|        | _     |   |   | PTCON | BPRT3 | BPRT2 | BPRT1 | <b>BPRT0</b> |

| RESET: | 0     | 0 | 0 | 1     | 1     | 1     | 1     | 1            |

PTCON — Protect for CONFIG

0 = CONFIG register can be programmed or erased normally

1 = CONFIG register cannot be programmed or erased

### BPRT[3:0] — Block Protect Bits for EEPROM

0 = Protection disabled for associated block

1 = Protection enabled for associated block

| Bit Name | Block Protected | Block Size |

|----------|-----------------|------------|

| BPRT0    | \$B600-\$B61F   | 32 Bytes   |

| BPRT1    | \$B620-\$B65F   | 64 Bytes   |

| BPRT2    | \$8660-\$86DF   | 128 Bytes  |

| BPRT3    | \$B6E0-\$B7FF   | 288 Bytes  |

### NOTE

Block protect register bits can be written to zero (protection disabled) within 64 cycles of a reset in normal modes, or at any time in special modes. Block protect register bits can be written to one (protection enabled) at any time.

#### **EEPROM Security Feature**

Although it is not an operating mode, the security feature affects how the MCU behaves in certain modes. When the optional security feature has been specified prior to manufacture and enabled via the NOSEC bit in CONFIG, the MCU is restricted to operation in single-chip modes only. When the NOSEC bit equals zero, the MCU ignores the state of the MODA pin during reset. This allows the MCU to be operated in single-chip and bootstrap modes only. These modes of operation do not allow external visibility of the internal address and data buses. Although the security feature can easily be disabled when in bootstrap mode, the bootloader firmware residing in bootstrap ROM checks to see if the NOSEC bit is clear. If NOSEC is clear (security enabled), the bootloader program first erases the entire EEPROM array then writes \$FF to all locations in RAM. The program then verifies that these two steps have been completed. If they have not, they are repeated. Once these steps have been verified, the reset sequence continues and the device is brought into bootstrap mode as usual. For more information refer to *M68HC11 Reference Manual* (M68HC11RM/AD).

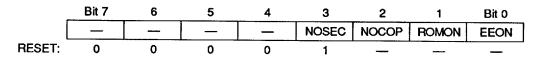

### **Configuration Control Register (CONFIG)**

The CONFIG register is used to define several system functions. CONFIG is made up of EEPROM cells and static working latches. The operation of the MCU is controlled directly by these latches and not the actual EEPROM byte. When programming the CONFIG register, the EEPROM byte is being accessed. When the CONFIG register is being read, the static latches are being accessed.

The CONFIG register can be read at any time. The value read is the one latched from the EEPROM cells during the last reset sequence. A new value programmed into this register cannot be read until a subsequent reset occurs. Unused bits always read as ones.

In normal modes (SMOD = 0), CONFIG bits can only be written using the EEPROM programming sequence, and are neither readable nor active until latched via the next reset. In special modes (SMOD = 1), CONFIG bits can be written at any time.

### **CONFIG** — System Configuration Register

\$103F

#### Bits [7:4] — Not implemented

Always read zero

#### NOSEC — Security Mode Disable

The security feature, a mask option, protects the contents of RAM and EEPROM by restricting the operation of a protected device to single-chip modes. Changing to other modes while the device is protected forces erasure of all RAM and EEPROM contents. This option must be specified before manufacture.

0 = RAM/EEPROM security mode enabled

1 = RAM/EEPROM security mode disabled

NOCOP — COP Watchdog Timer Disable

Refer to Resets and Interrupts.

#### **ROMON** — ROM/EPROM Enable

If SMOD = 1, this bit can be written at any time. If SMOD = 0, this bit **cannot** be written. In single-chip mode ROMON is forced to one out of reset. In special test, boot, and normal expanded modes, ROMON is forced to zero out of reset.

0 = 20 Kbytes of ROM/EPROM removed from the memory map

1 = 20 Kbytes of ROM/EPROM present in the memory map

### EEON --- EEPROM Enable

0 = 512 bytes EEPROM is removed from the memory map

1 = 512 bytes EEPROM is present in the memory map

### **Parallel Input/Output**

The MC68HC11E20 has up to 38 input/output lines, depending on the operating mode. The data bus of this microcontroller is multiplexed with the low-order address outputs on port C.

Port A has three input-only pins, three output-only pins, and two bidirectional I/O pins. Port A shares functions with the timer system.

Port B is an 8-bit output-only port in single-chip mode, and the high-order address bus in expanded modes.

Port C is an 8-bit bidirectional port in single-chip mode, and the multiplexed low-order address and data bus in expanded modes.

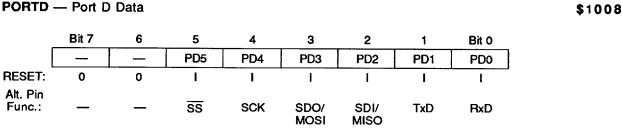

Port D, a 6-bit bidirectional port, shares functions with the serial systems (SCI and SPI).

Port E is an 8-bit input-only port that shares functions with the A/D converter system.

Simple and full handshake input and output functions are available on ports B and C lines in single-chip mode. The following is a description of the handshake functions.

In simple strobed mode, port B is a strobed output port and port C is a latching input port. The two activities are available simultaneously.

The STRB output is pulsed for two E-clock periods each time there is a write to the PORTB register. The INVB bit in the PIOC register controls the polarity of STRB pulses. Port C levels are latched into the alternate port C latch (PORTCL) register on each assertion of the STRA input. STRA edge select, flag, and interrupt enable bits are located in the PIOC register. Any or all of the port C lines can still be used as general-purpose I/O while in strobed input mode.

Full handshake modes involve port C pins and the STRA and STRB lines. Input and output handshake modes are supported, and output handshake mode has a three-stated variation. STRA is an edge detecting input, and STRB is a handshake output. Control and enable bits are located in the PIOC register.

In full input handshake mode, the MCU uses STRB as a ready line to an external system. Port C logic levels are latched into PORTCL when the STRA line is asserted by the external system. The MCU then negates STRB. The MCU reasserts STRB after the PORTCL register is read. A mix of latched inputs, static inputs, and static outputs is allowed on port C, differentiated by the data direction bits and use of the PORTC and PORTCL registers.

In full output handshake mode, the MCU writes data to PORTCL which, in turn, asserts the STRB output to indicate that data is ready. The external system reads port C and asserts the STRA input to acknowledge that data has been received.

In the three-state variation of output handshake mode, lines intended as three-state handshake outputs are configured as inputs by clearing the corresponding DDRC bits. The MCU writes data to PORTCL and asserts STRB. The external system responds by activating the STRA input, which forces the MCU to drive the data in PORTCL out on all of the port C lines. The mode variation does not allow part of port C to be used for static inputs while other port C pins are being used for handshake outputs. Refer to the PIOC register description for further information.

The following table is a summary of the configuration and features of each port.

| Port   | Input<br>Pins | Output<br>Pins | Bidirectional<br>Pins | Shared Functions                          |  |

|--------|---------------|----------------|-----------------------|-------------------------------------------|--|

| Port A | 3             | 3              | 2                     | Timer                                     |  |

| Port B | —             | 8              |                       | High Order Address                        |  |

| Port C | —             |                | 8                     | Data Bus/Low Order<br>Address/General I/O |  |

| Port D | —             | _              | 6                     | SCI and SPI                               |  |

| Port E | 8             |                |                       | A/D Converter                             |  |

Port pin function is mode dependent. Do not confuse pin function with the electrical state of the pin at reset. Port pins are either driven to a specified logic level or are configured as high impedance inputs. I/O pins configured as high-impedance inputs have port data that is indeterminate. The contents of the corresponding latches are dependent upon the electrical state of the pins during reset. In port descriptions, an "I" indicates this condition. Port pins that are driven to a known logic level during reset are shown with a value of either one or zero. Some control bits are unaffected by reset. Reset states for these bits are indicated with a "U".

PIOC - Parallel I/O Control

|        | Bit 7 | 6    | 5    | 4    | 3   | 2   | 1   | Bit 0 |

|--------|-------|------|------|------|-----|-----|-----|-------|

|        | STAF  | STAI | CWOM | HNDS | OIN | PLS | EGA | INVB  |

| RESET: | 0     | 0    | 0    | 0    | 0   | U   | 1   | 1     |

\$1002

### STAF — Strobe A Interrupt Status Flag

STAF is set when the selected edge occurs on Strobe A and cleared by reading PIOC with STAF set followed by a PORTCL read (simple strobed or full input handshake mode) or PORTCL write (output handshake mode).

- 0 = No Active Edge Detected

- 1 = Selected Active Edge Detected

- STAI Strobe A Interrupt Enable Mask

- 0 = STAF does not request interrupt

- 1 = STAF requests interrupt

- CWOM Port C Wired-OR Mode (affects all eight port C pins)

- 0 = Port C outputs are normal CMOS outputs

- 1 = Port C outputs are open-drain outputs

### HNDS — Handshake Mode

22

0 = Simple strobe mode

1 = Full input or output handshake mode

### OIN — Output or Input Handshake Select

HNDS must be set to one for this bit to have meaning.

- 0 = Input handshake

- 1 = Output handshake

### PLS — Pulse/Interlocked Handshake Operation

HNDS must be set to one for this bit to have meaning. Once activated, strobe B stays active until the selected edge of strobe A is detected when interlocked handshake is selected.

0 = Interlocked handshake

- 1 = Pulsed handshake (Strobe B pulses high for two E-clock cycles.)

- EGA Active Edge for Strobe A

- 0 = STRA falling edge selected

- 1 = STRA rising edge selected

#### INVB --- Invert Strobe B

- 0 = Active level is logic zero

- 1 = Active level is logic one

### Parallel I/O Control

|                                     | STAF<br>Clearing<br>Sequence                       | HNDS | OIN | PLS                                                  | EGA                                  | Port B                                                                                          | Port C                                                     |

|-------------------------------------|----------------------------------------------------|------|-----|------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Simple<br>strobed<br>mode           | Read PIOC<br>with STAF = 1<br>then read<br>PORTCL  | 0    | x   | x                                                    |                                      | Inputs latched<br>into PORTCL<br>on any<br>active edge<br>on STRA                               | STRB pulses<br>on writes to<br>PORTB                       |

| Full<br>input<br>handshake<br>mode  | Read PIOC<br>with STAF = 1<br>then read<br>PORTCL  | 1    | 0   | 0 = STRB<br>active level<br>1 = STRB<br>active pulse |                                      | Inputs latched<br>into PORTCL<br>on any<br>active edge<br>on STRA                               | Normal output<br>port, unaffected<br>in handshake<br>modes |

| Full<br>output<br>handshake<br>mode | Read PIOC<br>with STAF = 1<br>then write<br>PORTCL | 1    | 1   | 0 = STRB<br>active level<br>1 = STRB<br>active pulse | O Port C Driven  Follow DDRC  Follow | Driven as outputs if<br>STRA at active<br>level; follows<br>DDRC if STRA not<br>at active level | port, unaffected<br>in handshake                           |

PORTA — Port A Data

|                    | Bit 7 | 6   | 5   | 4   | 3       | 2   | 1   | Bit 0 |

|--------------------|-------|-----|-----|-----|---------|-----|-----|-------|

| ſ                  | PA7   | PA6 | PA5 | PA4 | PA3     | PA2 | PA1 | PA0   |

| RESET:             | J     | 0   | 0   | 0   |         | I   | ļ   | I     |

| Alt. Pin<br>Func.: | PAI   | OC2 | OC3 | OC4 | OC5/IC4 | IC1 | IC2 | IC3   |

| And/or:            | OC1   | OC1 | OC1 | OC1 | OC1     | —   |     |       |

\$1000

: 🛋 6367248 0137143 049 🖿

| PACTL — Pulse Accumulator Control                                     |                                                                               |           |                         |        |           |             |            |       |        |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------|-------------------------|--------|-----------|-------------|------------|-------|--------|--|--|--|--|

|                                                                       | Bit 7                                                                         | 6         | 5                       | 4      | 3         | 2           | 1          | Bit 0 |        |  |  |  |  |

|                                                                       | DDRA7                                                                         | PAEN      | PAMOD                   | PEDGE  | DDRA3     | I4/05       | RTR1       | RTR0  |        |  |  |  |  |

| RESET:                                                                | 0                                                                             | 0         | 0                       | 0      | 0         | 0           | 0          | 0     |        |  |  |  |  |

| (                                                                     | — Data Di<br>0 = Input o<br>1 = Output                                        | oniy      | <sup>r</sup> Port A Bit | 7      |           |             |            |       |        |  |  |  |  |

|                                                                       | PAEN — Pulse Accumulator System Enable<br>Refer to <b>Pulse Accumulator</b> . |           |                         |        |           |             |            |       |        |  |  |  |  |

| PAMOD — Pulse Accumulator Mode<br>Refer to <b>Pulse Accumulator</b> . |                                                                               |           |                         |        |           |             |            |       |        |  |  |  |  |

|                                                                       | — Puise A<br>er to <b>Puis</b> e                                              |           | -                       | ontrol |           |             |            |       |        |  |  |  |  |

| Ovei<br>(                                                             | — Data Dii<br>rridden if a<br>) = Input<br>I = Output                         | In output |                         | -      | configure | d to contro | ol the PA3 | pin.  |        |  |  |  |  |

|                                                                       | Input Cap<br>r to Main                                                        |           | tput Comp               | bare 5 |           |             |            |       |        |  |  |  |  |

| RTR[1:0] — Real-Time Interrupt (RTI) Rate<br>Refer to Main Timer.     |                                                                               |           |                         |        |           |             |            |       |        |  |  |  |  |

| PORTB                                                                 | — Port B                                                                      | Data      |                         | -      |           |             |            |       | \$1004 |  |  |  |  |

|                               | Bit 7    | 6        | 5        | 4        | 3        | 2        | 1        | Bit 0    |

|-------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

|                               | PB7      | PB6      | PB5      | PB4      | PB3      | PB2      | PB1      | PB0      |

| S. Chip<br>or Boot:<br>RESET: | PB7<br>0 | PB6<br>0 | PB5<br>0 | PB4<br>0 | PB3<br>0 | PB2<br>0 | PB1<br>0 | PB0<br>0 |

| Expan.<br>or Test:            | ADDR15   | ADDR14   | ADDR13   | ADDR12   | ADDR11   | ADDR10   | ADDR9    | ADDR8    |

In single-chip or bootstrap modes, port B pins are general-purpose outputs. In expanded or special test modes, port B pins are high order address outputs. In PROG mode, port B pins are high-order address inputs.

MOTOROLA 24 : 📰 6367248 0137144 T85 📰

|                                                                                      | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |  |

|--------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

|                                                                                      | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |  |  |

| S. Chip<br>or Boot:<br>RESET:                                                        | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |  |  |

| Expan.                                                                               | DATAZ | DATAC |       | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |  |  |

| or Test:                                                                             | DATA7 | DATA6 | DATA5 | DATA4 | DATAS | DATAZ | DATA  | DATAO |  |  |

| In single-chip and bootstrap modes, port C pins reset to high impedance inputs (DDRC |       |       |       |       |       |       |       |       |  |  |

IC bits are set to zero). It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. In expanded and special test modes, port C pins are multiplexed address/data bus and the port C register address is treated as an external memory location.

PORTCL — Port C Latched Data

PORTC - Port C Data

|        | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|-------|------|------|------|------|------|------|-------|

|        | PCL7  | PCL6 | PCL5 | PCL4 | PCL3 | PCL2 | PCL1 | PCLO  |

| RESET: | 1     | I    | I    | I    | I    | I    | ł    | ł     |

PORTCL is used in the handshake clearing mechanism. When an active edge occurs on the STRA pin, port C data is latched into the PORTCL register. Reads of this register return the last value latched into PORTCL and clear STAF flag (following a read of PIOC with STAF set).

DDRC — Data Direction Register for Port C

|        | Bit 7 6 |      | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|---------|------|------|------|------|------|------|-------|

| 1      | DDC7    | DDC6 | DDC5 | DDC4 | DDC3 | DDC2 | DDC1 | DDC0  |

| RESET: | 0       | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

DDC[7:0] — Data Direction for Port C

0 = Input

1 = Output

In handshake output mode, DDRC bits select the three-stated output option (DDCx = 1).

\$1007

In all modes, port D bits [5:0] can be used either for general-purpose I/O, or with the SCI and SPI subsystems. During reset, port D pins PD[5:0] are configured as high impedance inputs (DDRD bits cleared).

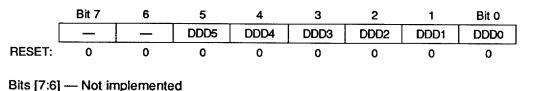

Always read zero

DDD[5:0] - Data Direction for Port D

0 = Input

1 = Output

PORTE - Port E Data

| _                  | Bit 7 | 6   | 5   | 4   | 3   | 2   | 1   | Bit 0 |

|--------------------|-------|-----|-----|-----|-----|-----|-----|-------|

|                    | PE7   | PE6 | PE5 | PE4 | PE3 | PE2 | PE1 | PE0   |

| RESET:             | I     | 1   | 1   | 1   | I   | l   | I   |       |

| Alt. Pin<br>Func.: | AN7   | AN6 | AN5 | AN4 | AN3 | AN2 | AN1 | AN0   |

🔳 6367248 O137146 858 🎟

Port E has eight general-purpose input pins and shares functions with the A/D converter system. When any port E pins are being used as A/D inputs, PORTE should not be read during the sample portion of an A/D conversion.

MC68HC11E20 MC68HC11E20TS/D

\$100A

### **Resets and Interrupts**

The MC68HC11E20 has 3 reset vectors and 18 interrupt vectors. The reset vectors are as follows:

- RESET, or Power-On Reset

- Clock Monitor Fail

- COP Failure

The 18 interrupt vectors service 23 interrupt sources (3 nonmaskable, 20 maskable). The three nonmaskable interrupt vectors are as follows:

- XIRQ Pin (X-Bit Interrupt)

- Illegal Opcode Trap

- Software Interrupt

On-chip peripheral systems generate maskable interrupts, which are recognized only if the global interrupt mask bit (I) in the condition code register (CCR) is clear. Maskable interrupts are prioritized according to a default arrangement; however, any one source can be elevated to the highest maskable priority position by a software-accessible control register, HPRIO. The HPRIO register can be written at any time, provided the I bit in the CCR is set.

Twenty interrupt sources in the MC68HC11E20 are subject to masking by a global interrupt mask bit (I bit in the CCR). In addition to the global I bit, all of these sources, except the external interrupt (IRQ) pin, are controlled by local enable bits in control registers. Most interrupt sources in the M68HC11 have separate interrupt vectors; therefore, there is usually no need for software to poll control registers to determine the cause of an interrupt.

For some interrupt sources, such as the SCI interrupts, flags are automatically cleared during the normal course of responding to the interrupt requests. For example, the RDRF flag in the SCI system is cleared by an automatic clearing mechanism consisting of a read of the SCI status register while RDRF is set, followed by a read of the SCI data register. The normal response to an RDRF interrupt request would be to read the SCI status register to check for receive errors, then to read the received data from the SCI data register. These two steps satisfy the automatic clearing mechanism without requiring any special instructions.

🔲 6367248 0137147 794 🖩

| Vector Address      | Interrupt Source                                     | CCR<br>Mask Bit | Local Mask | Priority<br>(1=High) |

|---------------------|------------------------------------------------------|-----------------|------------|----------------------|

| FFC0, C1 – FFD4, D5 | Reserved                                             | —               | —          | —                    |

| FFD6, D7            | SCI Serial System                                    | 1               |            |                      |

|                     | SCI Receive Data Register Full                       | ]               | RIE        |                      |

|                     | <ul> <li>SCI Receiver Overrun</li> </ul>             |                 | RIE        | 23                   |

|                     | <ul> <li>SCI Transmit Data Register Empty</li> </ul> |                 | TIE        |                      |

|                     | SCI Transmit Complete                                |                 | TCIE       |                      |

|                     | SCI Idle Line Detect                                 |                 | ILIE       |                      |

| FFD8, D9            | SPI Serial Transfer Complete                         | I               | SPIE       | 22                   |

| FFDA, DB            | Pulse Accumulator Input Edge                         |                 | PAII       | 21                   |

| FFDC, DD            | Pulse Accumulator Overflow                           | 1               | PAOVI      | 20                   |

| FFDE, DF            | Timer Overflow                                       | 1               | TOI        | 19                   |

| FFE0, E1            | Timer Input Capture 4/Output Compare 5               |                 | I4/O5I     | 17                   |

| FFE2, E3            | Timer Output Compare 4                               | 1               | OC4I       | 14                   |

| FFE4, E5            | Timer Output Compare 3                               | 1               | OC3I       | 13                   |

| FFE6, E7            | Timer Output Compare 2                               | 1               | OC2I       | 12                   |

| FFE8, E9            | Timer Output Compare 1                               | 1               | OC1I       | 11                   |

| FFEA, EB            | Timer Input Capture 3                                | I               | IC3I       | 10                   |

| FFEC, ED            | Timer Input Capture 2                                | I               | IC2I       | 9                    |

| FFEE, EF            | Timer Input Capture 1                                | 1               | IC1I       | 8                    |

| FFF0, F1            | Real-Time Interrupt                                  | I               | RTII       | 7                    |

| FFF2, F3            | Parallel I/O Handshake                               | I               | None       | 6                    |

|                     | IRQ (External Pin)                                   | I               | None       | 5                    |

| FFF4, F5            |                                                      | X               | None       | 4                    |

| FFF6, F7            | Software Interrupt                                   | None            | None       | *                    |

| FFF8, F9            | lllegal Opcode Trap                                  | None            | None       | *                    |

| FFFA, FB            | COP Failure                                          | None            | NOCOP      | 3                    |

| FFFC, FD            | Clock Monitor Fail                                   | None            | CME        | 2                    |

| FFFE, FF            | RESET                                                | None            | None       | 1                    |

Refer to the following table for interrupt and reset vector assignments.

\* Same level as an instruction

|          | Bit 7            | 6           | 5            | 4            | 3           | 2          | 1           | Bit 0        |        |  |

|----------|------------------|-------------|--------------|--------------|-------------|------------|-------------|--------------|--------|--|

|          | ADPU             | CSEL        | IRQE*        | DLY*         | CME         | ·          | CR1*        | CR0*         |        |  |

| RESET:   | 0                | 0           | 0            | 1            | 0           | 0          | 0           | 0            |        |  |

| * Can be | written only     | once in fi  | rst 64 cycle | s out of res | et in norma | l mode, or | at any time | in special r | modes. |  |

|          |                  |             |              |              |             |            |             |              |        |  |

| ADPU -   | - Analog-te      | o-Digital ( | Converter I  | Power Up     |             |            |             |              |        |  |

|          | -                | -           | igital Co    | •            |             |            |             |              |        |  |

|          |                  | •           | <b>v</b>     |              |             |            |             |              |        |  |

| CSEL -   | Clock Se         | lect        |              |              |             |            |             |              |        |  |

| Refe     | r to Ana         | loa-to-D    | igital Co    | nverter.     |             |            |             |              |        |  |

|          |                  | -           | •            |              |             |            |             |              |        |  |

| IRQE —   | IRQ Selec        | t Edae-S    | ensitive C   | nly          |             |            |             |              |        |  |

|          | ) = Low le       | •           |              | ,            |             |            |             |              |        |  |

|          | 1 = Falling      | -           |              |              |             |            |             |              |        |  |

|          | Caning           | , oago .o.  | oognition    |              |             |            |             |              |        |  |

| DLY — E  | Enable Os        | cillator St | artup Dela   | y on Exit fi | rom STOP    | ,          |             | ×.           |        |  |

|          |                  |             | delay on e   |              |             |            |             |              |        |  |

|          |                  |             | lay enable   |              |             | )          |             |              |        |  |

|          |                  |             | ,            | ·            |             |            |             |              |        |  |

| CME —    | Clock Mor        | nitor Enat  | ole          |              |             |            |             |              |        |  |

|          | ) = Clock        | monitor d   | isabled; sl  | ow clocks    | can be us   | ed         |             |              |        |  |

|          |                  |             | d clocks ca  |              |             |            |             |              |        |  |

|          |                  |             |              |              |             |            |             |              |        |  |

| Bit 2 I  | Not impler       | nented      |              |              |             |            |             |              |        |  |

|          | ,<br>iys reads : |             |              |              |             |            |             |              |        |  |

|          | .,               |             |              |              |             |            |             |              |        |  |

|          |                  | imer Rate   | Select       |              |             |            |             |              |        |  |

| CR[1:0]  |                  |             |              |              |             |            |             |              |        |  |

| CR[1:0]  | 001 11           |             |              |              |             |            |             |              |        |  |

Ħ

| CR[1:0] | Divide<br>E/2 <sup>15</sup> By | XTAL = 4.0 MHz<br>Timeout<br>0/+32.8 ms | XTAL = 8.0 MHz<br>Timeout<br>–0/+16.4 ms | XTAL = 12.0 MHz<br>Timeout<br>-0/+10.9 ms |

|---------|--------------------------------|-----------------------------------------|------------------------------------------|-------------------------------------------|

| 00      | 1                              | 32.768 ms                               | 16.384 ms                                | 10.923 ms                                 |

| 01      | 4                              | 131.072 ms                              | 65.536 ms                                | 43.691 ms                                 |

| 10      | 16                             | 524.288 ms                              | 262.140 ms                               | 174.76 ms                                 |

| 11      | 64                             | 2.097 sec                               | 1.049 sec                                | 699.05 ms                                 |

|         | E=                             | 1.0 MHz                                 | 2.0 MHz                                  | 3.0 MHz                                   |

.

MC68HC11E20 MC68HC11E20TS/D

|         | Bit 7    | 6           | 5         | 4           | 3           | 2             | 1     | Bit 0 |

|---------|----------|-------------|-----------|-------------|-------------|---------------|-------|-------|

|         | RBOOT*   | SMOD*       | MDA*      | IRVNE*      | PSEL3       | PSEL2         | PSEL1 | PSEL0 |