## 查询uPD1708AG供应商

# MOS INTEGRATED CIRCUIT

# **μPD1708AG**

# SINGLE-CHIP MICROCOMPUTER WITH BUILT-IN RPESCALER, PLL FREQUENCY SYNTHESIZER AND LCD DRIVER

The µPD1708 is a 4-bit CMOS microcomputer for digital tuning, which incorporates a prescaler that can be operated up to 150 MHz, a PLL frequency synthesizer and an LCD driver (1/2 duty; 1/2 bias) into one chip.

Its CPU provides the functions of 4-bit parallel addition/subtraction (AD and SU instructions), logical operation (EXL instruction), multiple bit test (TMT instruction), carry F/F set/reset (STC instruction) and timer function.

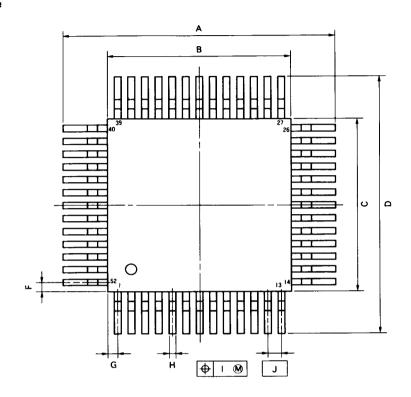

The µPD1708 is composed of a 52-pin flat package on which a number of input/output ports controllable by the powerful I/O instructions (IN and OUT) and input ports for the key switch are provided. WWW.DZSG.

#### **FEATURES**

- A 4-bit microcomputer for digital tuning

- Built-in prescaler (150 MHz, MAX.), PLL frequency synthesizer and LCD driver

- Single power supply of 5 V±10 %

- Low power consumption CMOS Easy backup of data memory (RAM) (by CE pin)

- Program memory (ROM): 16 bits x 1,528 steps

- Data memory (RAM): 4 bits x 96 words

- A variety of powerful instruction sets (all of one-word instruction)

- Instruction execution time: 33.3 μs (with 4.5 MHz crystal)

- A rich set of addition & subtraction instructions (12 addition and 12 subtraction instructions)

- Power composite judgement instructions (TMT, TMF)

- Storage-to-storage data transfer at the same row address

- Indirect transfer between registers (MVRD and MVRS instructions)

- 16 powerful general registers (on RAM space)

- Single stack level

- Built-in LCD driver (1/2 duty, 1/2 bias driven, frame frequency; 100 Hz)

- Built-in PLA (Programmable Logic Array: User programmable) for display purpose (LCD pattern)

- Clock stop by instruction (CKSTP instruction; power current of 10 μA or less)

- 12 powerful I/O ports (PA<sub>3</sub> to PA<sub>0</sub>: setting of input/output by one bit each, PB<sub>3</sub> to PB<sub>0</sub> and PC<sub>3</sub> to PC<sub>0</sub>; for output only)

- Input ports for key input (K<sub>3</sub> to K<sub>0</sub>)

- Superpower I/O instructions (IN, OUT)

- Test of status of input and output ports (TPT, TPF instructions)

- Built-in timer F/F (settable every 125 ms; easy timer setting)

- Built-in interval pulse output (internal output; test by pulse: TIP instructions every 5 ms (200 Hz, duty 60 %))

- Test of locked condition of PLL (TUL instruction)

- Transfer of data of rate and method of frequency division and reference frequency to PLL by single instruction (PLL instruction)

- Independent frequency input pin for AM and FM (maximum input frequency; 40 MHz (HF mode) for VCOL

(AM) pin and 150 MHz (VHF mode) for VCOH (FM) pin)

- Two program-selectable method of frequency division, pulse-swallowing process and direct process (VHF, HF and MF mode).

- Two independent error out pins (EO<sub>1</sub> and EO<sub>2</sub> pins)

- Program selection of 7 different reference frequencies (1 kHz, 5 kHz, 6.25 kHz, 9 kHz, 10 kHz, 12.5 kHz and 25 kHz)

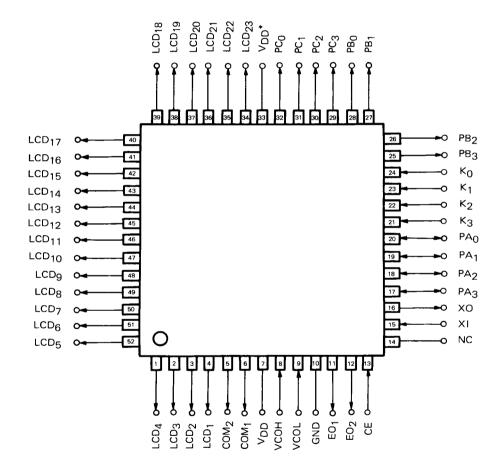

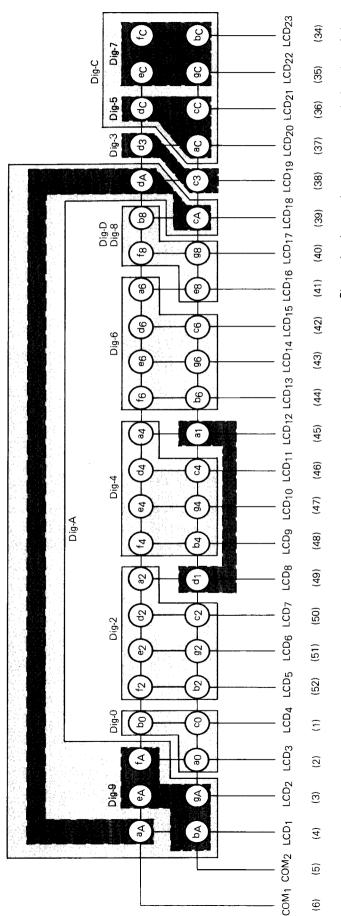

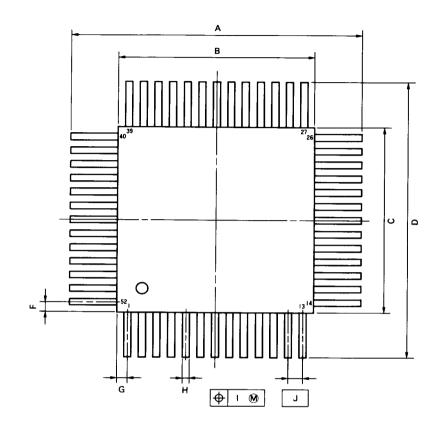

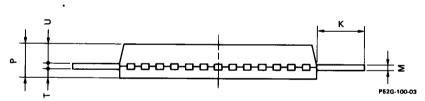

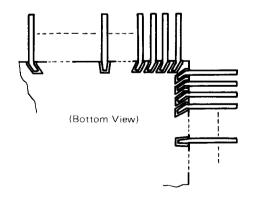

# PIN CONFIGURATION (Top View)

NC: No Connection

\* It is connected with 7 pin in the chip.

NOTE: In case of engineering sample (ceramic package), cap is connected with 7 pin, and 33 pin is NC.

# PIN DESCRIPTION

| PIN NO.                        | SYMBOL                                                         | NAME                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OUTPUT<br>TYPE    |

|--------------------------------|----------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

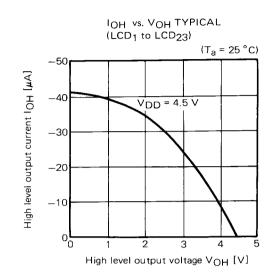

| 34<br>to<br>52<br>1<br>to<br>4 | LCD <sub>23</sub> to LCD <sub>5</sub> LCD4 to LCD <sub>1</sub> | LCD<br>Segment<br>Output   | These are the output pins of segment signals to the LCD panel. A maximum of 46 dots can be displayed by the matrixes of COM <sub>1</sub> and COM <sub>2</sub> , and the output to these pins can be made by the execution of LCDD instruction. Hence the content of data memory (RAM) at a given address as designated by the 1st operand of each LCDD instruction is output to the digit of LCD matrix as designated by the 2nd operand (see sect. 4, LCD driver). If an odd digit is designated, the content of data memory as designated by the 1st operand is loaded on the segment PLA (programmable logic array) and then output to these pins via PLA. The segment PLA is capable of generating 32 different kinds of patterns (see sect. 5, PLA).  Note: The low level (display OFF mode) is automatically output when the power is turned on (VDD = low to high) or when the CKSTP instruction is executed. | CMOS<br>Push-pull |

| 5<br>6                         | COM <sub>2</sub><br>COM <sub>1</sub>                           | LCD<br>Common<br>Output    | They are the output pins of common signals to the LCD panel. A maximum of 46 dots can be displayed by the matrixes of LCD <sub>1</sub> through LCD <sub>23</sub> .  Three different values of GND, 1/2V <sub>DD</sub> and V <sub>DD</sub> are output at the cycle of 50 Hz (at the intervals of 5 ms each). The segment where a potential difference of ±V <sub>DD</sub> arises between any of these pins and any of LCD <sub>1</sub> through LCD <sub>23</sub> is turned on (see sect. 4, LCD driver).  Note: The low level (display OFF mode) is automatically output when the power is turned on (V <sub>DD</sub> = low to high) or when the CKSTP instruction is executed.                                                                                                                                                                                                                                       | CMOS<br>Push-pull |

| 7<br>33                        | V <sub>DD</sub>                                                | Power Supply               | This is the device power pin, and it supplies the voltage of 5 V±10 % while the device is in operation. The voltage can be lowered to 2.5 V if to hold the internal data memory (RAM) (as the CKSTP instruction is being executed). When the voltage of 0 to 4.5 V is supplied to this pin, the device is reset and the program starts from the address 0 (see sect. 1.5, timer F/F).  Note: No voltage needs be supplied to pins 7 nor 33 as both are connected inside the chip; both can be operated when either is voltage-supplied.                                                                                                                                                                                                                                                                                                                                                                              | _                 |

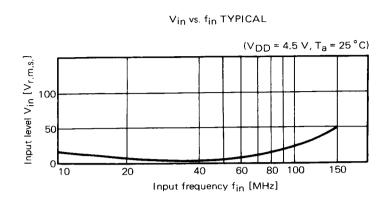

| 8                              | vсон                                                           | VCO (High)<br>Signal Input | This pin receives the local oscillation output (VCO output) from 10 to 150 MHz (0.5 V <sub>p-p</sub> MIN.). Provided inside the chip are a 1/2 fixed frequency-divided prescaler and two-modulus prescalers of 1/32 and 1/33. To determine the frequency-dividing ratio of programmable divider, it must be based on the frequency bisecting the local oscillation output (see sect. 2.5, SETTING OF PLL INFORMATION). The VCOH pin is automatically pulled down (GND) when the direct frequency dividing mode is selected and the HF instruction is executed under the pulse swallowing mode, that is, when the VCOL pin is selected. The input to this pin must be first cut by the capacitor as the AC amplifier is provided inside (see sect. 2.4, PLL register).                                                                                                                                                | Input             |

| PIN NO.  | SYMBOL                             | NAME                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OUTPUT<br>TYPE                                            |

|----------|------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|          |                                    |                           | This pin receives the local oscillation outputs (VCO outputs from 0.6 to 50 MHz (0.3 V <sub>p-p</sub> minimum: see sect. 2 PLL register). This pin is chosen and turned active with the direct frequency dividing mode is selected and HF instruction is executed under the pulse swallowing mode that the suprenum of frequency, which can be includiffers between the above two frequency dividing modes.    FREQUENCY   INPUT   INPUT   FRE-   DIVIDING   RATIO   RAT | 2.4,<br>nen<br>the<br>de.<br>out,                         |

| 9        | VCOL                               | VCO (Low)<br>Signal Input | Direct method 0.1 V <sub>p-p</sub> 0.59 to 20 16 to MIN. MHz (2 <sup>12</sup> -1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input                                                     |

|          |                                    |                           | Pulse swallowing 0.1 V <sub>p-p</sub> 0.6 to 40 method MIN. MHz 1024 to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                           |

|          |                                    |                           | instruction o.3 V <sub>p-p</sub> 0.6 to 50 (2 <sup>17</sup> -1) executed) MIN. MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |

|          |                                    |                           | In case the VHF instruction is executed under the pusuallowing mode, that is, when the VCOH pin is select the VCOL pin is automatically pulled down (GND). Nothe input needs be first cut by the capacitor as the amplifier is provided inside.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ed,<br>ote                                                |

| 10       | GND                                | Ground                    | The ground terminal of device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                         |

| 11<br>12 | EO <sub>1</sub><br>EO <sub>2</sub> | Error output              | The error output pins of PLL; the high level is out from the pins when the divided frequency of local oscillat frequency (VCO output) is higher than the refere frequency or the low level if it is lower. The terminals t to floating when both are equal. The outputs of pins input into the external LPF (low-pass filter) and apple to the varactor diode via LPF. The selection of eit pin is free to the user as both pins output the same was form.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | on<br>nce<br>urn<br>are CMOS<br>3-state                   |

| 13       | CE                                 | Chip enable               | The input pin of device select signals. To operate device normally, the high level needs be selected or the level if it is not to be used. While this pin is held at low level, PLL is inhibited or disabled. Any input less the 134 µs is not always acceptable. If the CKSTP instruction executed while it is used by the program and the CE is at the low level (the instruction is valid only if CE = low it works equal to the NOP instruction if CE = high), operation of internal clock generator and CPU are stopp thus holding the memory at a low current consumption µA or less). The display outputs (LCD1 to LCD23 at COM1, COM2) automatically turn to the display OFF modition (low level).  When CE pin is changed from the low to the high let the device is reset and the program is started from address (see sect. 1.5, Timer F/F). Also, the I/O port (Port Albecome input mode at this time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ow the nan n is pin or the ed, Input 110 and ode vel, s 0 |

| PIN NO.        | SYMBOL                                   | NAME                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OUTPUT<br>TYPE               |

|----------------|------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 14             | NC                                       | Non-<br>connection       | This pin cannot be used as it is not connected to the inside chip. But it can be connected any of OPEN, GND or VDD.                                                                                                                                                                                                                                                                                                                                                                                     | _                            |

| 15<br>16       | XI<br>XO                                 | X'tal                    | The connection pin of 4.5 MHz crystal oscillator. The oscillation frequency (4.5 MHz) must be adjusted while observing the XO terminal.                                                                                                                                                                                                                                                                                                                                                                 | Input (XI) CMOS Push-pull(XO |

| 17<br>to<br>20 | PA <sub>3</sub><br>to<br>PA <sub>0</sub> | Port A                   | These are the 4-bit I/O ports each of which allows to designate either the input or the output of 1 bit each, according to the content of data memory (RAM) at the address 1FH, known as the PAIO word. (see Notes 1 and 2 below)                                                                                                                                                                                                                                                                       | CMOS<br>Push-pull            |

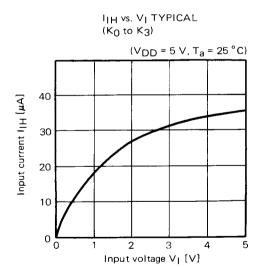

| 21<br>to<br>24 | K <sub>3</sub><br>to<br>K <sub>0</sub>   | Key return signal inputs | These are the 4-bit input ports to be used for the input of key matrix. When either the KIN or KI instruction is executed, the status of these pins are read into the data memory (RAM) as designated by the instruction's operand. As the key return signal source, port B and the two higher-order bits (PC3 and PC2) of port C can be used.                                                                                                                                                          | Input                        |

| 25<br>to<br>28 | PB <sub>3</sub><br>to<br>PB <sub>0</sub> | Port B                   | These are the 4-bit output ports to be used as the key return signal source of key matrix as the absorbing currents are designed extremely low due to the device configuration. As any of these ports is used as the key return signal source, all the external diodes can be eliminated. Note however that the proper low output cannot be output, depending on the driving circuit, if they are used as ordinary output ports; then a pull-down resistor must be connected. (see Note 1 and 3 below). | CMOS<br>Push-pull            |

| 29<br>to<br>32 | PC <sub>3</sub><br>to<br>PC <sub>0</sub> | Port C                   | These are the 4-bit output ports out of which PC3 and PC2 can be used as the key return signal source of key matrix, similar to the port B, as their absorbing currents are designed extremely low. (Note 1 and 3)                                                                                                                                                                                                                                                                                      | CMOS<br>Push-pull            |

- Note 1: In execution of the port control instruction (IN, OUT, SPB or RPB instruction), PA<sub>0</sub> is set against the lowermost bit of register or operand data and PB<sub>3</sub> against the highermost bit. It goes to port B or port C as well.

- Note 2: Port A (I/O port) turns to the input mode when the device is reset (VDD changes from low to high and CE from low to high) or when the CKSTP instruction is executed.

- Note 3: Unstable outputs are made to the output ports (ports B and C) when the power is turned on (VDD = low to high) so that it must be initialized by the program. The content of data remains unchanged even if the CE pin changes from the low to the high level and the CKSTP instruction is executed. Then both ports must be initialized by the program when it seems necessary.

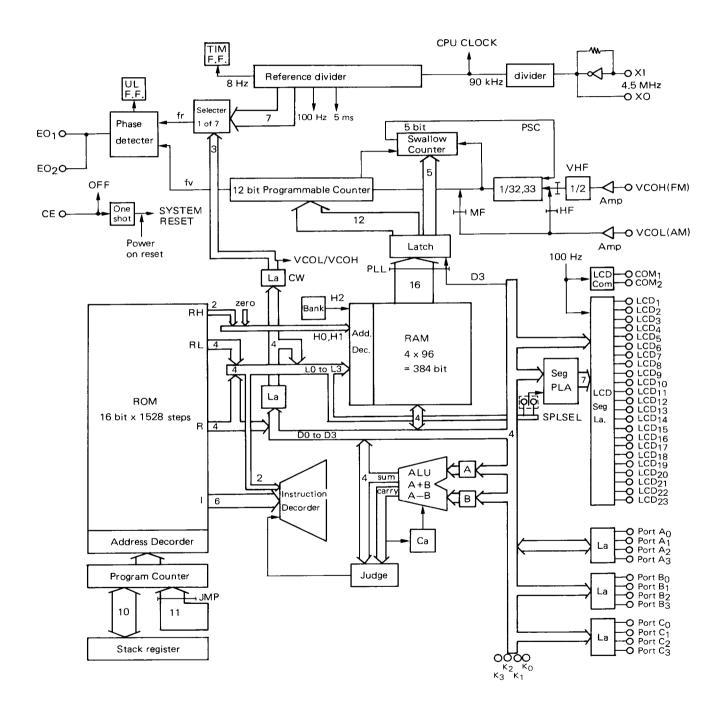

# **BLOCK DIAGRAM**

# **CONTENTS**

| 1. | CPU.    |                                     | 8  |

|----|---------|-------------------------------------|----|

|    | 1.1     | PROGRAM COUNTER                     | 8  |

|    | 1.2     | STACK REGISTER (SR)                 |    |

|    | 1.3     | PROGRAM MEMORY (ROM)                |    |

|    | 1.4     | DATA MEMORY (RAM)                   |    |

|    | 1.5     | TIMER F/F                           | 13 |

|    | 1.6     | INTERVAL PULSE (ITP)                | 16 |

|    | 1.7     | UNLOCK F/F (UL F/F)                 | 16 |

|    | 1.8     | CARRY F/F (C F/F)                   | 17 |

|    | 1.9     | BANK F/F (B F/F)                    | 17 |

|    | 1.10    | STATUS WORD                         |    |

|    |         |                                     |    |

| 2. | PLL.    |                                     |    |

|    | 2.1     | REFERENCE FREQUENCY GENERATOR (RFG) |    |

|    | 2.2     | PHASE DETECTOR (φ-DET)              | 18 |

|    | 2.3     | PROGRAMMABLE DIVIDER (P/D)          |    |

|    | 2.4     | PLL REGISTER                        |    |

|    | 2.5     | SETTING OF PLL INFORMATION          | 21 |

|    |         |                                     |    |

| 3. | PORT    |                                     |    |

|    | 3.1     | PORT A                              |    |

|    | 3.2     | PORT B & PORT C                     | 25 |

| _  |         | DRIVER                              | 26 |

| 4. | LCD     | DRIVER                              |    |

| 5. | PLA (   | PROGRAMMABLE LOGIC ALLAY)           | 32 |

|    | 5.1     | COMPOSITION OF SEGMENT PLA          |    |

|    | 5.2     | EXAMPLE OF PATTERNS OF SEGMENT PLA  |    |

|    | 5.3     | EXAMPLE OF DISPLAY PROGRAM          |    |

|    | 5.4     | EXAMPLE OF PLA PROGRAM              |    |

|    |         |                                     |    |

| 6. | INSTI   | RUCTION                             |    |

|    | 6.1     | INSTRUCTION SET                     |    |

|    | 6.2     | INSTRUCTIONS                        | 42 |

|    |         |                                     |    |

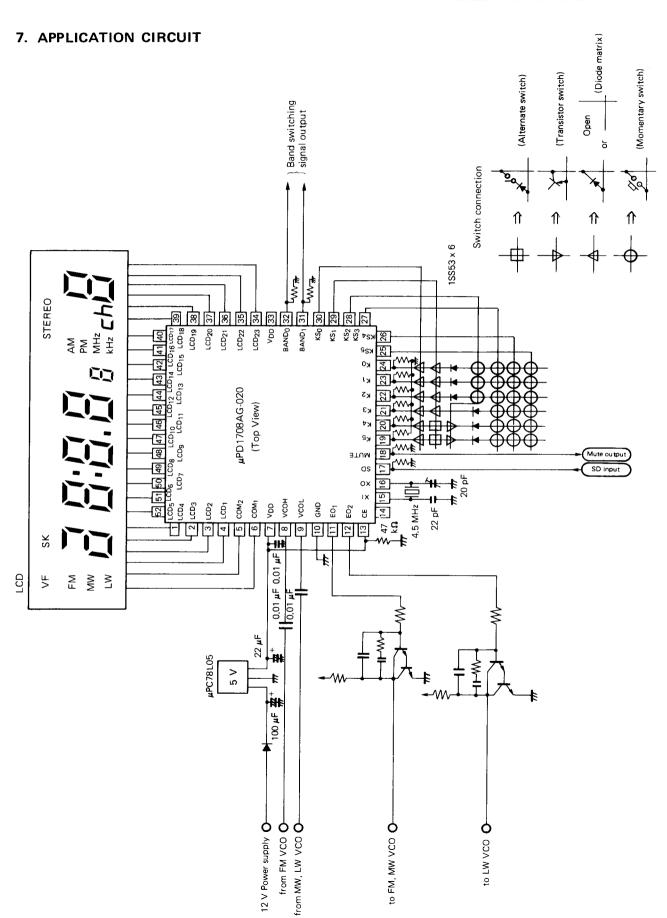

| 7. | APPL    | ICATION CIRCUIT                     | 48 |

| 0  | INIDI I | T/OUTPUT CIRCUIT OF TERMINAL        | 49 |

| ο. | INPU    | 1/00 FOT CINCOTT OF TERMINAL        | •  |

| 9. | ELEC    | TRICAL CHARACTERISTICS              | 54 |

| ٠. | 9.1     | ABSOLUTE MAXIMUM RATINGS            |    |

|    | 9.2     | RECOMMENDED OPERATING CONDITIONS    |    |

|    | 9.3     | DC CHARACTERISTICS                  |    |

|    | 9.4     | CAPACITANCE                         |    |

|    | 9.5     | AC CHARACTERISTICS                  |    |

|    |         |                                     |    |

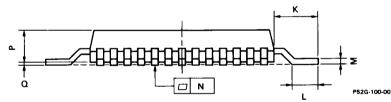

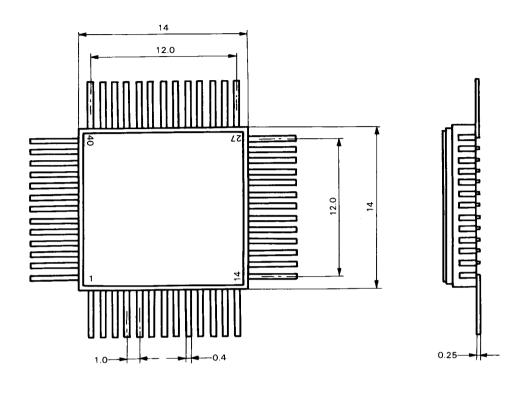

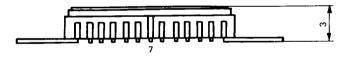

| 10 | O. PAC  | KAGE DIMENSIONS                     | 57 |

| 1  | 1. SUP  | PORT TOOLS                          | 60 |

|    |         |                                     |    |

# 1. CPU

#### 1.1 PROGRAM COUNTER

The program counter is composed of a 11-bit binary counter, and addresses the program memory (ROM), that is, the program.

The counter is generally increased by one every time one instruction has been executed, and it is loaded with the address as designated by the operand of a jump instruction or a subroutine call instruction when it is executed. When any skip instruction (e.g. ADS, TMT or RTS instruction) is executed, it designates the address of a command ensuing to the skip instruction, regardless of the content of skip condition. If the said condition requires the skip, the instruction subsequent to the skip instruction is considered NOP (no-operation). In other words, the address of next instruction can be designated after the execution of NOP.

- Note 1: The program counter of each of μPD1701, μPD1703, μPD1704, μPD1705, μPD1710 and μPD1711 (in the series having the ROM capacity less than 1K steps) is composed of 10 bits only.

- Note 2: Since the operand of the JMP instruction consists of ten bits, there are two types of JMP instructions in µPD1708 and PC<sub>10</sub> is set or reset depending on the operation code. These two JMP instructions have the same mnemonic code (JMP) so that the identity of these two instructions are judged by the assembler automatically. (See the Program Memory in Section 1.3) The CAL instruction is only one type. When the CAL instruction is executed, PC<sub>10</sub> is reset.

#### 1.2 STACK REGISTER (SR)

This register is composed of 1 x 11 bits and stores upon the execution of a subroutine call instruction the value adding one to the content of program counter or the return address (11 bits). The content of this stack register is loaded into the program counter by the execution of return instructions (RT, RTS) and returns into the main flow of program.

#### 1.3 PROGRAM MEMORY (ROM)

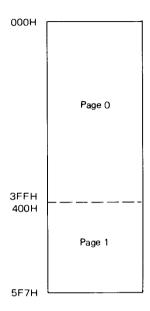

ROM is composed of 1,528 steps of 16 bits each and stores the programs. The applicable range of ROM addressing is 1,528 steps starting with 000H and ending with 5F7H.

Fig. 1 ROM Configuration

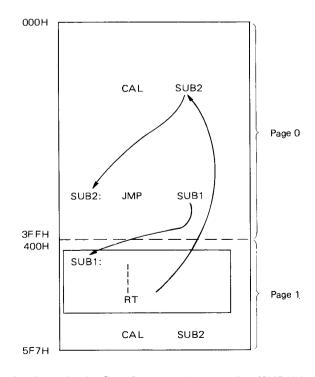

This ROM of  $\mu$ PD1708 needs the concept of page, and its addresses from 000H to 3FFH are called the Page 0 and the remaining addresses from 400H to 5F7H the Page 1.

The head address of any subroutine must be set within the page 0 when creating a program. The subroutine contained in Page 1 at its head address however cannot be called neither from the Page 0 or the Page 1 (see Caution to Use of CAL Instruction).

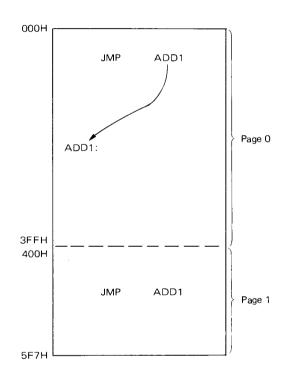

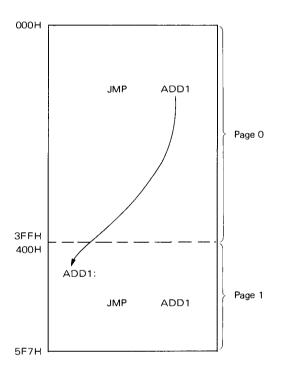

The above concept of page is not applicable to the JMP instruction when it is described by the assembler, and it can be used between the addresses 000H and 5F7H under the same description (JMP ADDR).

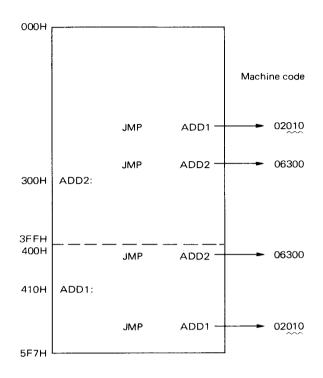

The operation codes of JMP instructions for Page 0 and Page 1 being different, care must be taken for the debug and patch correction (see Caution to Use of JMP Instruction).

The following points must be noted in the use of CAL and JMP instructions since ROM of  $\mu$ PD1708 applies the concept of page (discrimination between Page 0 and Page 1):

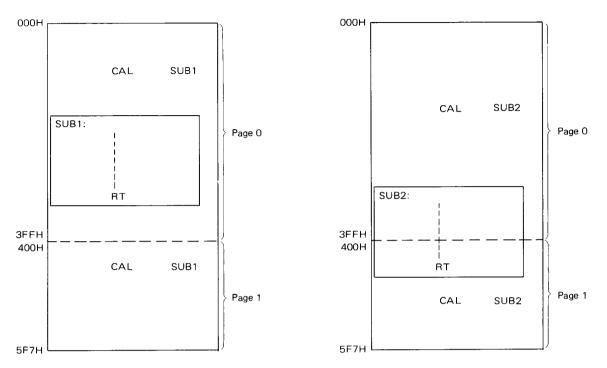

#### Caution to Use of CAL Instruction

The calling address of CAL instruction or the head address of its subroutine must be set within the Page 0 (000H to 3FFH), but the subroutine at the head address of Page 1 (400H to 5F7H) cannot be called. The return address (RT and RTS instructions) can be set within the Page 1.

Example 1: Head address of subroutine within Page 0

If the head address of a given subroutine is set within the Page 0, as shown above, the return addresses (RT and RTS instructions) may be set within either the Page 0 or Page 1.

While the head addresses of subroutines are contained within the Page 0, the CAL instruction can be used without being conscious with the concept of page. The following technique is however effective if the head address of a given subroutine is not allowed to be within the Page 0 for the convenience of programming:

In other words, a JMP instruction is set in the Page 0 and a real subroutine (SUB1) is called via this JMP instruction.

#### Caution to Use of JMP Instruction

As far as the JMP instructions are described by the assembler, the said instructions can be used without the concept of page between the ROM addresses 000H to 5F7H under the same description.

The operation codes of JMP instructions for Page 0 (000H to 3FFH) are different from those of other JMP instructions for Page 1 (400H to 5F7H). The operation code of JMP instruction for Page 0 is "06" while that of another JMP instruction for Page 1 is "02".

If the assembler of  $\mu$ PD1700 Series is used for assembling, the address to which the operation needs be jumped can be referred to and automatically converted by the assembler.

A Typical Case of Operation Code "06" (if the jump address is within Page 0)

A Typical Case of Operation Code "02" (if the jump address is within Page 1)

For the debug and patch correction the operation codes "06" and "02" must be converted by the programmer. And so must be the addresses if the JMP instruction designates any address beyond 400H (with the operation code of "02"). In this case the address 400H is turned to the address 000H and the remaining addresses are increased by one address each. Hence the address 5F7H is raised to the address 1F7H.

If JMP 400H is described by the assembler, for instance, and when you want to correct the patch, 02000 must be input so that JMP 000H turns to 06000.

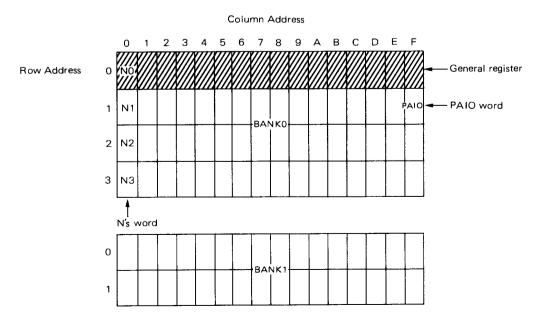

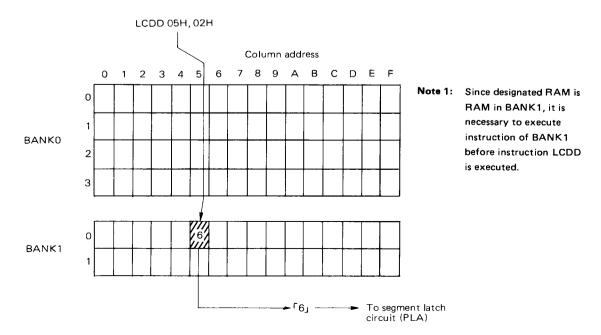

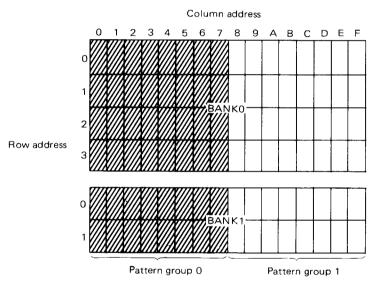

#### 1.4 DATA MEMORY (RAM)

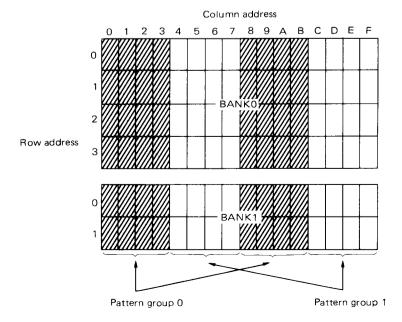

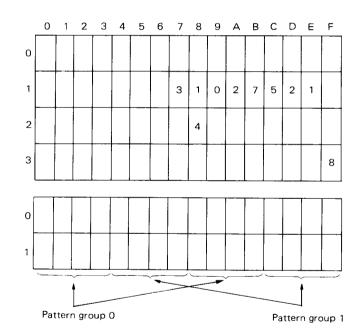

RAM is composed of 4 bits x 96 words and can be used to store ordinary data. The area of 96 words of this RAM is divided into the BANK 0 (64 words) and the BANK 1 (32 words). Either BANK must be designated (by BANK0 or BANK1 instruction) before data are processed within the designated BANK.

The addresses from 00H to 0FH of BANKO are called the general registers, which can be used for operations and transfers between the memory or which can be used as memories. No designations of BANKs are required to use the above addresses as the general registers, and they can be accessed under both status of BANKO and BANK1. To use them as memories, these addresses should be designated in BANKO.

Fig. 2 RAM Configuration

All the pertinent information for PLL control (e.g. divided values, reference frequency or dividing method) can be set by RAM.

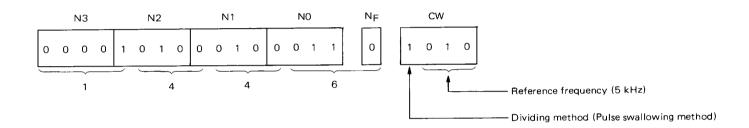

The bits to set a given divided value are assigned with a total of 17 bits composed of 4 bits x 4 words (N's words) at the address 00H, 10H, 20H and 30H and the highest-order bit ( $N_F$  bit) of a given general register; the bits to set both the reference frequency and the dividing method are assigned with one word (4 bits) of RAM, excepting N's words and one word including  $N_F$  bit. All these bits are to be transferred to the PLL register by the PLL 1 instruction.

The address 1FH of BANKO is called the PAIO word to be used to designate the Port A for input or output.

Note: The most important point you should keep in mind in the general register operation in BANK1 is that µPD1708 does not have operational instructions between the general registers and the immediate data. For example, expression "AI 00, 1" in a program in BANK0 adds one to the general register which is stored in address 00 in the data memory. This AI instruction is the operation between memory and the immediate data. This instruction is not the operation between the register and the immediate data. If the above instruction is executed when BANK1 is specified, this expression does not add one to the address 00 of the general register but adds one to the address 00 of the data memory in BANK1.

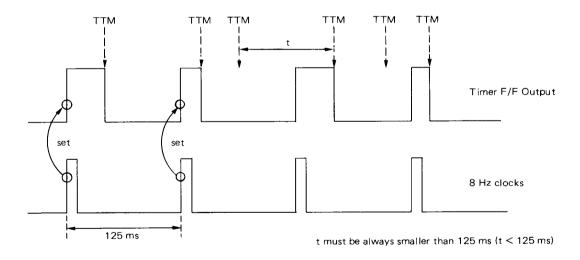

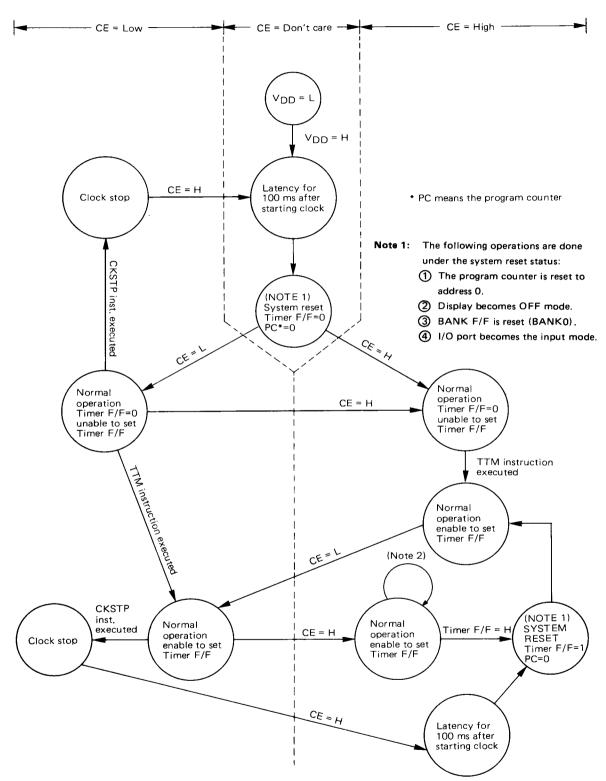

#### 1.5 TIMER F/F

The timer F/F is to be set with an 8 Hz (125 ms) signal and reset by the test timer instruction (TTM instruction). This timer F/F is automatically set every 125 ms so that it can be used to count the clock (one second by 8 counts) or the mute time.

Since the timer F/F can be reset only by the execution of TTM instruction this instruction must be executed within the period of 125 ms under any circumstance. When this instruction is executed within a period of 125 ms or more, the timer F/F fails to count up the clock and becomes unable to control the correct time.

Fig. 3 Execution Timing of TTM Instruction

This timer F/F can be also used to judge the detection of power failure. It is reset when  $V_{DD}$  changes from low to high or it is set again by the execution of CKSTP instruction or when CE changes from low to high. Fig. 4 shows the status transition diagram illustrating the afore-mentioned relations.

Fig. 4 CPU Status Transition by CE Terminal

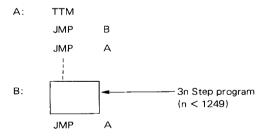

Note 2: It is impossible to come out from this loop if the setting of the timer F/F and the execution of the TTM instruction are done simultaneously. If this is the case, the loop can be broken by the setting of the next timer F/F (after 125 ms), then the program jumps to address 0 after turning the timer F/F to "1". It must be noted if the execution of the TTM instruction is periodic and if the execution cycle happens to coincide with the cycle of the timer F/F setting (125 ms), program cannot be cleared to address 0 permanently.

As apparent from the above illustration, the program starts from the address 0 after the power is turned on  $(V_{DD})$  changes from Low to High), no matter what condition the CE pin is held, while the timer F/F remains reset. The timer F/F is not set again unless the TTM instruction was once executed (status unable to set the timer F/F). Once the TTM instruction was executed, however, the timer F/F can be set at any time at the intervals of 125 ms each.

If the power is being fed ( $V_{DD}$ =high) and the CE terminal changes from low to high, the program flow jumps to the address 0 immediately when the timer F/F is set. The program therefore starts from the address 0 while the time F/F remains set.

As you could understand well from the above explanation, the contents of Timer F/F vary between the time the power failure is recovered (V<sub>DD</sub> changes from low to high) and the time when the power is continuously fed (V<sub>DD</sub> =high and CE=low) or when the device is restored from the backed-up condition. Through testing the contents of this timer F/F (i.e. the execution of TTM instruction) it is possible to judge if it is restored from the power failure or from the non-power failure. In other words the power failure can be judged if the execution of TTM instruction, which is executed within 125 ms from the start of program from the address 0, results in 0 (false) or it can be determined as non-power failure (backed-up condition) if the result of test turns to 1 (true).

Care must be also taken to the programming when restoring from the non-power failure (V<sub>DD</sub>=high and CE changes from low to high) while the clock function of a given program, if provided, needed to be operated (without using the CKSTP instruction) even if CE was low. The program flow in this case jumps to the address 0 immediately after the timer F/F is set. It is therefore necessary to update the clock after executing the TTM instruction to detect the power failure (the execution results in finding true). Otherwise the clock delays by 125 ms each whenever the CE pin changes from low to high.

- Note 1: The program starts from the address 0 after the timer F/F was set if CE pin changed from low to high following the execution of CKSTP instruction in case of μPD1708. The timer F/F is reversely reset and the program starts from the address 0 under μPD1701, μPD1704 and μPD1710. It must be noted when executing the CKSTP instruction that the contents of timer F/F differ between μPD1708 and the group of μPD1701, μPD1704 and μPD1710.

- Note 2: Even if the CE pin changes from low to high level, the program flow does not move to address 0 when the setting of the timer F/F and the execution of the TTM instruction overlap. If this is the case, the system judges that the timer F/F is set by the TTM instruction execution and the timer F/F is reset. This point must be kept in mind when a power failure detection is done by the TTM instruction. That is, you should know that the TTM instruction has higher priority than the setting of the timer F/F when they overlap. Therefore, the clock does not become incorrect and a misjudging of a power failure does not occur. However, if the TTM instruction execution and the timer F/F setting happen to coincide in the following program, the program does not jump to address 0 forever. (The timer F/F will not be reset.)

In this example the program executes the normal TTM instruction, skips the next 'JMP B' instruction because the timer F/F is reset, and executes 'JMP A' instruction. Therefore, it cycles this loop. The cycle is  $100 \, \mu s$ . (3 steps) The timer F/F is set once every 125 ms and the operations of B are performed. This operations take (3n + 3) steps (multiple of  $100 \, \mu s$ ). If the CE pin happens to change from low to high level during the TTM instruction execution in this program, operations in B are done due to the judgement that the timer F/F is set by the TTM instruction. However, the timer F/F is set again (125 ms later) when the next TTM instruction is executed because the time interval from the last TTM execution to the next TTM execution is a multiple of  $100 \, \mu s$ . Therefore, the timer F/F will not be reset and the program cycles this endless loop. This problem occurs in a program where the TTM instruction is executed in every 125 ms. If this is the case, change the program so that the TTM instruction is not executed after 125 ms (3750 steps) from the TTM execution.

#### 1.6 INTERVAL PULSE (ITP)

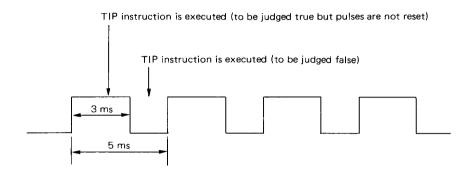

The interval pulses are 60 % duty pulses that are output at 5 ms each and can be tested by the TIP instruction. As no flipflops are provided, the pulse output cannot be reset even if the TIP instruction is executed.

A precise timer of the multiple of 5 ms can be created by the constant executions of TIP instruction to catch the edges of interval pulses.

Fig. 5 Interval Pulse Timing

#### 1.7 UNLOCK F/F (UL F/F)

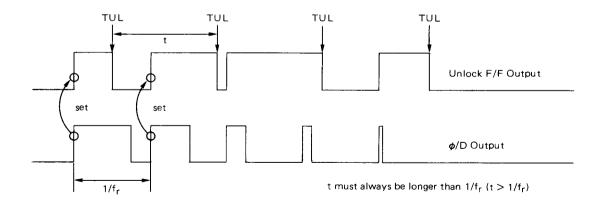

The phase detector  $(\phi\text{-DET})$  outputs pulses at the cycle of reference frequency  $(f_r)$  if the PLL system is not locked or if the reference frequency  $(f_r)$  does coincides with the divided output frequency of VCO. The unlock F/F is set with this pulse and reset by the execution of TUL instruction. The period of executing the TUL instruction should be always longer than that of  $f_r$ . If it is shorter, the PLL system is considered to be locked, although it is not in fact, and it may lead to certain malfunction.

Similarly the TUL instruction, which is executed first after the PLL instruction, needs be executed after a period over the  $f_r$  period after executing the PLL instruction.

Fig. 6 Execution Timing of TUL Instruction

#### 1.8 CARRY F/F (C F/F)

The carry F/F is set if a carry or a borrow is generated as the result of execution of a given operation instruction. Or it is reset if any of carry or borrow occured, and its content remains unchanged unless an operation instruction is executed.

The carry F/F can be also set or reset directly by the carry F/F set/reset instructions (STC and RSC instructions) as well as the status word operation instructions (SS and RS instructions).

#### 1.9 BANK F/F (B F/F)

The BANK F/F is used to designate the BANK for the data memory (RAM and to address the port groups. RAM of 96 words is divided into the BANKO (64 words) and BANK1 (32 words), and either BANK must be designated (execution of BANKO or BANK1 instruction) before data are processed by either BANK. The data processing between two BANKs is carried out via the general registers (the address 00H to 0FH within BANKO). To use the above addresses of BANKO as the general registers, and the data can be accessed from either the BANKO or BANK1 without requiring the designation of BANKs. But the BANKO must be designated in case the addresses are used as the memories.

The BANK F/F is also used for addressing of the port group. The addressing is then performed with two bits of the operands of a given instruction and the content of BANK F/F (see 3. Port).

The BANK F/F is reset and the BANKO is automatically designated by the initial power input ( $V_{DD} = low$  to high) and CE changes from low to high or when the device is reset.

#### 1.10 STATUS WORD

The status word is to split the inside status of a given device, which must be known for the execution of program or which must be designated unconditionally, into four bits each, and to thereby test, set or reset the status by the program.

Two kinds of the status words are provided, status word 1 and 2, to which any of the following terminals or F/F input or output is connected.

#### (1) Status Word 1 (write-only word)

Operation instruction: SS, RS, etc.

| #3 | #2          | # 1          | #0 |

|----|-------------|--------------|----|

| 0  | BANK<br>F/F | Carry<br>F/F | 0  |

The status word 1 can be set or reset by the SS, RS or El instruction.

#### (2) Status Word 2 (read-only word)

Operation instruction: TST, TSF, etc.

| #3 | #2          | # 1            | #0 |

|----|-------------|----------------|----|

| 0  | BANK<br>F/F | CE<br>terminal | 0  |

The contents of status word 2 can be judged by the TST, TSF or SBK0 instruction.

#### 2. PLL

# 2.1 REFERENCE FREQUENCY GENERATOR (RFG)

Seven different kinds of the reference frequencies, viz., 5 kHz, 6.25 kHz, 9 kHz, 10 kHz, 12.5 kHz and 25 kHz, are derived by this generator, which divides the frequency of external crystal oscillator (4.5 MHz). The selection of required reference frequency can be made by the program (data of control word).

#### 2.2 PHASE DETECTOR ( $\phi$ -DET)

It is the circuit that detects the phase difference between the reference frequency ( $f_r$ ) and those of the output of VCO, which are divided by the programmable divider.

The output is input into the internal charge pump, which in turn outputs the following pulses to the  $EO_1$  and  $EO_2$  pins:

(1)  $f_r > f_{osc}/N$ : low level

(2)  $f_r < f_{osc}/N$  : high level

(3)  $f_r = f_{osc}/N$  : floating

where fosc means the oscillation frequency of VCO and N the dividing ratio of programmable divider.

#### 2.3 PROGRAMMABLE DIVIDER (P/D)

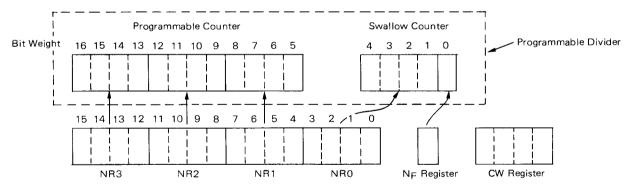

The programmable divider is a binary down counter, composed of a swallow counter and a programmable counter. The swallow counter is a presettable down counter of 5 bits into which the contents of NR0 (4 bits) and  $N_F$  (1 bit) out of N registers are preset at the period of reference frequency.

The programmable counter is composed of 12 bits into which the contents of NR1 through NR3 of the N registers are preset and which is counted down simultaneously with the swallow counter.

Fig. 7 Programmable Divider Configuration

#### 2.4 PLL REGISTER

To control PLL of  $\mu$ PD1708 needs the following three information:

- (1) Dividing ratio (N)

- (2) Reference frequency (fr)

- (3) Dividing method (direct & pulse swallowing methods)

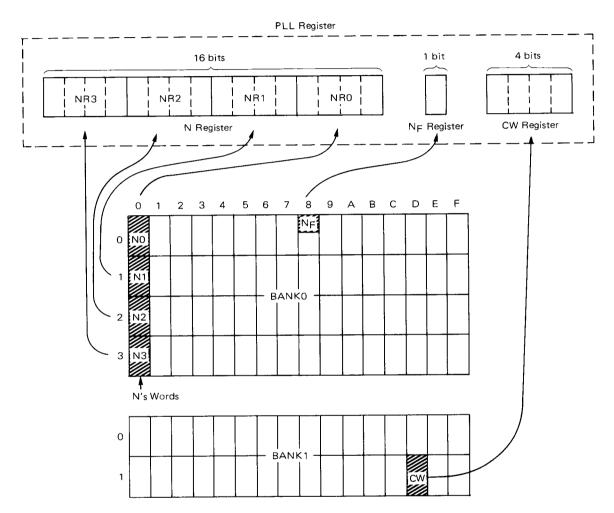

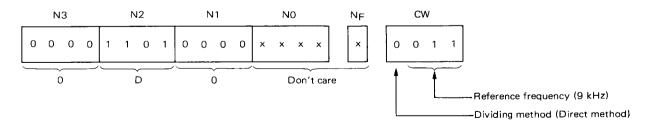

The PLL register stores the above three information; and it is composed of N register (16 bits) and N<sub>F</sub> register (1 bit), both of which set the dividing ratio, and control word register (4 bits) that sets the reference frequency and the dividing method. These registers correspond to N's words, N<sub>F</sub> bit and control words (CW) of the data memory (RAM) respectively. The contents of above memory are all transferred to PLL register at a time by the PLL instruction.

Note: Since CW is in BANK 1 in this example, the BANK must be set to "1" before the PLL instruction is executed.

Fig. 8 Operation by Execution of PLL Instruction

The N's words are assigned to the addresses 00H, 10H, 20H and 30H of RAM, the  $N_F$  bit to the highest-order bit of a general register and CW to any RAM area excluding the N's words and one word including the  $N_F$  bit.

The data code of control words, as shown in Table 1, enables you to select any of seven different reference frequencies. The highest-order bit (#3) of control word selects the direct dividing method if the bit is set to "0" or the pulse swallowing method if set to "1".

In case the direct method is chosen, the VCOL pin is also selected to which the frequencies ranging from 0.59 to 20 MHz ( $v_i$ =0.1  $V_{p-p}$ ) can be input. The then input frequency is directly divided according to the value of programmable divider.

Table 1 Control Word Codes

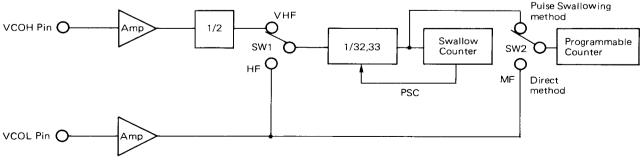

If the pulse swallowing method is selected, the terminal that may be chosen by the execution of instruction varies with the VHF and HF instructions. If then the pulse swallowing method was selected and the VHF instruction was executed, the VCOH pin is chosen into which the frequencies from 10 to 130 MHz ( $v_i$ =0.3  $V_{p-p}$ ) can be input. These frequencies input into the VCOH pin are then divided by the 1/2 divider and sent to the programmable counter via two-modulus prescalers of 1/32 and 1/33.

If the pulse swallowing method was selected and the HF instruction was executed, the VCOL pin is chosen into which the frequencies from 0.6 to 40 MHz (v<sub>i</sub>=0.1 V<sub>p-p</sub>) can be input. The frequencies thus input into the VCOL pin are sent to the programmable counter via two-modulus prescalers of 1/32 and 1/33.

In any case where the pulse swallowing method is selected, either the VHF or HF instruction must be executed once again.

Fig. 9 shows the internal equivalent circuit, which explains the afore-mentioned operations.

Note: Both SW1 and SW2 in the above diagram remain unchanged when the power is turned on (VDD changes from low to high).

Fig. 9 Internal Equivalent Circuit

In the above diagram SW1 is switched by the execution of VHF or HF instruction while SW2 is switched likewise by the execution of PLL instruction. Where the direct method was selected and either VHF or HF instruction was executed, the status of SW1 is switched by the instruction executed, but the PLL operation of direct method remains unaffected.

The direct method generally applies to the reception of MW and LW bands; the pulse swallowing method is then used for the reception of FM band (by VHF) or for the reception of SW band (by HF).

Table 2 Condition of VCOL and VCOH pin by dividing method

| CW #3 | FREQUENCY DIVIDING METHOD       | CONDITION OF<br>VCOL AND VCOH PIN | INPUT<br>VOLTAGE          | INPUT<br>FREQUENCY | DIVIDING<br>RATIO                      |

|-------|---------------------------------|-----------------------------------|---------------------------|--------------------|----------------------------------------|

| 0     | Direct Method                   | VCOL pin = Active                 | 0.1 V <sub>p-p</sub> MIN. | 0.59 to 20 MHz     | 16 to (2 <sup>12</sup> -1)<br>(1 step) |

|       | Pulse Swallowing Method         | (VCOH pin = Pull-down)            | 0.1 V <sub>p-p</sub> MIN. | 0.6 to 40 MHz      | 1024 to (2 <sup>17</sup> -1)           |

|       | (When HF instruction executed)  |                                   | 0.3 V <sub>p-p</sub> MIN. | 0.6 to 50 MHz      | (1 step)                               |

| 1     | Pulse Swallowing Method         | VCOH pin = Active                 | 0.3 V <sub>p-p</sub> MIN. | 10 to 130 MHz      | 2048 to (2 <sup>17</sup> -2)           |

|       | (When VHF instruction executed) | (VCOL pin = Pull-down)            | 0.5 V <sub>p-p</sub> MIN. | 10 to 150 MHz      | (2 steps)                              |

#### 2.5 SETTING OF PLL INFORMATION

The PLL information (i.e. the dividing ratio, dividing method and reference frequencies) are set by the respective programs. Shown below is the setting of divided value of programmable divider.

# (1) Direct Method

$$N = \frac{f_{VCOL}}{f_r}$$

where f<sub>VCOL</sub> = VCOL pin input frequency

f<sub>r</sub> = Reference frequency

Example: To receive MW (the receiving frequency: 1,422 kHz, reference frequency: 9 kHz, IF frequency: 450 kHz)

$$N = \frac{1422 + 450}{9} = 208$$

= 0D0H (H means a hexadecimal code)

The contents of both N0 and N<sub>F</sub> are ignored under the direct method.

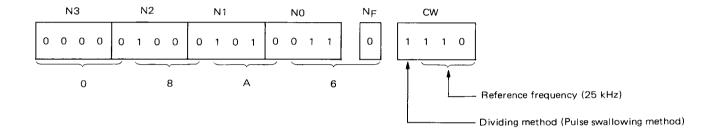

(2) Pulse Swallowing Method (by execution of VHF instruction)

$$N = \frac{f_{VCOH}}{P \times f_r}$$

where  $f_{VCOH} = V_0$

where  $f_{VCOH} = VCOH$  pin input frequency

f<sub>r</sub> = Reference frequency

P = Divided value of 1/2 divider (=2)

Example: To receive FM (US band)

(the receiving frequency: 100.0 MHz, reference frequency: 25 kHz, IF frequency: 10.7 MHz)

$$N = \frac{(100.0 + 10.7) \times 10^6}{2 \times 25 \times 10^3} = 2214$$

= 8A6H (H means a hexadecimal code)

The above example is the case where the N<sub>F</sub> bit is varied one by one as the lowest-order bit; then the VCO oscillation frequency changes by 50 kHz each. To change the VCO frequency by 100 kHz each, the bits must be varied by one each from N0 or by two each for 200 kHz change or by four each for 400 kHz change.

The value N is determined in the above example, assuming the  $N_F$  bit to be the lowest-order bit. It is however much easy to understand the programming when the bits are divided by four bits each from N0. The reference frequency is thus assumed to be 50 kHz in the computation.

$$N = \frac{(100.0 + 10.7) \times 10^6}{2 \times 50 \times 10^3} = 1107$$

$$= 453H$$

As shown above, the result of calculation becomes equal to the one where the reference frequency is assumed to be 25 kHz.

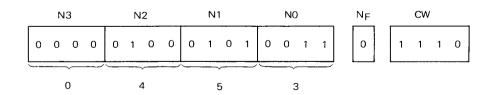

(3) Pulse Swallowing Method (by execution of HF instruction)

$$N = \frac{f_{VCOL}}{f_r}$$

where  $f_{VCOL} = VCOL$  pin input frequency

$$f_r = Reference frequency$$

Example: To receive SW (the receiving frequency: 25.50 MHz, reference frequency: 5 kHz, IF frequency: 450 kHz)

$$N = \frac{25.5 \times 10^6 + 450 \times 10^3}{5 \times 10^3} = 5190$$

$$= 1446H$$

The above example is the case where the  $N_F$  bit is varied by one as the lowest-order bit; the VCO oscillation frequency then changes by 5 kHz each. To change it by 10 kHz each, the bits must be varied by one from N0 or by two for 20 kHz change or by four for 40 kHz change.

As apparent from the above three examples, the selection of pulse swallow method makes 17 bits valid from the  $N_F$  bit or the selection of direct method make 12 bits effective from the N1 word.

## 3. PORT

The  $\mu$ PD1708 has Port A (PA<sub>3</sub> to PA<sub>0</sub>) as its I/O ports and Port B (PB<sub>3</sub> to PB<sub>0</sub>) and Port C (PC<sub>3</sub> to PC<sub>0</sub>) as its output ports.

The addressing of these ports is performed by the direct addressing of two bits contained in the operand of a given instruction and by the BANK F/F. The port addressings by these two elements are as shown in Table 3 below.

DIRECT ADD.

BANK F/F

# 1

# 0

BANK0

BANK1

0

0

PA

0

1

PB

1

0

PC

1

1

**Table 3 Port Addresses**

Note: All the ports (Ports A, B and C) of μPD1708 are assigned within the BANKO. To access to a given port after accessing to RAM of BANK1, the BANK F/F must be set back to BANK0. No ports can be accessed while the BANK1 is chosen by the BANK F/F even if any port operation instruction (e.g. IN, OUT, SPB or RPB instruction) is executed.

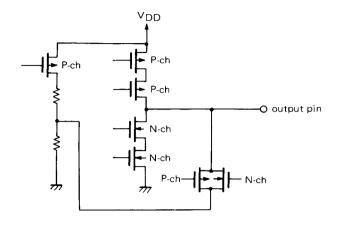

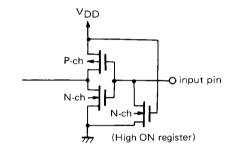

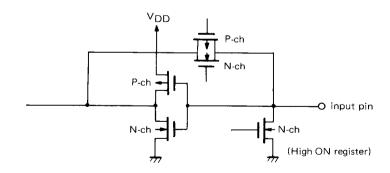

## 3.1 PORT A

The Port A (PA<sub>3</sub> to PA<sub>0</sub>) can be set either to the input or the output by the unit of 1 bit each. The input or output is settable according to the content at the address 1FH of BANKO within the data memory (RAM) known as the PAIO word. To set the input port, "0" needs be set to the bit of PAIO word corresponding to the required port or "1" must be set to set any Port A to the output.

|                                     | #3              | #2              | # 1             | #0              |

|-------------------------------------|-----------------|-----------------|-----------------|-----------------|

| PAIO Word<br>(Address 1FH)<br>BANKO | PA <sub>3</sub> | PA <sub>2</sub> | PA <sub>1</sub> | PA <sub>0</sub> |

Example 1: To set PA<sub>3</sub> and PA<sub>2</sub> to the output and PA<sub>1</sub> and PA<sub>0</sub> to the input

|           | #3 | #2 | # 1 | #0 |

|-----------|----|----|-----|----|

| PAIO Word | 1  | 1  | 0   | 0  |

Example 2: To set all Port A ports (PA<sub>3</sub> to PA<sub>0</sub> ) to the output

|           | #3 | #2 | # 1 | #0 |

|-----------|----|----|-----|----|

| PAIO Word | 1  | 1  | 1   | 1  |

Either the input or the output must be set in the PAIO word for Port A; then the input or output instruction should be executed. The input mode or output mode once set up remains valid until after the content of PAIO word (data stored at the address 1FH of BANK 0) is changed. Port A however is changed automatically to the input mode when the power is turned on (V<sub>DD</sub> changes to low to high) or after the execution of CKSTP instruction or if CE changes from low to high.

It must be noted that the contents of PAIO word do not coincide with the current mode of Port A, viz., the input or output mode. Port A works under the input mode continuously until the content of PAIO word is set.

#### Example:

#### 3.2 PORT B & PORT C

Both the Port B (PB<sub>3</sub> to PB<sub>0</sub>) and Port C (PC<sub>3</sub> to PC<sub>0</sub>) of  $\mu$ PD1708 are the output ports of CMOS type, which can be generally accessed by the output instruction (e.g. OUT, SPB and RPB instructions). When an input instruction (IN) is executed, the content of data currently being output is read into the register as designated by the operand of the said instruction. The contents being output by the execution of IN instruction may remain unchanged. If "1" is output during the execution of an output instruction, the high level (V<sub>DD</sub> potential) is output or the low level (GND potential) is output if "0" is output.

- Note 1: When the power is turned on (VDD changes from low to high), the contents of output to be made by Port B or Port C are unknown. It is therefore imperative to initialize both ports by the respective program after turning on the power.

- Note 2: Where V<sub>DD</sub> is set high, CE pin changes from high to low or it changes reversely, the contents of outputs of Port B and Port C do not change and the preceding status are retained. The output contents also remain unchanged even after the CKSTP instruction was executed.

# Example 1: Port initialization before turning on the power

#### START:

```

1FH, 1111B ; to set all bits of Port A to output port

MVI

0AH, 0

to set the port initialize data

MVI

Port A (PA_3 \text{ to } PA_0) = AII \text{ Low}

OUT

0, 0AH

; Port B (PB<sub>3</sub> to PB<sub>0</sub>) = All Low

OUT

1,0AH

Port C (PC_3 to PC_0) = All Low

OUT

2. 0AH

if the timer F/F is set,

TTM

then go to BACKUP

BACKUP

JMP.

MVI

00H, 0

RAM initialize

RAM initialize

MVI

01H, 0

```

BACKUP:

Example 2: In the μPD1708, Ports B and C maintain the state immediately before even when the clock stop instruction is executed. Reset the ports before the clock stop instruction as shown below to disable the current flowing from the ports (ports to low) in a clock stop state:

① TCET; Does not skip if the level at CE pin is low more than 100 μs before ①.

2) TCEF; Skips if the level at CE pin is low more than 133.3 \( \mu \)s before 2).

3 JMP NOTSTP ; To NOTSTP (does not CKSTP)

; if the level at CE pin is decided to be high at  $\bigcirc$  or  $\bigcirc$ .

(4) BANKO ; Set the bank to 0 RPB 1, 1111B ; Reset Port B entirely

RPB 2, 1111B ; Reset Port C entirely

⑤ CKSTP ; Synchronize to 8 Hz and branch to Address 0 if the level of CE pin is high after

③ . (Resetting is applied.)

⑥ JMP \$−1; In this case, go round the loop between ⑤ and ⑥ until the 8 Hz signal rise.

If the level of CE pin is still low at (5), stop the clock.

NOTE: The methods described in ① and ② are taken to prevent maloperation as resetting is not possible even when a low level lower than 134 μs is input to CE pin. A low level or 100 μs (three instruction cycles) or higher will be required to enable a decision as a low level in an instruction (TCET or TCEF). The CKSTP instruction stops the clock if the level of CE pin is low more than 133.3 μs (four instruction cycles) before this instruction is given.

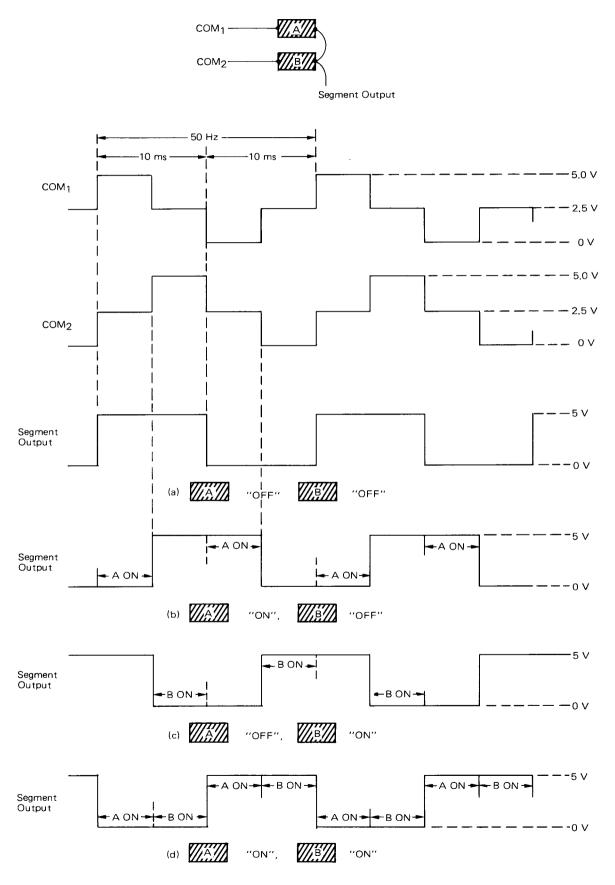

#### 4. LCD DRIVER

$\mu$ PD1708 contains in it an LCD driver (frame frequency: 100 Hz) of 1/2 duty and 1/2 bias drive (voltage equalization system) type. Fig. 10 is a timing chart which illustrates the principle of the LCD driver. As can be seen from Fig. 10, two common signals deviating from each other in phase by 1/4 output three potentials; 0 V (GND), 5 V (V<sub>DD</sub>) and 2.5 V (1/2 V<sub>DD</sub>) intermediate between them. In other words, the common signals output a potential of  $\pm$ 1/2 V<sub>DD</sub> on both sides of 1/2 V<sub>DD</sub>. The above display system is, therefore, referred to as 1/2 bias drive system.

In this system, two segments (A and B) are driven by an output of one segment, and a segment whose potential  $(V_{DD})$  is most different from that of the common signal lights up. Four clock timings (a) to (d) are outputted as a segment output according to combinations of ON and OFF of two connected segments A and B. A segment to be lighted at this time repeats ON and OFF at 5 ms intervals. In other words, the segment is kept lighted on at a frequency of 100 Hz and duty factor of 1/2.

Fig. 10 Timing Chart of 1/2 Duty and 1/2 Bias (Voltage Equalization System) LCD Driver

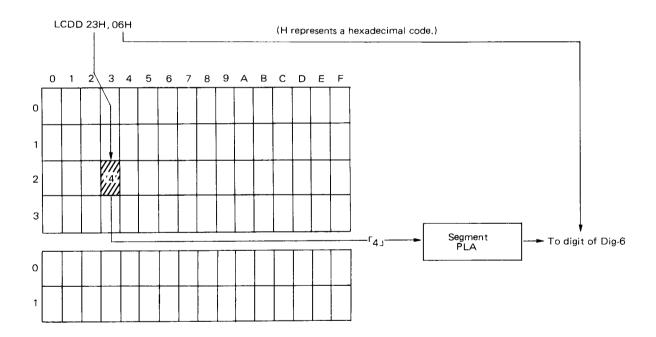

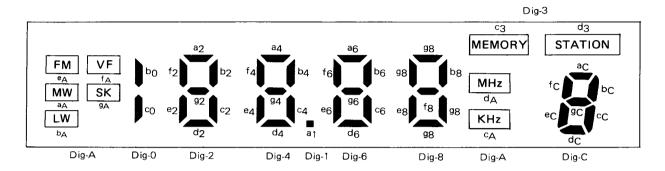

$\mu$ PD1708 is able to make an outer LCD panel display data by executing an instruction LCDD M, D. "M" represents any address in a data memory (RAM), and "D" represents the number of digits of display. "D" takes a total of fifteen (15) values, i.e., fourteen (14) values 00H to 0DH of Dig-O to Dig-D as shown in an LCD matrix of Fig. 11 and a special value 0FH which determines ON and OFF modes of display.

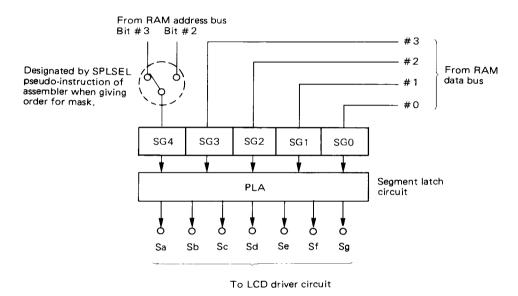

When even digits (Dig-0, Dig-2, Dig-4, Dig-7, Dig-8, Dig-A and Dig-C) are entered in "D", data stored in the data memory (RAM) designated by "M" are unconditionally loaded on a PLA (Programmable Logic Array), and output (displayed) in a digit designated by "D" through the PLA.

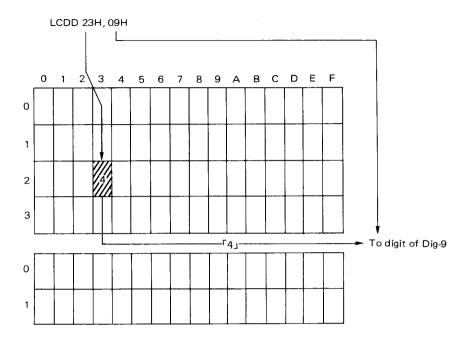

When odd digits (Dig-1, Dig-3, Dig-5, Dig-7, Dig-9, Dig-B and Dig-D) are entered in "D", data stored in the data memory (RAM) is output (displayed) directly in a digit designated by "D", without passing through the PLA. Table 4 shows relations between bits of RAM data to be output in an odd digit at this time and segments arranged in odd digits.

Examples of operations when executing an LCDD instructions in even and odd digits are described the following.

#### O Example in Case of Even Digit

The data "4" stored in the address 23H of the data memory (RAM) is led to the PLA, and data stored in the PLA is output to the digit of Dig-6.

#### O Example in Case of Odd Digit

The data "4" stored in the address 23H of the data memory is output directly to a digit of Dig-9. Four segments  $b_A$ ,  $e_A$ ,  $f_A$  and  $g_A$  are arranged in the digit of Dig-9, and when "4" = 0100B is output, only the segment  $f_A$  lights up. (See Table 4 "Bits Corresponding to Odd Digit (Which Does not Pass Through PLA)). When "5" = 0101B is output to the digit of Dig-9, segments  $f_A$  and  $e_A$  light up.

As can be seen from the LCD matrix of Fig. 11, the digit of Dig-8 (even digit) can be used also as a digit of Dig-D (odd digit). If, for instance, LCDD 10H, 08H is entered, data of the digit of Dig-8 is displayed through the PLA. If LCDD 10H, 0DH is entered, data is displayed as a digit of Dig-D without passing through the PLA.

Similarly, the digits of Dig-5 and Dig-7 (odd digits) can be used also as a digit of Dig-C (even digit), and those of Dig-9 and Dig-B (odd digits) can be used also as a digit of Dig-A (even digit). In other words, it can be selected whether segments of these digits light up through the PLA or not through the PLA.

When power is turned on  $(V_{DD} = Low \rightarrow High)$  and an instruction CKSTP is executed, the levels at LCD segment terminals (LCD<sub>1</sub> to LCD<sub>23</sub>) and LCD common terminals (COM<sub>1</sub> and COM<sub>2</sub>) all automatically become low (**display OFF mode**). In the display OFF mode, therefore, all segments on the LCD panel are put out.

Even though an instruction LCDD M, D (provided that  $0 \le D \le 0DH$ ) is executed in the display OFF mode, the display is not turned on. If an LCDD instruction is executed in this case, only such operation that the latch data of the LCD segment latch circuit is rewritten is made.

It is, therefore, necessary to set the LCD segment and common terminals once in the **display ON mode** for making the display on the LCD panel light up. When changing the operation mode from display OFF to display ON, the following instruction is executed.

LCDD M, OFH

**JMP**

FLASH

However, data to be stored in a data memory (RAM) addressed by "M" is larger than 8. That is, 0FH is entered in the second operand part (D) of the instruction LCDD, and a value larger than 8 (8  $\leq$  (M)  $\leq$  F) is set for data to be stored in the data memory (RAM). In other words, a value larger than 8 should be output to the digit of Dig-F.

On the contrary, when changing a display ON mode to a display OFF one with a program, a value of smaller than  $7 \ (0 \le (M) \le 7)$  is output to the digit of Dig-F. When a display mode is changed to display OFF, latch data of the LCD segment latch circuit does not change from the preceding data (data stored in the display ON mode), unless an instruction LCDD M, 0 (provided that  $0 \le D \le 0$ DH) is executed. When, therefore, preparing such a program as to make every segment of the LCD panel flash at fixed time intervals, the purpose is attained by alternately and repeatedly executing an instruction LCDD which sets a display mode to display ON or display OFF as mentioned above. Examples of programs to be prepared are given below.

```

LCDD 12H, 0DH

Output to digit of Dig-D.

LCDD 11H, 0CH

Output to digit of Dig-C.

Sets 5-second timer.

MVI CONT. 8

Sets display OFF mode data.

MVI

34H, 0

FLASH:

LCDD 34H, 0FH

Display OFF mode (every segment OFF).

Calls subroutine of waiting for 500 ms.

CAL WT500M

ΑI

34H. 8

Turn over the display.

Skips after five times, i.e., five seconds.

SIS

CONT, 1

```

The above examples are programs of making every segment, i.e., whole of the LCD panel flash (OFF for 500 ms and ON for 500 ms) for five seconds at 500 ms intervals, after displaying data in all digits of the LCD panel.

Returns to FLASH again if five seconds have not elapsed.

Note: Contents of data to be applied to the LCD segment latch circuit when turning power on (V<sub>DD</sub> = Low → High) is indefinite.

If, therefore, a display mode is changed to display ON immediately after turning power on, an undesired display may be made.

In such cases, it is necessary to beforehand output data, those are desired to be displayed before changing a display mode to display ON, i.e., in a display OFF mode, to all digits.

Figures given in parentheses represent terminal numbers of IC.

Fig. 11 LCD Matrix

Table 4 Bits Corresponding to Odd Digit (Which Does not Pass Through PLA)

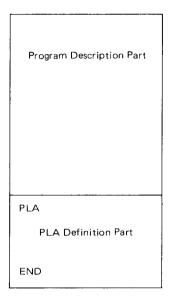

# 5. PLA (PROGRAMMABLE LOGIC ARRAY)