# KS88C0604 8-Bit CMOS Microcontroller

**Data Sheet**

## **DESCRIPTION**

The KS88C0604 single-chip 8-bit microcontroller is fabricated using an advanced CMOS process. With five configurable I/O ports that have 12bit-programmable pins for external interrupts, and an 8-bit interval timer with a 4-bit prescaler, the KS88C0604 is especially suitable for use as a keyboard controller.

#### **FEATURES**

## CPU

SAM8 CPU core

### Memory

- 4-Kbyte internal program memory (ROM)

- · 208-byte internal register file

#### **Instruction Set**

- 79 instructions

- IDLE and STOP instructions added for powerdown modes

## **Instruction Execution Time**

1.2 μs at 5 MHz f<sub>OSC</sub> (minimum)

## Interrupts

- 13 interrupt sources

- Three interrupt priority levels with three vectors

- Fast interrupt processing (one level only)

### **Oscillation Circuit Options**

- RC oscillator (with internal capacitor)

- External clock source

- Crystal/ceramic oscillator

### General I/O

- Five ports (32 pins total)

- Three nibble-programmable ports (20 pins total)

- Two bit-programmable ports with external interrupts (12 pins total)

## Timer/Counter

- One 8-bit interval timer with 4-bit prescaler

- Programmable oscillation stabilization interval generation function

## **Operating Temperature Range**

• -20°C to +85°C

## **Operating Voltage Range**

4.5 V to 5.5 V

## Package Types

• 40-pin DIP, 44-pin QFP

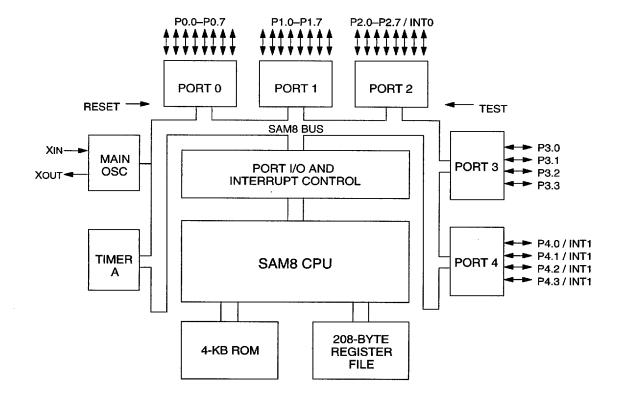

## **BLOCK DIAGRAM**

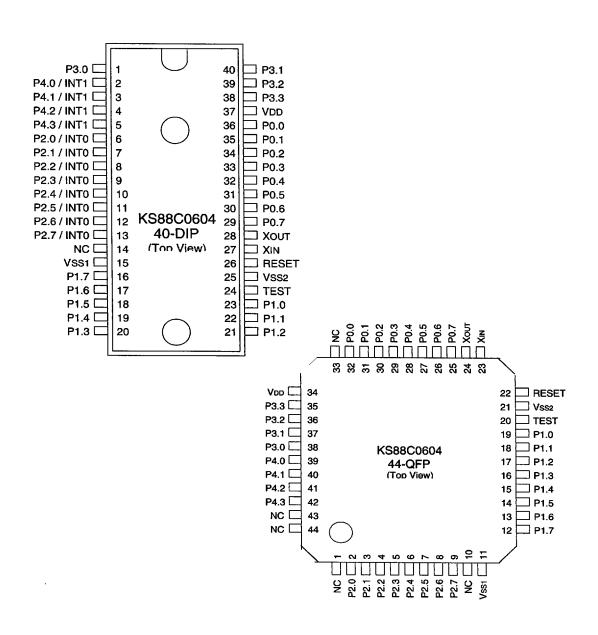

## **PIN ASSIGNMENTS**

KS88C0604 **DATA SHEET**

## **PIN DESCRIPTIONS**

| Pin<br>Names                        | Pin<br>Type | Pin<br>Description                                                                                                                                                                                                                                                     | Circuit<br>Number | Pin<br>Numbers               | Share<br>Pins |

|-------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------|---------------|

| P0.0–P0.7                           | I/O         | Nibble-programmable I/O port. Input mode or n-channel, open-drain output mode and pull-up resistors (33 $\rm K\Omega$ ) are assignable by software.                                                                                                                    | 3                 | 36–29<br>(32–25              | -             |

| P1.0-P1.7                           | I/O         | Same as port 0.                                                                                                                                                                                                                                                        | 3                 | 23–16<br>(19–12)             | _             |

| P2.0-P2.7                           | I/O         | Bit-programmable I/O port. Input mode or push-pull output mode is assignable by software. Pins can be individually configured as external interrupt inputs.                                                                                                            | 5                 | 6–13<br>(2–9)                | INT0          |

| P3.0-P3.3                           | I/O         | 4-bit nibble-programmable I/O port with internal serial resistors (typical 220 $\Omega$ ). Input mode or n-channel, open-drain output mode and pull-up resistors (33 K $\Omega$ ) are software assignable. Port 3 pins are designed for high current drive capability. | 4                 | 1, 40–38<br>(38–35)          |               |

| P4.0-P4.3                           | I/O         | 4-bit bit-programmable I/O port. Input mode or n-channel, open-drain output mode are software assignable. Pins can be individually configured as external interrupt inputs. Pull-up resistors (2.2 K $\Omega$ ) are also software assignable.                          | 6                 | 2–5<br>(39–42)               | INT1          |

| INTO                                | 1/0         | External interrupt for bit-programmable port2 pins when set to input mode                                                                                                                                                                                              | 5                 | 6–13<br>(2–9)                | P2.0-P2.7     |

| INT1                                | I/O         | External interrupt for bit-programmable port4 pins when set to input mode                                                                                                                                                                                              | 6                 | 2–5<br>(39–42)               | P4.0-P4.3     |

| X <sub>IN</sub> , X <sub>OUT</sub>  | -           | System clock input and output pin (for RC oscillator, crystal/ceramic oscillator, or external clock source)                                                                                                                                                            | _                 | 27, 28<br>(23, 24)           | _             |

| RESET                               | ļ           | RESET signal input pin. Schmitt trigger input with a 220-KΩ internal pull-up resistor.                                                                                                                                                                                 | . 1               | 26 (22)                      | -             |

| TEST                                | I           | Test signal input pin. (For factory use only; must be connected to VSS during normal operation.) Normal operation is always 0 V; factory test mode is 7–9 V.                                                                                                           | 2                 | 24 (20)                      | _             |

| V <sub>DD</sub>                     | _           | Power input pin                                                                                                                                                                                                                                                        | _                 | 37 (34)                      | _             |

| V <sub>SS1</sub> , V <sub>SS2</sub> | _           | Ground pins                                                                                                                                                                                                                                                            | _                 | 15, 25<br>(11, 21)           | _             |

| NC                                  | <u>-</u>    | No connection                                                                                                                                                                                                                                                          | _                 | 14<br>(1, 10, 33,<br>43, 44) | _             |

NOTE: 1. Pin numbers shown in parentheses '( )' are for the 44-QFP package; others are for the 40-DIP package.

2. Pin numbers 1, 33, 43, 44 (on the 44-QFP package), would be better connecting to V<sub>SS</sub>.

3. VSS1 and VSS2 must be connected in external circuit.

## **FUNCTION OVERVIEW**

#### **ADDRESS SPACES**

#### Overview

The KS88C0604 microcontroller has two kinds of address space:

- Internal program memory (ROM)

- Internal register file

A 16-bit address bus supports program memory operations. A separate 8-bit register bus carries addresses and data between the CPU and the internal register file. An external memory interface is not implemented.

## **Program Memory (ROM)**

The KS88C0604 has 4K bytes of mask-programmable program memory. The first 256 bytes of the ROM are reserved as an interrupt vector area. Unused locations in this address range can be used as normal program memory. The program reset address in the ROM is 0020H.

### **Register File**

The upper 64 bytes of the KS88C0604's internal register file are logically expanded into two 64-byte areas, called set 1 and set 2. The upper 32-byte area of set 1 is divided into two register banks, called bank 0 and bank 1. The total addressable register space is thereby expanded from 256 bytes to 352 bytes. 238 registers in this space can be accessed; of these registers, 208 are available for general-purpose use.

The entire physical 256-byte register space of the KS88C0604 is addressed as page 0. The 8-bit register bus can address up to 256 bytes in page 0.

The extension of the physical register space into separately addressable areas (sets, banks, and pages) is supported by various addressing mode restrictions, the select bank instructions SB0 and SB1, and the register page pointer (PP).

There are 208 general-purpose registers. Thirteen 8-bit registers are used for system control and there are 17 mapped peripheral control and data registers. A 16-byte common working register area is allocated for data operations. In addition, there is freely addressable 128-byte prime register area, and a 64-byte area for general-purpose use and for stack operations.

### Register Addressing

The SAM8 register architecture provides an efficient method of working register addressing that takes full advantage of shorter instruction formats to reduce execution times. Registers can be addressed either as a single 8-bit register or a 16-bit register pair.

The SAM8 instruction set supports seven addressing modes. Not all of these addressing modes are available for each instruction. The seven addressing modes and their symbols are:

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Indirect Address (IA)

- Relative Address (RA)

- Immediate (IM)

In Register (R) addressing mode, the operand value is the content of a specific register or register pair. You can use this mode to access all locations in the internal register file except for set 2. Working register addressing uses register pointers to select a specific register within a working register space.

To increase the speed of context switches during program execution, you use the register pointers to dynamically select movable 8-byte "slices" of the register file as active working register space.

#### **INTERRUPTS**

The KS88C0604 microcontroller has thirteen peripheral interrupt sources:

- Eight external interrupts for port 2, P2.0-P2.7

- Four external interrupts for port 4, P4.0–P4.3

- Timer A overflow interrupt

Each interrupt source has a corresponding vector address. Only three levels are used in the KS88C0604 interrupt structure.

When multiple interrupt levels are active, the interrupt priority register (IPR) determines the order in which contending interrupts are to be serviced. If multiple interrupts occur within the same interrupt level, the interrupt with the lowest vector address is usually processed first.

### **INSTRUCTION SET**

The SAM8 instruction set is designed to support a large register file. It includes 79 arithmetic and logical operations, including multiply and divide. Binary-coded decimal (BCD) operations include decimal adjustment of binary values. You can increment and decrement 16-bit address and counter values. Flexible instructions for bit addressing, and for rotate and shift operations complete the powerful data manipulation capabilities of the instruction set.

#### **CLOCK CIRCUIT**

An RC oscillation source or a separate external clock source provides a maximum 5 MHz clock for the KS88C0604. An internal capacitor supports the RC oscillator circuit. The X<sub>IN</sub> and X<sub>OUT</sub> pins connect the oscillation source to the on-chip clock circuit.

To increase processing speed and to reduce clock noise, non-divided logic is implemented for the main oscillator circuit.

#### RESET

A reset is initiated when the signal at the RESET pin is held Low for at least 22 CPU clocks. The RESET signal is input through a Schmitt trigger circuit (with a 220-K $\Omega$  pull-up resistor) and synchronized with the CPU clock.

### STOP MODE

Stop mode is invoked by the instruction STOP (opcode 7FH). In Stop mode, both the CPU and its peripherals are "put to sleep". That is, the on-chip main oscillator stops and all system functions are halted. Current data values in the internal register file are retained.

There are two ways to release Stop mode:

- External reset operation

- Port 2 or port 4 external interrupt

## **IDLE MODE**

Idle mode is invoked by the instruction IDLE (opcode 6FH). In Idle mode, the CPU "sleeps" while select peripherals remain active. During Idle mode, the internal clock signal is gated off to the CPU, but not to interrupts or the interval timer.

Port pins retain the mode (input or output) they had at the time Idle mode was entered. The contents of system registers, control registers, and data registers are retained.

You can release Idle mode in one of three ways:

- External reset operation

- Port 2 or port 4 external interrupt

- Timer A internal time-out interrupt

#### I/O PORTS

The KS88C0604 has five I/O ports (0-4) with a total of 32 pins. You access these ports directly by writing or reading port data register addresses.

For keyboard applications, ports 0, 1, and 2 are usually configured as keyboard matrix inputs. Port 3 can directly drive up to four LEDs. Port 4 is used for host communication or for controlling a mouse or other external device.

#### TIMER A

The KS88C0604 has an 8-bit timer/counter module called timerA. It has the following components:

- 8-bit counter and comparator

- Control register with 4-bit prescaler for timer A clock input

- Reference data register

Timer A has two functions:

- To control the duration of the oscillation stabilization interval when Stop mode is released and before normal CPU operation resumes, and

- To serve as a normal interval timer, generating a timer A interrupt (IRQ6) at programmed time intervals.

During interval timer operation, the timer A clock source is the CPU clock. The CPU clock is divided by 1000 on its way to the prescaler.

When timer A is used to program the oscillation stabilization time for Stop mode release, the timerA clock source switches automatically to the main oscillator input at the X<sub>IN</sub> pin. When normal CPU operation resumes, the CPU clock is automatically restored as the timer A clock source.

## D.C. ELECTRICAL CHARACTERISTICS

$(T_A = -20^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$

| Parameter                      | Symbol            | Conditions                                                                            | Min                   | Тур | Max                 | Unit |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|-----------------------|-----|---------------------|------|

| Input High<br>Voltage          | V <sub>IH1</sub>  | All inputs except V <sub>IH2</sub>                                                    | 0.8 V <sub>DD</sub>   | _   | V <sub>DD</sub>     | ٧    |

|                                | V <sub>IH2</sub>  | X <sub>IN</sub>                                                                       | V <sub>DD</sub> – 0.5 |     | V <sub>DD</sub>     |      |

| Input Low Voltage              | V <sub>IL1</sub>  | All inputs except V <sub>IL2</sub>                                                    |                       | _   | 0.2 V <sub>DD</sub> | ٧    |

|                                | V <sub>IL2</sub>  | X <sub>IN</sub>                                                                       |                       |     | 0.4                 |      |

| Output High<br>Voltage         | V <sub>OH1</sub>  | V <sub>DD</sub> = 4.5–5.5 V<br>I <sub>OH</sub> = -1 mA<br>Port 3 only                 | V <sub>DD</sub> – 1.0 | _   | -                   | ٧    |

|                                | V <sub>OH2</sub>  | V <sub>DD</sub> = 4.5–5.5 V<br>I <sub>OH</sub> = -200 μA<br>All outputs except port 3 | V <sub>DD</sub> – 1.0 |     |                     |      |

| Output Low<br>Voltage          | V <sub>OL1</sub>  | V <sub>DD</sub> = 4.5–5.5 V<br>I <sub>OL1</sub> = 2 mA<br>Ports 0, 1, 2, and 4        |                       | _   | 0.4                 | V    |

|                                | V <sub>OL2</sub>  | V <sub>DD</sub> = 4.5–5.5 V<br>I <sub>OL2</sub> = 10 mA<br>Port 3 only                |                       |     | 1.0                 |      |

| Input High<br>Leakage Current  | l <sub>LIH1</sub> | V <sub>IN</sub> = V <sub>DD</sub><br>All inputs except I <sub>LIH2</sub>              | -                     |     | 3                   | μА   |

|                                | LIH2              | $V_{IN} = V_{DD}$<br>$X_{IN}, X_{OUT}$                                                |                       |     | 20                  |      |

| Input Low<br>Leakage Current   | JLIL1             | V <sub>IN</sub> = 0 V<br>All inputs except I <sub>LIL2</sub>                          | _                     | -   | -3                  | μΑ   |

|                                | lLIL2             | $V_{IN} = 0 V$<br>$X_{IN}, X_{OUT}$                                                   |                       |     | - 20                |      |

| Output High<br>Leakage Current | ILOH              | V <sub>OUT</sub> = V <sub>DD</sub><br>All outputs except port 2                       | -                     | -   | 3                   | μА   |

| Output Low<br>Leakage Current  | ILOL              | V <sub>OUT</sub> = 0 V<br>All outputs                                                 | -                     | _   | -3                  | μА   |

| Pull-up Resistors              | R <sub>L1</sub>   | V <sub>IN</sub> = 0 V; V <sub>DD</sub> = 4.5–5.5 V,<br>Ports 0, 1, 2, and 3           | 10                    | 29  | 40                  | ΚΩ   |

|                                | R <sub>L2</sub>   | V <sub>IN</sub> = 0 V, V <sub>DD</sub> = 4.5–5.5 V,<br>Port 4 only                    | 1.2                   | 2.2 | 4.0                 |      |

|                                | R <sub>L3</sub>   | $V_{IN} = 0 \text{ V}, V_{DD} = 4.5-5.5 \text{ V},$<br>RESET only                     | 100                   | 220 | 350                 |      |

KS88C0604 DATA SHEET

# D.C. ELECTRICAL CHARACTERISTICS (Continued)

$(T_A = -20^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$

| Parameter                | Symbol           | Conditions                                                        | Min | Тур | Max | Unit |

|--------------------------|------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| Supply<br>Current (NOTE) | I <sub>DD1</sub> | V <sub>DD</sub> = 4.5–5.5 V<br>4-MHz CPU clock                    |     | 10  | 20  | mA   |

|                          | I <sub>DD2</sub> | Idle mode; V <sub>DD</sub> = 4.5–5.5 V,<br>4-MHz CPU clock        |     | 3.2 | 8   |      |

|                          | I <sub>DD3</sub> | Stop mode; V <sub>DD</sub> = 5.0 V,<br>No pull-up resistor option |     | 0.6 | 20  | μА   |

| Operating frequency      | fosc             | V <sub>DD</sub> = 4.5–5.5 V                                       | 0.5 | _   | 4   | MHz  |

|                          |                  | RC oscillator, crystal/ceramic oscillator                         | _   |     | 5   |      |

NOTE: Supply current does not include current drawn through internal pull-up resistors or external output current loads.

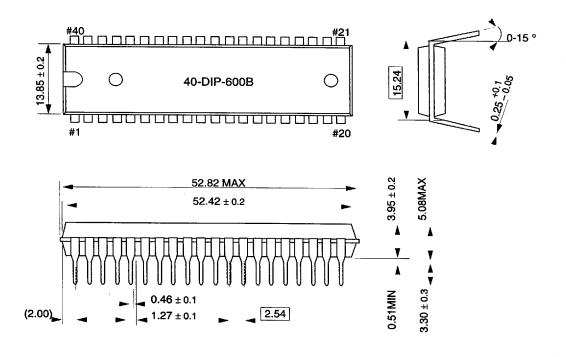

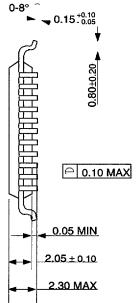

## **PACKAGE DIMENSIONS**

NOTE: Dimensions are in millimeters.

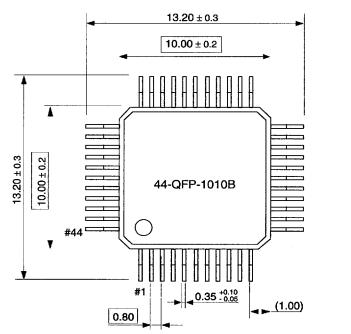

## **PACKAGE DIMENSIONS (Continued)**

NOTE: Dimensions are in millimeters.