© 2002 National Semiconductor Corporation

DS200315

# 捷多邦,专业PCB打样工厂,24小时加急出货

February 2002

National Semiconductor

# LM2704 Micropower Step-up DC/DC Converter with 550mA Peak **Current Limit General Description**

The LM2704 is a micropower step-up DC/DC in a small 5-lead SOT-23 package. A current limited, fixed off-time control scheme conserves operating current resulting in high efficiency over a wide range of load conditions. The 21V switch allows for output voltages as high as 20V. The low 400ns off-time permits the use of tiny, low profile inductors and capacitors to minimize footprint and cost in space-conscious portable applications. The LM2704 is ideal for LCD panels requiring low current and high efficiency as well as white LED applications for cellular phone back-lighting. The LM2704 can drive up to 8 white LEDs from a single Li-Ion battery.

#### Features

- 550mA, 0.7Ω, internal switch

- Uses small surface mount components

- Adjustable output voltage up to 20V

- 2.2V to 7V input range

- Input undervoltage lockout

- 0.01µA shutdown current

- Small 5-Lead SOT-23 package

# Applications

- LCD Bias Supplies

- White LED Back-Lighting

- Handheld Devices

- **Digital Cameras**

- Portable Applications

www.national.com

# LM2704

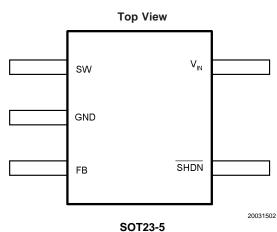

# **Connection Diagram**

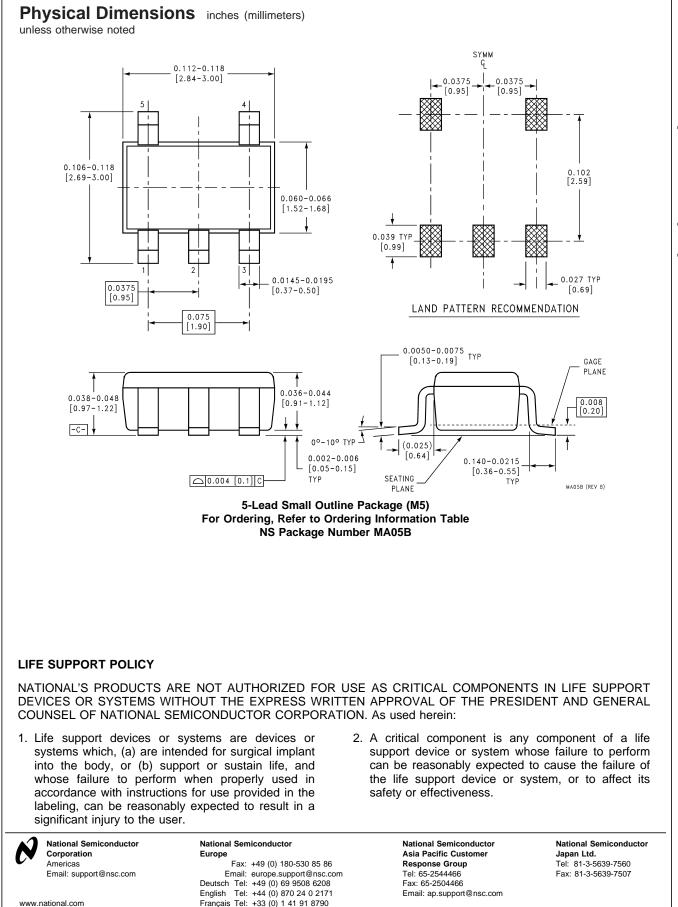

$T_{Jmax} = 125^{\circ}C, \theta_{JA} = 220^{\circ}C/W$  (Note 2)

#### **Ordering Information**

| Order Number  | Package Type | NSC Package Drawing | Supplied As               |

|---------------|--------------|---------------------|---------------------------|

| LM2704MF-ADJ  | SOT23-5      | MA05B               | 1000 Units, Tape and Reel |

| LM2704MFX-ADJ | SOT23-5      | MA05B               | 3000 Units, Tape and Reel |

# **Pin Description/Functions**

| Pin | Name            | Function                            |  |

|-----|-----------------|-------------------------------------|--|

| 1   | SW              | Power Switch input.                 |  |

| 2   | GND             | Ground.                             |  |

| 3   | FB              | Output voltage feedback input.      |  |

| 4   | SHDN            | Shutdown control input, active low. |  |

| 5   | V <sub>IN</sub> | Analog and Power input.             |  |

**SW(Pin 1):** Switch Pin. This is the drain of the internal NMOS power switch. Minimize the metal trace area connected to this pin to minimize EMI.

GND(Pin 2): Ground Pin. Tie directly to ground plane.

**FB(Pin 3):** Feedback Pin. Set the output voltage by selecting values for R1 and R2 using:

$$\mathsf{R1} = \mathsf{R2} \left( \frac{\mathsf{V}_{\mathsf{OUT}}}{1.237\mathsf{V}} \, \text{-} 1 \right)$$

Connect the ground of the feedback network to an AGND plane which should be tied directly to the GND pin.

**SHDN(Pin 4):** Shutdown Pin. The shutdown pin is an active low control. Tie this pin above 1.1V to enable the device. Tie this pin below 0.3V to turn off the device.

$V_{\text{IN}}(\text{Pin 5})\text{:}$  Input Supply Pin. Bypass this pin with a capacitor as close to the device as possible.

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| V <sub>IN</sub>                       | 7.5V  |

|---------------------------------------|-------|

| SW Voltage                            | 21V   |

| FB Voltage                            | 2V    |

| SHDN Voltage                          | 7.5V  |

| Maximum Junction Temp. T <sub>J</sub> | 150°C |

| (Note 2)                              |       |

| Lead Temperature                      |       |

| (Soldering 10 sec.)                   | 300°C |

| Vapor Phase                           |       |

| (60 sec.)                             | 215°C |

|                                       |       |

| Infrared               |       |

|------------------------|-------|

| (15 sec.)              | 220°C |

| ESD Ratings (Note 3)   |       |

| Human Body Model       | 2kV   |

| Machine Model (Note 4) | 200V  |

# **Operating Conditions**

| –40°C to +125°C |

|-----------------|

| 2.2V to 7V      |

| 20.5V           |

|                 |

#### Electrical Characteristics (Note 5)

Specifications in standard type face are for  $T_J = 25^{\circ}C$  and those in **boldface type** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}C$  to +125°C). Unless otherwise specified.  $V_{IN} = 2.2V$ .

| Symbol                        | Parameter                  | Conditions                                                                   | Min<br>(Note 5) | <b>Typ</b><br>(Note 6) | Max<br>(Note 5) | Units      |

|-------------------------------|----------------------------|------------------------------------------------------------------------------|-----------------|------------------------|-----------------|------------|

| l <sub>Q</sub>                | Device Disabled            | FB = 1.3V                                                                    |                 | 40                     | 70              |            |

|                               | Device Enabled             | FB = 1.2V                                                                    |                 | 235                    | 300             | μA         |

|                               | Shutdown                   | SHDN = 0V                                                                    |                 | 0.01                   | 2.5             |            |

| V <sub>FB</sub>               | Feedback Trip Point        |                                                                              | 1.189           | 1.237                  | 1.269           | V          |

| I <sub>CL</sub>               | Switch Current Limit       |                                                                              | 490             | 550                    | ) 610           | <u>س</u> ۸ |

|                               |                            |                                                                              | 420             |                        | 620             | mA         |

| I <sub>B</sub>                | FB Pin Bias Current        | FB = 1.23V (Note 7)                                                          |                 | 30                     | 120             | nA         |

| V <sub>IN</sub>               | Input Voltage Range        |                                                                              | 2.2             |                        | 7.0             | V          |

| R <sub>DSON</sub>             | Switch R <sub>DSON</sub>   |                                                                              |                 | 0.7                    | 1.6             | Ω          |

| T <sub>OFF</sub>              | Switch Off Time            |                                                                              |                 | 400                    |                 | ns         |

| I <sub>SD</sub>               | SHDN Pin Current           | $\overline{\text{SHDN}} = V_{IN}, T_J = 25^{\circ}\text{C}$                  |                 | 0                      | 80              |            |

|                               |                            | $\overline{\text{SHDN}} = V_{\text{IN}}, T_{\text{J}} = 125^{\circ}\text{C}$ |                 | 15                     |                 | nA         |

|                               |                            | SHDN = GND                                                                   |                 | 0                      |                 |            |

| IL                            | Switch Leakage Current     | $V_{SW} = 20V$                                                               |                 | 0.05                   | 5               | μA         |

| UVP                           | Input Undervoltage Lockout | ON/OFF Threshold                                                             |                 | 1.8                    |                 | V          |

| V <sub>FB</sub><br>Hysteresis | Feedback Hysteresis        |                                                                              |                 | 8                      |                 | mV         |

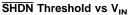

| SHDN                          | SHDN low                   |                                                                              |                 | 0.7                    | 0.3             | V          |

| Threshold                     | SHDN High                  |                                                                              | 1.1             | 0.7                    |                 |            |

| $\theta_{JA}$                 | Thermal Resistance         |                                                                              |                 | 220                    |                 | °C/W       |

Note 1: Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

**Note 2:** The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J(MAX)$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . See the Electrical Characteristics table for the thermal resistance. The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_D (MAX) = (T_{J(MAX)} - T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature. **Note 3:** The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 4: ESD susceptibility using the machine model is 150V for SW pin.

Note 5: All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested or guaranteed through statistical analysis. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 6: Typical numbers are at 25  $^\circ\text{C}$  and represent the most likely norm.

Note 7: Feedback current flows into the pin.

LM2704

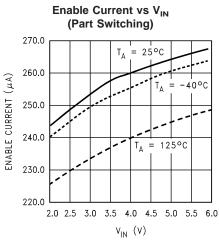

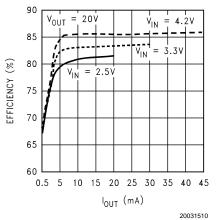

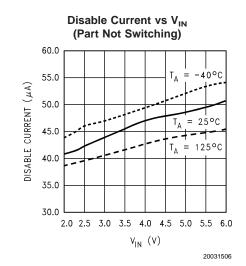

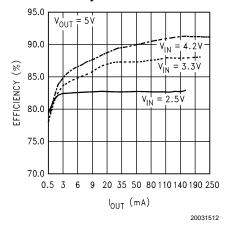

# **Typical Performance Characteristics**

Efficiency vs Load Current

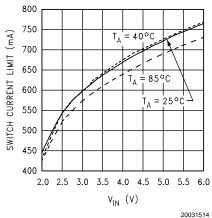

Switch Current Limit vs V<sub>IN</sub>

LM2704

#### Typical Performance Characteristics (Continued) Switch R<sub>DSON</sub> vs V<sub>IN</sub> FB Trip Point and FB Pin Current vs Temperature 1.20 125 55 1.10 50 FEEDBACK BIAS CURRENT (nA) v FEEDBACK TRIP POINT (V) 1.00 124 45 0.90 R<sub>DSON</sub> (D) 40 0.80 123 = 125°C TA 0.70 35 0.60 122 30 = 25°C Τ<sub>Δ</sub> 0.50 nΑ 25 0.40 121 20 0.30 Τ<sub>Α</sub> 40°C 0.20 15 120 $2.0 \hspace{0.1in} 2.5 \hspace{0.1in} 3.0 \hspace{0.1in} 3.5 \hspace{0.1in} 4.0 \hspace{0.1in} 4.5 \hspace{0.1in} 5.0 \hspace{0.1in} 5.5 \hspace{0.1in} 6.0$ -20 -40 0 20 40 60 80 100 120 $V_{IN}$ (V) JUNCTION TEMPERATURE (°C) 20031515 20031538 Step Response Start-Up/Shutdown 1 2 2→ 3→ 3-20031516 $V_{OUT} = 20V, V_{IN} = 3.0V$ 20031517 $V_{OUT} = 20V, V_{IN} = 2.5V$ 1) Load, 1mA to 17mA to 1mA, DC 1) SHDN, 1V/div, DC 2) V<sub>OUT</sub>, 200mV/div, AC 2) I<sub>L</sub>, 250mA/div, DC 3) I<sub>L</sub>, 500mA/div, DC 3) V<sub>OUT</sub>, 20V/div, DC T = 40µs/div $T = 400 \mu s/div$ $R_L = 1.3k\Omega$

LM2704

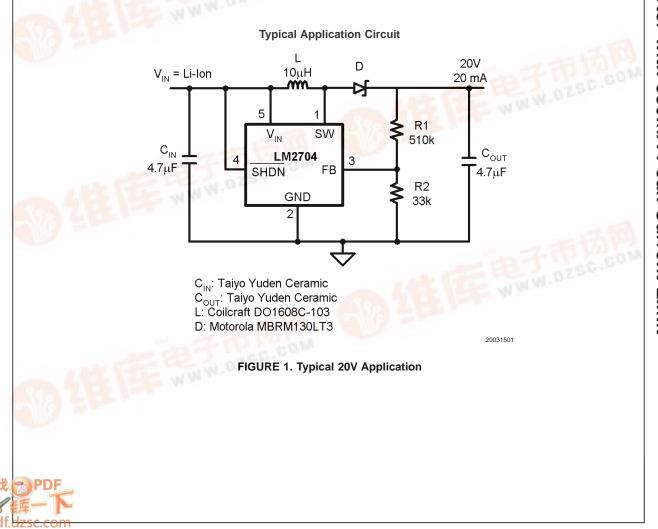

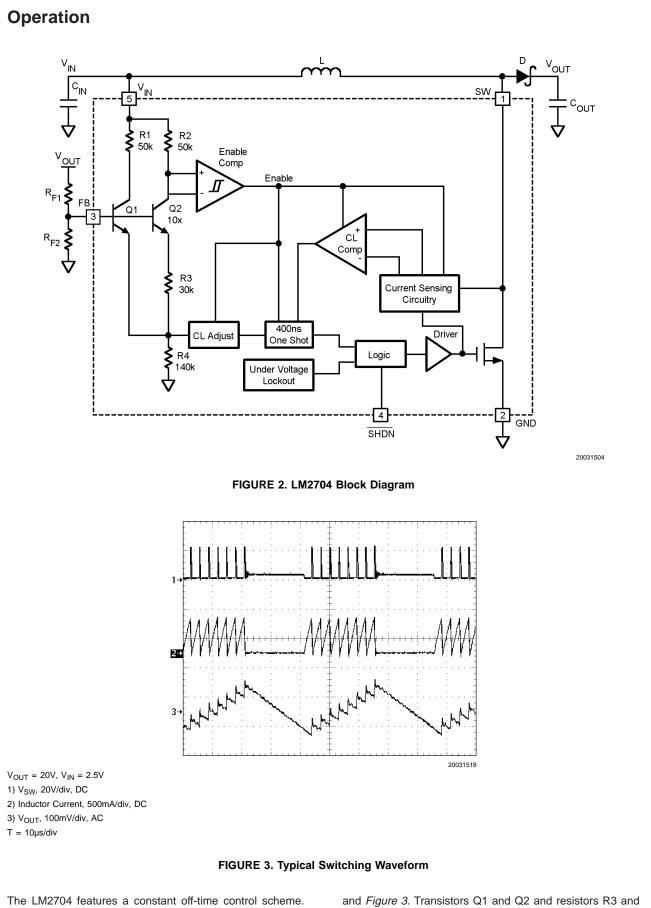

Operation can be best understood by referring to Figure 2

R4 of Figure 2 form a bandgap reference used to control the

#### **Operation** (Continued)

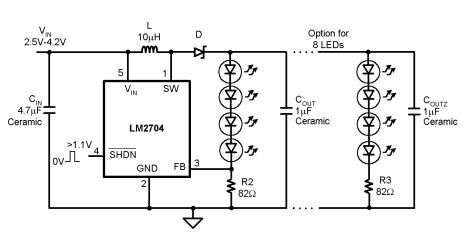

output voltage. When the voltage at the FB pin is less than 1.237V, the Enable Comp in Figure 2 enables the device and the NMOS switch is turned on pulling the SW pin to ground. When the NMOS switch is on, current begins to flow through inductor L while the load current is supplied by the output capacitor  $C_{\mbox{\scriptsize OUT}}.$  Once the current in the inductor reaches the peak current limit, the CL Comp trips and the 400ns One Shot turns off the NMOS switch. The SW voltage will then rise to the output voltage plus a diode drop and the inductor current will begin to decrease as shown in Figure 3. During this time the energy stored in the inductor is transferred to COUT and the load. After the 400ns off-time the NMOS switch is turned on and energy is stored in the inductor again. This energy transfer from the inductor to the output causes a stepping effect in the output ripple as shown in Figure 3.

This cycle is continued until the voltage at FB reaches 1.237V. When FB reaches this voltage, the enable comparator then disables the device turning off the NMOS switch and reducing the Iq of the device to 40uA. The load current is then supplied solely by  $C_{OUT}$  indicated by the gradually decreasing slope at the output as shown in *Figure 3*. When the FB pin drops slightly below 1.237V, the enable comparator enables the device and begins the cycle described previously. The SHDN pin can be used to turn off the LM2704 and reduce the I<sub>q</sub> to 0.01µA. In shutdown mode the output voltage will be a diode drop lower than the input voltage.

#### **Application Information**

#### **Inductor Selection**

The appropriate inductor for a given application is calculated using the following equation:

$$L = \left(\frac{V_{OUT} - V_{IN(min)} + V_{D}}{I_{CL}}\right) T_{OFF}$$

where  $V_D$  is the schottky diode voltage,  $I_{CL}$  is the switch current limit found in the *Typical Performance Characteristics* section, and  $T_{OFF}$  is the switch off time. When using this equation be sure to use the minimum input voltage for the application, such as for battery powered applications. For the LM2704 constant-off time control scheme, the NMOS power switch is turned off when the current limit is reached. There is approximately a 200ns delay from the time the current limit is reached in the NMOS power switch and when the internal logic actually turns off the switch. During this 200ns delay, the peak inductor current will increase. This increase in inductor current demands a larger saturation current rating for the inductor. This saturation current can be approximated by the following equation:

$$I_{PK} = I_{CL} + \left(\frac{V_{IN(max)}}{L}\right) 200 \text{ns}$$

Choosing inductors with low ESR decrease power losses and increase efficiency.

Care should be taken when choosing an inductor. For applications that require an input voltage that approaches the output voltage, such as when converting a Li-Ion battery voltage to 5V, the 400ns off time may not be enough time to discharge the energy in the inductor and transfer the energy to the output capacitor and load. This can cause a ramping effect in the inductor current waveform and an increased ripple on the output voltage. Using a smaller inductor will cause the  $I_{PK}$  to increase and will increase the output voltage ripple further. This can be solved by adding a 4.7pF capacitor across the  $R_{F1}$  feedback resistor (*Figure 2*) and slightly increasing the output capacitor. A smaller inductor can then be used to ensure proper discharge in the 400ns off time.

#### **Diode Selection**

To maintain high efficiency, the average current rating of the schottky diode should be larger than the peak inductor current,  $I_{PK}$ . Schottky diodes with a low forward drop and fast switching speeds are ideal for increasing efficiency in portable applications. Choose a reverse breakdown of the schottky diode larger than the output voltage.

#### **Capacitor Selection**

Choose low ESR capacitors for the output to minimize output voltage ripple. Multilayer ceramic capacitors are the best choice. For most applications, a  $1\mu F$  ceramic capacitor is sufficient. For some applications a reduction in output voltage ripple can be achieved by increasing the output capacitor.

Local bypassing for the input is needed on the LM2704. Multilayer ceramic capacitors are a good choice for this as well. A  $4.7\mu$ F capacitor is sufficient for most applications. For additional bypassing, a 100nF ceramic capacitor can be used to shunt high frequency ripple on the input.

#### Layout Considerations

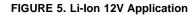

The input bypass capacitor C<sub>IN</sub>, as shown in Figure 1, must be placed close to the IC. This will reduce copper trace resistance which effects input voltage ripple of the IC. For additional input voltage filtering, a 100nF bypass capacitor can be placed in parallel with  $\mathrm{C}_{\mathrm{IN}}$  to shunt any high frequency noise to ground. The output capacitor, COUT, should also be placed close to the IC. Any copper trace connections for the Cout capacitor can increase the series resistance, which directly effects output voltage ripple. The feedback network, resistors R1 and R2, should be kept close to the FB pin to minimize copper trace connections that can inject noise into the system. The ground connection for the feedback resistor network should connect directly to an analog ground plane. The analog ground plane should tie directly to the GND pin. If no analog ground plane is available, the ground connection for the feedback network should tie directly to the GND pin. Trace connections made to the inductor and schottky diode should be minimized to reduce power dissipation and increase overall efficiency.

# Application Information (Continued)

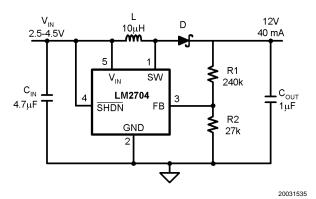

$\begin{array}{l} C_{\text{IN}} \cdot \text{Taiyo Yuden Ceramic} \\ C_{\text{OUT}} \cdot \text{Taiyo Yuden Ceramic} \\ L: \text{Coilcraft DO1608C-103} \\ D: \text{Motorola MBRM130LT3} \end{array}$

20031509

FIGURE 4. White LED Application

FIGURE 6. 5V to 12V Application

LM2704

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.