| 至EB 1 1 1999<br>查询SM5807ES供应商  | ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ●            |

|--------------------------------|--------------------------------------------------|

| NIPPON PRECISION CIRCUITS LTD. | 4-Time Oversampling Digital Filter for CD System |

#### GENERAL DESCRIPTION

The SM5807 digital filter is manufactured using MOLYGATE ( $\neq \forall \forall \neg \uparrow^{\circ}$ ) CMOS technology developed by NPC and is implemented in 4 times oversampling scheme with the stopband (above 24.1 kHz) attenuation of more than 50 dB and the passband ripple of less than +0.05 dB. Two channel filters are provided and the 4 times oversampled output signal of each channel can be independently obtained. Because of this 4 times oversampling, the requirement of the analog filter can be greatly relaxed, and also the serious data format reduces the size of hardware requirement characteristics. required in the system design. Two types, D and E are available in different characteristics.

#### **FEATURES**

- Filter Structure

- 4 times oversampling

2 channel filters

- 2 stages linear phase FIR filter (61 + 13 taps)

- Overflow limiter

- Internal crystal oscillator circuit

- Clock buffer Filter Characteristics

|                                         | SM5807DP,DS           | SM5807EP,ES |  |

|-----------------------------------------|-----------------------|-------------|--|

| Passband ripple(0~20kHz)                | <±0.05dB              | <±0.05dB    |  |

| Stopband attenuation<br>(above 24.1kHz) | >50dB                 | >45dB       |  |

| Group delay time                        | Constant linear phase |             |  |

#### • Input/Output

- 16-bit serial data input and output (2's complement, MSB first)

- TTL compatible

- Power Supply 5±0.5V

16-Pin plastic DIP/SOP

Molygate CMOS technology

#### PRODUCT SELECT LIST

| Part Number  | PACKAGE    |

|--------------|------------|

| SM5807DP, EP | 16-Pin DIP |

| SM5807DS, ES | 16-Pin SOP |

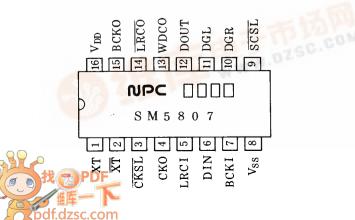

#### **PIN CONFIGURATION**

(Top View)

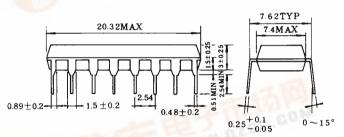

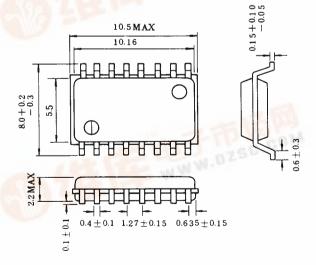

PACKAGE DIMENSIONS

All dimensions in millimeters

16-Pin DIP

5 - v

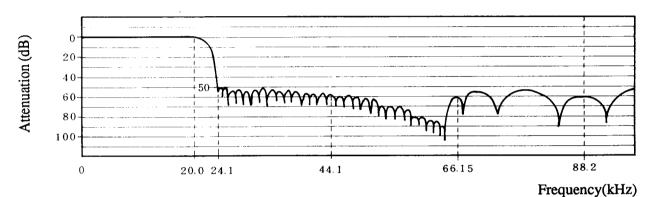

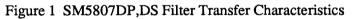

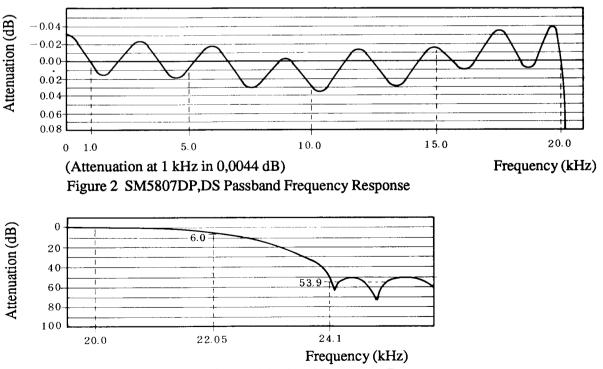

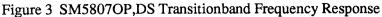

#### ■ THEORETICAL FILTER CHARACTERISTICS 1. SM5807DP,DS (0~88.2kHz)

| Parameter                                | Characteristic |

|------------------------------------------|----------------|

| Passband                                 | 0~20kHz        |

| Stopband                                 | Above 24.1 kHz |

| Passband Ripple                          | ±0.05dB        |

| Stopband Attenuation<br>(above 24.1 kHz) | 50dB(minimum)  |

## **SM5807** 4-Time Oversampling Digital Filter for CD System

#### 2. SM5807EP, ES (0~88.2kHz) Characteristics Parameter Passband 0~20kHz Above 24.1kHz Stopband ±0.05dB Passband Ripple Stopband Attenuator (24.1~40.0kHz) 45dB (minimum) (40.0kHz) 50dB (minimum) 0 Attenuation (dB) 20 40 45 60 80 100-0 20.2 24.1 66.15 88.2 40.0 44.1 Frequency (kHz) Figure 4 SM5807EP,ES Filter Transfer Characteristics 0.04 Attenuation (dB) 0.02 0.00 0.02 0.04 0.06 0.08 1.0 0 5.0 10.0 15.0 20.0 <1 kHz 0.0365dB> Frequency (kHz) Figure 5 SM5807EP,ES Passband Frequency Response 0 Attenuation (dB) 6.0 20-40-60 80-100 20.0 22.05 24.1 0 Frequency (kHz)

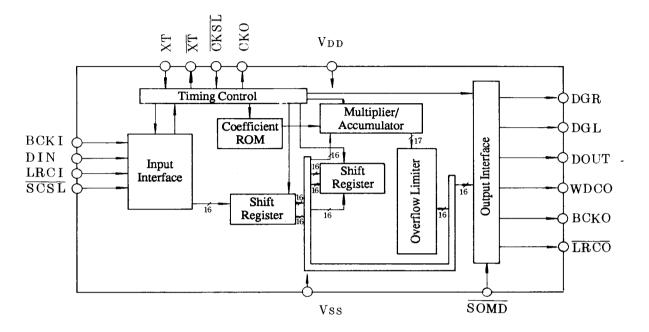

#### **BLOCK DIAGRAM**

| Pin No. | Pin Name        | I/O | Function/Descriptions                                                                                              |

|---------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------|

| 1       | XT              | I   | Crystal oscillator or clock input                                                                                  |

| 2       | <b>XT</b>       | 0   | Oscillator output.when CKSL=H<br>Open, when CKSL=L                                                                 |

| 3       | CKSL            | Ip  | CKSL=H: 16.9349 MHz ~ 17.2872MHz Crystal Osc.or Clock to XT pin<br>CKSL=L: 8.4672MHZ or 8.6436 MHz Clock to XT pin |

| 4       | CKO             | 0   | Clock output (XT clock buffered output)                                                                            |

| 5       | LRCI            | Ip  | Clock input (synchronized 44.1 kHz)                                                                                |

| 6       | DIN             | Ip  | Serial data input                                                                                                  |

| 7       | BCKI            |     | Bit clock input                                                                                                    |

| 8       | V <sub>ss</sub> | Ip  | Ground, 0 <sup>v</sup>                                                                                             |

| 9       | SCSL            | Ip  | SCSL=H : System Clock = 192fs<br>SCSL=L : System Clock =196fs (fs:sampling frequency)                              |

| 10      | DGR             | 0   | Rch deglitch signal (176.4 kHz)                                                                                    |

| 11      | DGL             | 0   | Lch deglitch signal (176.4 kHz)                                                                                    |

| 12      | DOUT            | 0   | Serial data output                                                                                                 |

| 13      | WDCO            | 0   | Output Control Clock (352.8 kHz)                                                                                   |

| 14      | LRCO            | 0   | Output Control Clock (176.4 kHz)                                                                                   |

| 15      | ВСКО            | 0   | Serial Output Bit Clock (8.4672 MHz or 8.6436 MHz)                                                                 |

| 16      | V <sub>DD</sub> |     | Power Supply (5V)                                                                                                  |

#### ■ PIN DESCRIPTION

I : Input

o : Output Ip: Input with pull-up resistor

# 4-Time Oversampling Digital Filter for CD System

#### $(V_{ss}=0^{v})$ Symbol Parameter Rating Units Supply Voltage -0.3~7.0 ۷ VDD ۷ VIN -0.3~V<sub>DD</sub>+0.3 Input Voltage T -40~125 ۰C Storage Temperature Power Dissipation 250 mW $\mathbf{P}_{\mathbf{w}}$ ۰C 255 Soldering Temperature T<sub>SLD</sub> Soldering Time 10 Sec. t<sub>sld</sub>

## ABSOLUTE MAXIMUM RATINGS

#### ■ RECOMMENDED OPERATING CONDITIONS

|                       |                 |            | $(V_{ss} = 0^{v})$ |

|-----------------------|-----------------|------------|--------------------|

| Parameter             | Symbol          | Conditions | Unit               |

| Supply Voltage        | V <sub>DD</sub> | 4.5~5.5    | V                  |

| Operating Temperature | T               | -20~70     | °C                 |

#### ■ DC ELECTRICAL CHARACTERISTICS

#### Ta=-20~70°C, $V_{DD}$ =4.5~5.5V, $V_{ss}$ =0<sup>v</sup> unless otherwise noted Limit Parameter Pin Symbol Condition Unit MIN TYP MAX Supply Current VDD I<sub>DD</sub> V<sub>DD</sub>=5V 10 20 mA <u>v</u>\_<u>пн1</u> v $0.7V_{dd}$ Input Voltage (1) ΧТ V<sub>IL1</sub> 0.3V<sub>DD</sub> ٧ V 2.4 v (\*1) Input Voltage (2) v ٧<sub>11.2</sub> 0.5 ٧ I<sub>oH</sub>=-0.4mA 2.5 V<sub>oh</sub> Output Volage (\*2) I<sub>oL</sub>=1.6mA 0.4 v (\*3) V<sub>IN</sub>=OV 1.0 μA $I_{LL}$ Input Leakage Current (\*4) 1.0 I<sub>LH</sub> $V_{IN} = V_{DD}$ μA (\*1) V<sub>IN</sub>=OV 10 20 Input Current μA I<sub>II</sub>

#### **Pin-Group** List

| *1 | CKSL, LRCI, DIN, BCKI, SCSL                   |

|----|-----------------------------------------------|

| *2 | CKO, LRCO, BCKO, WDCO, DOUT, DGL, DGR         |

| *3 | (XT, at CKSL=L)                               |

| *4 | CKSL,, LRCI, DIN, BCKI, SCSL, (XT, at CKSL=L) |

#### AC ELECTRICAL CHARACTERISTICS

**1.XT**

a. Crystal Oscillator (Ta=-20~70°C, VDD=4.5~5.5V,  $V_{ss}=0^{\circ}$ )

| Parameter | Symbol |     | Unit |     |      |

|-----------|--------|-----|------|-----|------|

|           |        | MIN | ТҮР  | MAX | Cint |

| Frequency | fosc   |     |      | 20  | MHz  |

b.External Clock

(Ta=-20~70°C, V<sub>DD</sub>=4.5~5.5V, V<sub>ss</sub>=OV)

| Parameter          | Symbol | Limit |     |     | Unit | Condition |

|--------------------|--------|-------|-----|-----|------|-----------|

| I di atticici      | Symbol | MIN   | TYP | MAX | СШ   | Condition |

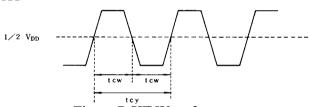

| Clock Pulse Width  | tcw    | 50    |     |     | nSec | CKSL=L    |

| CIOCK I HISC WIGHT |        | 25    |     |     | nSec | CKSL=H    |

| Clock Pulse Period | tcy    | 100   |     |     | nSec | CKSL=L    |

|                    |        | 50    |     |     | nSec | CKSL=H    |

XT

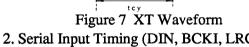

| Serial Input Tim  |                  |      |       |       |       |              |

|-------------------|------------------|------|-------|-------|-------|--------------|

| Parameter         | Symbol           |      | Limit |       |       |              |

|                   | Symbol           | MIN  | TYPE  | MAX   | Unit  |              |

| BCKI Pulse Width  | t <sub>BCW</sub> | 100  |       |       | nsec  | ts           |

| BCKI Pulse Period | t <sub>всу</sub> | 200  |       |       | nsec  |              |

| DIN, LRCZ         |                  | 75   |       |       | nsec  |              |

| set-up time       | L <sub>S</sub>   | 1 13 | lisec | lisee | 15    |              |

| DIN, LRCZ         |                  | 75   |       |       | nsec  | Figure       |

| holding time      | Ч                | ''   | 1     |       | 11360 | Input Timing |

**3.Serial Output Timing**

| Parameter         | Symbol            | Limit |     |     | Unit | Remarks                       |

|-------------------|-------------------|-------|-----|-----|------|-------------------------------|

|                   | Symbol            | MIN   | TYP | MAX | OILL | itemarks                      |

| BCKO Pulse Width  | t <sub>oBCW</sub> | 40    |     |     | nSec |                               |

| BCKO Pulse Period | t <sub>obcy</sub> | 100   |     |     | nSec |                               |

| Output Delay Time | t <sub>DHL</sub>  | 0     |     | 25  | nSec | LRCO, WDCO,<br>DOUT, DGL, DGR |

|                   | t <sub>DLH</sub>  |       |     | 25  | nSec | DOUT, DGL, DGR<br>outputs     |

Figure 9 Output Timing Waveform

#### INTRODUCTION

#### **Basic Filter Structure**

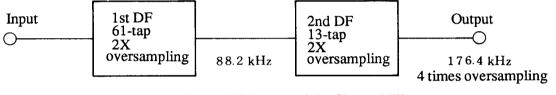

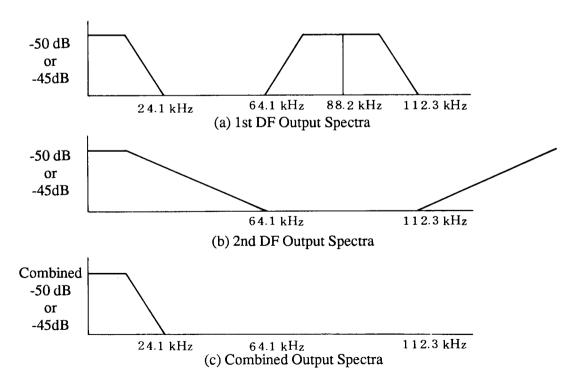

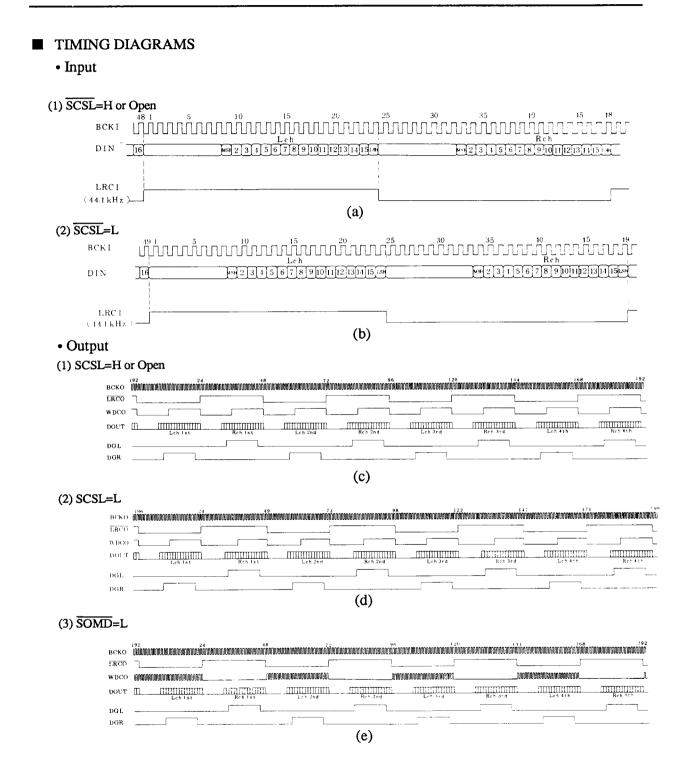

The SM5807 consists of two channel filters implemented in two times oversampling two stages cascaded linear phase FIR filter as shown in Fig 10. The 44.1KHz sampled signal.is two times oversampled in the 61-tap first filter stage and is converted to a 88.2KHz sample signal. It is further two times oversampled in the 13-tap second filter stage and becomes 176.4KHz sampled signal which is 4 times oversampled as compared with that at the input. Fig.11 illustrates sampled signal spectrum of the output of channel filter (see Fig.10). Fig.11(a) shows the output spectra of the first filter which provides -50dB or -45dB attenuation at and above 24.1KHz. However, the input signal spectrum of  $\pm 24.1$ KHz centered on 88.2KHz sampling frequency still exists. The second filter which further doubles the sampling frequency for filtering the output of the first filter provides -50dB or -45dB for the signal band between 64.1KHz and 112.3KHz as shown in Fig.11(b). The combined filter characteristics are illustrated in Fig.11(c). The SM5807 was designed based on this oversampling technique and their filter characteristics are illustrated in page 2 through 3.

Figure 10 Block Diagram of the Channel Filter.

Figure 11 Signal Spectra

■ FUNCTIONAL DESCRIPTION

| 1.System | Clock |  |

|----------|-------|--|

| FT 11    |       |  |

| The system clock freq | uency, 8.4672 l | MHz (=192fs) or 8. | .6436MHz(=196fs) is selected by |  |

|-----------------------|-----------------|--------------------|---------------------------------|--|

| SCSL logic level.     | SCSL=H (or of   | pen), fsc=192fs    | where fs=44.1kHz                |  |

|                       | SCSL=L,         | fsc=196fs          | where fs=44.1kHz                |  |

| Clock | Generation |

|-------|------------|

| CIOCK | Generation |

| SCSL                       | H (or open)                             |                                       | L                                       |                                         |

|----------------------------|-----------------------------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|

| CKSL                       | H (or open)                             | L                                     | Н                                       | L                                       |

| Clock Source               | Crystal oscillator<br>or external clock | Crystal Oscillator<br>or System Clock | Crystal Oscillator<br>or External Clock | Crystal Oscillator<br>or External Clock |

| XT/XT<br>Input Frequency   | 384fs=16.9344MHz                        | 192fs=8.4672MHz                       | 392fs=17.2872MHz                        | 196fs=8.6436MHz                         |

| CKO<br>Clock Output        | 384fs=16.9344MHz                        | 192fs=8.4672MHz                       | 392fs=17.2872MHz                        | 196fs=8.6436MHz                         |

| System Clock<br>(Internal) | 192fs=8.4672MHz                         | 192fs=8.4672MHz                       | 196fs=8.6436MHz                         | 196fs=8.6436MHz                         |

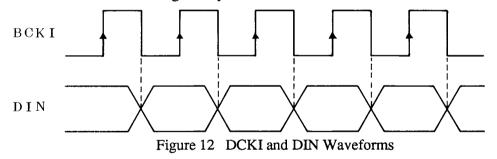

#### 2. Serial Input (data and bit clock)

The serial input data is entered at at the rising edge of serial input bit clock, BCKI. The data can be changed at the falling edge of BCKI. After the 16 bits data have been entered, they are latched in the internal register by the LRCI clock.

3. Input Data Format

The format is 2's complement, MSB first.

4. Starting of Data Process

The data process starts at the rising edge of LRCI clock.

5. Serial Output (data and bit clock)

The Lch and Rch serial data are delivered to pin DOUT alternately and therefore using one DAC for conversion is implementable. For using two DAC's, additional gates are required (see Fig.15,b). The serial output bit clock is available at pin BCKO.

| BCKO=8.4672MHz | (SCSL=H or open | system clock: 192fs) |

|----------------|-----------------|----------------------|

| BCKO=8.6436MHz | (SCSL=L         | system clock: 196fs) |

6.Output Data Format

The format is 2's complement, MSB first.

- 7. Deglitch Signals

- The 176.4kHz, 25% duty cycle deglitch signals are available at pins DGL and DGR for Lch and Rch respectively.

Figure 13 Serial Input and Output Timing Diagrams -9-

### APPLICATION DIAGRAMS

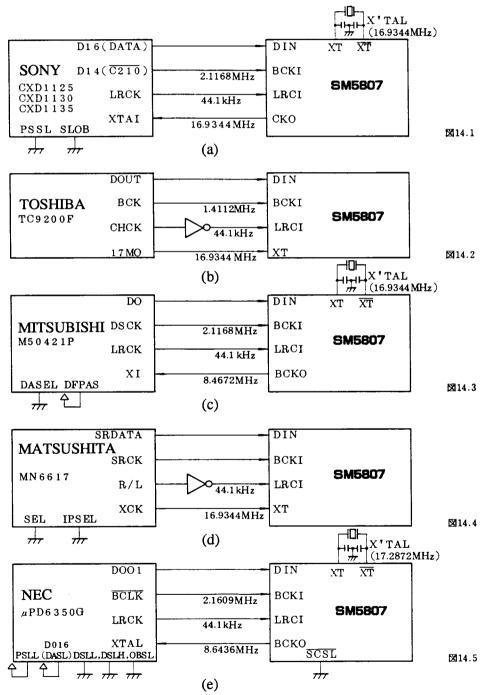

1. Input Connection

## 4-Time Oversampling Digital Filter for CD System

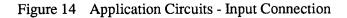

## 2. Output Connection

## a.1DAC

Figure 15 Application Circuit - Output connections