## PHASE-LOCKED-LOOP WITH VCO

#### **FEATURES**

- Low power consumption

- · Centre frequency of up to

17 MHz (typ.) at V<sub>CC</sub> = 4.5 V

Choice of three phase comparators: EXCLUSIVE-OR; edge-triggered JK flip-flop; edge-triggered RS flip-flop

- Excellent VCO frequency linearity

- VCO-inhibit control for ON/OFF keying and for low standby power consumption

- Minimal frequency drift

- Operating power supply voltage range:

VCO section 3.0 to 6.0 V digital section 2.0 to 6.0 V

- Zero voltage offset due to op-amp

buffering

- Output capability: standard

- I<sub>CC</sub> category: MSI

|                 |                                           |                                                  | TYF | UNIT |       |  |

|-----------------|-------------------------------------------|--------------------------------------------------|-----|------|-------|--|

| SYMBOL          | PARAMETER                                 | CONDITIONS                                       | нс  | нст  | CINIT |  |

| f <sub>o</sub>  | VCO centre frequency                      | C1 = 40 pF<br>R1 = 3 kΩ<br>V <sub>CC</sub> = 5 V | 19  | 19   | MHz   |  |

| CI              | input capacitance (pin 5)                 |                                                  | 3.5 | 3.5  | pF    |  |

| C <sub>PD</sub> | power dissipation capacitance per package | notes 1 and 2                                    | 24  | 24   | рF    |  |

GND = 0 V; Tamb = 25 °C

#### Note

1. CPD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

$$P_D = C_{PD} \times V_{CC}^2 \times f_i + \Sigma (C_L \times V_{CC}^2 \times f_0)$$

where:

f; = input frequency in MHz

CL = output load capacitance in pF

fo = output frequency in MHz

VCC = supply voltage in V

\(\tilde{\Sigma}\) (C<sub>L</sub> x \(\tilde{\Sigma}\) CC<sup>2</sup> x \(\tilde{\tilde{\Sigma}}\) of outputs

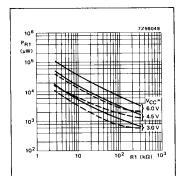

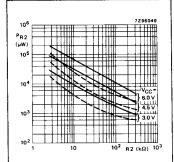

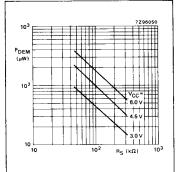

2. Applies to the phase comparator section only (VCO disabled). For power dissipation of the VCO and demodulator sections see Figs 22, 23 and 24.

#### PACKAGE OUTLINES

16-lead DIL; plastic (SOT38Z). 16-lead mini-pack; plastic (SO16; SOT109A).

#### **GENERAL DESCRIPTION**

The 74HC/HCT4046A are high-speed Si-gate CMOS devices and are pin compatible with the "4046" of the "4000B" series. They are specified in compliance with JEDEC standard no. 7A.

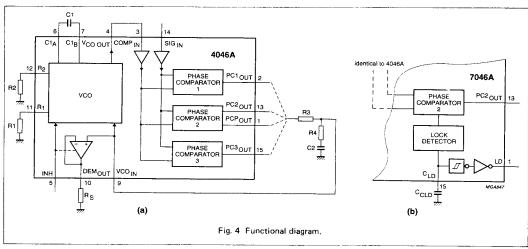

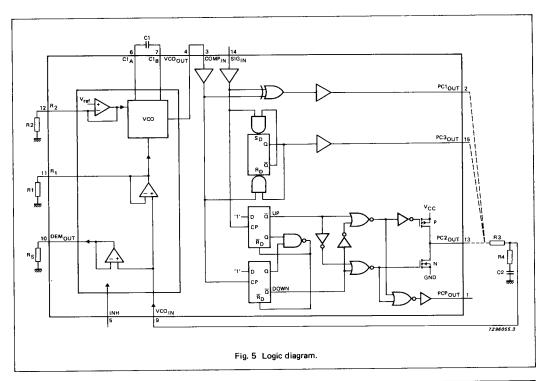

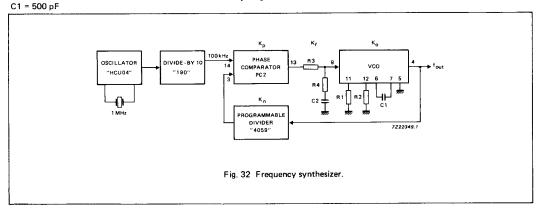

The 74HC/HCT4046A are phase-lockedloop circuits that comprise a linear voltage-controlled oscillator (VCO) and three different phase comparators (PC1, PC2 and PC3) with a common signal input amplifier and a common comparator input. The signal input can be directly coupled to large voltage signals, or indirectly coupled (with a series capacitor) to small voltage signals. A self-bias input circuit keeps small voltage signals within the linear region of the input amplifiers. With a passive low-pass filter, the "4046A" forms a second-order loop PLL. The excellent VCO linearity is achieved by the use of linear op-amp techniques. (continued on next page)

## APPLICATIONS

- FM modulation and demodulation

- Frequency synthesis and multiplication

- Frequency discrimination

- Tone decoding

- Data synchronization and conditioning

- Voltage-to-frequency conversion

- Motor-speed control

#### PIN DESCRIPTION

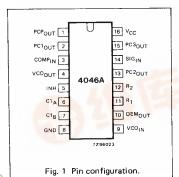

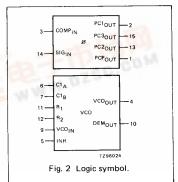

| PIN NO. | SYMBOL             | NAME AND FUNCTION             |

|---------|--------------------|-------------------------------|

| 1       | PCPOUT             | phase comparator pulse output |

| 2       | PC1 <sub>OUT</sub> | phase comparator 1 output     |

| 3       | COMPIN             | comparator input              |

| 4       | vco <sub>out</sub> | VCO output                    |

| 5       | INH                | inhibit input                 |

| 6       | C1 <sub>A</sub>    | capacitor C1 connection A     |

| 7       | C1 <sub>B</sub>    | capacitor C1 connection B     |

| 8       | GND                | ground (0 V)                  |

| 9       | VCOIN              | VCO input                     |

| 10      | DEMOUT             | demodulator output            |

| 11      | R <sub>1</sub>     | resistor R1 connection        |

| 12      | R <sub>2</sub>     | resistor R2 connection        |

| 13      | PC2 <sub>OUT</sub> | phase comparator 2 output     |

| 14      | SIGIN              | signal input                  |

| 15      | PC3 <sub>OUT</sub> | phase comparator 3 output     |

| 16      | Vcc                | positive supply voltage       |

## GENERAL DESCRIPTION (Cont'd) vco

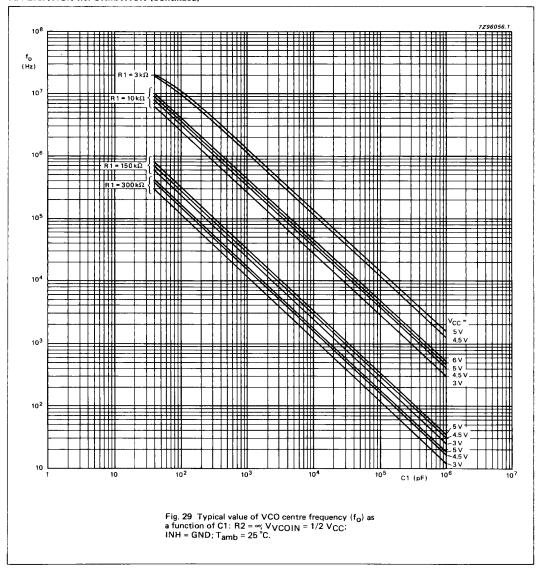

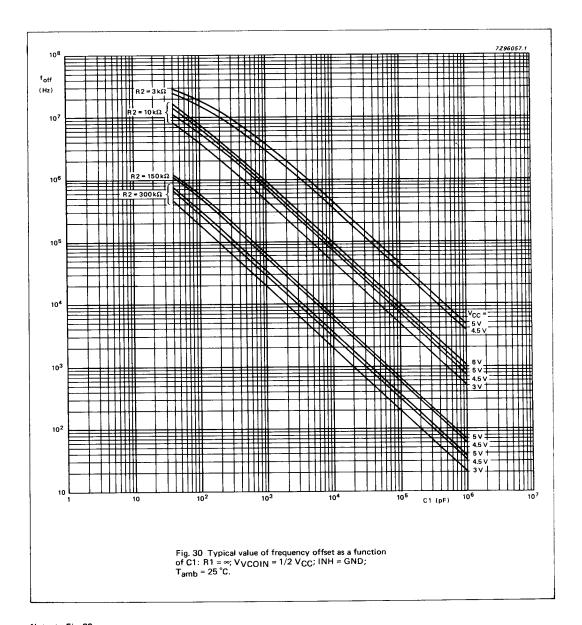

The VCO requires one external capacitor C1 (between C1A and C1B) and one external resistor R1 (between R1 and GND) or two external resistors R1 and R2 (between R1 and GND, and R2 and GND). Resistor R1 and capacitor C1 determine the frequency range of the VCO. Resistor R2 enables the VCO to have a frequency offset if required.

The high input impedance of the VCO simplifies the design of low-pass filters by giving the designer a wide choice of

resistor/capacitor ranges. In order not to load the low-pass filter, a demodulator output of the VCO input voltage is provided at pin 10 (DEMOUT). In contrast to conventional techniques where the DEMOUT voltage is one threshold voltage lower than the VCO input voltage, here the DEMOUT voltage equals that of the VCO input. If DEMOUT is used, a load resistor (RS) should be connected from DEMOUT to GND; if unused, DEMOUT should be left open. The VCO output (VCOOLIT) can be connected directly to the comparator input (COMP<sub>IN</sub>), or connected via a frequency-divider. The

VCO output signal has a duty factor of 50% (maximum expected deviation 1%), if the VCO input is held at a constant DC level. A LOW level at the inhibit input (INH) enables the VCO and demodulator, while a HIGH level turns both off to minimize standby power consumption.

The only difference between the HC and HCT versions is the input level specification of the INH input. This input disables the VCO section. The sections of the comparator are identical, so that there is no difference in the SIGIN (pin 14) or COMPIN (pin 3) inputs between the HC and HCT versions.

#### Phase comparators

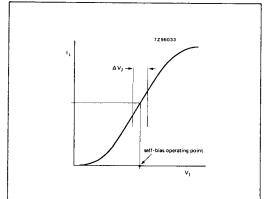

The signal input (SIGIN) can be directly coupled to the self-biasing amplifier at pin 14, provided that the signal swing is between the standard HC family input logic levels. Capacitive coupling is required for signals with smaller swings.

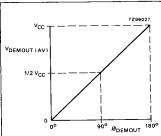

Phase comparator 1 (PC1)

This is an EXCLUSIVE-OR network. The signal and comparator input frequencies (fi) must have a 50% duty factor to obtain the maximum locking range. The transfer characteristic of PC1, assuming ripple  $(f_r = 2f_i)$  is suppressed, is:

$$V_{DEMOUT} = \frac{V_{CC}}{\pi} (\phi_{SIGIN} - \phi_{COMPIN})$$

where VDEMOUT is the demodulator output at pin 10; VDEMOUT = VPC1OUT (via low-pass

The phase comparator gain is:  $K_p = \frac{V_{CC}}{\pi} (V/r)$ .

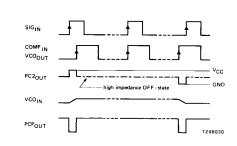

The average output voltage from PC1, fed to the VCO input via the low-pass filter and seen at the demodulator output at pin 10 (VDEMOUT), is the resultant of the phase differences of signals (SIG\_IN) and the comparator input (COMP\_IN) as shown in Fig. 6. The average of VDEMOUT is equal to 1/2 VCC when there is no signal or noise at SIG\_IN and with this input the VCO oscillates at the centre frequency (f\_o). Typical waveforms for the PC1 loop locked at f\_o are shown in Fig. 7.

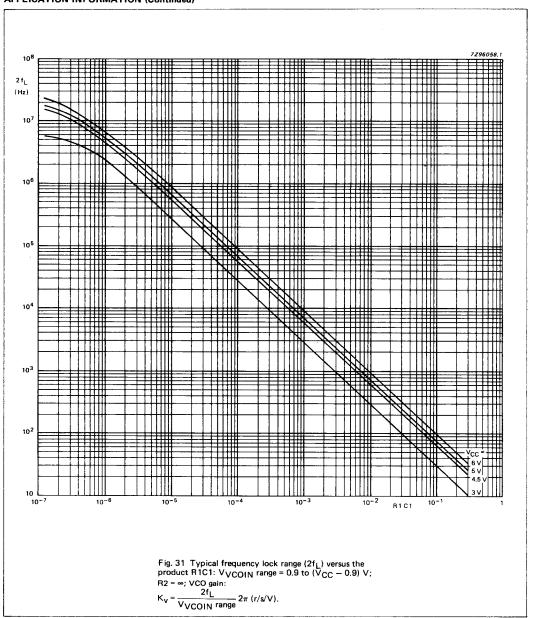

The frequency capture range  $(2f_{\rm c})$  is defined as the frequency range of input signals on which the PLL will lock if it was initially out-of-lock. The frequency lock range  $(2f_{\rm L})$  is defined as the frequency range of input signals on which the loop will stay locked if it was initially in lock. The capture range is smaller or equal to the lock range.

VDEMOUT = VPC10UT =

$\frac{V_{CC}}{\pi}(\phi_{SIGIN} - \phi_{COMPIN})$

$\phi$ DEMOUT =  $(\phi$ SIGIN -  $\phi$ COMPIN).

Fig. 7 Typical waveforms for PLL using phase comparator 1, loop locked at  $f_{\rm O}$ .

#### GENERAL DESCRIPTION (Cont'd)

#### Phase comparators (Cont'd)

With PC1, the capture range depends on the low-pass filter characteristics and can be made as large as the lock range. This configuration retains lock even with very noisy input signals. Typical behaviour of this type of phase comparator is that it can lock to input frequencies close to the harmonics of the VCO centre frequency.

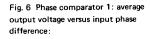

#### Phase comparator 2 (PC2)

This is a positive edge-triggered phase and frequency detector. When the PLL is using this comparator, the loop is controlled by positive signal transitions and the duty factors of SIGIN and COMPIN are not important. PC2 comprises two D-type flip-flops, control-gating and a 3-state output stage. The circuit functions as an up-down counter (Fig. 5) where SIGIN causes an up-count and COMPIN a down-count. The transfer function of PC2, assuming ripple ( $f_r=f_j$ ) is suppressed, is:

$V_{DEMOUT} = \frac{V_{CC}}{4\pi} (\phi_{SIGIN} - \phi_{COMPIN})$

where VDEMOUT is the demodulator output at pin 10;

VDEMOUT = VPC2OUT (via low-pass filter).

The phase comparator gain is:

$$K_p = \frac{V_{CC}}{4\pi} (V/r).$$

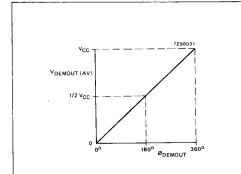

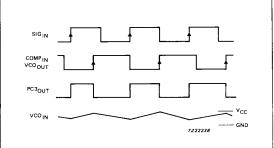

$V_{\mbox{\footnotesize{DEMOUT}}}$  is the resultant of the initial phase differences of SIG\_{IN} and COMP\_{IN} as shown in Fig. 8. Typical waveforms for the PC2 loop locked at  $f_{\mbox{\footnotesize{O}}}$  are shown in Fig. 9.

When the frequencies of SIGIN and COMPIN are equal but the phase of SIGIN leads that of COMPIN, the p-type output driver at PC2<sub>OUT</sub> is held "ON" for a time corresponding to the phase difference ( $\phi$ DEMOUT). When the phase of SIGIN lags that of COMPIN, the n-type driver is held "ON".

When the frequency of SIGIN is higher than that of COMPIN, the p-type output driver is held "ON" for most of the input signal cycle time, and for the remainder of the cycle both n and p- type drivers are "OFF" (3-state). If the SIGIN frequency

is lower than the COMP<sub>IN</sub> frequency, then it is the n-type driver that is held "ON" for most of the cycle. Subsequently, the voltage at the capacitor (C2) of the low-pass filter connected to PC2<sub>OUT</sub> varies until the signal and comparator inputs are equal in both phase and frequency. At this stable point the voltage on C2 remains constant as the PC2 output is in 3-state and the VCO input at pin 9 is a high impedance. Also in this condition, the signal at the phase comparator pulse output (PCP<sub>OUT</sub>) is a HIGH level and so can be used for indicating a locked condition.

Thus, for PC2, no phase difference exists between  $SIG_{1N}$  and  $COMP_{1N}$  over the full frequency range of the VCO. Moreover, the power dissipation due to the low-pass filter is reduced because both p and n-type drivers are "OFF" for most of the signal input cycle. It should be noted that the PLL lock range for this type of phase comparator is equal to the capture range and is independent of the low-pass filter. With no signal present at  $SIG_{1N}$  the VCO adjusts, via PC2, to its lowest frequency.

Fig. 8 Phase comparator 2: average output voltage versus input phase difference:

VDEMOUT = VPC2OUT =

$\frac{V_{CC}}{4\pi}(\phi_{SIGIN} - \phi_{COMPIN})$

$\phi$ DEMOUT =  $(\phi$ SIGIN -  $\phi$ COMPIN).

Fig. 9 Typical waveforms for PLL using phase comparator 2, loop locked at  $f_{\rm O}$ .

## Phase comparator 3 (PC3)

This is a positive edge-triggered sequential phase detector using an RS-type flip-flop. When the PLL is using this comparator, the loop is controlled by positive signal transitions and the duty factors of SIG  $_{IN}$  and COMP  $_{IN}$  are not important. The transfer characteristic of PC3, assuming ripple ( $f_{\rm r}=f_{\rm l}$ ) is suppressed, is:

$$V_{DEMOUT} = \frac{V_{CC}}{2\pi} (\phi_{SIGIN} - \phi_{COMPIN})$$

where VDEMOUT is the demodulator output at pin 10;

VDEMOUT = VPC3OUT (via low-pass filter).

The phase comparator gain is:

The phase compa

$$K_{p} = \frac{V_{CC}}{2\pi} (V/r).$$

The average output from PC3, fed to the VCO via the low-pass filter and seen at the demodulator output at pin 10 (VDEMOUT), is the resultant of the phase differences of SIG IN and COMP IN as shown in Fig. 10. Typical waveforms for the PC3 loop locked at fo are shown in Fig. 11.

The phase-to-output response characteristic of PC3 (Fig. 10) differs from that of PC2 in that the phase angle between SIGIN and COMPIN varies between 0° and 360° and is 180° at the

centre frequency. Also PC3 gives a greater voltage swing than PC2 for input phase differences but as a consequence the ripple content of the VCO input signal is higher. The PLL lock range for this type of phase comparator and the capture range are dependent on the low-pass filter. With no signal present at SIG<sub>IN</sub> the VCO adjusts, via PC3, to its lowest frequency.

Fig. 10 Phase comparator 3: average output voltage versus input phase difference:

V<sub>DEMOUT</sub> = V<sub>PC3OUT</sub> =

$$\frac{V_{CC}}{2\pi}(\phi_{SIGIN} - \phi_{COMPIN})$$

$\phi_{DEMOUT} = (\phi_{SIGIN} - \phi_{COMPIN}).$

Fig. 11 Typical waveforms for PLL using phase comparator 3, loop locked at  $f_{\rm O}$ .

# RECOMMENDED OPERATING CONDITIONS FOR 74HC/HCT

| SYMBOL                          | PARAMETER                                    |      |         |                    | 74HC | Г    |      | 004101710410 |                                                                               |  |

|---------------------------------|----------------------------------------------|------|---------|--------------------|------|------|------|--------------|-------------------------------------------------------------------------------|--|

|                                 | TOTAMETER                                    | min. | typ.    | max.               | min. | typ. | max. | UNIT         | CONDITIONS                                                                    |  |

| vcc                             | DC supply voltage                            | 3.0  | 5.0     | 6.0                | 4.5  | 5.0  | 5.5  | v            |                                                                               |  |

| vcc                             | DC supply voltage if VCO section is not used | 2.0  | 5.0     | 6.0                | 4.5  | 5.0  | 5.5  | V            |                                                                               |  |

| Vi                              | DC input voltage range                       | 0    |         | Vcc                | 0    |      | Vcc  | V            |                                                                               |  |

| v <sub>o</sub>                  | DC output voltage range                      | 0    |         | Vcc                | 0    |      | Vcc  | ν            |                                                                               |  |

| T <sub>amb</sub>                | operating ambient temperature range          | -40  | <u></u> | +85                | - 40 |      | +85  | °C           | see DC and AC                                                                 |  |

| T <sub>amb</sub>                | operating ambient temperature range          | -40  |         | +125               | -40  |      | +125 | °C           | CHARACTERISTICS                                                               |  |

| t <sub>r</sub> , t <sub>f</sub> | input rise and fall times (pin 5)            |      | 6.0     | 1000<br>500<br>400 |      | 6.0  | 500  | ns           | V <sub>CC</sub> = 2.0 V<br>V <sub>CC</sub> = 4.5 V<br>V <sub>CC</sub> = 6.0 V |  |

## **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Voltages are referenced to GND (ground = 0 V)

| SYMBOL           | PARAMETER                                 | MIN. | MAX. | UNIT | CONDITIONS                                                                                      |

|------------------|-------------------------------------------|------|------|------|-------------------------------------------------------------------------------------------------|

| v <sub>cc</sub>  | DC supply voltage                         | -0.5 | +7   | v    |                                                                                                 |

| ±11K             | DC input diode current                    |      | 20   | mA   | for $V_{I} < -0.5 \text{ V}$ or $V_{I} > V_{CC} + 0.5 \text{ V}$                                |

| ±loк             | DC output diode current                   | 1    | 20   | mA   | for V <sub>O</sub> < -0.5 V or V <sub>O</sub> > V <sub>CC</sub> + 0.5 V                         |

| ±10              | DC output source or sink current          |      | 25   | mA   | for -0.5 V < V <sub>O</sub> < V <sub>CC</sub> + 0.5 V                                           |

| ±ICC;<br>±IGND   | DC V <sub>CC</sub> or GND current         |      | 50   | mA   |                                                                                                 |

| T <sub>stg</sub> | storage temperature range                 | - 65 | +150 | °C   |                                                                                                 |

| P <sub>tot</sub> | power dissipation per package plastic DIL |      | 750  | mW   | for temperature range: -40 to +125 °C<br>74HC/HCT<br>above +70 °C: derate linearly with 12 mW/K |

|                  | plastic mini-pack (SO)                    |      | 500  | mW   | above +70 °C: derate linearly with 8 mW/K                                                       |

## DC CHARACTERISTICS FOR 74HC

## Quiescent supply current

Voltages are referenced to GND (ground = 0 V)

|          |                                         |                           | T <sub>amb</sub> (°C) |      |                 |       |      |       |    | TEST CONDITIONS |                                                                                                           |  |

|----------|-----------------------------------------|---------------------------|-----------------------|------|-----------------|-------|------|-------|----|-----------------|-----------------------------------------------------------------------------------------------------------|--|

| SYMBOL   | PARAMETER                               |                           | 74HC                  |      |                 |       |      |       |    |                 | OTUED                                                                                                     |  |

| STIVIBUL | PARAMETER                               | +25 -40 to +85 -40 to +12 | o +125                | UNIT | V <sub>CC</sub> | OTHER |      |       |    |                 |                                                                                                           |  |

|          |                                         | min.                      | typ.                  | max. | min.            | max.  | min. | max.  |    |                 |                                                                                                           |  |

| icc      | quiescent supply current (VCO disabled) |                           |                       | 8.0  |                 | 80.0  |      | 160,0 | μΑ | 6.0             | pins 3, 5, and 14 at V <sub>CC</sub> ;<br>pin 9 at GND; I <sub>I</sub> at pins<br>3 and 14 to be excluded |  |

## Phase comparator section

Voltages are referenced to GND (ground = 0 V)

|                  |                                                                                 |                    |                   | •                          | T <sub>amb</sub> ( | °C)                        |                    |                             |      | TEST CONDITIONS          |                                          |                                                                                  |  |

|------------------|---------------------------------------------------------------------------------|--------------------|-------------------|----------------------------|--------------------|----------------------------|--------------------|-----------------------------|------|--------------------------|------------------------------------------|----------------------------------------------------------------------------------|--|

| SYMBOL           | PARAMETER                                                                       |                    |                   |                            | 74H                | С                          |                    |                             | UNIT | .,                       | ,,                                       | OTHER                                                                            |  |

| STIMBUL          | FARAMETER                                                                       | +25                |                   |                            | -40 to +85         |                            | -40 to +125        |                             | UNIT | V <sub>CC</sub>          | Vį                                       | OTHER                                                                            |  |

|                  |                                                                                 | min.               | typ.              | max.                       | min.               | max.                       | min.               | max.                        | 1    |                          |                                          |                                                                                  |  |

| V <sub>1H</sub>  | DC coupled HIGH level input voltage SIGIN, COMPIN                               | 1.5<br>3.15<br>4.2 | 1.2<br>2.4<br>3.2 |                            | 1.5<br>3.15<br>4.2 |                            | 1.5<br>3.15<br>4.2 |                             | v    | 2.0<br>4.5<br>6.0        |                                          |                                                                                  |  |

| VIL              | DC coupled<br>LOW level input voltage<br>SIG <sub>IN</sub> , COMP <sub>IN</sub> |                    | 0.8<br>2.1<br>2.8 | 0.5<br>1.35<br>1.8         |                    | 0.5<br>1.35<br>1.8         |                    | 0.5<br>1.35<br>1.8          | v    | 2.0<br>4.5<br>6.0        |                                          |                                                                                  |  |

| V <sub>OH</sub>  | HIGH level output voltage PCPOUT, PCnOUT                                        | 1.9<br>4.4<br>5.9  | 2.0<br>4.5<br>6.0 |                            | 1.9<br>4.4<br>5.9  |                            | 1.9<br>4.4<br>5.9  |                             | v    | 2.0<br>4.5<br>6.0        | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 20 μA<br>- I <sub>O</sub> = 20 μA<br>- I <sub>O</sub> = 20 μA |  |

| v <sub>OH</sub>  | HIGH level output voltage PCPOUT, PCnOUT                                        | 3.98<br>5.48       |                   |                            | 3.84<br>5.34       |                            | 3.7<br>5.2         |                             | v    | 4.5<br>6.0               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 4.0 mA<br>- I <sub>O</sub> = 5.2 mA                           |  |

| V <sub>OL</sub>  | LOW level output voltage PCPOUT, PCnOUT                                         |                    | 0<br>0<br>0       | 0.1<br>0.1<br>0.1          |                    | 0.1<br>0.1<br>0.1          |                    | 0.1<br>0.1<br>0.1           | V    | 2.0<br>4.5<br>6.0        | VIH<br>or<br>VIL                         | I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA       |  |

| V <sub>OL</sub>  | LOW level output voltage PCPOUT, PCnOUT                                         |                    | 0.15<br>0.16      | 0.26<br>0.26               |                    | 0.33<br>0.33               |                    | 0.4<br>0.4                  | v    | 4.5<br>6.0               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 4.0 mA<br>I <sub>O</sub> = 5.2 mA                               |  |

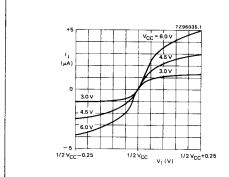

| ±I;              | input leakage current<br>SIG <sub>IN</sub> , COMP <sub>IN</sub>                 |                    |                   | 3.0<br>7.0<br>18.0<br>30.0 |                    | 4.0<br>9.0<br>23.0<br>38.0 |                    | 5.0<br>11.0<br>27.0<br>45.0 | μА   | 2.0<br>3.0<br>4.5<br>6.0 | V <sub>CC</sub><br>or<br>GND             |                                                                                  |  |

| ±I <sub>OZ</sub> | 3-state<br>OFF-state current<br>PC2 <sub>OUT</sub>                              |                    |                   | 0.5                        |                    | 5.0                        |                    | 10.0                        | μА   | 6.0                      | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | VO = VCC or                                                                      |  |

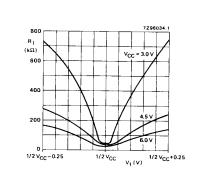

| R <sub>I</sub>   | input resistance<br>SIG <sub>IN</sub> , COMP <sub>IN</sub>                      |                    | 800<br>250<br>150 |                            |                    |                            |                    |                             | kΩ   | 3.0<br>4.5<br>6.0        | point;                                   | self-bias operating $\Delta V_{\parallel} = 0.5 \text{ V}$ ; gs 12, 13 and 14    |  |

# 74HC/HCT4046A MSI

# DC CHARACTERISTICS FOR 74HC (Cont'd) VCO section

Voltages are referenced to GND (ground = 0 V)

|                 |                                                               |                    |                   |                    | T <sub>amb</sub> ( | °C)                |                    |                    |      |                   | TEST C                                   | ONDITIONS                                                                        |

|-----------------|---------------------------------------------------------------|--------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|------|-------------------|------------------------------------------|----------------------------------------------------------------------------------|

| SYMBOL          | PARAMETER                                                     |                    |                   |                    | 74H                | С                  |                    |                    | 1    |                   |                                          |                                                                                  |

| OTHIDOL         | PANAMETER                                                     |                    | +25               |                    | -40                | to +85             | -40 t              | o +125             | UNIT | VCC               | VI                                       | OTHER                                                                            |

|                 |                                                               | min.               | typ.              | max.               | min.               | max.               | min.               | max.               |      |                   |                                          |                                                                                  |

| VIH             | HIGH level<br>input voltage<br>INH                            | 2.1<br>3.15<br>4.2 | 1.7<br>2.4<br>3.2 |                    | 2.1<br>3.15<br>4.2 |                    | 2.1<br>3.15<br>4.2 |                    | v    | 3.0<br>4.5<br>6.0 |                                          |                                                                                  |

| V <sub>IL</sub> | LOW level<br>input voltage<br>INH                             |                    | 1.3<br>2.1<br>2.8 | 0.9<br>1.35<br>1.8 |                    | 0,9<br>1,35<br>1.8 |                    | 0.9<br>1.35<br>1.8 | v    | 3.0<br>4.5<br>6.0 |                                          |                                                                                  |

| V <sub>OH</sub> | HIGH level<br>output voltage<br>VCO <sub>OUT</sub>            | 2.9<br>4.4<br>5.9  | 3.0<br>4.5<br>6.0 |                    | 2.9<br>4.4<br>5.9  |                    | 2.9<br>4.4<br>5.9  |                    | v    | 3.0<br>4.5<br>6.0 | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 20 μA<br>- I <sub>O</sub> = 20 μA<br>- I <sub>O</sub> = 20 μA |

| V <sub>OH</sub> | HIGH level<br>output voltage<br>VCO <sub>OUT</sub>            | 3.98<br>5.48       | 4.32<br>5.81      |                    | 3.84<br>5.34       |                    | 3.7<br>5.2         |                    | v    | 4.5<br>6.0        | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 4.0 mA<br>- I <sub>O</sub> = 5.2 mA                           |

| VOL             | LOW level<br>output voltage<br>VCOOUT                         |                    | 0<br>0<br>0       | 0.1<br>0.1<br>0.1  |                    | 0.1<br>0.1<br>0.1  |                    | 0.1<br>0.1<br>0.1  | v    | 3.0<br>4.5<br>6.0 | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA       |

| VOL             | LOW level<br>output voltage<br>VCOOUT                         |                    | 0.15<br>0.16      |                    |                    | 0.33<br>0.33       |                    | 0.4<br>0.4         | v    | 4.5<br>6.0        | V <sub>1H</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 4.0 mA<br>I <sub>O</sub> = 5.2 mA                               |

| v <sub>OL</sub> | LOW level output<br>voltage C1 <sub>A</sub> , C1 <sub>B</sub> |                    |                   | 0.40<br>0.40       |                    | 0.47<br>0.47       |                    | 0.54<br>0.54       | v    | 4.5<br>6.0        | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 4.0 mA<br>I <sub>O</sub> = 5.2 mA                               |

| ±1 <sub>1</sub> | input leakage current<br>INH, VCO <sub>IN</sub>               |                    |                   | 0.1                |                    | 1.0                |                    | 1.0                | μА   | 6.0               | V <sub>CC</sub><br>or<br>GND             |                                                                                  |

| R1              | resistor range                                                | 3.0<br>3.0<br>3.0  |                   | 300<br>300<br>300  |                    |                    |                    |                    | kΩ   | 3.0<br>4.5<br>6.0 |                                          | note 1                                                                           |

| R2              | resistor range                                                | 3.0<br>3.0<br>3.0  |                   | 300<br>300<br>300  |                    |                    |                    |                    | kΩ   | 3.0<br>4.5<br>6.0 |                                          | note 1                                                                           |

| C1              | capacitor range                                               | 40<br>40<br>40     |                   | no<br>limit        |                    |                    |                    |                    | рF   | 3.0<br>4.5<br>6.0 |                                          |                                                                                  |

| Vvcoin          | operating voltage<br>range at VCO <sub>IN</sub>               | 1.1<br>1.1<br>1.1  |                   | 1.9<br>3.4<br>5.9  |                    |                    |                    |                    | v    | 3.0<br>4.5<br>6.0 |                                          | over the range<br>specified for R1;<br>for linearity see<br>Figs 20 and 21.      |

## Note

<sup>1.</sup> The parallel value of R1 and R2 should be more than 2.7 k $\Omega$ . Optimum performance is achieved when R1 and/or R2 are/is > 10 k $\Omega$ .

## Demodulator section

Voltages are referenced to GND (ground = 0 V)

|                  |                                     |                |                   |            | T <sub>amb</sub> ( | °C)  |              |  |      | TEST CONDITIONS   |                                                                                                                      |  |

|------------------|-------------------------------------|----------------|-------------------|------------|--------------------|------|--------------|--|------|-------------------|----------------------------------------------------------------------------------------------------------------------|--|

|                  | PARAMETER                           | i i            |                   |            | 74H                | C    |              |  | UNIT | ],,               | OTHER                                                                                                                |  |

| SYMBOL           |                                     | +25            |                   |            | -40 to +85         |      | 5 -40 to +12 |  | ONIT | VCC               | OTHER                                                                                                                |  |

|                  | min.                                | typ.           | max.              | min.       | max.               | min. | max.         |  |      |                   |                                                                                                                      |  |

| RS               | resistor range                      | 50<br>50<br>50 |                   | 300<br>300 |                    |      |              |  | kΩ   | 3.0<br>4.5<br>6.0 | at R <sub>S</sub> $>$ 300 k $\Omega$ the leakage current can influence VDEMOUT                                       |  |

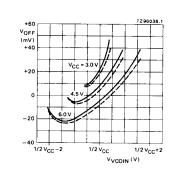

| V <sub>OFF</sub> | offset voltage<br>VCOIN to VDEMOUT  |                | ±30<br>±20<br>±10 |            |                    |      |              |  | mV   | 3.0<br>4.5<br>6.0 | V <sub>I</sub> = V <sub>VCOIN</sub> = 1/2 V <sub>CC</sub> ;<br>values taken over R <sub>S</sub> range<br>see Fig. 15 |  |

| RD               | dynamic output resistance at DEMOUT |                | 25<br>25<br>25    |            |                    |      |              |  | Ω    | 3.0<br>4.5<br>6.0 | V <sub>DEMOUT</sub> = 1/2 V <sub>CC</sub>                                                                            |  |

# 74HC/HCT4046A MSI

## **AC CHARACTERISTICS FOR 74HC**

## Phase comparator section

GND = 0 V;  $t_f = t_f = 6$  ns;  $C_L = 50$  pF

|                                                   |                                                                                                |      |                     | •               | T <sub>amb</sub> ( | °C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                  |      |                          | TEST CONDITIONS        |

|---------------------------------------------------|------------------------------------------------------------------------------------------------|------|---------------------|-----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|------|--------------------------|------------------------|

| SYMBOL                                            | PARAMETER                                                                                      |      |                     |                 | 74H                | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                  | UNIT |                          | OTHER                  |

| STWBOL                                            |                                                                                                | +25  |                     |                 | -40 to +85         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -40 to +125 |                  |      | V <sub>CC</sub>          | OTHER                  |

|                                                   |                                                                                                | min. | typ.                | max.            | min.               | max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | min.        | max.             |      |                          |                        |

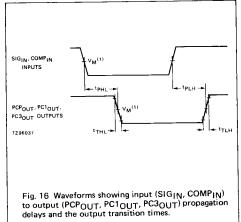

| <sup>t</sup> PHL <sup>/</sup><br>tPLH             | propagation delay<br>SIGIN, COMPIN<br>to PC1 <sub>OUT</sub>                                    |      | 63<br>23<br>18      | 200<br>40<br>34 |                    | 250<br>50<br>43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 300<br>60<br>51  | ns   | 2.0<br>4.5<br>6.0        | Fig. 16                |

| <sup>t</sup> PHL <sup>/</sup>                     | propagation delay<br>SIG <sub>IN</sub> , COMP <sub>IN</sub><br>to PCP <sub>OUT</sub>           |      | 96<br>35<br>28      | 340<br>68<br>58 |                    | 425<br>85<br>72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 510<br>102<br>87 | ns   | 2.0<br>4.5<br>6.0        | Fig. 16                |

| <sup>t</sup> PHL <sup>/</sup><br><sup>t</sup> PLH | propagation delay<br>SIGIN, COMPIN<br>to PC3 <sub>OUT</sub>                                    |      | 77<br>28<br>22      | 270<br>54<br>46 |                    | 340<br>68<br>58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 405<br>81<br>69  | ns   | 2.0<br>4.5<br>6.0        | Fig. 16                |

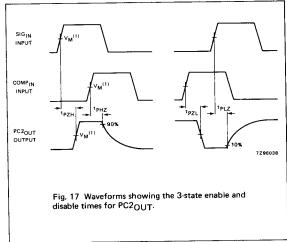

| <sup>t</sup> PZH <sup>/</sup><br><sup>t</sup> PZL | 3-state output enable time SIG <sub>IN</sub> , COMP <sub>IN</sub> to PC2 <sub>OUT</sub>        |      | 83<br>30<br>24      | 280<br>56<br>48 |                    | 350<br>70<br>60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 420<br>84<br>71  | ns   | 2.0<br>4.5<br>6.0        | Fig. 17                |

| <sup>t</sup> PHZ <sup>/</sup><br><sup>t</sup> PLZ | 3-state output disable<br>time SIG <sub>IN</sub> , COMP <sub>IN</sub><br>to PC2 <sub>OUT</sub> |      | 99<br>36<br>29      | 325<br>65<br>55 |                    | 405<br>81<br>69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | 490<br>98<br>83  | ns   | 2.0<br>4.5<br>6.0        | Fig. 17                |

| <sup>t</sup> THL <sup>/</sup><br><sup>t</sup> TLH | output transition time                                                                         |      | 19<br>7<br>6        | 75<br>15<br>13  |                    | 95<br>19<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | 110<br>22<br>19  | ns   | 2.0<br>4.5<br>6.0        | Fig. 16                |

| V <sub>I(p-p)</sub>                               | AC coupled input sensitivity<br>(peak-to-peak value) at<br>SIGIN or COMPIN                     |      | 9<br>11<br>15<br>33 |                 |                    | And the second s |             |                  | mV   | 2.0<br>3.0<br>4.5<br>6.0 | f <sub>i</sub> = 1 MHz |

## VCO section

$\mathsf{GND} = \mathsf{0} \; \mathsf{V}; \, \mathsf{t_f} = \mathsf{t_f} = \mathsf{6} \; \mathsf{ns}; \, \mathsf{C_L} = \mathsf{50} \; \mathsf{pF}$

|            |                                                   |                     | T <sub>amb</sub> (°C) |      |                      |      |             |      |      | TEST CONDITIONS   |                                                                                                                |  |

|------------|---------------------------------------------------|---------------------|-----------------------|------|----------------------|------|-------------|------|------|-------------------|----------------------------------------------------------------------------------------------------------------|--|

| SYMBOL     | DADAMETER                                         |                     |                       |      | 74H                  | C    |             |      |      |                   |                                                                                                                |  |

| STIMBUL FA | PARAMETER                                         | +25                 |                       |      | -40 to +85           |      | -40 to +125 |      | UNIT | V <sub>CC</sub>   | OTHER                                                                                                          |  |

|            |                                                   | min.                | typ.                  | max. | typ.                 | max. | min.        | max. |      |                   |                                                                                                                |  |

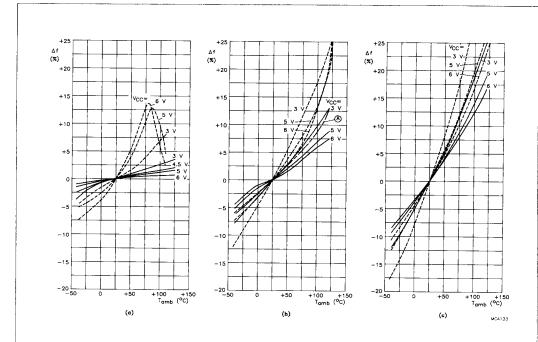

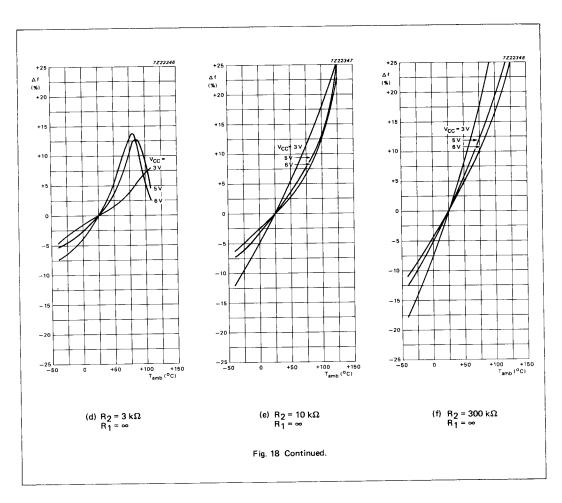

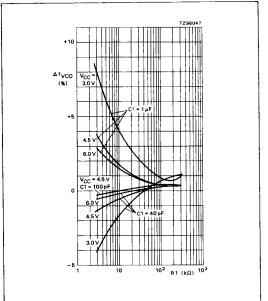

| ∆f/T       | frequency stability<br>with temperature<br>change |                     |                       |      | 0.20<br>0.15<br>0.14 |      |             |      | %/K  | 3.0<br>4.5<br>6.0 | $V_{\parallel} = V_{VCOIN} = 1/2 V_{CC};$<br>R1 = 100 k $\Omega$ ; R2 = $\infty$ ;<br>C1 = 100 pF; see Fig. 18 |  |

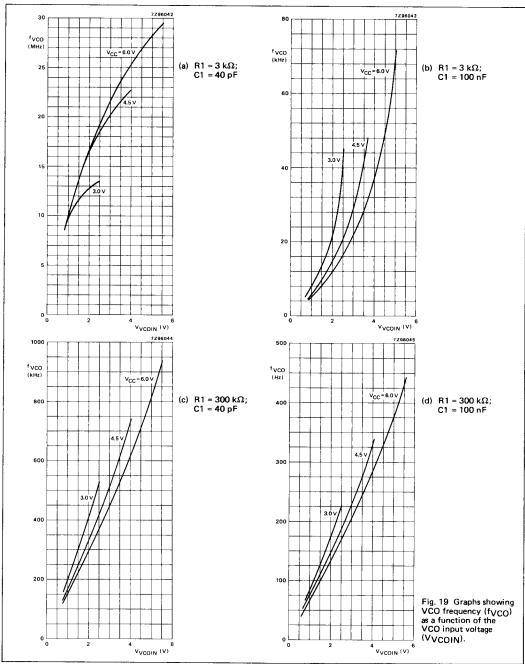

| fo         | VCO centre frequency<br>(duty factor = 50%)       | 3.0<br>11.0<br>13.0 |                       |      |                      |      |             |      | MHz  | 3.0<br>4.5<br>6.0 | $V_{VCOIN} = 1/2 V_{CC};$<br>$R1 = 3 k\Omega; R2 = \infty;$<br>C1 = 40 pF; see Fig. 19                         |  |

| ∆fvco      | VCO frequency linearity                           |                     | 1.0<br>0.4<br>0.3     |      |                      |      |             |      | %    | 3.0<br>4.5<br>6.0 | R1 = 100 kΩ; R2 = ∞;<br>C1 = 100 pF;<br>see Figs 20 and 21                                                     |  |

| δvco       | duty factor at VCO <sub>OUT</sub>                 |                     | 50<br>50<br>50        |      |                      |      |             |      | %    | 3.0<br>4.5<br>6.0 |                                                                                                                |  |

## DC CHARACTERISTICS FOR 74HCT

Quiescent supply current

Voltages are referenced to GND (ground = 0 V)

| ·      |                                                                                                                                     | T <sub>amb</sub> (°C) |      |      |            |      |             |       |      | TEST CONDITIONS  |                                                                                                          |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------------|------|-------------|-------|------|------------------|----------------------------------------------------------------------------------------------------------|--|

|        |                                                                                                                                     |                       |      |      |            |      |             |       |      | V                | OTHER                                                                                                    |  |

| SYMBOL | DL PARAMETER                                                                                                                        | +25                   |      |      | -40 to +85 |      | -40 to +125 |       | UNIT | V <sub>CC</sub>  | Omen                                                                                                     |  |

|        |                                                                                                                                     | min.                  | typ. | max. | min.       | max. | min.        | max.  |      |                  |                                                                                                          |  |

| lcc    | quiescent supply current (VCO disabled)                                                                                             |                       |      | 8.0  |            | 80.0 |             | 160.0 | μА   | 6.0              | pins 3, 5 and 14 at V <sub>CC</sub> ;<br>pin 9 at GND; I <sub>1</sub> at pins<br>3 and 14 to be excluded |  |

| ΔICC   | additional quiescent supply current per input pin for unit load coefficient is 1 (note 1)  V <sub>I</sub> = V <sub>CC</sub> - 2.1 V |                       | 100  | 360  |            | 450  |             | 490   | μΑ   | 4.5<br>to<br>5.5 | pins 3 and 14 at V <sub>CC</sub> ;<br>pin 9 at GND; I <sub>1</sub> at pins<br>3 and 14 to be excluded    |  |

#### Note

1. The value of additional quiescent supply current ( $\Delta l_{CC}$ ) for a unit load of 1 is given above. To determine  $\Delta l_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT | UNIT LOAD<br>COEFFICIENT |

|-------|--------------------------|

| INH   | 1.00                     |

# 74HC/HCT4046A MSI

## DC CHARACTERISTICS FOR 74HCT

## Phase comparator section

Voltages are referenced to GND (ground = 0 V)

|                 |                                                                           |      |      | -    | т <sub>ать</sub> ( | °C)  |             |      |      | TEST CONDITIONS |                                          |                                                                      |  |

|-----------------|---------------------------------------------------------------------------|------|------|------|--------------------|------|-------------|------|------|-----------------|------------------------------------------|----------------------------------------------------------------------|--|

|                 | PARAMETER                                                                 |      |      |      | 74HC               | т    |             |      |      | 071150          |                                          |                                                                      |  |

| SYMBOL          |                                                                           | +25  |      |      | -40 to +85         |      | -40 to +125 |      | UNIT | VCC             | VI                                       | OTHER                                                                |  |

|                 |                                                                           | min. | typ. | max. | min.               | max. | min.        | max. |      |                 |                                          |                                                                      |  |

| VIH             | DC coupled<br>HIGH level input voltage<br>SIGIN, COMPIN                   | 3.15 | 2.4  |      |                    |      |             |      | ٧    | 4.5             |                                          |                                                                      |  |

| VIL             | DC coupled LOW level input voltage SIG <sub>IN</sub> , COMP <sub>IN</sub> |      | 2.1  | 1.35 |                    |      |             |      | v    | 4.5             |                                          |                                                                      |  |

| V <sub>OH</sub> | HIGH level output voltage<br>PCP <sub>OUT</sub> , PC <sub>nOUT</sub>      | 4.4  | 4.5  |      | 4.4                |      | 4.4         |      | v    | 4.5             | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 20 μA                                             |  |

| V <sub>OH</sub> | HIGH level output voltage PCPOUT, PCnOUT                                  | 3.98 | 4.32 |      | 3.84               |      | 3.7         |      | v    | 4.5             | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 4.0 mA                                            |  |

| v <sub>OL</sub> | LOW level output voltage<br>PCPOUT, PCnOUT                                |      | 0    | 0.1  |                    | 0.1  |             | 0.1  | v    | 4.5             | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | ΙΟ = 20 μΑ                                                           |  |

| VOL             | LOW level output voltage<br>PCP <sub>OUT</sub> , PC <sub>nOUT</sub>       |      | 0.15 | 0.26 |                    | 0.33 |             | 0.4  | v    | 4.5             | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 4.0 mA                                              |  |

| ±II             | input leakage current<br>SIG <sub>1N</sub> , COMP <sub>1N</sub>           |      |      | 30   |                    | 38   |             | 45   | μΑ   | 5.5             | V <sub>CC</sub><br>or<br>GND             |                                                                      |  |

| ±10Z            | 3-state OFF-state current PC2 <sub>OUT</sub>                              |      |      | 0.5  |                    | 5.0  |             | 10.0 | μΑ   | 5.5             | VIH<br>or<br>VIL                         | VO = VCC or<br>GND                                                   |  |

| R <sub>I</sub>  | input resistance<br>SIG <sub>IN</sub> , COMP <sub>IN</sub>                |      | 250  |      |                    |      |             |      | kΩ   | 4.5             | point                                    | self-bias operating<br>$\triangle V_1 = 0.5 V_2$<br>gs 12, 13 and 14 |  |

# DC CHARACTERISTICS FOR 74HCT VCO section

Voltages are referenced to GND (ground = 0 V)

|                 |                                                                                       |      |      | T           | amb (        |        | TEST CONDITIONS |      |      |                  |                                          |                                                                             |

|-----------------|---------------------------------------------------------------------------------------|------|------|-------------|--------------|--------|-----------------|------|------|------------------|------------------------------------------|-----------------------------------------------------------------------------|

| SYMBOL          |                                                                                       |      |      |             | 74HC         | т      | UNIT            | .,   |      | OTHER            |                                          |                                                                             |

|                 | PARAMETER                                                                             | +25  |      |             | <b>-40</b> 1 | to +85 | -40 to +125     |      | וואט | V <sub>CC</sub>  | Vi                                       | UINER                                                                       |

|                 |                                                                                       | min. | typ. | max.        | min.         | max.   | min.            | max. | ]    |                  |                                          |                                                                             |

| V <sub>IH</sub> | HIGH level<br>input voltage<br>INH                                                    | 2.0  | 1.6  |             | 2.0          |        | 2.0             |      | v    | 4.5<br>to<br>5.5 |                                          |                                                                             |

| VIL             | LOW level<br>input voltage<br>INH                                                     |      | 1.2  | 0.8         |              | 8.0    |                 | 0.8  | v    | 4.5<br>to<br>5.5 |                                          |                                                                             |

| V <sub>OH</sub> | HIGH level<br>output voltage<br>VCOOUT                                                | 4.4  | 4.5  |             | 4.4          |        | 4.4             |      | V    | 4.5              | VIH<br>or<br>VIL                         | - I <sub>O</sub> = 20 μA                                                    |

| V <sub>OH</sub> | HIGH level<br>output voltage<br>VCOOUT                                                | 3.98 | 4.32 |             | 3.84         |        | 3.7             |      | v    | 4.5              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | - I <sub>O</sub> = 4.0 mA                                                   |

| VOL '           | LOW level<br>output voltage<br>VCOOUT                                                 |      | 0    | 0.1         |              | 0.1    |                 | 0.1  | v    | 4.5              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | 1 <sub>O</sub> = 20 μΑ                                                      |

| VOL             | LOW level<br>output voltage<br>VCOOUT                                                 |      | 0.15 | 0.26        |              | 0.33   |                 | 0.4  | V    | 4.5              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 4.0 mA                                                     |

| v <sub>OL</sub> | LOW level output<br>voltage C1 <sub>A</sub> , C1 <sub>B</sub><br>(test purposes only) |      |      | 0.40        |              | 0.47   |                 | 0.54 | v    | 4.5              | VIH<br>or<br>VIL                         | I <sub>O</sub> = 4.0 mA                                                     |

| ±IĮ             | input leakage current<br>INH, VCO <sub>IN</sub>                                       |      |      | 0.1         |              | 1.0    |                 | 1.0  | μА   | 5.5              | V <sub>CC</sub><br>or<br>GND             |                                                                             |

| R1              | resistor range                                                                        | 3.0  |      | 300         |              |        |                 |      | kΩ   | 4.5              | _                                        | note 1                                                                      |

| R2              | resistor range                                                                        | 3.0  |      | 300         |              |        |                 |      | kΩ   | 4.5              | <u> </u>                                 | note 1                                                                      |

| C1              | capacitor range                                                                       | 40   |      | no<br>limit |              |        |                 |      | pF   | 4.5              |                                          |                                                                             |

| VVCOIN          | operating voltage range at VCOIN                                                      | 1.1  |      | 3.4         |              |        |                 |      | V    | 4.5              |                                          | over the range<br>specified for R1;<br>for linearity see<br>Figs 20 and 21. |

### Note

<sup>1.</sup> The parallel value of R1 and R2 should be more than 2.7 k $\Omega$ . Optimum performance is achieved when R1 and/or R2 are/is > 10 k $\Omega$ .

# 74HC/HCT4046A MSI

# DC CHARACTERISTICS FOR 74HCT

## Demodulator section

Voltages are referenced to GND (ground = 0 V)

|                  |                                                            | T <sub>amb</sub> (°C) |      |      |            |      |             |      |        | TEST CONDITIONS |                                                                                                                      |  |

|------------------|------------------------------------------------------------|-----------------------|------|------|------------|------|-------------|------|--------|-----------------|----------------------------------------------------------------------------------------------------------------------|--|