#### **Philips Semiconductors**

#### 提多邦,专业PCB打样工厂,24小时

8-bit serial-in/serial or parallel-out shift register with output latches; 3-state

1月74日CS95N&NDSP,1共应格

### **74HC7HCT595**

#### FEATURES

- 8-bit serial input

- 8-bit serial or parallel output

- Storage register with 3-state outputs

- Shift register with direct clear

- 100 MHz (typ) shift out frequency

- · Output capability:

- parallel outputs; bus driver

- serial output; standard

- I<sub>cc</sub> category: MSI.

#### **APPLICATIONS**

- Serial-to-parallel data conversion

- Remote control holding register.

#### DESCRIPTION

The 74HC/HCT595 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

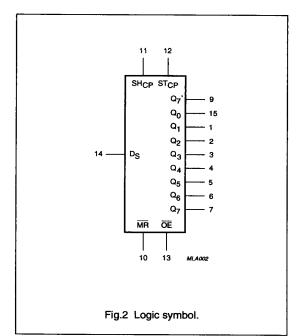

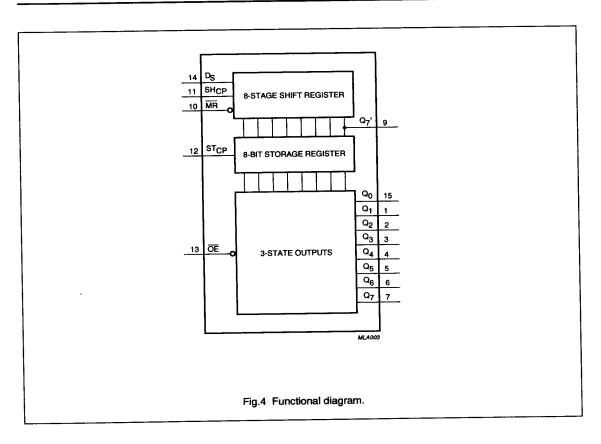

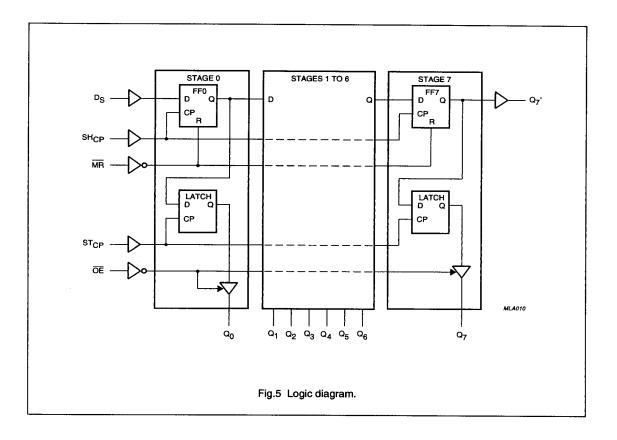

The "595" is an 8-stage serial shift register with a storage register and 3-state outputs. The shift register and storage register have separate clocks.

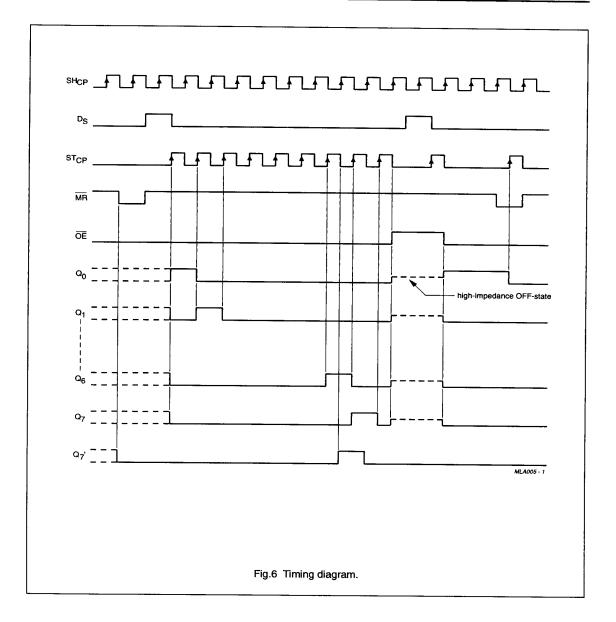

Data is shifted on the positive-going transitions of the  $SH_{CP}$  input. The data in each register is transferred to the storage register on a positive-going transition of the  $ST_{CP}$  input. If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register.

#### QUICK REFERENCE DATA

GND = 0 V;  $T_{amb} = 25 \text{ °C}$ ;  $t_r = t_f = 6 \text{ ns}$ .

stages. The storage register has 8 parallel 3-state bus driver outputs. Data in the storage register appears at the output whenever the output enable input (OE) is LOW.

| SYMBOL                             |                                                                                              | CONDITIONS                                      | T١             |                |                |

|------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------|----------------|----------------|----------------|

|                                    | PARAMETER                                                                                    | CONDITIONS                                      | НС             | нст            | UNIT           |

| t <sub>phl</sub> /t <sub>plh</sub> | propagation delay<br>SH <sub>CP</sub> to $Q_7'$<br>ST <sub>CP</sub> to $Q_n$<br>MR to $Q_7'$ | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | 16<br>17<br>14 | 21<br>20<br>19 | ns<br>ns<br>ns |

| f <sub>max</sub>                   | maximum clock<br>frequency SH <sub>CP</sub> , ST <sub>CP</sub>                               |                                                 | 100            | 57             | MHz            |

| Cı                                 | input capacitance                                                                            |                                                 | 3.5            | 3.5            | pF             |

| C <sub>PD</sub>                    | power dissipation<br>capacitance per<br>package                                              | notes 1 and 2                                   | 115            | 130            | pF             |

#### Notes

$C_{PD}$  is used to determine the dynamic power dissipation ( $P_{D}$  in  $\mu W$ ):

$P_D = C_{PD} \times V_{CC}^2 \times f_i + \Sigma (C_L \times V_{CC}^2 \times f_o)$  where:

- $f_i = input frequency in MHz$   $C_L = output load capacitance in pF$

- f<sub>e</sub> = output frequency in MHz V<sub>cc</sub> = supply voltage in V

- $\Sigma(C_L \times V_{CC}^2 \times f_o) = \text{sum of outputs.}$

For HC the condition is  $V_i$  = GND to  $V_{cc}$ For HCT the condition is  $V_i$  = GND to  $V_{cc}$  - 1.5 V.

#### **ORDERING INFORMATION**

| EXTENDED TYPE | PACKAGE |              |          |         |  |  |  |  |  |

|---------------|---------|--------------|----------|---------|--|--|--|--|--|

| NUMBER        | PINS    | PIN POSITION | MATERIAL | CODE    |  |  |  |  |  |

| 74HC/HCT595N  | 16      | DIL          | plastic  | SOT38Z  |  |  |  |  |  |

| 74HC/HCT595D  | 16      | SO16         | plastic  | SOT109A |  |  |  |  |  |

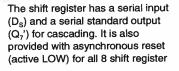

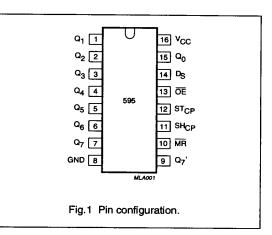

#### PINNING

| SYMBOL                          | PIN       | DESCRIPTION                  |

|---------------------------------|-----------|------------------------------|

| Q <sub>0</sub> - Q <sub>7</sub> | 15, 1 - 7 | parallel data output         |

| GND                             | 8         | ground (0 V)                 |

| Q <sub>7</sub> '                | 9         | serial data output           |

| MR                              | 10        | master reset (active LOW)    |

| SH <sub>CP</sub>                | 11        | shift register clock input   |

| ST <sub>CP</sub>                | 12        | storage register clock input |

| ŌĒ                              | 13        | output enable (active LOW)   |

| Ds                              | 14        | serial data input            |

| V <sub>cc</sub>                 | 16        | positive supply voltage      |

74HC/HCT595

# 8-bit serial-in/serial or parallel-out shift register with output latches; 3-state

### 74HC/HCT595

#### FUNCTION TABLE

| INPUTS           |                  |    |    |    | OU               | PTUTS            | FUNCTION                                                                                                                                                                                                            |  |  |  |

|------------------|------------------|----|----|----|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SH <sub>CP</sub> | ST <sub>CP</sub> | ŌĒ | MR | Ds | Q7'              | Q                |                                                                                                                                                                                                                     |  |  |  |

| X                | X                | L  | Ļ  | x  | L                | NC               | a LOW level on MR only affects the shift registers                                                                                                                                                                  |  |  |  |

| x                | 1                | L  | L  | x  | L                | L                | empty shift register loaded into storage register                                                                                                                                                                   |  |  |  |

| x                | x                | н  | L  | x  | L                | z                | shift register clear. Parallel<br>outputs in high-impedance<br>OFF-state                                                                                                                                            |  |  |  |

| <b>↑</b>         | x                | L  | н  | н  | Q <sub>6</sub> ' | NC               | logic high level shifted into shift<br>register stage 0. Contents of all<br>shift register stages shifted<br>through, e.g. previous state of<br>stage 6 (internal $Q_6$ ) appears on<br>the serial output ( $Q_7$ ) |  |  |  |

| x                | <i>,</i> ↑       | L  | н  | x  | NC               | Q <sub>n</sub> ' | contents of shift register stages<br>(internal $Q_n$ ) are transferred to<br>the storage register and parallel<br>output stages                                                                                     |  |  |  |

| <b>↑</b>         | 1                | L  | н  | x  | Q <sub>6</sub> ' | Q <sub>n</sub> ' | contents of shift register shifted<br>through. Previous contents of the<br>shift register is transferred to the<br>storage register and the parallel<br>output stages.                                              |  |  |  |

H = HIGH voltage level

- L = LOW voltage level

- ↑ = LOW-to-HIGH transition

$\downarrow$  = HIGH-to-LOW transition

- Z = high-impedance OFF-state

- NC = no change

- X = don't care.

#### DC CHARACTERISTICS FOR 74HC

For the DC characteristics see chapter "HCMOS family characteristics", section "Family specifications".

Output capability: parallel outputs, bus driver; serial output, standard Icc category: MSI.

#### AC CHARACTERISTICS FOR 74HC

$GND = 0 V; t_r = t_i = 6 ns; C_L = 50 pF.$

|                                    |                                                           | T <sub>amb (°C)</sub> |     |     |     |       |       |      |      | TEST CONDITION         |            |

|------------------------------------|-----------------------------------------------------------|-----------------------|-----|-----|-----|-------|-------|------|------|------------------------|------------|

| SYMBOL                             | PARAMETER                                                 |                       | +25 |     |     | o +85 | 40 to | +125 | UNIT | V <sub>cc</sub><br>(V) | WAVEFORMS  |

|                                    |                                                           | MIN                   | ТҮР | MAX | MIN | MAX   | MIN   | MAX  |      |                        |            |

|                                    |                                                           | -                     | 52  | 160 | -   | 200   | -     | 240  | ns   | 2.0                    |            |

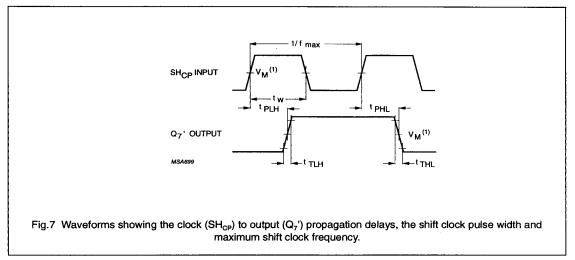

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay<br>SH <sub>CP</sub> to Q <sub>7</sub> ' | -                     | 19  | 32  | -   | 40    | -     | 48   | ns   | 4.5                    | Fig.7      |

|                                    | SHCP IO Q7                                                | -                     | 15  | 27  | -   | 34    |       | 41   | ns   | 6.0                    |            |

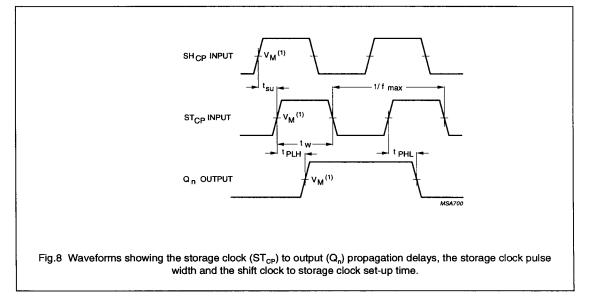

|                                    |                                                           | -                     | 55  | 175 | -   | 220   | -     | 265  | ns   | 2.0                    | <b>F</b> 0 |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay                                         | -                     | 20  | 35  | ]-  | 44    | -     | 53   | ns   | 4.5                    | Fig.8      |

|                                    | SICPIOUn                                                  | -                     | 16  | 30  | -   | 37    |       | 45   | ns   | 6.0                    |            |

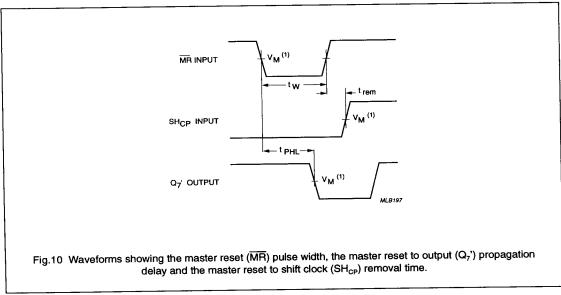

|                                    |                                                           | -                     | 47  | 175 |     | 220   | 1-    | 265  | ns   | 2.0                    | Fi 40      |

| t <sub>PHL</sub>                   | propagation delay<br>MR to Q7'                            | -                     | 17  | 35  | 1-  | 44    | -     | 53   | ns   | 4.5                    | Fig.10     |

| 1112                               |                                                           | -                     | 14  | 30  | -   | 37    | -     | 45   | ns   | 6.0                    |            |

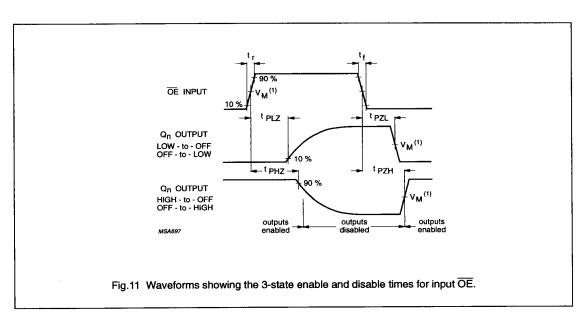

|                                    | 3-state output                                            | -                     | 47  | 150 | -   | 190   | -     | 225  | ns   | 2.0                    |            |

| t <sub>PZH</sub> /t <sub>PZL</sub> | enable time                                               | -                     | 17  | 30  | -   | 38    | 1-    | 45   | ns   | 4.5                    | Fig.11     |

| ·F2H ·F2L                          | OE to Q <sub>n</sub>                                      | -                     | 14  | 26  | -   | 33    | -     | 38   | ns   | 6.0                    |            |

|                                    | 3-state output                                            | -                     | 41  | 150 | -   | 190   | -     | 225  | ns   | 2.0                    |            |

| t <sub>PHZ</sub> /t <sub>PLZ</sub> | disable time<br>OE to Qn                                  | -                     | 15  | 30  | -   | 38    | -     | 45   | ns   | 4.5                    | Fig.11     |

| PHZ PLZ                            |                                                           | -                     | 12  | 26  | -   | 33    |       | 38   | ns   | 6.0                    |            |

|                                    | shift clock pulse<br>width HIGH or<br>LOW                 | 75                    | 17  | -   | 95  | T-    | 110   | -    | ns   | 2.0                    |            |

| t <sub>w</sub>                     |                                                           | 15                    | 6   | -   | 19  | -     | 22    |      | ns   | 4.5                    | Fig.7      |

| •₩                                 |                                                           | 13                    | 5   | -   | 16  | -     | 19    |      | ns   | 6.0                    |            |

| ·                                  | storage clock                                             | 75                    | 11  | -   | 95  | Τ_    | 110   | -    | ns   | 2.0                    |            |

| tw                                 |                                                           | 15                    | 4   | -   | 19  | -     | 22    | -    | ns   | 4.5                    | Fig.8      |

| -00                                | or LOW                                                    | 13                    | 3   | -   | 16  | -     | 19    |      | ns   | 6.0                    |            |

|                                    |                                                           | 75                    | 17  | _   | 95  | _     | 110   | -    | ns   | 2.0                    |            |

| tw                                 | master reset                                              | 15                    | 6.0 | -   | 19  | -     | 22    | -    | ns   | 4.5                    | Fig.10     |

| -vv                                | pulse width LOW                                           | 13                    | 5.0 | -   | 16  | 1     | 19    | -    | ns   | 6.0                    |            |

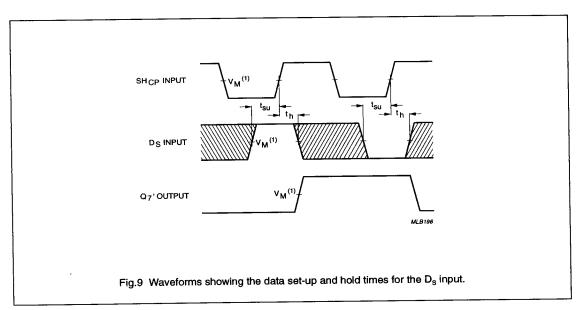

|                                    |                                                           | 50                    | 11  | -   | 65  |       | 75    | -    | ns   | 2.0                    |            |

| t <sub>su</sub>                    | set-up time Ds to                                         | 10                    | 4.0 | -   | 13  | -     | 15    | -    | ns   | 4.5                    | Fig.9      |

| -su                                | SHCP                                                      | 9.0                   | 3.0 | 1-  | 11  | -     | 13    | -    | ns   | 6.0                    |            |

|                                    |                                                           | 75                    | 22  |     | 95  | -     | 110   | -    | ns   | 2.0                    |            |

| t <sub>su</sub>                    | set-up time SH <sub>CP</sub>                              | 15                    | 8   | -   | 19  | -     | 22    | -    | ns   | 4.5                    | Fig.8      |

| ารน                                | to ST <sub>CP</sub>                                       | 13                    | 7   | -   | 16  | -     | 19    |      | ns   | 6.0                    |            |

|                                    |                                                           | 3                     | -6  | -   | 3   |       | 3     | -    | ns   | 2.0                    |            |

| t <sub>h</sub>                     | hold time Ds to                                           | 3                     | -2  | -   | 3   | -     | 3     | -    | ns   | 4.5                    | Fig.9      |

| n-                                 | SHCP                                                      | 3                     | -2  | -   | 3   | -     | 3     |      | ns   | 6.0                    |            |

|                                    |                                                           | 50                    | -19 | -   | 65  | -     | 75    | -    | ns   | 2.0                    |            |

| t <sub>rem</sub>                   | removal time MR                                           | 10                    | -7  | -   | 13  | -     | 15    | -    | ns   | 4.5                    | Fig.10     |

| 'rem                               | to SH <sub>CP</sub>                                       | 9                     | -6  | -   | 11  | ]-    | 13    |      | ns   | 6.0                    |            |

### 74HC/HCT595

| SYMBOL           |                                                         |          |           |         | T <sub>amb (°C</sub> | )      |          |        |            | TEST            | CONDITION    |  |

|------------------|---------------------------------------------------------|----------|-----------|---------|----------------------|--------|----------|--------|------------|-----------------|--------------|--|

|                  | PARAMETER                                               |          | +25       |         | -40 1                | to +85 | -40 to   | o +125 | UNIT       | V <sub>cc</sub> |              |  |

|                  |                                                         | MIN      | ТҮР       | MAX     | MIN                  | MAX    | MIN      | MAX    | 1          | (Ň)             | WAVEFORMS    |  |

| _                | maximum clock                                           | 6        | 30        | -       | 4.8                  | -      | 4        | -      | MHz        | 2.0             |              |  |

| f <sub>max</sub> | pulse frequency<br>SH <sub>CP</sub> or ST <sub>CP</sub> | 30<br>35 | 91<br>108 | -<br> - | 24<br>28             | -      | 20<br>24 | -      | MHz<br>MHz | 4.5<br>6.0      | Figs 7 and 8 |  |

#### DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see chapter "HCMOS family characteristics", section "Family specifications".

Output capability: parallel outputs, bus driver; serial output, standard  $I_{\rm cc}$  category: MSI.

#### Note to HCT types

The value of additional quiescent supply current  $(\Delta I_{cc})$  for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{cc}$  per input, multiply this value by the unit load coefficient shown in the table below.

#### $GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

| INPUT            | UNIT LOAD<br>COEFFICIENT |

|------------------|--------------------------|

| D <sub>s</sub>   | 0.25                     |

| MR               | 1.50                     |

| SH <sub>CP</sub> | 1.50                     |

| ST <sub>CP</sub> | 1.50                     |

| ŌĒ               | 1.50                     |

### 74HC/HCT595

#### AC CHARACTERISTICS FOR 74HCT

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF.$

|                                     |                                                                          |     |     |     | T <sub>amb (°C)</sub> |       |       |      |      | TEST CONDITION  |              |

|-------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|-----------------------|-------|-------|------|------|-----------------|--------------|

| SYMBOL                              | PARAMETER                                                                |     | +25 |     | -40 t                 | o +85 | 40 to | +125 | UNIT | V <sub>cc</sub> | WAVEFORMS    |

|                                     |                                                                          | MIN | ΤΥΡ | MAX | MIN                   | MAX   | MIN   | MAX  |      | (V)             |              |

| t <sub>PHL</sub> /t <sub>PLH</sub>  | propagation delay<br>SH <sub>CP</sub> to Q <sub>7</sub> '                | -   | 25  | 42  | -                     | 53    | -     | 63   | ns   | 4.5             | Fig.7        |

| t <sub>PHL</sub> /t <sub>PLH</sub>  | propagation delay<br>ST <sub>CP</sub> to Q <sub>n</sub>                  | 1   | 24  | 40  | -                     | 50    | -     | 60   | ns   | 4.5             | Fig.8        |

| t <sub>PHL</sub>                    | propagation delay<br>MR to Q <sub>7</sub> '                              | -   | 23  | 40  | -                     | 50    | -     | 60   | ns   | 4.5             | Fig.10       |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time $\overline{OE}$ to $Q_n$                      | -   | 21  | 35  | -                     | 44    | -     | 53   | ns   | 4.5             | Fig.11       |

| t <sub>PHZ</sub> /t <sub>PLZ</sub>  | 3-state output disable time $\overline{OE}$ to $Q_n$                     | -   | 18  | 30  | -                     | 38    | -     | 45   | ns   | 4.5             | Fig.11       |

| t <sub>w</sub>                      | shift clock pulse<br>width HIGH or LOW                                   | 16  | 6   | -   | 20                    | _     | 24    | -    | ns   | 4.5             | Fig.7        |

| t <sub>w</sub>                      | storage clock pulse<br>width HIGH or LOW                                 | 16  | 5   | -   | 20                    | -     | 24    |      | ns   | 4.5             | Fig.8        |

| t <sub>w</sub>                      | master reset pulse width LOW                                             | 20  | 8   | -   | 25                    | -     | 30    | -    | ns   | 4.5             | Fig.10       |

| t <sub>su</sub>                     | set-up time $D_s$ to $SH_{CP}$                                           | 16  | 5   |     | 20                    | -     | 24    | -    | ns   | 4.5             | Fig.9        |

| t <sub>su</sub>                     | set-up time SH <sub>CP</sub> to<br>ST <sub>CP</sub>                      | 16  | 8   | -   | 20                    | -     | 24    |      | ns   | 4.5             | Fig.8        |

| t <sub>h</sub>                      | hold time D <sub>s</sub> to SH <sub>CP</sub>                             | 3   | -2  | -   | 3                     | -     | 3     | -    | ns   | 4.5             | Fig.9        |

| t <sub>rem</sub>                    | removal time MR to<br>SH <sub>CP</sub>                                   | 10  | -7  | -   | 13                    | -     | 15    |      | ns   | 4.5             | Fig.10       |

| f <sub>max</sub>                    | maximum clock<br>pulse frequency<br>SH <sub>CP</sub> or ST <sub>CP</sub> | 30  | 52  |     | 24                    | -     | 20    | -    | MHz  | 4.5             | Figs 7 and 8 |

### Product specification

### 74HC/HCT595

#### AC WAVEFORMS

74HC/HCT595

## 8-bit serial-in/serial or parallel-out shift register with output latches; 3-state

#### Note to AC waveforms

(1) HC :  $V_M = 50\%$ ;  $V_I = GND$  to  $V_{CC}$ HCT:  $V_M = 1.3$  V;  $V_I = GND$  to 3 V.