**Product specification**

### Home automation modem

### **TDA5051A**

#### **FEATURES**

- · Full digital carrier generation and shaping

- Modulation/demodulation frequency set by clock adjustment, from microcontroller or on-chip oscillator

- High clock rate of 6-bit A/D (Digital to Analog) converter for rejection of aliasing components

- Fully integrated output power stage with overload protection

- Automatic Gain Control (AGC) at receiver input

- 8-bit A/D (Analog to Analog) converter and narrow digital filtering

- · Digital demodulation delivering baseband data

- Easy compliance with EN50065-1 with simple coupling network

- Few external components for low cost applications

- SO16 plastic package.

#### **APPLICATIONS**

- Home appliance control (air conditioning, shutters, lighting, alarms and so on)

- Energy/heating control

- Amplitude Shift Keying (ASK) data transmission using the home power network.

#### **GENERAL DESCRIPTION**

The TDA5051A is a modem IC, specifically dedicated to ASK transmission by means of the home power supply network, at 600 or 1200 baud data rate. It operates from a single 5 V supply.

#### QUICK REFERENCE DATA

| SYMBOL               | PARAMETER                                                          | CONDITIONS                  | MIN. | TYP.           | MAX.  | UNIT   |

|----------------------|--------------------------------------------------------------------|-----------------------------|------|----------------|-------|--------|

| V <sub>DD</sub>      | supply voltage                                                     |                             | 4.75 | 5.0            | 5.25  | V      |

| I <sub>DD(tot)</sub> | total supply current                                               | f <sub>osc</sub> = 8.48 MHz |      |                | - 47  |        |

|                      | reception mode                                                     |                             |      | 28             | 38    | mA     |

|                      | transmission mode ( $\overline{DATA}_{IN} = 0$ )                   | Z <sub>L</sub> = 30 Ω       | - F  | 47             | 68    | mA     |

|                      | power-down mode                                                    | 4Ft.1                       | - 1  | 19             | 25    | mA     |

| f <sub>cr</sub>      | carrier frequency                                                  | note 1                      | 95   | 132.5          | 148.5 | kHz    |

| f <sub>osc</sub>     | oscillator frequency                                               |                             | 6.08 | 8.48           | 9.504 | MHz    |

| V <sub>o(rms)</sub>  | output carrier signal on CISPR16 load (RMS value)                  | N.                          | 120  | _              | 122   | dBμV   |

| V <sub>i(rms)</sub>  | input signal (RMS value)                                           | note 2                      | 82   | _              | 122   | dΒμV   |

| THD                  | total harmonic distortion on CISPR16<br>load with coupling network |                             | _    | -55            | -     | dB     |

| $Z_L$                | load impedance                                                     |                             | 1    | 30             | -4 17 | Ω      |

| BR                   | baud rate                                                          |                             | ل سے | 600            | 1200  | bits/s |

| T <sub>amb</sub>     | ambient temperature                                                | 1 15-70 T                   | 0    | Total Williams | 70    | °C     |

#### Notes

- 1. Frequency range corresponding to the EN50065-1 band. However, the modem can operate at any lower oscillator frequency.

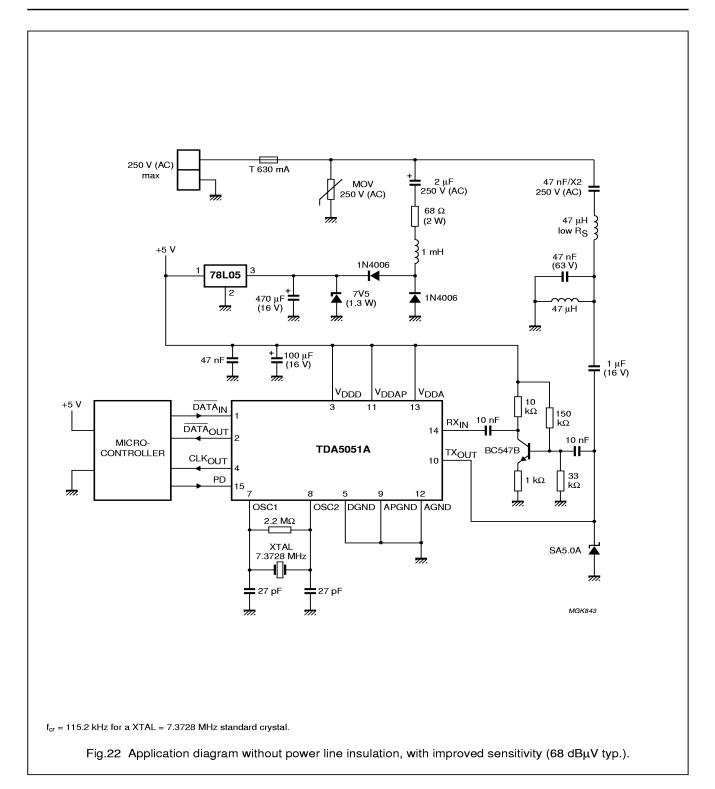

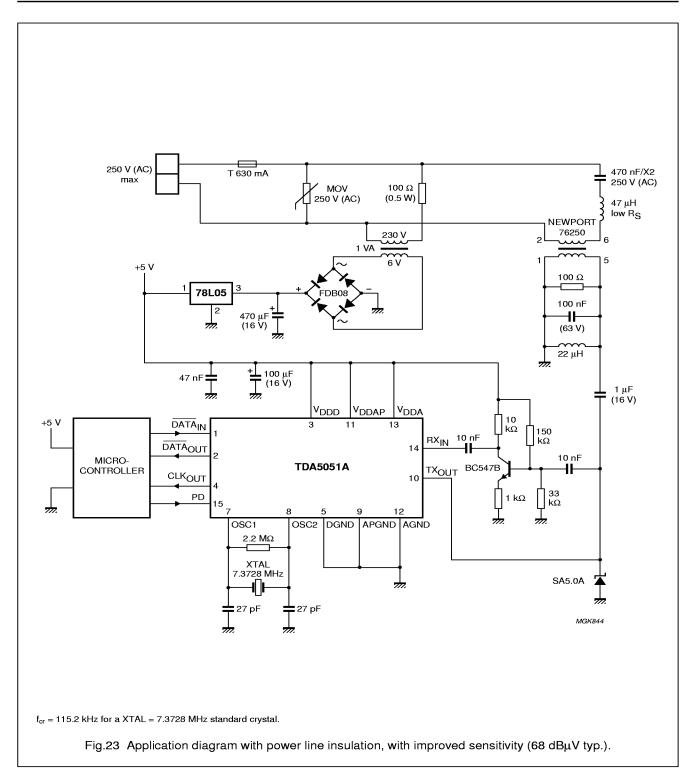

- 2. The minimum value can be improved by using an external amplifier, see application diagrams Figs 22 and 23.

## Home automation modem

TDA5051A

#### **ORDERING INFORMATION**

| TYPE PACKAGE |      | PACKAGE                                                    |          |

|--------------|------|------------------------------------------------------------|----------|

| NUMBER       | NAME | DESCRIPTION                                                | VERSION  |

| TDA5051AT    | SO16 | plastic small outline package; 16 leads; body width 7.5 mm | SOT162-1 |

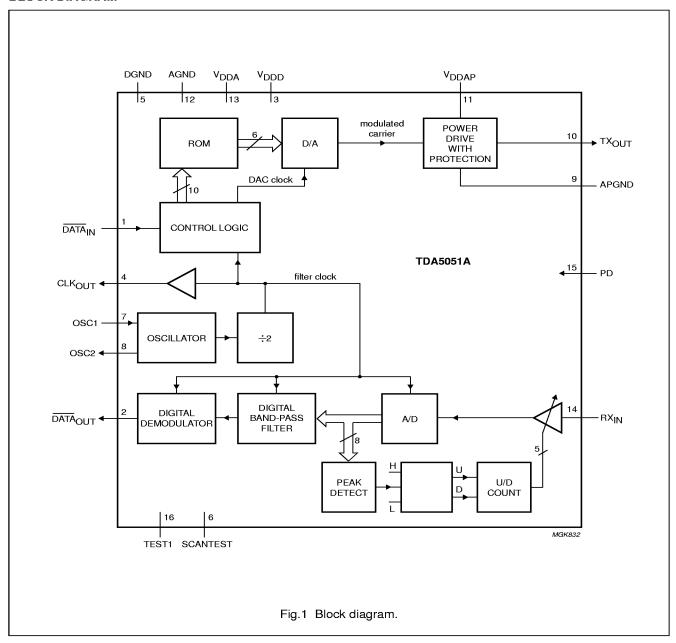

### **BLOCK DIAGRAM**

3

1999 May 31

### TDA5051A

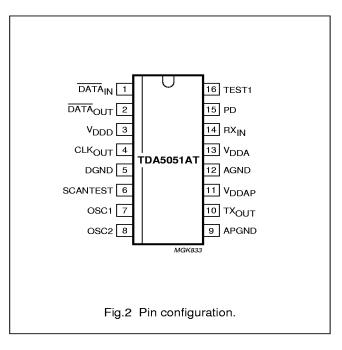

#### **PINNING**

| SYMBOL              | PIN | DESCRIPTION                               |  |

|---------------------|-----|-------------------------------------------|--|

| DATA <sub>IN</sub>  | 1   | digital data input (active LOW)           |  |

| DATA <sub>OUT</sub> | 2   | digital data output (active LOW)          |  |

| $V_{DDD}$           | 3   | digital supply voltage                    |  |

| CLK <sub>OUT</sub>  | 4   | clock output                              |  |

| DGND                | 5   | digital ground                            |  |

| SCANTEST            | 6   | test input (LOW in application)           |  |

| OSC1                | 7   | oscillator input                          |  |

| OSC2                | 8   | oscillator output                         |  |

| APGND               | 9   | analog ground for power amplifier         |  |

| TX <sub>OUT</sub>   | 10  | analog signal output                      |  |

| $V_{DDAP}$          | 11  | analog supply voltage for power amplifier |  |

| AGND                | 12  | analog ground                             |  |

| $V_{DDA}$           | 13  | analog supply voltage                     |  |

| RX <sub>IN</sub>    | 14  | analog signal input                       |  |

| PD                  | 15  | power-down input (active HIGH)            |  |

| TEST1 16            |     | test input (HIGH in application)          |  |

#### **FUNCTIONAL DESCRIPTION**

Both transmission and reception stages are controlled either by the master clock of the microcontroller or by the on-chip reference oscillator connected to a crystal. This ensures the accuracy of the transmission carrier and the exact trimming of the digital filter, thus making the performance totally independent of application disturbances such as component spread, temperature, supply drift and so on.

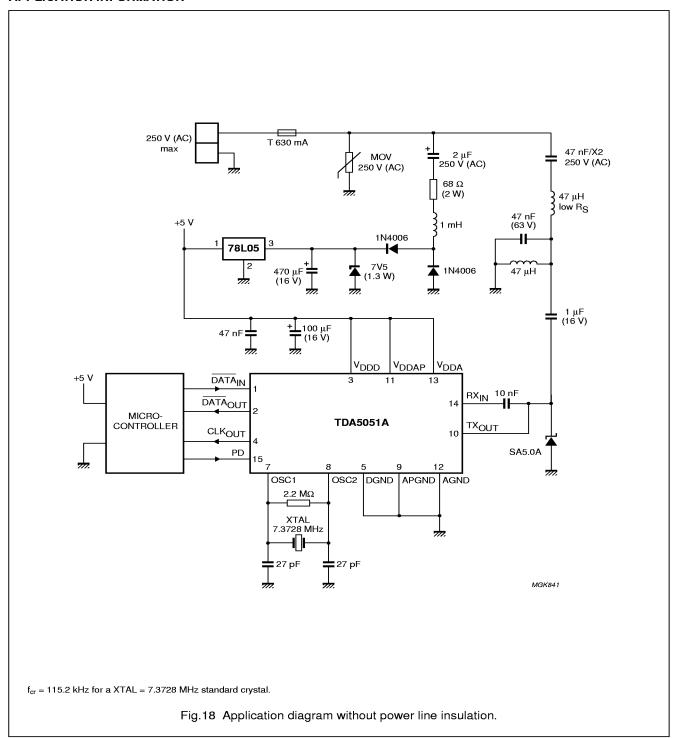

The interface with the power network is made by means of an LC network (see Fig.18). The device includes a power output stage that feeds a 120 dB $\mu$ V (RMS) signal on a typical 30  $\Omega$  load.

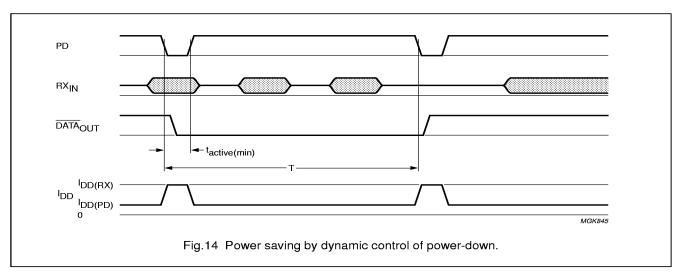

To reduce power consumption, the IC is disabled by a power-down input (pin PD): in this mode, the on-chip oscillator remains active and the clock continues to be supplied at pin CLK<sub>OUT</sub>. For low-power operation in reception mode, this pin can be dynamically controlled by the microcontroller, see Section "Power-down mode".

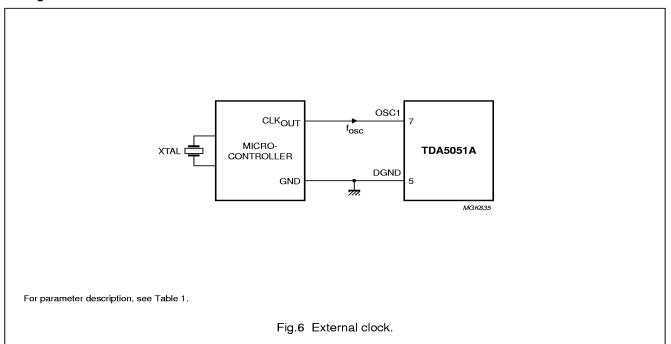

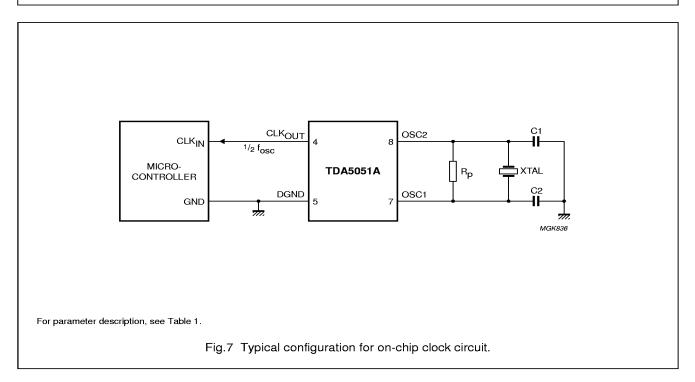

When the circuit is connected to an external clock generator (see Fig.6), the clock signal must be applied at pin OSC1 (pin 7); OSC2 (pin 8) must be left open-circuit. Fig.7 shows the use of the on-chip clock circuit.

All logic inputs and outputs are compatible with TTL/CMOS levels, providing an easy connection to a standard microcontroller I/O port.

The digital part of the IC is fully scan-testable. Two digital inputs, SCANTEST and TEST1, are used for production test: these pins must be left open-circuit in functional mode (correct levels are internally defined by pull-up or pull-down resistors).

#### **Transmission mode**

To provide strict stability with respect to environmental conditions, the carrier frequency is generated by scanning the ROM memory under the control of the microcontroller clock or the reference frequency provided by the on-chip oscillator. High frequency clocking rejects the aliasing components to such an extent that they are filtered by the coupling LC network and do not cause any significant disturbance. The data modulation is applied through pin  $\overline{DATA}_{IN}$  and smoothly applied by specific digital circuits to the carrier (shaping). Harmonic components are limited in this process, thus avoiding unacceptable disturbance of the transmission channel (according to CISPR16 and EN50065-1 recommendations). A –55 dB Total Harmonic Distortion (TDH) is reached when the typical LC coupling network (or an equivalent filter) is used.

TDA5051A

The DAC and the power stage are set in order to provide a maximum signal level of 122 dBμV (RMS) at the output.

The output of the power stage ( $TX_{OUT}$ ) must **always** be connected to a decoupling capacitor, because of a DC level of  $0.5V_{DD}$  at this pin, which is present even when the device is not transmitting. This pin must also be **protected against overvoltage and negative transient signals**. The DC level of  $TX_{OUT}$  can be used to bias a unipolar transient suppressor, as shown in the application diagram; see Fig.18.

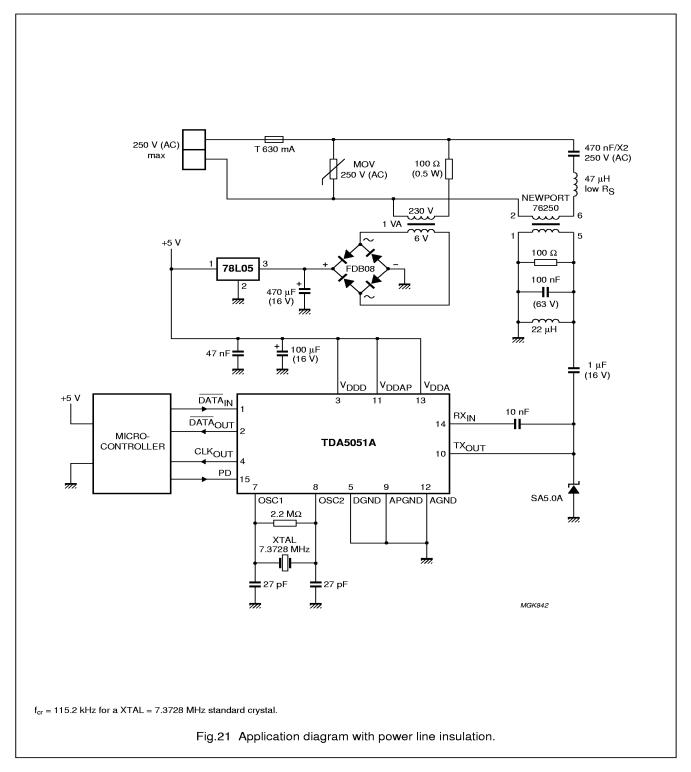

Direct connection to the mains is done through an LC network for low-cost applications. However, a HF signal transformer could be used when power-line insulation has to be performed.

#### CAUTION

In transmission mode, the receiving part of the circuit is **not disabled** and the detection of the transmitted signal is normally performed. In this mode, the gain chosen before the beginning of the transmission is stored, and the **AGC** is internally set to –6 dB as long as  $\overline{DATA}_{IN}$  is LOW. Then, the old gain setting is automatically restored.

### Reception mode

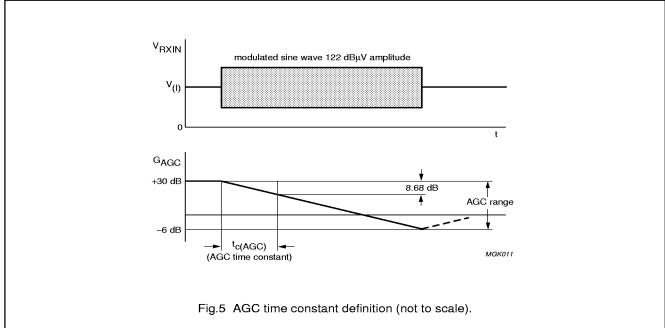

The input signal received by the modem is applied to a wide range input amplifier with AGC (–6 to +30 dB). This is basically for noise performance improvement and signal level adjustment, which ensures a maximum sensitivity of the ADC. An 8-bit conversion is then performed, followed by digital band-pass filtering, to meet the CISPR normalization and to comply with some additional limitations met in current applications.

After digital demodulation, the baseband data signal is made available after pulse shaping.

The signal pin (RX<sub>IN</sub>) is a high-impedance input which has to be protected and DC decoupled for the same reasons as with pin TX<sub>OUT</sub>. The high sensitivity (82 dB $\mu$ V) of this input requires an efficient 50 Hz rejection filter (realized by the LC coupling network), which also acts as an anti-aliasing filter for the internal digital processing; see Fig.18.

#### **Data format**

TRANSMISSION MODE

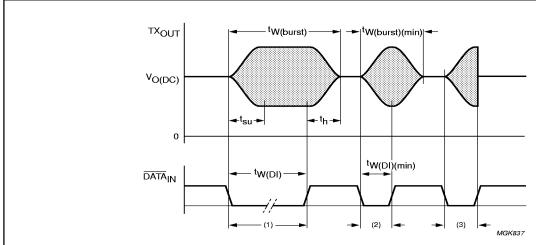

The data input  $(\overline{DATA}_{IN})$  is active LOW: this means that a burst is generated on the line (pin  $TX_{OUT}$ ) when  $\overline{DATA}_{IN}$  pin is LOW.

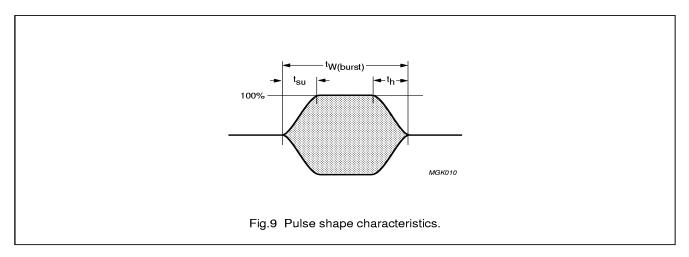

Pin  $TX_{OUT}$  is in a high-impedance state as long as the device is not transmitting. Successive logic 1s are treated in a Non-Return-to-Zero (NRZ) mode, see pulse shapes in Figs 8 and 9.

#### RECEPTION MODE

The data output (pin DATA<sub>OUT</sub>) is active LOW; this means that the data output is LOW when a burst is received. Pin DATA<sub>OUT</sub> remains LOW as long as a burst is received.

#### Power-down mode

Power-down input (pin PD) is active HIGH; this means that the power consumption is minimum when pin PD is HIGH. Now, all functions are disabled, except clock generation.

#### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER            | MIN. | MAX. | UNIT |

|------------------|----------------------|------|------|------|

| $V_{DD}$         | supply voltage       | 4.5  | 5.5  | V    |

| f <sub>osc</sub> | oscillator frequency | _    | 12   | MHz  |

| T <sub>stg</sub> | storage temperature  | -50  | +150 | °C   |

| T <sub>amb</sub> | ambient temperature  | -10  | +80  | °C   |

| T <sub>i</sub>   | junction temperature | _    | 125  | °C   |

### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

# Home automation modem

TDA5051A

### CHARACTERISTICS

$V_{DDD} = V_{DDA} = 5~V~\pm 5\%;~T_{amb} = 0~to~70~^{\circ}C;~V_{DDD}~connected~to~V_{DDA};~DGND~connected~to~AGND.$

| SYMBOL                                                            | PARAMETER                                                                                                     | CONDITIONS                                                                                                                                                              | MIN.               | TYP.         | MAX.                     | UNIT    |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--------------------------|---------|

| Supply                                                            |                                                                                                               |                                                                                                                                                                         | •                  |              |                          | •       |

| $V_{DD}$                                                          | supply voltage                                                                                                |                                                                                                                                                                         | 4.75               | 5            | 5.25                     | V       |

| I <sub>DD(RX/TX)(tot)</sub>                                       | total analog + digital supply current                                                                         | $V_{DD}$ = 5 V ±5%<br>TX or RX mode                                                                                                                                     | _                  | 28           | 38                       | mA      |

| I <sub>DD(PD)(tot)</sub>                                          | total analog + digital supply current;                                                                        | $V_{DD}$ = 5 V ±5%;<br>PD = HIGH<br>Power-down mode                                                                                                                     | -                  | 19           | 25                       | mA      |

| I <sub>DD(PAMP)</sub>                                             | power amplifier supply current                                                                                | $\begin{array}{c} V_{DD} = 5 \text{ V } \pm 5\%; \\ Z_L = 30  \Omega; \\ \overline{\text{DATA}}_{IN} = \text{LOW} \\ \text{in transmission mode} \end{array}$           | -                  | 19           | 30                       | mA      |

| I <sub>DD(PAMP)(max)</sub>                                        | maximum power amplifier supply current                                                                        | $\begin{aligned} &V_{DD} = 5 \text{ V } \pm 5\%; \\ &Z_L = 1 \Omega; \\ &\overline{\text{DATA}}_{\text{IN}} = \text{LOW} \\ &\text{in transmission mode} \end{aligned}$ | _                  | 76           | _                        | mA      |

| DATA <sub>IN</sub> and F                                          | PD inputs: $\overline{	extsf{DATA}}_{	extsf{OUT}}$ and CL                                                     | K <sub>OUT</sub> outputs                                                                                                                                                |                    |              |                          |         |

| V <sub>IH</sub>                                                   | HIGH-level input voltage                                                                                      |                                                                                                                                                                         | $0.2V_{DD} + 0.9$  | _            | V <sub>DD</sub> + 0.5    | ٧       |

| V <sub>IL</sub>                                                   | LOW-level input voltage                                                                                       |                                                                                                                                                                         | -0.5               | _            | $0.2V_{DD} - 0.1$        | ٧       |

| V <sub>OH</sub>                                                   | HIGH-level output voltage                                                                                     | I <sub>OH</sub> = -1.6 mA                                                                                                                                               | 2.4                | _            | _                        | ٧       |

| $V_{OL}$                                                          | LOW-level output voltage                                                                                      | I <sub>OL</sub> = 1.6 mA                                                                                                                                                | _                  | _            | 0.45                     | ٧       |

|                                                                   | and OSC2 output (OSC2 onl<br>an external clock generator)                                                     |                                                                                                                                                                         | nal quartz crys    | stal; mus    | t be left open-          | circuit |

| V <sub>IH</sub>                                                   | HIGH-level input voltage                                                                                      |                                                                                                                                                                         | 0.7V <sub>DD</sub> | _            | V <sub>DD</sub> + 0.5    | V       |

| V <sub>IL</sub>                                                   | LOW-level input voltage                                                                                       |                                                                                                                                                                         | -0.5               | _            | 0.2V <sub>DD</sub> - 0.1 | V       |

| V <sub>OH</sub>                                                   | HIGH-level output voltage                                                                                     | I <sub>OH</sub> = -1.6 mA                                                                                                                                               | 2.4                | _            | -                        | V       |

| V <sub>OL</sub>                                                   | LOW-level output voltage                                                                                      | I <sub>OL</sub> = 1.6 mA                                                                                                                                                | _                  | _            | 0.45                     | V       |

| Clock                                                             | , -                                                                                                           |                                                                                                                                                                         | •                  |              | •                        |         |

| f <sub>osc</sub>                                                  | oscillator frequency                                                                                          |                                                                                                                                                                         | 6.080              | _            | 9.504                    | MHz     |

| $\frac{f_{osc}}{f_{cr}}$                                          | ratio between oscillator and carrier frequency                                                                |                                                                                                                                                                         | -                  | 64           | -                        |         |

| f <sub>osc</sub>                                                  | ratio between oscillator and clock output frequency                                                           |                                                                                                                                                                         | -                  | 2            | _                        |         |

| Transmission                                                      | n mode                                                                                                        |                                                                                                                                                                         |                    |              |                          |         |

| f <sub>cr</sub>                                                   | carrier frequency                                                                                             | f <sub>osc</sub> = 8.48 MHz                                                                                                                                             | _                  | 132.5        | -                        | kHz     |

| t <sub>su</sub>                                                   | set-up time of the shaped<br>burst                                                                            | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.8                                                                                                                               | _                  | 170          | _                        | μs      |

| t <sub>h</sub>                                                    | hold time of the shaped burst                                                                                 | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.8                                                                                                                               | _                  | 170          | _                        | μs      |

| f <sub>CLKOUT</sub> Transmission  f <sub>cr</sub> t <sub>su</sub> | and clock output frequency  mode  carrier frequency  set-up time of the shaped burst  hold time of the shaped | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.8<br>f <sub>osc</sub> = 8.48 MHz;                                                                                               |                    | 132.5<br>170 |                          | μs      |

# Home automation modem

# TDA5051A

| SYMBOL                  | PARAMETER                                                                                                             | CONDITIONS                                                                                                                                              | MIN. | TYP. | MAX. | UNIT                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------------------|

| t <sub>W(DI)(min)</sub> | minimum pulse width of DATA <sub>IN</sub> signal                                                                      | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.8                                                                                                               | _    | 190  | _    | μs                   |

| V <sub>o(rms)</sub>     | output carrier signal (RMS value)                                                                                     | $\frac{Z_{L} = CISPR16;}{DATA_{IN} = LOW}$                                                                                                              | 120  | _    | 122  | dBμV                 |

| I <sub>o(max)</sub>     | power amplifier maximum output current (peak value)                                                                   | $\frac{Z_{L} = 1}{DATA_{IN}} \Omega;$                                                                                                                   | _    | 160  | -    | mA                   |

| Z <sub>o</sub>          | output impedance of the power amplifier                                                                               |                                                                                                                                                         | _    | 5    | -    | Ω                    |

| Vo                      | output DC level at pin TX <sub>OUT</sub>                                                                              |                                                                                                                                                         | _    | 2.5  | -    | V                    |

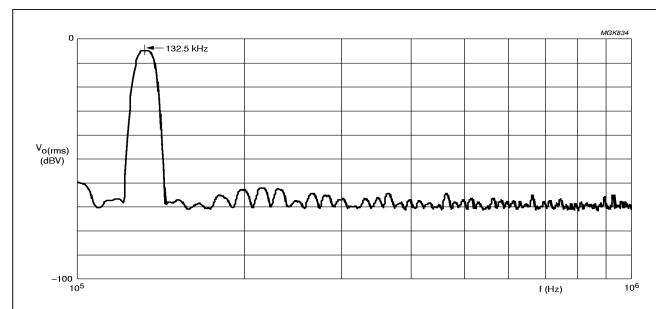

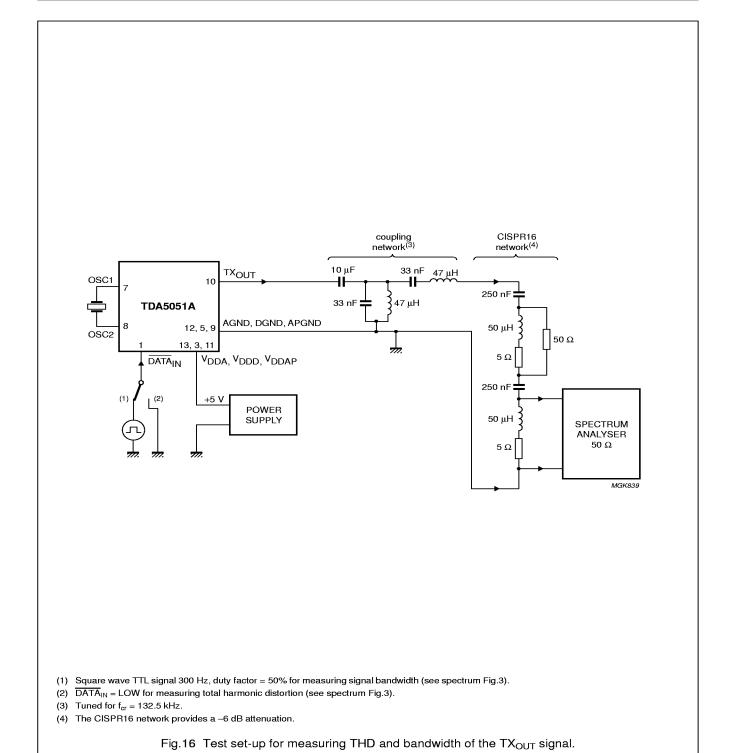

| THD                     | total harmonic distortion on<br>CISPR16 load with the<br>coupling network<br>(measured on the first ten<br>harmonics) | V <sub>o(rms)</sub> = 121 dBμV on<br>CISPR16 load;<br>f <sub>osc</sub> = 8.48 MHz;<br>DATA <sub>IN</sub> = LOW<br>(no modulation);<br>see Figs 3 and 16 | _    | -55  | -    | dB                   |

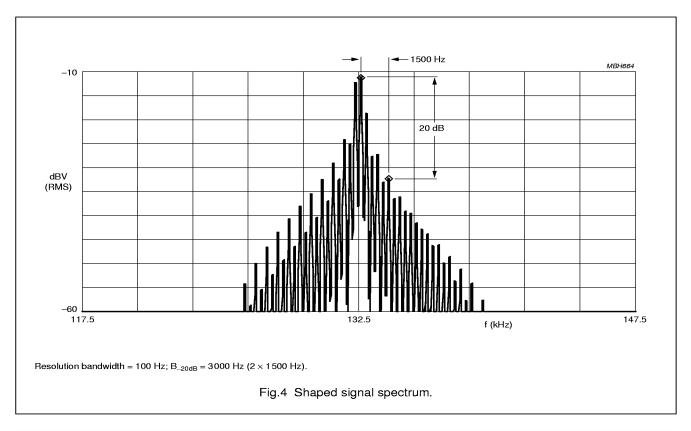

| B <sub>-20dB</sub>      | bandwidth of the shaped<br>output signal (at -20 dB)<br>on CISPR16 load with the<br>coupling network                  | $V_{o(rms)}$ = 121 dBμV on CISPR16 load; $f_{osc}$ = 8.48 MHz; $\overline{DATA}_{IN}$ = 300 Hz; duty factor = 50%; see Fig.4                            | _    | 3000 | -    | Hz                   |

| Reception r             | mode                                                                                                                  |                                                                                                                                                         | •    |      |      | _                    |

| V <sub>i(rms)</sub>     | analog input signal<br>(RMS value)                                                                                    |                                                                                                                                                         | 82   | -    | 122  | dBμV                 |

| V <sub>I</sub>          | DC level at pin RX <sub>IN</sub>                                                                                      |                                                                                                                                                         | _    | 2.5  | _    | V                    |

| Zi                      | RX <sub>IN</sub> input impedance                                                                                      |                                                                                                                                                         | _    | 50   | _    | kΩ                   |

| R <sub>AGC</sub>        | AGC range                                                                                                             |                                                                                                                                                         | _    | 36   | _    | dB                   |

| t <sub>c(AGC)</sub>     | AGC time constant                                                                                                     | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.5                                                                                                               | _    | 296  | _    | μs                   |

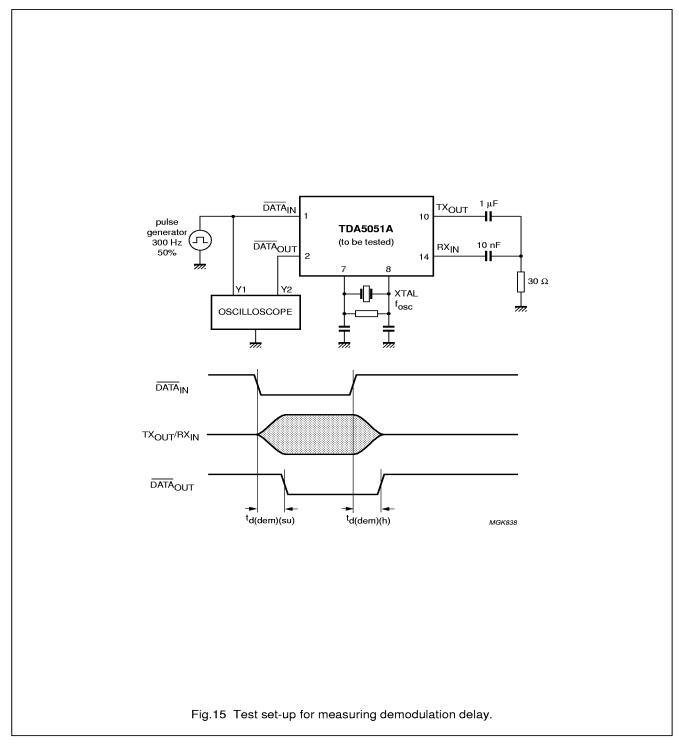

| t <sub>d(dem)(su)</sub> | demodulation delay set-up time                                                                                        | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.15                                                                                                              | _    | 350  | 400  | μs                   |

| t <sub>d(dem)(h)</sub>  | demodulation delay hold time                                                                                          | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.15                                                                                                              | _    | 420  | 470  | μs                   |

| B <sub>det</sub>        | detection bandwidth                                                                                                   | f <sub>osc</sub> = 8.48 MHz                                                                                                                             | _    | 3    | _    | kHz                  |

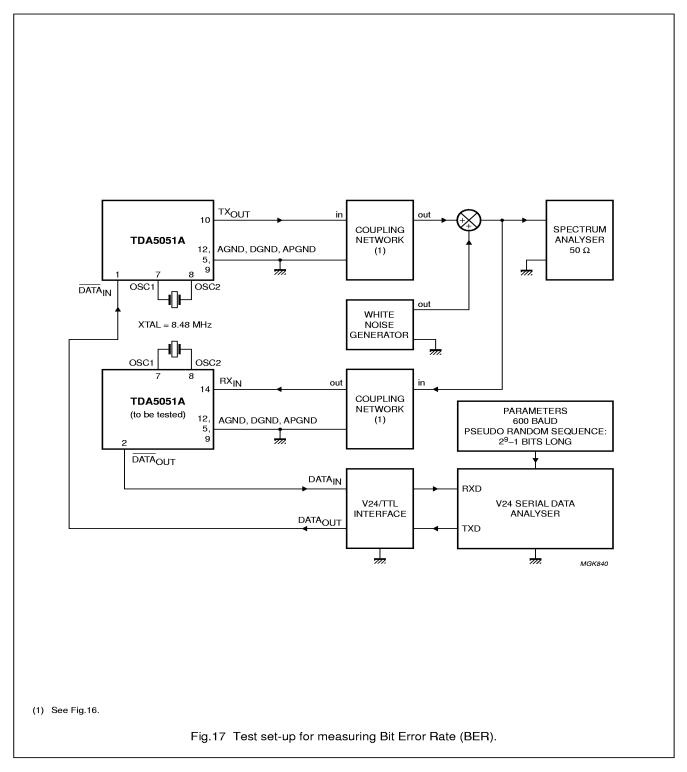

| BER                     | bit error rate                                                                                                        | f <sub>osc</sub> = 8.48 MHz;<br>600 baud; S/N = 35 dB;<br>signal 76 dBμV;<br>see Fig.17                                                                 | _    | 1    | _    | 1 × 10 <sup>-4</sup> |

## Home automation modem

## TDA5051A

| SYMBOL                   | PARAMETER                                                              | CONDITIONS                                                                                                                                   | MIN. | TYP. | MAX. | UNIT |

|--------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Power-up tin             | ning                                                                   |                                                                                                                                              |      |      |      |      |

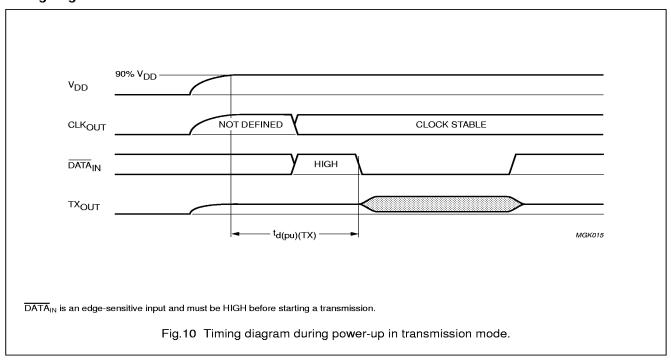

| t <sub>d(pu)(TX)</sub>   | delay between power-up and DATA <sub>IN</sub> in transmission mode     | XTAL = 8.48 MHz;<br>C1 = C2 = 27 pF;<br>$R_p$ = 2.2 MΩ; see Fig.10                                                                           | _    | 1    | _    | μs   |

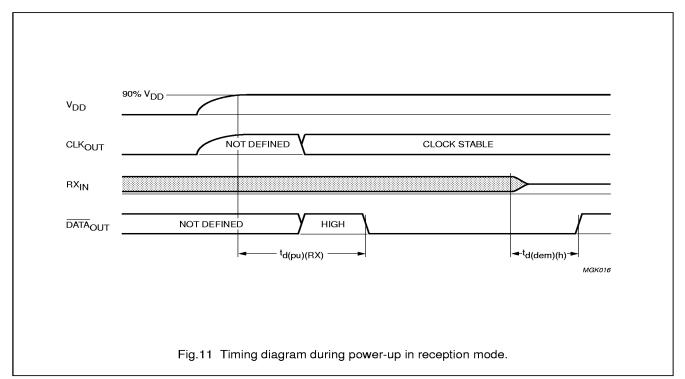

| t <sub>d(pu)(RX)</sub>   | delay between power-up and DATA <sub>OUT</sub> in reception mode       | $XTAL = 8.48 \text{ MHz};$ $C1 = C2 = 27 \text{ pF};$ $R_p = 2.2 \text{ M}Ω;$ $f_{RXIN} = 132.5 \text{ kHz};$ 120 dBμV sine wave; see Fig.11 | _    | 1    | _    | μs   |

| Power-down               | timing                                                                 |                                                                                                                                              |      |      |      |      |

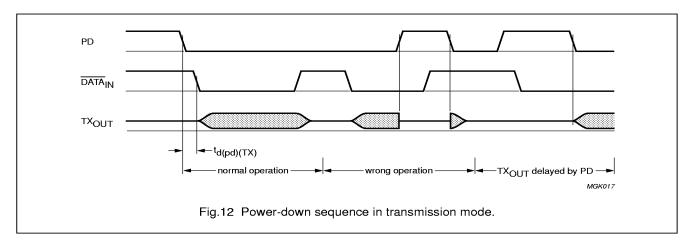

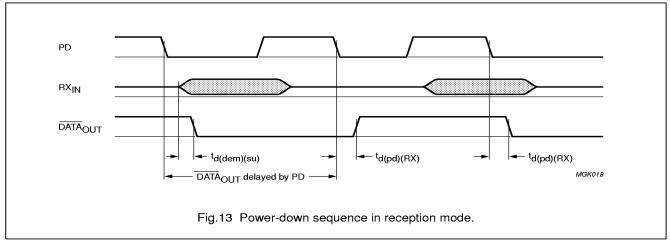

| t <sub>d(pd)(TX)</sub>   | delay between PD = 0 and DATA <sub>IN</sub> in transmission mode       | f <sub>osc</sub> = 8.48 MHz;<br>see Fig.12                                                                                                   | _    | 10   | _    | μs   |

| t <sub>d(pd)(RX)</sub>   | delay between PD = 0 and DATA <sub>OUT</sub> in reception mode         | $f_{osc}$ = 8.48 MHz;<br>$f_{RXIN}$ = 132.5 kHz;<br>120 dB $\mu$ V sine wave;<br>see Fig.13                                                  | -    | 500  | _    | μs   |

| t <sub>active(min)</sub> | minimum active time with T = 10 ms power-down period in reception mode | f <sub>osc</sub> = 8.48 MHz;<br>f <sub>RXIN</sub> = 132.5 kHz;<br>120 dBμV sine wave;<br>see Fig.14                                          | _    | 1    | _    | μѕ   |

Resolution bandwidth = 9 kHz; top: 0 dBV (RMS) = 120 dB $\mu$ V (RMS); marker at –5 dBV (RMS) = 115 dB $\mu$ V (RMS); the CISPR16 network provides an attenuation of 6 dB, so the signal amplitude is 121 dB $\mu$ V (RMS).

Fig.3 Carrier spectrum.

## Home automation modem

# TDA5051A

9

1999 May 31

## Home automation modem

## TDA5051A

### **TIMING**

### **Configuration for clock**

# Home automation modem

TDA5051A

Table 1 Clock oscillator parameters

| OSCILLATOR<br>FREQUENCY<br>f <sub>osc</sub> | CARRIER FREQUENCY | CLOCK OUTPUT<br>FREQUENCY<br>1/2fosc | EXTERNAL COMPONENTS                                                                         |

|---------------------------------------------|-------------------|--------------------------------------|---------------------------------------------------------------------------------------------|

| 6.080 to 9.504 MHz                          | 95 to 148.5 kHz   | 3.040 to 4.752 MHz                   | C1 = C2 = 27 to 47 pF;<br>$R_p$ = 2.2 to 4.7 M $\Omega$ ;<br>XTAL = standard quartz crystal |

Table 2 Calculation of parameters depending on the clock frequency

| SYMBOL                     | PARAMETER                                         | CONDITIONS                                                                                                             | UNIT |

|----------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|

| f <sub>osc</sub>           | oscillator frequency                              | with on-chip oscillator: frequency of the crystal quartz; with external clock: frequency of the signal applied at OSC1 | Hz   |

| fclkout                    | clock output frequency                            | ½fosc                                                                                                                  | Hz   |

| f <sub>cr</sub>            | carrier frequency/digital filter tuning frequency | 1/ <sub>64</sub> f <sub>osc</sub>                                                                                      | Hz   |

| t <sub>su</sub>            | set-up time of the shaped burst                   | $\frac{23}{f_{cr}}$ or $\frac{1472}{f_{osc}}$                                                                          | s    |

| t <sub>h</sub>             | hold time of the shaped burst                     | $\frac{23}{f_{cr}}$ or $\frac{1472}{f_{osc}}$                                                                          | S    |

| t <sub>W(DI)(min)</sub>    | minimum pulse width of DATA <sub>IN</sub> signal  | $t_{su} + \frac{1}{f_{cr}}$                                                                                            | s    |

| t <sub>W(burst)(min)</sub> | minimum burst time of V <sub>O(DC)</sub> signal   | t <sub>W(DI)(min)</sub> + t <sub>h</sub>                                                                               | s    |

| t <sub>c(AGC)</sub>        | AGC time constant                                 | 2514<br>f <sub>osc</sub>                                                                                               | s    |

| t <sub>su(demod)</sub>     | demodulation set-up time                          | 3200 <sub>fosc</sub> (≈max.)                                                                                           | s    |

| t <sub>h(demod)</sub>      | demodulation hold time                            | 3800 <sub>fosc</sub> (≈max.)                                                                                           | s    |

TDA5051A

- (1)  $t_{W(DI)} > t_{W(DI)(min)}$ .

- (2)  $t_{W(DI)(min)} = t_{su} + \frac{1}{f_{cr}}$

- (3)  $t_{W(DI)(min)} < t_{su}$ ; wrong operation.

Fig.8 Relationship between  $\overline{DATA}_{IN}$  and  $TX_{OUT}$  (see Table 3).

**Table 3** Relationship between  $\overline{DATA}_{IN}$  and  $TX_{OUT}$

| PD | DATA <sub>IN</sub> | TX <sub>OUT</sub>                      |

|----|--------------------|----------------------------------------|

| 1  | X <sup>(1)</sup>   | high-impedance                         |

| 0  | 1                  | high-impedance (after t <sub>h</sub> ) |

| 0  | 0                  | active with DC offset                  |

### Note

1. X = don't care.

## Home automation modem

### TDA5051A

### Timing diagrams

## Home automation modem

# TDA5051A

## Home automation modem

# TDA5051A

#### **TEST INFORMATION**

## TDA5051A

## TDA5051A

## Home automation modem

### TDA5051A

#### **APPLICATION INFORMATION**

## TDA5051A

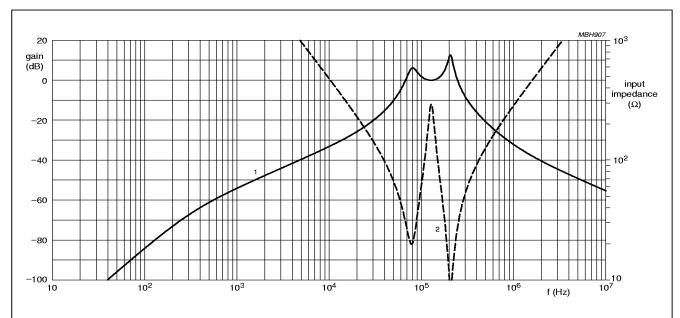

Main features of the coupling network: 50 Hz rejection >80 dB; anti-aliasing for the digital filter >50 dB at the sampling frequency ( $^{1}_{2}f_{oso}$ ). Input impedance always higher than 10  $\Omega$  within the 95 to 148.5 kHz band.

Fig.19 Gain (curve 1) and input impedance (curve 2) of the coupling network ( $f_{cr}$  = 115.2 kHz; L = 47  $\mu$ H; C = 47 nF).

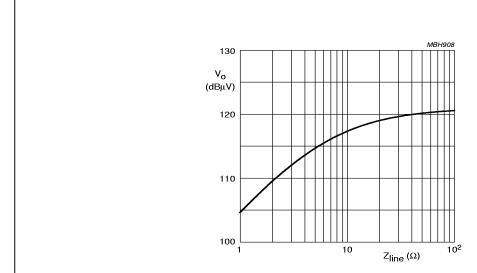

Fig.20 Output voltage as a function of line impedance (with coupling network;  $L = 47 \mu H$ ; C = 47 nF).

## TDA5051A

## TDA5051A

## TDA5051A

TDA5051A

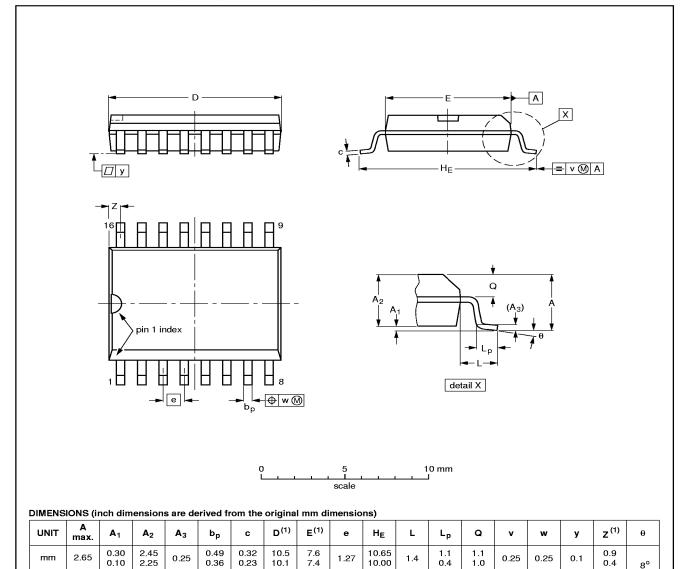

#### **PACKAGE OUTLINE**

SO16: plastic small outline package; 16 leads; body width 7.5 mm

SOT162-1

#### Note

inches

0.012

0.004

0.10

0.096

0.089

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

0.01

0.019

0.014

0.013

0.009

0.40

| OUTLINE  |        | REFER    | ENCES | EUROPEAN   | ISSUE DATE                      |

|----------|--------|----------|-------|------------|---------------------------------|

| VERSION  | IEC    | JEDEC    | EIAJ  | PROJECTION | ISSUE DATE                      |

| SOT162-1 | 075E03 | MS-013AA |       |            | <del>95-01-24</del><br>97-05-22 |

0.050

0.30

0.419 0.394 0.043 0.016

0.055

0.043 0.039

0.01

0.01

0.004

0.035 0.016

TDA5051A

#### **SOLDERING**

#### Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering is not always suitable for surface mount ICs, or for printed-circuit boards with high population densities. In these situations reflow soldering is often used.

#### Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, infrared/convection heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 230 °C.

#### Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is **preferred** to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis

must be parallel to the transport direction of the

printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

### Home automation modem

TDA5051A

#### Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE                         | SOLDERING METHOD                  |                       |  |  |

|---------------------------------|-----------------------------------|-----------------------|--|--|

| PACKAGE                         | WAVE                              | REFLOW <sup>(1)</sup> |  |  |

| BGA, SQFP                       | not suitable                      | suitable              |  |  |

| HLQFP, HSQFP, HSOP, HTSSOP, SMS | not suitable <sup>(2)</sup>       | suitable              |  |  |

| PLCC <sup>(3)</sup> , SO, SOJ   | suitable                          | suitable              |  |  |

| LQFP, QFP, TQFP                 | not recommended <sup>(3)(4)</sup> | suitable              |  |  |

| SSOP, TSSOP, VSO                | not recommended <sup>(5)</sup>    | suitable              |  |  |

#### **Notes**

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

- 2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

- 3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

#### **DEFINITIONS**

| Data sheet status                                                                                              |                                                                                       |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Objective specification                                                                                        | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification                                                                                      | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification                                                                                          | This data sheet contains final product specifications.                                |

| Limiting values                                                                                                |                                                                                       |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or |                                                                                       |

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.