# TRANSWITCH

QE1M Device Quad E1 Mapper TXC-04252

DATA SHEET

#### **FEATURES I**

- Add/drop four 2.048 Mbit/s signals from STM-1/VC-4, STS-3/AU-3 or STS-1 buses

- Independent add and drop bus timing modes

- Selectable HDB3 positive/negative rail or NRZ E1 interface. Performance counter provided for coding violations.

- Digital desynchronizer

- Drop buses are monitored for parity, loss of clock, upstream AIS and H4 multiframe errors

- Performance counters are provided for TU/VT pointer movements, BIP-2 errors and Far End Block Errors (FEBEs)

- TU/VTs are monitored for Loss Of Pointer, New Data Flags (NDFs), AIS, Remote Defect Indication (RDI), and size errors (S-bits)

- V5 Byte Signal Label Mismatch and Unequipped detection

- E1 facility and line loopbacks, generation of BIP-2 and FEBE errors, and send RDI capability

- Intel / Motorola / Multiplexed-compatible microprocessor bus interface with interrupt capability

- Programmable internal RISC processor implements VT-POH and VT-alarm handling

- J2 16-byte ETSI trail trace comparison

- Optional V4 receive and transmit byte access

- TU tandem connection processing (N2 byte)

- IEEE 1149.1 standard boundary scan

- Single +5 V ± 5 % power supply

- 160-lead plastic quad flat package or 208-lead PBGA (17 mm x 17 mm)

#### **DESCRIPTION**

The Quad E1 Mapper device is designed for add/drop multiplexer, terminal multiplexer, and dual and single unidirectional ring applications. Four E1 2.048 Mbit/s signals are mapped to and from asynchronous Tributary Unit-12 (TU-12) or Virtual Tributary 2 (VT2) formats. The QE1M a multiple-segment, interfaces to byte-parallel SDH/SONET-formatted bus at the 19.44 Mbit/s byte rate for STM-1/STS-3 operation or at the 6.48 Mbit/s byte rate for STS-1 operation. The E1 2.048 Mbit/s signals can be either HDB3 positive/negative rail- or NRZ-formatted signals. The QE1M provides performance counters, alarm detection, and the ability to generate errors and Alarm Indication Signals (AIS). E1 facility and line loopback capabilities are also provided.

The QE1M bus interface is used to connect to other TranSwitch devices such as the STM-1/STS-3/STS-3c Overhead Terminator (SOT-3), TXC-03003 or TXC-03003B, to form an STM-1/STS-3 add/drop or terminal system.

#### **APPLICATIONS**

- STM-1/STS-3/STS-1 to 2.048 Mbit/s add/drop mux/demux

- Unidirectional or bidirectional ring applications

- STM-1/STS-3/STS-1 termination terminal mode multiplexer

- STM-1/STS-3/STS-1 test equipment

3 Enterprise Drive

U.S. Patents No. 4,967,405; 5,033,064; 5,040,170; 5,265,096; 5,289,057;

5,297,180; 5,473,611; 5,528,598; 5,535,218; U.S. and/or foreign patents issued or pending

Copyright © 2000 TranSwitch Corporation

TranSwitch and TXC are registered trademarks of TranSwitch Corporation

TranSwitch Corporation

Document Number: TXC-04252-MB Ed. 3, December 2000

USA

#### **TABLE OF CONTENTS**

| Section                                                | Page |

|--------------------------------------------------------|------|

| List of Figures                                        | 3    |

| Block Diagram                                          | 4    |

| Block Diagram Description                              | 5    |

| Lead Diagrams                                          | 9    |

| Lead Descriptions                                      | 11   |

| Absolute Maximum Ratings and Environmental Limitations | 21   |

| Thermal Characteristics                                | 21   |

| Power Requirements                                     | 21   |

| Input, Output and Input/Output Parameters              | 22   |

| Timing Characteristics                                 | 25   |

| Operation                                              | 43   |

| Bus Interface Modes                                    | 43   |

| Bus Mode Selection                                     | 44   |

| SDH/SONET Add/Drop Multiplexing Format Selections      |      |

| Drop TU/VT Selection                                   | 45   |

| Add TU/VT Selection                                    | 46   |

| Bus Timing                                             |      |

| Unequipped Operation                                   | 47   |

| Drop Bus Multiframe Alignment                          | 49   |

| Add Bus Multiframe Alignment                           |      |

| Performance Counters                                   | 51   |

| Alarm Structure                                        |      |

| Interrupt Structure                                    | 52   |

| SDH/SONET AIS Detection                                | 58   |

| TU/VT Pointer Tracking                                 | 59   |

| Remote Defect Indications                              |      |

| Overhead Communications Bit Access                     | 64   |

| BIP-2, AIS Indication, TC REI and TC OEI Processing    |      |

| TUG-3 Null Pointer Indicator                           |      |

| E1 Loopback Capability                                 |      |

| PRBS Pattern Generator and Analyzer                    | 72   |

| Resets                                                 |      |

| Start-Up Procedure                                     |      |

| Pointer Leak Rate Calculations                         |      |

| Jitter Measurements                                    |      |

| Internal Spot Processor                                |      |

| Boundary Scan                                          |      |

| Multiplex Format and Mapping Information               |      |

| Memory Map                                             |      |

| Memory Map Descriptions                                |      |

| Package Information                                    |      |

| Ordering Information                                   | 140  |

### TRANSWITCH:

#### **DATA SHEET**

| Documentation Update Registration Form * | 147 |

|------------------------------------------|-----|

| List of Data Sheet Changes               | 143 |

| Standards Documentation Sources          | 141 |

| Related Products                         | 140 |

#### LIST OF FIGURES

| Figu | ire                                                                       | Page |

|------|---------------------------------------------------------------------------|------|

| 1.   | QE1M TXC-04252 Block Diagram                                              | 4    |

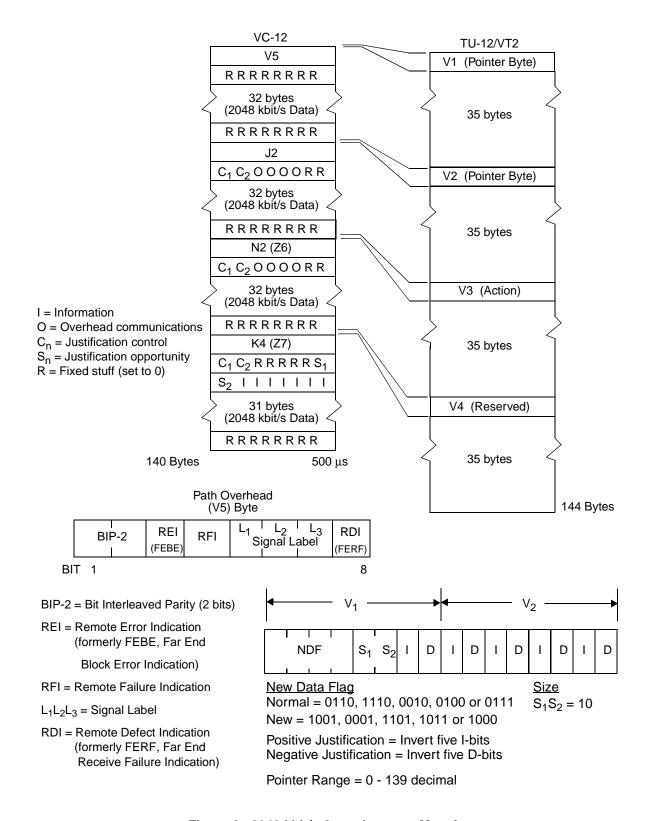

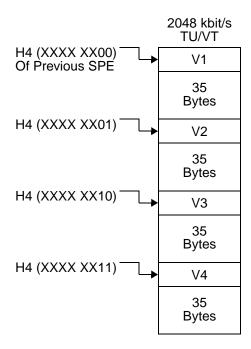

| 2.   | 2048 kbit/s Asynchronous Mapping                                          | 8    |

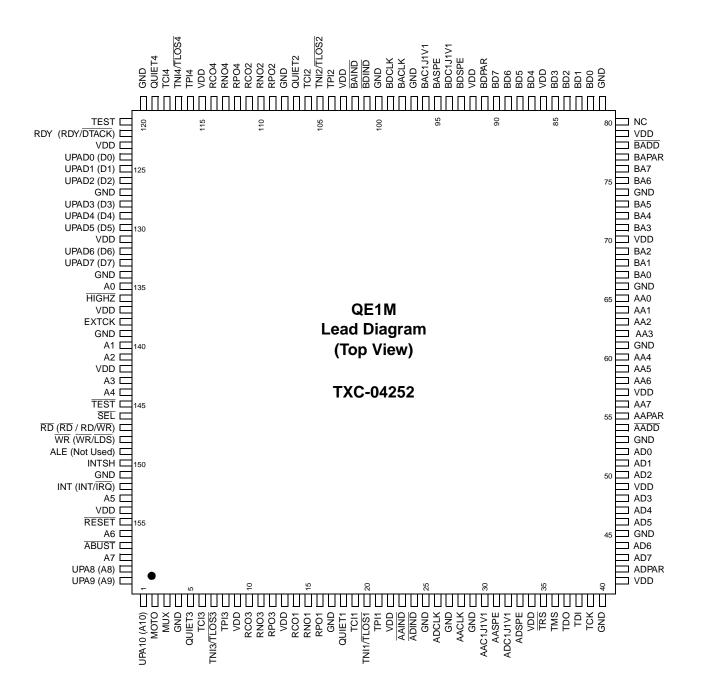

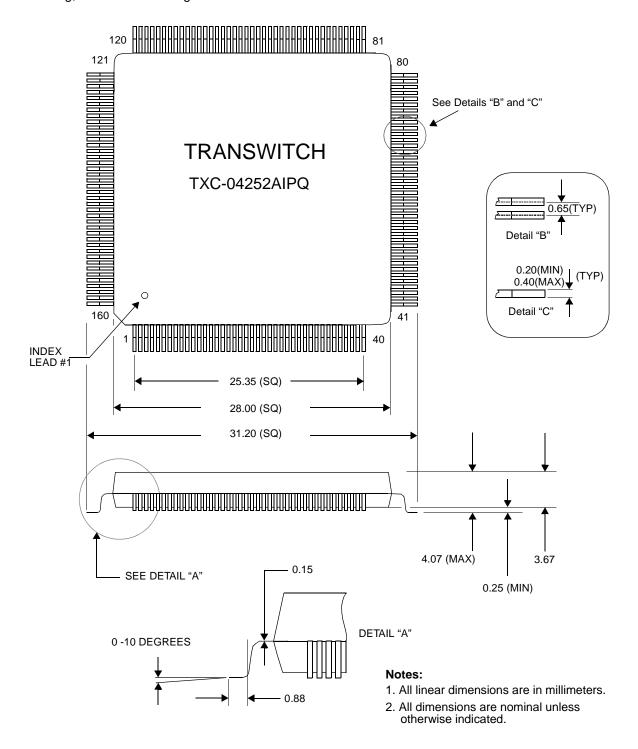

| 3.   | QE1M TXC-04252 Plastic Quad Flat Package Lead Diagram                     | 9    |

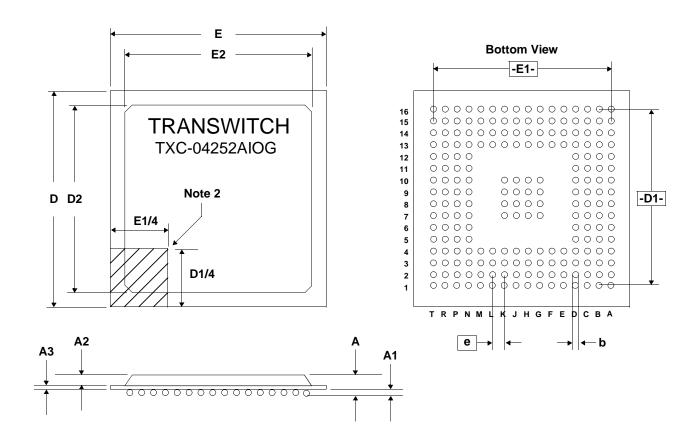

| 4.   | QE1M TXC-04252 Plastic Ball Grid Array Package Lead Diagram               | 10   |

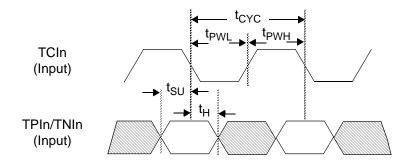

| 5.   | Ports 1, 2, 3 and 4 E1 Transmit Timing                                    | 25   |

| 6.   | Ports 1, 2, 3 and 4 E1 Receive Timing                                     | 26   |

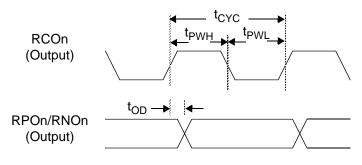

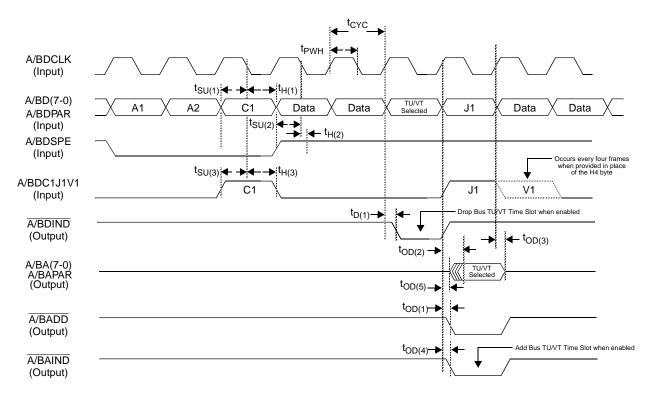

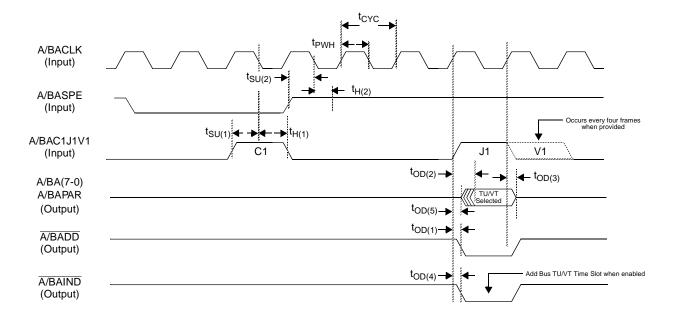

| 7.   | STS-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus          | 27   |

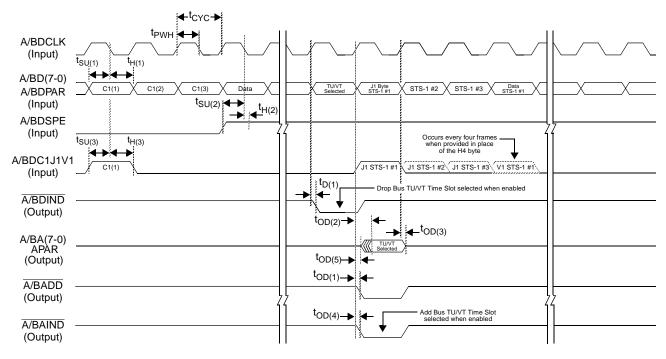

| 8.   | STM-1/STS-3 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus    | 28   |

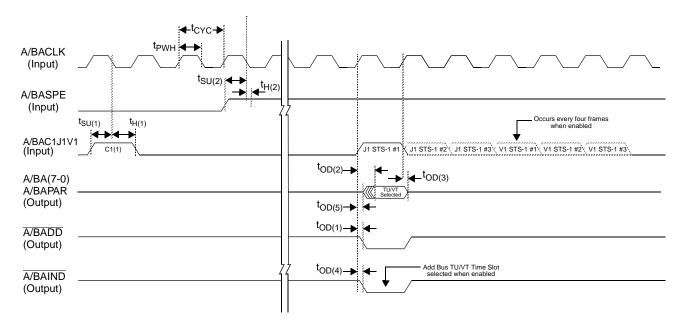

| 9.   | STS-1 A/B Add Bus Signals, Timing Derived from Add Bus                    | 29   |

| 10.  | STM-1/STS-3 A/B Add Bus Signals, Timing Derived from Add Bus              | 30   |

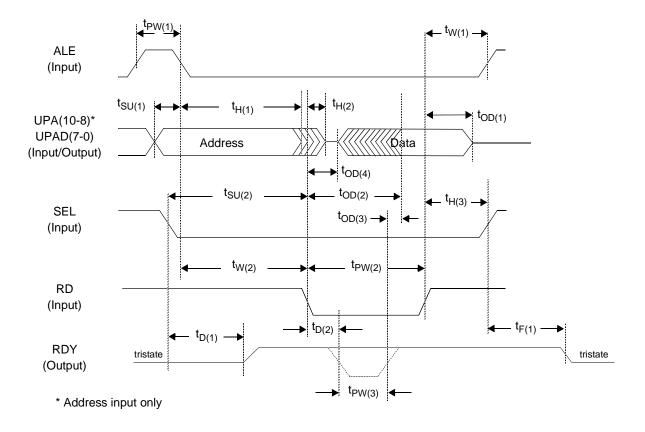

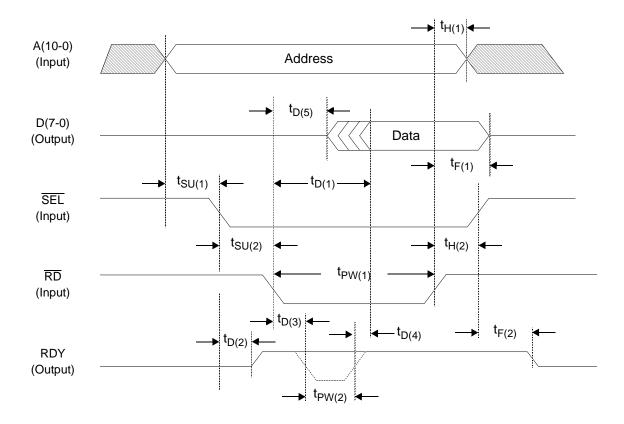

| 11.  | Microprocessor Read Cycle Timing - Multiplex Bus                          | 31   |

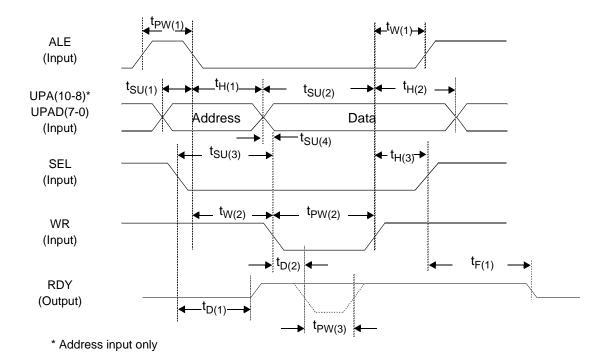

| 12.  | Microprocessor Write Cycle Timing - Multiplex Bus                         | 33   |

| 13.  | Microprocessor Read Cycle Timing - Intel                                  | 35   |

| 14.  | Microprocessor Write Cycle Timing - Intel                                 | 37   |

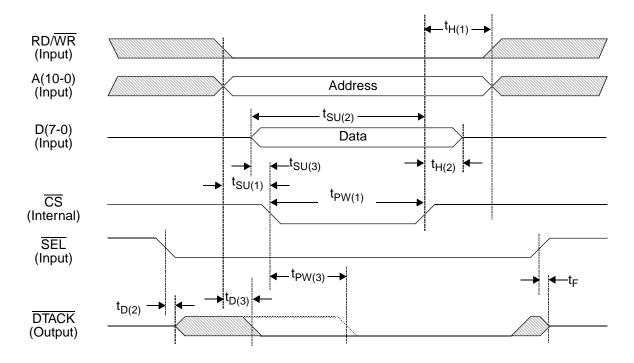

| 15.  | Microprocessor Read Cycle Timing - Motorola                               | 38   |

| 16.  | Microprocessor Write Cycle Timing - Motorola                              | 40   |

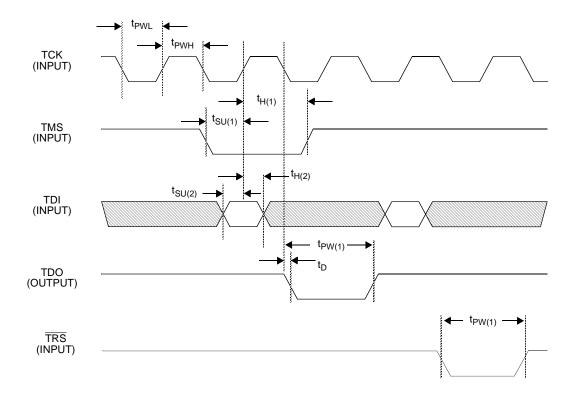

| 17.  | Boundary Scan Timing                                                      | 42   |

| 18.  | H4 Byte Floating VT Mode Bit Allocation                                   | 49   |

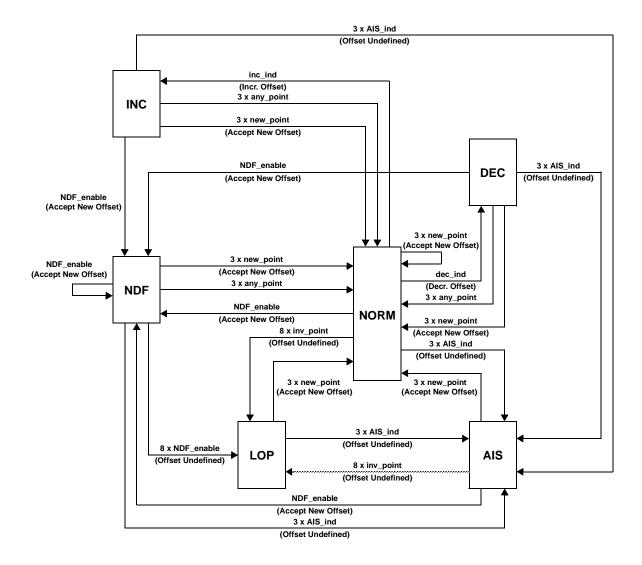

| 19.  | TU/VT Pointer Tracking State Machine                                      | 60   |

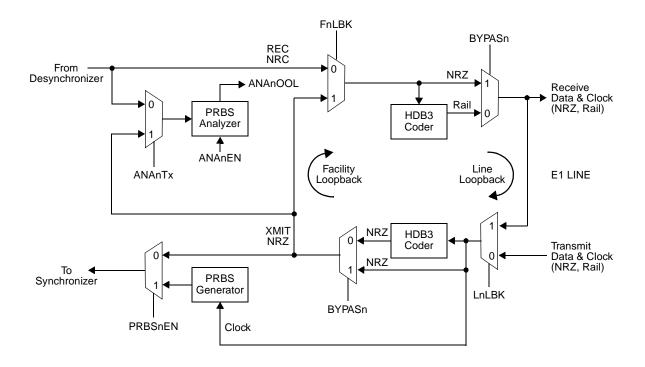

| 20.  | Facility and Line Loopbacks                                               | 71   |

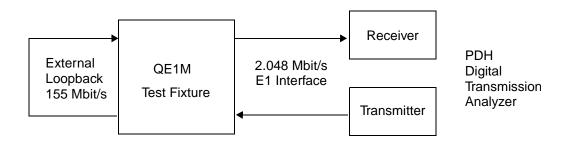

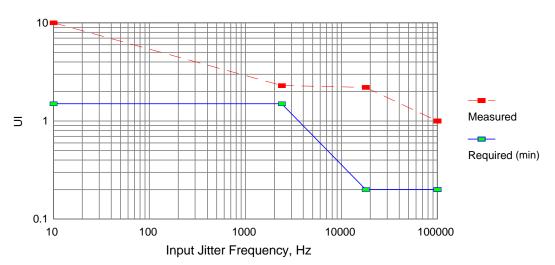

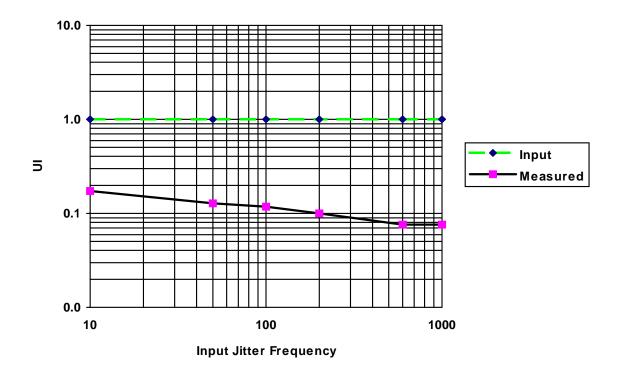

| 21.  | Jitter Tolerance and Jitter Test Arrangements                             | 76   |

| 22.  | Jitter Tolerance Measurements                                             | 76   |

| 23.  | Jitter Transfer Measurements                                              | 77   |

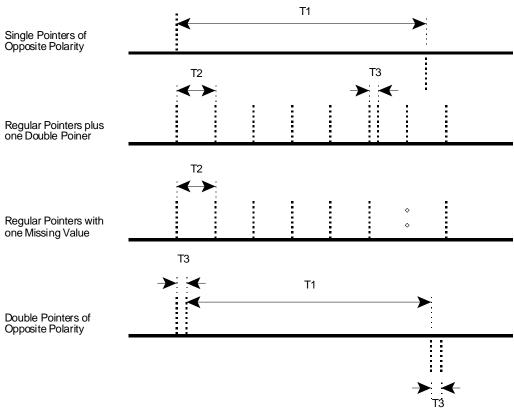

| 24.  | Standard Pointer Test Sequences                                           | 79   |

| 25.  | Schematic Diagram of QE1M Showing SPOT Processor Interfaces               | 82   |

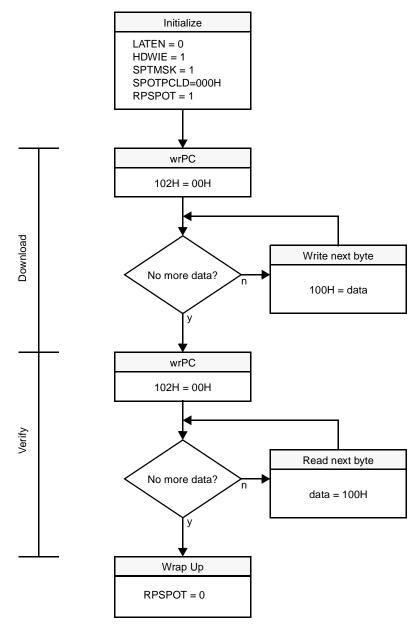

| 26.  | Recommended Implementation Flowchart for Reprogramming the SPOT Processor | 83   |

| 27.  | Boundary Scan Schematic                                                   | 85   |

| 28.  | QE1M TXC-04252 160-Lead Plastic Quad Flat Package                         | 138  |

| 29.  | QE1M TXC-04252 208-Lead Plastic Ball Grid Array Package                   | 139  |

|      |                                                                           |      |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

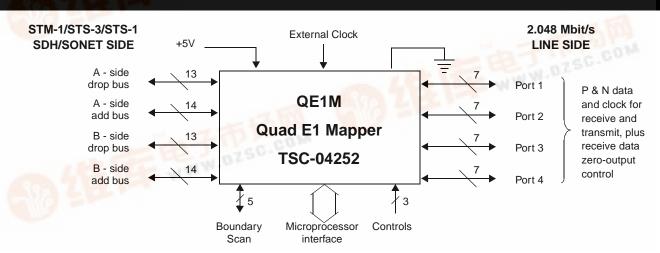

#### **BLOCK DIAGRAM**

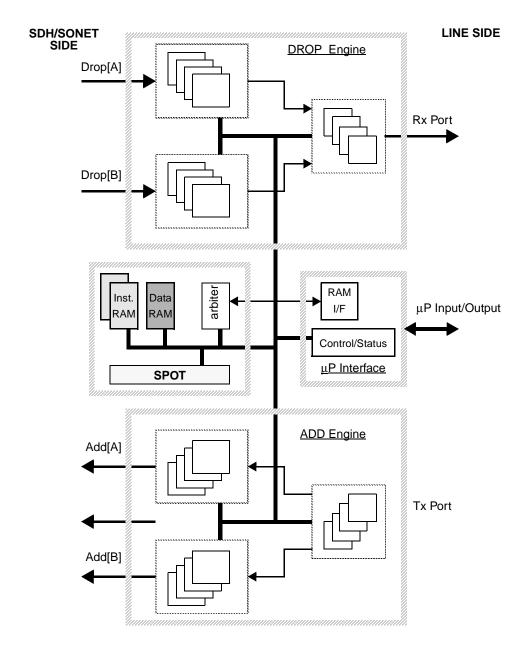

Figure 1. QE1M TXC-04252 Block Diagram

QE1M TXC-04252

#### **BLOCK DIAGRAM DESCRIPTION**

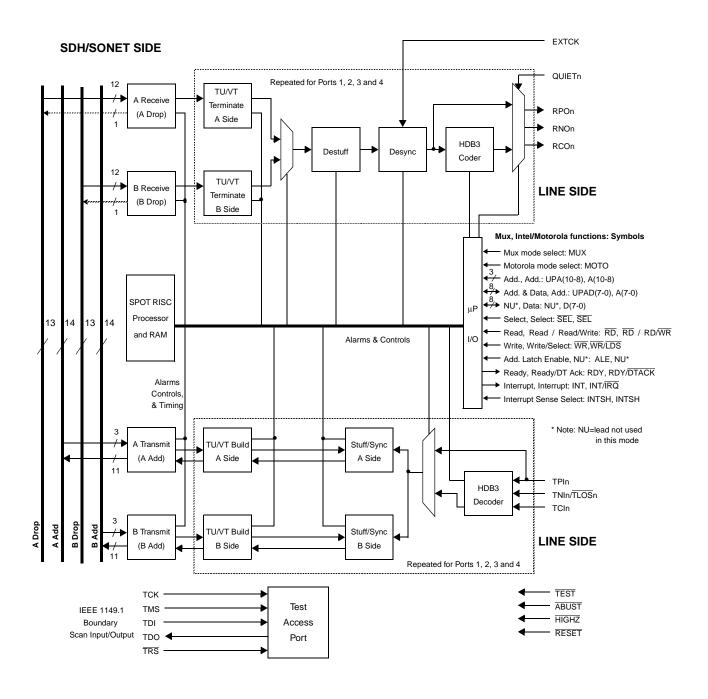

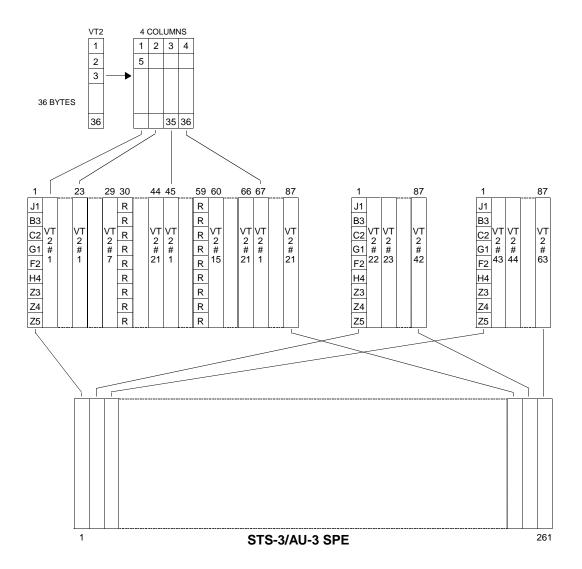

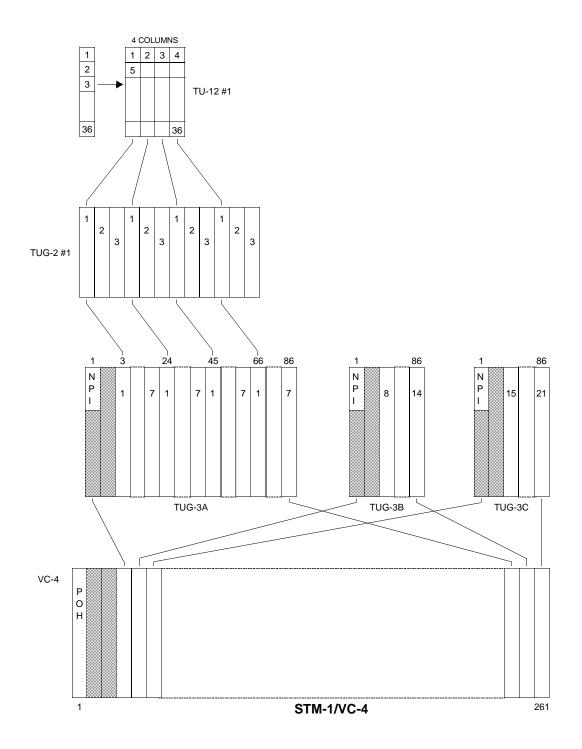

The block diagram for the Quad E1 Mapper is shown in 1. The Quad E1 Mapper interfaces to four buses, designated as A Drop, B Drop, A Add, and B Add. The four buses run at the STM-1/STS-3 rate of 19.44 Mbyte/s, or at the STS-1 rate of 6.48 Mbyte/s. For North American applications, the asynchronous E1 signals are carried in floating Virtual Tributary 2 (VT2) format in a Synchronous Transport Signal - 1 (STS-1), or in an STS-1 that is carried in a Synchronous Transport Signal - 3 (STS-3). For ITU-T applications, the E1 signals are carried in floating mode Tributary Unit - 12 (TU-12) format in the STM-1 Virtual Container - 4 structure (VC-4) using Tributary Unit Group - 3 (TUG-3), or in the STM-1 Virtual Container - 3 structure (VC-3) using Tributary Unit Group -2 (TUG-2) mapping schemes. Four E1 signals can be dropped from one bus (A Drop or B Drop), or from both of the drop buses, to the E1 lines. Four asynchronous E1 signals are converted into TU-12 or VT2 format and are added to either of the add buses, or both, depending upon the mode of operation. When the Quad E1 Mapper is configured for drop bus timing, the add buses are, by definition, byte- and multiframe-synchronous with their like-named drop buses, but are delayed by one byte time because of internal processing. For example, if a byte in the STM-1 Virtual Container - 4 structure (VC-4) using Tributary Unit Group - 3 (TUG-3), TU-12/VT2 is to be added to the A Add bus, the time of its placement on the bus is derived from the A Drop bus timing, and from software instructions specifying which TU/VT number is being dropped/added. When the device is configured for add bus timing, the add bus, parity, and add indicator signals are derived from the add clock, C1J1V1 and SPE signals.

The A Receive block is identical to the B Receive block. The TU/VT Terminate block is repeated 8 times, two for each port (A and B sides). The Destuff, Desync, and HDB3 Coder blocks are repeated four times, one for each port. The interface between a drop bus and Receive block consists of 12 input leads, and an optional output lead: a byte clock, byte-wide data, a C1J1 indicator which may be carrying a V1 indication making the signal a C1J1V1 indicator, an SPE indicator, and an odd parity bit for the last-named three signals. Parity is selectable by control bits for even parity and for the data byte only. The output lead is an optional TU/VT select indicator signal. The Drop C1J1V1 signal is used in conjunction with the Drop SPE signal to determine the location of the various pulses. The C1 pulse identifies the location of the C1 byte when the SPE signal is low. A single J1 pulse identifies the starting location of the J1 byte in the VC-4 format, when the SPE signal is high. Three J1 pulses are provided for the STS-3 format, each identifying the starting location of the J1 byte in each of the STS-1 signals.

The Quad E1 Mapper can operate with a V1 pulse in the C1J1V1 signal, or it can use an internal H4 detector for determining the location of the V1 pulse. The V1 pulse location is used to determine the location of the pointer byte V1. For STM-1 VC-4 operation, if the C1J1V1 signal is used, a single V1 pulse must occur three drop bus clock cycles every four frames following the J1 pulse when the SPE signal is high. For STS-3 operation, three V1 pulses must be present every four frames. Each of the three V1 pulses must be present three clock cycles after the corresponding J1 pulse, when the SPE signal is high. For example, in a VC-4 signal, the J1 pulse identifies the J1 byte location (defined as the starting location for the VC-4) in the POH bytes. In the next column (first clock cycle) all the rows are assigned as fixed stuff. Similarly, in the next column (second clock cycle) all the rows are assigned as fixed stuff. The next column (third clock cycle) defines the start of TUG-3 A. This column is where the V1 pulse occurs every four frames. However, the actual V1 byte location is six clock cycles after the V1 pulse.

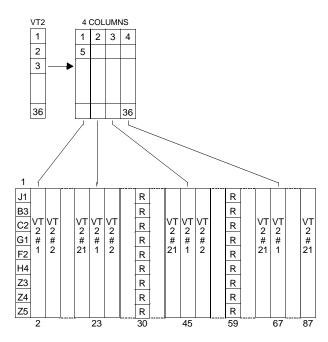

For STS-1 operation, one V1 pulse must be present if the C1J1V1 signal is used. The V1 pulse must occur on the next clock cycle after the J1 pulse, and when the SPE signal is high. The J1 pulse identifies the J1 byte location (defined as the starting location for the STS-1) in the POH bytes. In the next column (first clock cycle) the TUs start. Thus, the V1 pulse identifies the starting location of the first V1 byte in the signal. The rest of the V1 bytes for the 21 TU-12/VT2s are also aligned with respect to the V1 pulse (please see the first diagram in the Operation - Multiplex Format and Mapping Information section).

Each bus is monitored for parity errors, loss of clock, H4 multiframe alignment if selected, and an upstream SDH/SONET AIS indication. The Quad E1 Mapper can monitor either the TOH E1 bytes or the H1/H2 bytes for an AIS indication. Which E1 byte and H1/H2 bytes are selected is a function of the TU/VT selected.

TVO 04050 NI

#### **DATA SHEET**

Each TU/VT Terminate block (A and B side) performs pointer processing based on the location of the V1 and V2 bytes. The pointer bytes are monitored for loss of pointer, TU AIS indication, and NDF. The pointer tracking process is based on the latest ETSI standard, which also meets ANSI/Bellcore requirements. Pointer increments and decrements are also counted, and the SS-bits are monitored for the correct value. This block also monitors the various alarms found in the V5 and K4 (formerly known as Z7) bytes, including signal label mismatch detection, unequipped status detection, BIP-2 parity error detection and error counter, FEBE counter, and the three RDI indications. The Quad E1 Mapper performs a 16-byte J2 trail trace comparison on the channels selected. For 64-byte messages, the bytes are stored in a memory map segment for a microprocessor read cycle. The device also provides the TU tandem connection feature and performs the 16-byte message comparison for the N2 (formerly known as Z6) byte message.

A control bit for each port selects the TU/VT from either the A Drop or B Drop bus. The TU/VT is destuffed in the Destuff block using majority logic rules for the three sets of three justification control bits to determine if the two S-bits are data bits or frequency justification bits.

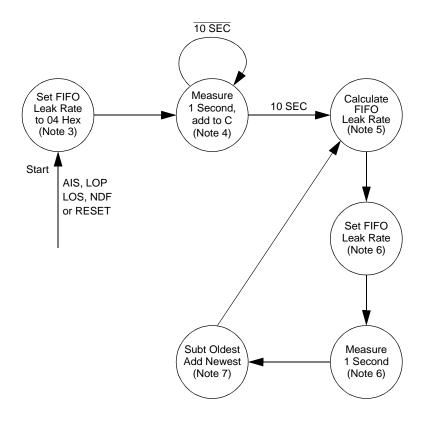

The Desync block removes the effects on the E1 output of systemic jitter that might occur because of signal mappings and pointer movements in the network. The Desync block contains two parts, a pointer leak buffer, and a E1 loop buffer. The pointer leak buffer can accept up to five consecutive pointer movements, and can adjust the effect over time. The E1 Loop Buffer consists of a digital loop filter, which is designed to track the frequency of the received E1 signal and to remove both transmission and stuffing jitter.

An option for each port provides either NRZ data, or an HDB3-encoded positive and negative rail signal for the E1 interface. Receive data (towards the E1 line), for all four channels, can be clocked out on either rising or falling edges of the clock. In addition, control bits are provided for forcing the data and clock signals to a high impedance state (tristate). A control lead is provided for forcing the output leads to the 0 state.

In the add direction, the Quad E1 Mapper accepts clock and either NRZ data or HDB3-encoded positive and negative rail signals. Data, for all four channels, can be clocked in on either the falling or rising edge of the clock. In the NRZ mode, an external loss of clock indication input signal can be provided. For the rail signal, coding violations are counted, and there is monitoring for loss of signal. An E1AIS detector is also provided.

The data signal is written into a FIFO in one of the eight Stuff/Sync blocks. Threshold modulation is used for the frequency justification process. Timing information from the drop bus or add bus is used to read the FIFO and perform the TU/VT justification process. This block permits tracking of an incoming E1 signal having an average frequency offset as high as 120 ppm, and up to 1.5 UI of peak-to-peak jitter. Since the Quad E1 Mapper supports a ring architecture, two sets of blocks are provided for each port. The TU/VT selection is the same for both blocks. A control bit, and transmit line alarms, can generate an E1AIS.

The eight TU/VT Build blocks format the TU/VT into a STS-1, STS-3 or STM-1 structure for the asynchronous 2048 kbit/s signals, as shown in 2. The pointer value carried in the V1 and V2 bytes is transmitted with a fixed value of 105. Transmit access is provided for the 8 overhead communications channel bits (O-bits) via the microprocessor. The microprocessor also writes the signal label, and the value of the J2 message, either as a 16-byte or a 64-byte message. The Quad E1 Mapper provides the TU tandem connection feature for the TU, including the transmission of the 16-byte message and the various alarms associated with the tandem connection feature. The device provides three-bit RDI using the V5 and K4 (Z7) bytes. Local alarms, or the microprocessor, can generate the remote payload, server, or connectivity defect indications. The Far End Block Error (FEBE) is inserted from the BIP-2 errors detected on the receive side, and BIP-2 parity is generated for the V5 byte. Control bits are provided for generating unequipped status, generating TU/VT AIS, and inserting FEBE and BIP-2 errors. The ability to generate Null Pointer Indicators (NPIs) is also provided for the STM-1 VC-4 format.

The A Transmit block is identical to the B Transmit block. The interface between an add bus and a Transmit block consists of three input leads and eleven output leads, when the add bus timing mode is selected. The input leads are a byte clock, a C1J1V1 indicator, and an SPE indicator. The output leads are byte-wide data, a parity indicator, an add indicator, and an optional TU/VT selection indicator signal. The Add C1J1V1 signal is used in conjunction with the Add SPE signal to determine the location of the various pulses. An option is pro-

. . . . .

## TRANSWITCH'

#### **DATA SHEET**

QE1M TXC-04252

vided in which the drop side V1 reference pulse, either from the drop bus C1J1V1 indicator or from the H4 multiframe detector, may be used as the add side V1 reference pulse.

When drop bus timing is selected, the output leads are byte-wide data, a parity indicator, an add indicator, and an optional TU/VT selection indicator signal. The add bus clock, SPE and C1J1V1 signals are disabled.

The Microprocessor Input/Output Interface block consists of an Intel-, Motorola- or multiplexed address/data-compatible bus interface that provides access to assigned QE1M memory map addresses in the range from 000H to 7FFH (please see the Memory Map and Memory Map Description sections for further information). Interrupt capability is also provided. The alarms that cause the interrupt can be set on positive, negative, or both positive and negative transitions, or on positive levels. Interrupt mask bits are provided for register byte locations, and some defined bits.

Control bits are provided which enable an E1 facility or line loopback. Because of the complexity of the SDH/SONET interface and the two timing modes, SDH/SONET loopback of the TU/VTs is not supported.

The SPOT (SONET Processor for Overhead Termination) block is a RISC processor with associated instruction and data memory that performs selected low-speed functions, including all overhead processing and counter maintenance. The SPOT program must be loaded into the SPOT instruction memory after power-up. Executable microcode is provided by TranSwitch (see the Operations - Internal SPOT Processor section).

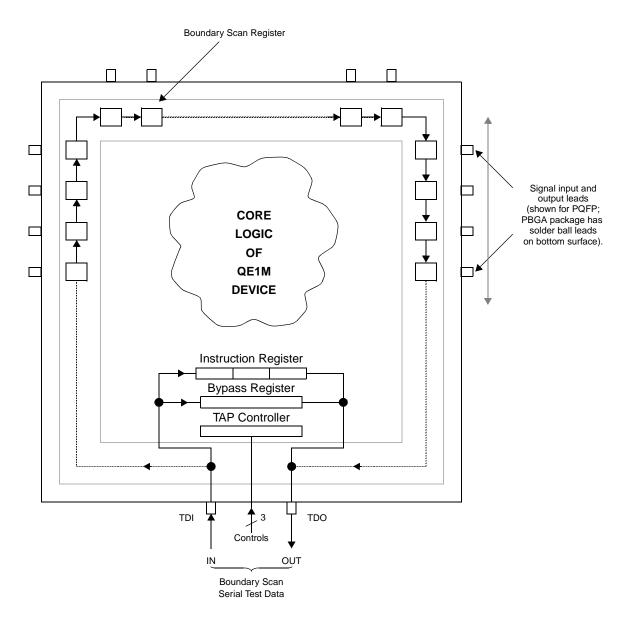

The Boundary Scan Interface Block provides a five-lead Test Access Port (TAP) that conforms to the IEEE 1149.1 standard. This standard provides external boundary scan functions to read and write the external Input/Output leads from the TAP for board and component test.

7 ( 4 4 0

TVO 04050 M

Figure 2. 2048 kbit/s Asynchronous Mapping

. . . . . .

#### **LEAD DIAGRAMS**

Note: See Figure 28 for Package Information. X(Y/Z) format is used for microprocessor interface signals to identify Multiplex (Intel/Motorola) interface functions, where these are different.

Figure 3. QE1M TXC-04252 Plastic Quad Flat Package Lead Diagram

1.10 TVO 0.1050 M

**DATA SHEET**

| VDD        | BD1        | BD3        | BD4        | BD7                                   | BDC1J1V1   | BACLK      | NC         | NC         | QUIET2     | RNO2       | NC         | VDD         | TPI4       | NC         | TCI4          |           |

|------------|------------|------------|------------|---------------------------------------|------------|------------|------------|------------|------------|------------|------------|-------------|------------|------------|---------------|-----------|

| $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$    | 16        |

| NC         | NC         | BD2        | VDD        | BD6                                   | BDSPE      | NC         | GND        | TPI2       | NC         | NC         | RNO4       | NC          | TNI4       | QUIET4     | RDY/DT/       | 4CK<br>15 |

| $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$    | 13        |

| BAPAR      | BADD       | BD0        | NC         | BDPAR                                 | BASPE      | BDCLK      | BDIND      | VDD        | TCI2       | RPO2       | RPO4       | RCO4        | TEST       | NC         | VDD           | 14        |

| $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$                            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | $\bigcup$     |           |

| BA7        | BA6        | GND        | BD5        | VDD                                   | BAC1J1V1   | NC         | BAIND      | NC         | TNI2       | NC         | RCO2       | GND         | UPAD1      | UPAD0      | UPAD2         | 13        |

| $\bigcirc$ | $\bigcirc$ | $\bigcup$  | $\bigcirc$ | $\bigcirc$                            | $\bigcup$  | $\bigcup$  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcup$  | $\bigcup$     |           |

| BA4        | BA5        | BA3        | VDD        |                                       |            |            |            |            |            |            |            | NC          | UPAD5      | UPAD3      | UPAD4         | 12        |

| $\bigcirc$ | $\bigcup$  |            |            |                                       |            |            |            |            |            |            |            | $\bigcup$   | $\bigcup$  |            | $\bigcup$     |           |

| BA2        | NC         | BA1        | BA0        |                                       |            |            |            |            |            |            |            | UPAD7       | UPAD6      | VDD        | NC            | 11        |

| $\bigcup$  | $\bigcup$  | $\bigcup$  | $\bigcirc$ |                                       |            |            |            |            |            |            |            |             | $\bigcup$  | $\bigcup$  | $\bigcup$     |           |

| AA0        | NC         | AA1        | AA2        |                                       |            | NC         | GND        | NC         | GND        |            |            | EXTCK       | VDD        | A0         | HIGHZ         | 10        |

| $\bigcup$  | $\bigcup$  | $\bigcup$  | $\bigcup$  |                                       |            | <u> </u>   | <u> </u>   | $\bigcup$  | <u> </u>   |            |            |             |            | $\bigcup$  |               |           |

| GND        | AA3        | NC         | AA4        |                                       |            | GND        | GND        | GND        | GND        |            |            | VDD         | A2         | A1         | GND           | 9         |

| $\bigcup$  | $\bigcup$  | $\bigcup$  |            |                                       |            | 0          | 0          | 0          |            |            |            |             |            |            |               |           |

| NC         | VDD        | AA6        | AA5        |                                       |            | GND        | GND        | GND        | GND        |            |            | A3          | A4         | SEL        | TEST          | 8         |

| $\bigcup$  |            | $\bigcup$  | $\bigcup$  |                                       |            | <u> </u>   | <u> </u>   | $\bigcup$  |            |            |            | $\subseteq$ |            |            | <u> </u>      |           |

| AAPAR      | AADD       | AA7        | NC         |                                       |            | NC         | GND        | NC         | GND        |            |            | RD          | WR         | INTSH      | ALE           | 7         |

| 100        | VDD        | $\bigcup$  | 400        |                                       |            | $\bigcup$  | $\bigcup$  | $\bigcup$  | $\bigcup$  |            |            | U)          | 0          | VDD        | \( \tag{\chi} |           |

| AD2        | VDD        | AD1        | AD0        |                                       |            |            |            |            |            |            |            | INT/IRQ     | A5         | VDD        | NC            | 6         |

| AD5        | NC         | AD4        | AD3        |                                       |            |            |            |            |            |            |            | NC          | RESET      | A6         | NC            |           |

| ADS        |            | AD4        | AD3        |                                       |            |            |            |            |            |            |            |             | KESEI      | Ab         |               | 5         |

| NC         | AD7        | AD6        | GND        | NC                                    | AAC1J1V1   | GND        | NC         | VDD        | TNI1       | RPO1       | RPO3       | TPI3        | NC         | NC         | ABUST         |           |

|            | ADI        | ADO        | GND        |                                       | AACIJIVI   | GND        |            |            |            | ( )        | ( )        |             |            |            | ABUST         | 4         |

| ADDAD      | NO         | NO         | NO         | ADODE                                 | NO         | ADCLIC     | AAIND      | NO         | NO         | DNIOA      | DNO        | TOIO        | LIDAGO     | NO         | 47            |           |

| ADPAR      | NC         | NC         | NC         | ADSPE                                 | NC         | ADCLK      | AAIND      | NC         | NC         | RN01       | RNOS       | 3 TCI3      | UPA10      | NC         | A7            | 3         |

| VDD        | TCK        | NC         | TMS        | VDD                                   | ADC1J1V1   | AACIK      | ADIND      | NC         | QUIET1     | VDD        | VDD        | QUIET3      | GND        | UPA9       | UPA8          |           |

|            |            |            |            |                                       | ADCIJIVI   | AACER      |            |            | COLLIT     |            |            | QOIL 13     |            | OIAS       | OTAG          | 2         |

| NO         | TDI        | TDO        | TDC        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | AACDE      | CNID       | NO         | TDIA       | TOU        | D004       | DOOD       | TNUO        | MILIV      | мото       | NO            |           |

| NC         | TDI        | TDO        | TRS        | NC                                    | AASPE      | GND        | NC         | TPI1       | TCI1       | RCO1       | RCO3       | TNI3        | MUX        | мото       | NC            | 1         |

|            | R          | P          | N          | M                                     |            | K          |            | <u> </u>   | G          | F          | F          | D           | C          | R          | $\bigcirc$    |           |

|            |            |            |            |                                       |            |            |            |            |            |            |            |             |            |            |               |           |

Note: This is the bottom view. The leads are solder balls. See Figure 29 for package information. Some signal Symbols have been abbreviated to fit the space available. The Symbols are shown in full in the Lead Descriptions section.

Figure 4. QE1M TXC-04252 Plastic Ball Grid Array Package Lead Diagram

#### **LEAD DESCRIPTIONS**

#### POWER SUPPLY, GROUND AND NO CONNECT

| Symbol | 160-Lead<br>PQFP Lead<br>No.                                                                              | 208-Lead<br>PBGA<br>Lead No.                                                                                                                                                                                                                                                    | I/O/P * | Туре | Name/Function                                                                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | 9, 13, 22,<br>34, 41, 49,<br>57, 70, 79,<br>86, 92, 103,<br>115, 123,<br>131, 137,<br>142, 154            | A14, B6,<br>B11, C10,<br>D9, D16,<br>E2, F2, H4,<br>H14, M2,<br>M13, N12,<br>N15, R6,<br>R8, T2, T16                                                                                                                                                                            | Р       |      | VDD: +5 volt supply voltage, ±5%.                                                                                                                                                     |

| GND    | 4, 17, 25,<br>27, 29, 40,<br>45, 53, 61,<br>66, 74, 81,<br>97, 100,<br>108, 120,<br>127, 134,<br>139, 151 | A9, C2,<br>D13, G7,<br>G8, G9,<br>G10, H8,<br>H9, J7, J8,<br>J9, J10,<br>J15, K1, K4,<br>K8, K9, N4,<br>P13, T9                                                                                                                                                                 | P       |      | Ground: 0 volt reference.                                                                                                                                                             |

| NC     | 80                                                                                                        | A1, A5, A6,<br>A11, B3,<br>B4, B14,<br>B16, C4,<br>D5, D12,<br>D15, E16,<br>F13, F15,<br>G3, G15,<br>H2, H3, H7,<br>H10, H13,<br>H16, J1, J4,<br>J16, K7,<br>K10, K13,<br>K15, L3,<br>M1, M4, N3,<br>N7, N14,<br>P2, P3, P9,<br>R3, R5,<br>R10, R11,<br>R15, T1,<br>T4, T8, T15 |         |      | No Connect: NC leads are not to be connected, not even to another NC lead, but must be left floating. Connection of these leads may impair performance or cause damage to the device. |

Note: I = Input; O = Output; P = Power; T=Tristate

TVO 04050 M

#### **DATA SHEET**

#### A DROP AND A ADD BUS I/O

| Symbol   | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No.         | I/O/P | Type *      | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------------------------------|--------------------------------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCLK    | 26                           | К3                                   | I     | TTL         | A Drop Bus Clock: This clock operates at 19.44 MHz for STM-1/STS-3 operation, and at 6.48 MHz for STS-1 operation. A Drop bus byte-wide data (AD7-AD0), the parity bit (ADPAR), SPE indication (ADSPE), and the C1J1V1 indication (ADC1J1V1) are clocked in on falling edges of this clock. This clock may also be used for timing and deriving the like-named add bus byte-wide data, add and TU/VT indications, and parity bits. The add bus signals are clocked out on rising edges of the clock during the time slots that correspond to the selected TU/VT.        |

| ADPAR    | 42                           | Т3                                   | I     | TTL         | A Drop Bus Parity Bit: An odd parity bit input signal representing the parity calculation for each data byte, SPE, and C1J1V1 signal from the drop bus. Control bits are provided in address 012H which enable parity to be calculated as even (control bit DPE is 1), and/or for the data byte only (control bit PDDO is 1).                                                                                                                                                                                                                                           |

| AD(7-0)  | 43, 44,<br>46-48,<br>50-52   | R4, P4, T5,<br>P5, N5, T6,<br>P6, N6 | I     | TTL         | A Drop Bus Data Byte: Byte-wide data that corresponds to the STM-1/STS-3/STS-1 signal from the drop bus. The first bit received (dropped) corresponds to bit 7.                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADSPE    | 33                           | M3                                   | I     | TTL         | A Drop Bus SPE Indicator: A signal that is active high during each byte of the STM-1/STS-3/STS-1 payload, and low during Transport Overhead times.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ADC1J1V1 | 32                           | L2                                   | ı     | TTL         | A Drop Bus C1J1V1 Indications: An active high timing signal that carries STM-1/STS-3/STS-1 starting frame and SPE information. This signal works in conjunction with the ADSPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1/STS-3 signal, and the C1 byte in the STS-1 signal, when ADSPE is low. The J1 signal identifies the starting location of the J1 signal when ADSPE is high. One or more V1 pulses may be present depending upon the format. The V1 pulses may be used in place of the H4 byte as the multiframe indication. |

| ADIND    | 24                           | J2                                   | 0     | CMOS<br>4mA | A Drop Bus TU/VT Selection Indication: Enabled when control bit ADnEN is written with a 1. An active low signal that is clocked out for the time slots determined by TU/VT selection (RTUNn register) for each port (n=port number, 1-4).                                                                                                                                                                                                                                                                                                                               |

<sup>\*</sup>See Input, Output and Input/Output Parameters section below for Type definitions.

# TRANSWITCH\*

### DATA SHEET

| Symbol   | 160-Lead<br>PQFP<br>Lead No.            | 208-Lead<br>PBGA<br>Lead No.               | I/O/P | Type *      | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------------|--------------------------------------------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AACLK    | 28                                      | K2                                         | I     | TTL         | A Add Bus Clock: When the add bus timing mode is selected, this input must be provided for add bus timing. This clock operates at 19.44 MHz for STM-1/STS-3 operation, and at 6.48 MHz for STS-1 operation. The add bus SPE indication (AASPE), and the C1J1V1 indication (AAC1J1V1) are clocked in on falling edges of this clock. Add bus byte-wide data (AA7-AA0), add indicator (AADD), and parity bit (AAPAR) are clocked out on rising edges of the clock during the time slots that correspond to the selected TU/VT. When drop bus timing is selected, this input is disabled.                                                                                                                               |

| AAPAR    | 55                                      | T7                                         | O(T)  | CMOS<br>4mA | A Add Bus Parity Bit: An odd parity output signal that is calculated over the byte-wide add data. This tristate lead is only active when there is data being added to the add bus. When control bit APE is 1, even parity is calculated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AA(7-0)  | 56, 58,<br>59, 60,<br>62, 63,<br>64, 65 | P7, P8,<br>N8, N9,<br>R9, N10,<br>P10, T10 | O(T)  | CMOS<br>4mA | A Add Bus Data Byte: Byte-wide data that corresponds to the selected TU/VT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AASPE    | 31                                      | L1                                         | I     | TTL         | A Add Bus SPE Indicator: When the add bus timing mode is selected, this signal must be provided for add bus timing. This signal must be high during each byte of the STM-1/STS-3/STS-1 payload, and low during Transport Overhead byte times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AAC1J1V1 | 30                                      | L4                                         | I     | TTL         | A Add Bus C1J1V1 Indications: When the add bus timing mode is selected, this signal must be provided for add bus timing. An active high timing signal that carries STM-1/STS-3/STS-1 starting frame and SPE information. This signal works in conjunction with the AASPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1/STS-3 signal, and the C1 byte in the STS-1 signal, when AASPE is low. The J1 signal identifies the starting location of the J1 signal when AASPE is high. The J1 signal identifies the location of the J1 byte. One or more V1 pulses may be present depending upon the format. The V1 pulses are used in place of the H4 byte as the multiframe indication. |

| AAIND    | 23                                      | J3                                         | 0     | CMOS<br>4mA | A Add Bus TU/VT Selection Indication: Enabled when control bit AAnEN is written with a 1. An active low signal that is clocked out for the time slots determined by TU/VT selection (TTUNn register) for each port (n=port number, 1-4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AADD     | 54                                      | R7                                         | 0     | CMOS<br>4mA | A Add Bus Add Data Present Indicator: This normally active low signal is present when output data to the A Add bus is valid. It identifies the location of all of the TU/VT time slots being selected. When control bit ADDI is 1, the indicator is active high instead of active low.                                                                                                                                                                                                                                                                                                                                                                                                                               |

40 (440

TVO 04050 M5

#### **DATA SHEET**

#### **B DROP AND B ADD BUS I/O**

| Symbol   | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No.                    | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------------------------------|-------------------------------------------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDCLK    | 99                           | K14                                             | I     | TTL         | B Drop Bus Clock: This clock operates at 19.44 MHz for STM-1/STS-3 operation, and at 6.48 MHz for STS-1 operation. B Drop bus byte-wide data (BD7-BD0), the parity bit (BDPAR), SPE indication (BDSPE), and the C1J1V1 indication (BDC1J1V1) are clocked in on falling edges of this clock. This clock may also be used for timing and deriving the like-named add bus byte-wide data, add and TU/VT indications, and parity bits. The add bus signals are clocked out on rising edges of the clock during the time slots that correspond to the selected TU/VT.        |

| BDPAR    | 91                           | M14                                             | I     | TTL         | B Drop Bus Parity Bit: An odd parity bit input signal representing the parity calculation for each data byte, SPE, and C1J1V1 signal from the drop bus. Control bits are provided in address 012H which enable parity to be calculated as even (control bit DPE is 1), and/or for the data byte only (control bit PDDO is 1).                                                                                                                                                                                                                                           |

| BD(7-0)  | 90-87,<br>85-82              | M16, M15,<br>N13, N16,<br>P16, P15,<br>R16, P14 | I     | TTL         | B Drop Bus Data Byte: Byte-wide data that corresponds to the STM-1/STS-3/STS-1 signal from the drop bus. The first bit received (dropped) corresponds to bit 7.                                                                                                                                                                                                                                                                                                                                                                                                         |

| BDSPE    | 93                           | L15                                             | I     | TTL         | <b>B Drop Bus SPE Indicator:</b> A signal that is active high during each byte of the STM-1/STS-3/STS-1 payload, and low during Transport Overhead times.                                                                                                                                                                                                                                                                                                                                                                                                               |

| BDC1J1V1 | 94                           | L16                                             | I     | TTL         | B Drop Bus C1J1V1 Indications: An active high timing signal that carries STM-1/STS-3/STS-1 starting frame and SPE information. This signal works in conjunction with the BDSPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1/STS-3 signal, and the C1 byte in the STS-1 signal, when BDSPE is low. The J1 signal identifies the starting location of the J1 signal when BDSPE is high. One or more V1 pulses may be present depending upon the format. The V1 pulses may be used in place of the H4 byte as the multiframe indication. |

| BDIND    | 101                          | J14                                             | 0     | CMOS<br>4mA | B Drop Bus TU/VT Selection Indication: Enabled when control bit BDnEN is written with a 1. An active low signal that is clocked out for the time slots determined by TU/VT selection (RTUNn register) for each port (n=port number, 1-4).                                                                                                                                                                                                                                                                                                                               |

# TRANSWITCH\*

### DATA SHEET

| Symbol   | 160-Lead<br>PQFP<br>Lead No.         | 208-Lead<br>PBGA<br>Lead No.                    | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|--------------------------------------|-------------------------------------------------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BACLK    | 98                                   | K16                                             | I     | TTL         | B Add Bus Clock: When the add bus timing mode is selected, this input must be provided for add bus timing. This clock operates at 19.44 MHz for STM-1/STS-3 operation, and at 6.48 MHz for STS-1 operation. The add bus SPE indication (BASPE), and the C1J1V1 indication (BAC1J1V1) are clocked in on falling edges of this clock. Add bus byte-wide data (BA7-BA0), add indicator (BADD), and parity bit (BAPAR) are clocked out on rising edges of the clock during the time slots that correspond to the selected TU/VT. When drop bus timing is selected, this input is disabled.                                                                                                                               |

| BAPAR    | 77                                   | T14                                             | O(T)  | CMOS<br>4mA | <b>B Add Bus Parity Bit:</b> An odd parity output signal that is calculated over the byte-wide add data. This tristate lead is only active when there is data being added to the add bus. When control bit APE is 1, even parity is calculated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BA(7-0)  | 76, 75, 73,<br>72, 71, 69,<br>68, 67 | T13, R13,<br>R12, T12,<br>P12, T11,<br>P11, N11 | O(T)  | CMOS<br>4mA | <b>B Add Bus Data Byte:</b> Byte-wide data that corresponds to the selected TU/VT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BASPE    | 95                                   | L14                                             | I     | TTL         | B Add Bus SPE Indicator: When the add bus timing mode is selected, this signal must be provided for add bus timing. This signal must be high during each byte of the STM-1/STS-3/STS-1 payload, and low during Transport Overhead byte times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BAC1J1V1 | 96                                   | L13                                             | I     | TTL         | B Add Bus C1J1V1 Indications: When the add bus timing mode is selected, this signal must be provided for add bus timing. An active high timing signal that carries STM-1/STS-3/STS-1 starting frame and SPE information. This signal works in conjunction with the BASPE signal. The C1 pulse identifies the location of the first C1 byte in the STM-1/STS-3 signal, and the C1 byte in the STS-1 signal, when BASPE is low. The J1 signal identifies the starting location of the J1 signal when BASPE is high. The J1 signal identifies the location of the J1 byte. One or more V1 pulses may be present depending upon the format. The V1 pulses are used in place of the H4 byte as the multiframe indication. |

| BAIND    | 102                                  | J13                                             | 0     | CMOS<br>4mA | B Add Bus TU/VT Selection Indication: Enabled when control bit BAnEN is written with a 1. An active low signal that is clocked out for the time slots determined by TU/VT selection (TTUNn register) for each port (n=port number, 1-4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BADD     | 78                                   | R14                                             | 0     | CMOS<br>4mA | B Add Bus Add Data Present Indicator: This normally active low signal is present when output data to the B Add bus is valid. It identifies the location of all of the TU/VT time slots being selected. When control bit ADDI is 1, the indicator is active high instead of active low.                                                                                                                                                                                                                                                                                                                                                                                                                               |

45 (440

#### PORT n LINE INTERFACE (n = 1, 2, 3 or 4)

| Symbol              | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No. | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                             |

|---------------------|------------------------------|------------------------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCOn<br>(n=1-4)     | 14, 111,<br>10, 114          | F1, E13,<br>E1, D14          | O(T)  | CMOS<br>4mA | Receive Port n Output Clock: A 2.048 MHz clock output. Data is normally clocked out on rising edges of this clock. When control bit RCKI is 1, data is clocked out on falling edges of this clock. When control bit RnEN is 0, this lead is forced to a high impedance state.             |

| RPOn<br>(n=1-4)     | 16, 109,<br>12, 112          | F4, F14,<br>E4, E14          | O(T)  | CMOS<br>4mA | Receive Port n Data Positive Rail or NRZ: When control bit BYPASn is 0, positive rail data is provided on this lead. When control bit BYPASn is 1, an NRZ signal is provided on this lead. When control bit RnEN is 0, this lead is forced to a high impedance state.                     |

| RNOn<br>(n=1-4)     | 15, 110,<br>11, 113          | F3, F16,<br>E3, E15          | O(T)  | CMOS<br>4mA | Receive Port n Data Negative Rail: When control bit BYPASn is 0, negative rail data is provided on this lead. When control bit RnEN is 0, or control bit BYPASn is 1, this lead is forced to a high impedance state.                                                                      |

| TCIn<br>(n=1-4)     | 19, 106,<br>6, 118           | G1, G14,<br>D3, A16          | I     | TTL         | Transmit Port n Input Clock: A 2.048 MHz clock input. Data is normally clocked in on falling edges of this clock. When control bit TCKI is 1, data is clocked in on the rising edges of this clock.                                                                                       |

| TPIn<br>(n=1-4)     | 21, 104,<br>8, 116           | H1, H15,<br>D4, C16          | I     | TTL         | Transmit Port n Data Positive Rail or NRZ: When control bit BYPASn is 0, positive rail input data is provided on this lead. When control bit BYPASn is 1, an NRZ signal is provided on this lead.                                                                                         |

| TNIn/ TLOSn (n=1-4) | 20, 105,<br>7, 117           | G4, G13,<br>D1, C15          | I     | TTL         | Transmit Port n Data Negative Rail/External Loss Of Signal: When control bit BYPASn is 0, negative rail input data is provided on this lead. When control bit BYPASn is 1, this lead may be used to input an active low external loss of signal indicator from the line interface device. |

| QUIETn<br>(n=1-4)   | 18, 107,<br>5, 119           | G2, G16,<br>D2, B15          | I     | TTL         | Quiet Port n: A high forces the RPOn and RNOn leads to the 0 state for either a rail or NRZ interface, overriding control bit RnEN when it is 0. A low disables this feature.                                                                                                             |

#### MICROPROCESSOR BUS INTERFACE SELECTION

| Symbol | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No. | I/O/P | Туре | Name/Function                                                                                                                                                                                               |

|--------|------------------------------|------------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUX    | 3                            | C1                           | I     |      | <b>Multiplex Mode:</b> A high placed on this lead configures the microprocessor bus to a multiplexed address/data bus interface. A low configures the Intel or Motorola interfaces (see Symbol MOTO below). |

# TRANSWITCH'

### DATA SHEET

| Symbol | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                          |

|--------|------------------------------|------------------------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| МОТО   | 2                            | B1                           | _     | TTL  | Motorola Mode: Enabled when a low is placed on the MUX lead. The following table lists the bus selection options.  MUX MOTO Action H L or H Multiplex bus interface L L Intel bus interface L H Motorola bus interface This selection modifies some bus interface lead functions, as described in the next two sections of this table. |

#### MICROPROCESSOR BUS INTERFACE - MULTIPLEXED BUS

| Symbol    | 160-Lead<br>PQFP<br>Lead No.                    | 208-Lead<br>PBGA<br>Lead No.                    | I/O/P         | Туре            | Name/Function                                                                                                                                                                                                                        |

|-----------|-------------------------------------------------|-------------------------------------------------|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPA(10-8) | 1, 160,<br>159                                  | C3, B2, A2                                      | I<br>(Note 1) | TTL<br>(Note 1) | Address Bus: These are additional address lines for accessing QE1M memory locations (most significant three bits). UPA10 is the most significant bit. High is logic 1.                                                               |

| UPAD(7-0) | 133, 132,<br>130, 129,<br>128, 126,<br>125, 124 | D11, C11,<br>C12, A12,<br>B12, A13,<br>C13, B13 | I/O           | TTL<br>8mA      | Address/Data Bus: These leads are the time-multi-<br>plexed address (lower eight bits only) and data bus<br>for accessing the QE1M memory locations. UPAD7<br>is the most significant bit. High is logic 1.                          |

| SEL       | 146                                             | B8                                              | _             | TTL             | <b>Select:</b> An active low signal generated by the microprocessor for accessing the QE1M memory locations.                                                                                                                         |

| RD        | 147                                             | D7                                              | I             | TTL             | <b>Read:</b> An active low signal generated by the microprocessor for reading the QE1M memory locations. The memory map is selected by placing a low on the select lead.                                                             |

| WR        | 148                                             | C7                                              | I             | TTL             | <b>Write:</b> An active low signal generated by the microprocessor for writing to QE1M memory locations. The memory map is selected by placing a low on the select lead.                                                             |

| ALE       | 149                                             | A7                                              | I             | TTL             | Address Latch Enable: An active high signal generated by the microprocessor for holding an address stable during a read or write cycle.                                                                                              |

| RDY       | 122                                             | A15                                             | O(T)          | TTL<br>8mA      | Ready: A high is an acknowledgment from the addressed memory location that the transfer can be completed. A low indicates that the Mapper cannot complete the transfer cycle, and that microprocessor wait states must be generated. |

| INT       | 152                                             | D6                                              | O(T)          | TTL<br>8mA      | Interrupt: A high or low on this output lead signals an interrupt request to the microprocessor. The polarity of this signal is determined by the state of the INTSH lead.                                                           |

#### **DATA SHEET**

| Symbol | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No. | I/O/P | Туре | Name/Function                                                                                                                                                                            |

|--------|------------------------------|------------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTSH  | 150                          | В7                           | I     |      | Interrupt Sense High Selection: A high on this lead causes the interrupt sense to be high when an interrupt occurs. A low causes the interrupt sense to be low when an interrupt occurs. |

Note 1: Leads UPA(10-8) are implemented as Input/Output type TTL 4mA to support production tests but are used as TTL inputs.

#### MICROPROCESSOR BUS INTERFACE - SPLIT BUS FOR MOTOROLA (M) OR INTEL (I)

| Symbol        | 160-Lead<br>PQFP<br>Lead No.                                       | 208-Lead<br>PBGA<br>Lead No.                               | I/O/P         | Туре            | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------------|--------------------------------------------------------------------|------------------------------------------------------------|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A(10-0)       | 1, 160,<br>159, 158,<br>156, 153,<br>144, 143,<br>141, 140,<br>135 | C3, B2,<br>A2, A3,<br>B5, C6,<br>C8, D8,<br>C9, B9,<br>B10 | I<br>(Note 1) | TTL<br>(Note 1) | Address Bus (Motorola/Intel Buses): These address line inputs are used for accessing a QE1M memory location for a read/write cycle. A10 is the most significant bit. High is logic 1.                                                                                                                                                                                                                                                                                                                                                     |  |

| D(7-0)        | 133, 132,<br>130, 129,<br>128, 126,<br>125, 124                    | D11, C11,<br>C12, A12,<br>B12, A13,<br>C13, B13            | I/O           | TTL<br>8mA      | <b>Data Bus (Motorola/Intel Buses):</b> Bidirectional data lines used for transferring data to or from a QE1M memory location. D7 is the most significant bit. High is logic 1.                                                                                                                                                                                                                                                                                                                                                           |  |

| SEL           | 146                                                                | B8                                                         | I             | TTL             | <b>Select:</b> A low enables data transfers between the microprocessor and the QE1M memory during a read/write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| RD /<br>RD/WR | 147                                                                | D7                                                         | I             | TTL             | Read (I mode) or Read/Write (M mode): Intel Mode - An active low signal generated by the micro- processor for reading the QE1M memory locations. Motorola Mode - An active high signal generated by the microprocessor for reading the QE1M memory locations. An active low signal is used to write to memory locations.                                                                                                                                                                                                                  |  |

| WR /<br>LDS   | 148                                                                | C7                                                         | I             | TTL             | Write (I mode) or Device Select (M mode): Intel Mode - An active low signal generated by the mic processor for writing to the QE1M memory locations. Motorola Mode - The SEL and LDS inputs are logically OR-gated inside the QE1M, generating an internal actilow select signal (CS) that is similar to SEL. This internal signal is used to enable data transfer. This lead can be used for the interface with the Motorola 68302 microprocessor. If it is not used, it should be tied to ground, so that CS is the same signal as SEL. |  |

# TRANSWITCH:

#### **DATA SHEET**

| Symbol      | 160-Lead<br>PQFP<br>Lead No. | 208-Lead<br>PBGA<br>Lead No. | I/O/P | Туре       | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|------------------------------|------------------------------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY / DTACK | 122                          | A15                          | O(T)  | TTL<br>8mA | Ready (I mode) or Data Transfer Acknowledge (M mode): Intel Mode - A high is an acknowledgment from the addressed QE1M memory location that the transfer can be completed. A low indicates that the Mapper cannot complete the transfer cycle, and that microprocessor wait states must be generated.  Motorola Mode - During a read bus cycle, a low signal indicates that the information on the data bus is valid. During a write bus cycle, a low signal acknowledges the acceptance of data. This lead is tristated. |

| INT/<br>IRQ | 152                          | D6                           | O(T)  | TTL<br>8mA | Interrupt: When INTSH is high, a high on this output lead signals an interrupt request INT to the microprocessor, as required for Intel. When INTSH is low, a low signals an interrupt request $\overline{\text{IRQ}}$ to the microprocessor, as required for Motorola.                                                                                                                                                                                                                                                   |