## 捷多邦,专业PCB打样工厂,24小时加急出货

#### April 2002

400mW(typ.)

0.1µA(typ.)

National Semiconductor

# LM4890 Boomer<sup>®</sup> Audio Power Amplifier Series 1 Watt Audio Power Amplifier

## **General Description**

The LM4890 is an audio power amplifier primarily designed for demanding applications in mobile phones and other portable communication device applications. It is capable of delivering 1 watt of continuous average power to an  $8\Omega$  BTL load with less than 1% distortion (THD+N) from a  $5V_{DC}$  power supply.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM4890 does not require output coupling capacitors or bootstrap capacitors, and therefore is ideally suited for mobile phone and other low voltage applications where minimal power consumption is a primary requirement.

The LM4890 features a low-power consumption shutdown mode, which is achieved by driving the shutdown pin with logic low. Additionally, the LM4890 features an internal thermal shutdown protection mechanism.

The LM4890 contains advanced pop & click circuitry which eliminates noises which would otherwise occur during turn-on and turn-off transitions.

The LM4890 is unity-gain stable and can be configured by external gain-setting resistors.

# **Key Specifications**

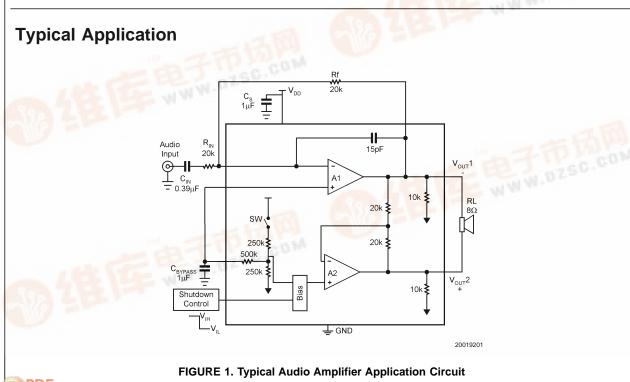

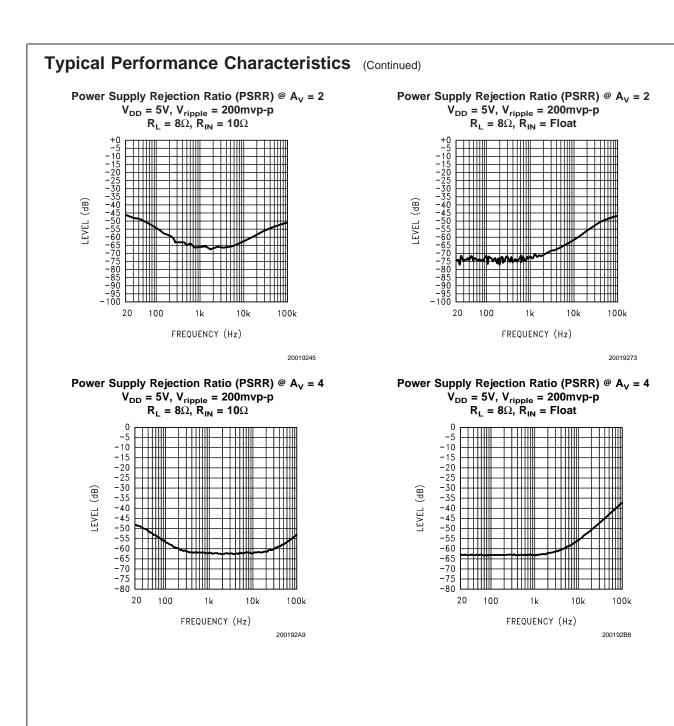

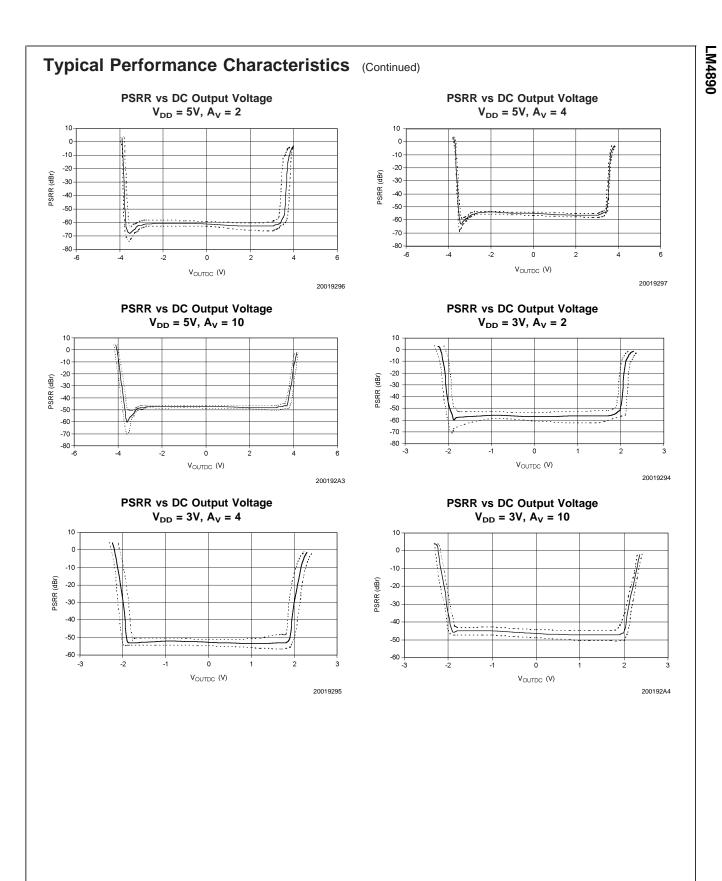

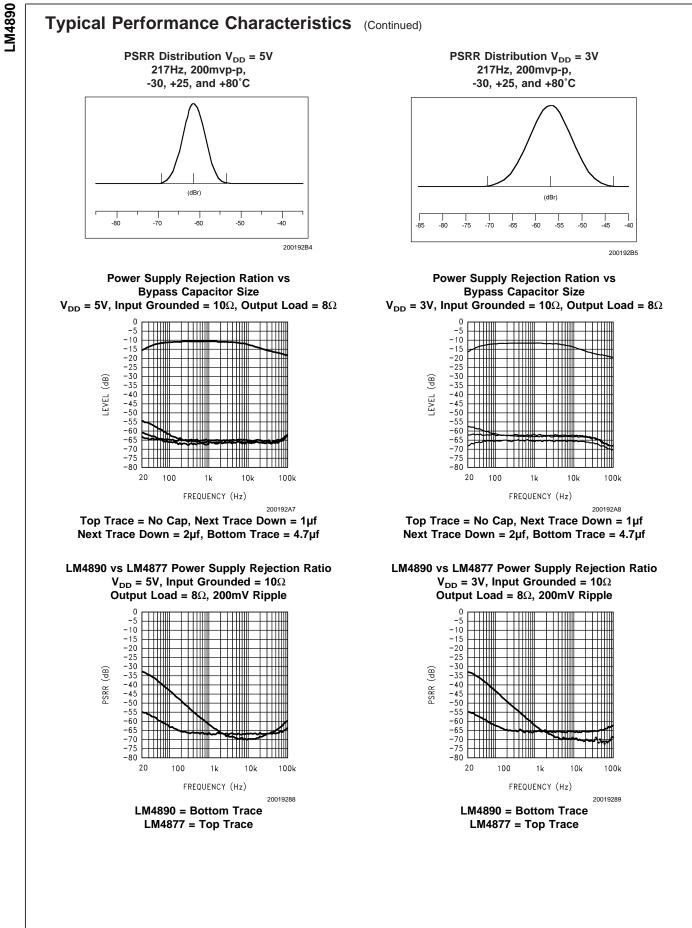

- PSRR at 217Hz, V<sub>DD</sub> = 5V (Fig. 1) 62dB(typ.)

- Power Output at 5.0V & 1% THD 1W(typ.)

- Power Output at 3.3V & 1% THD

- Shutdown Current

## **Features**

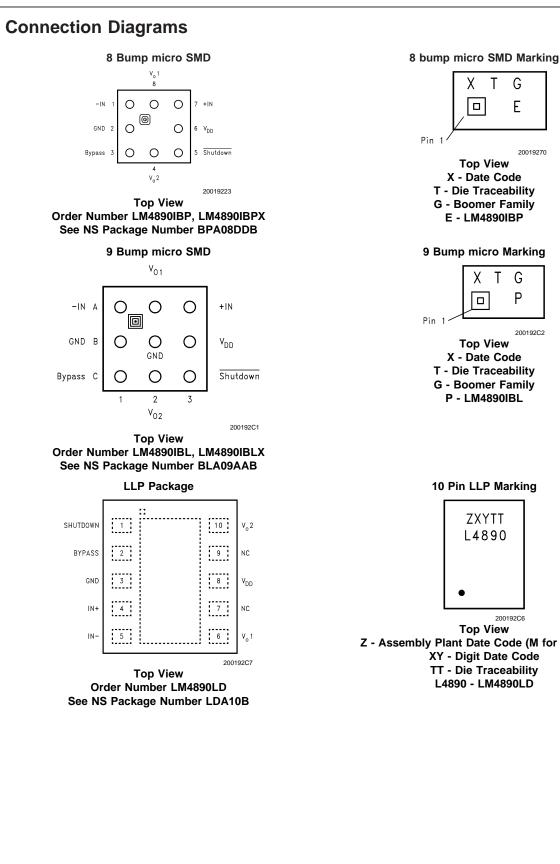

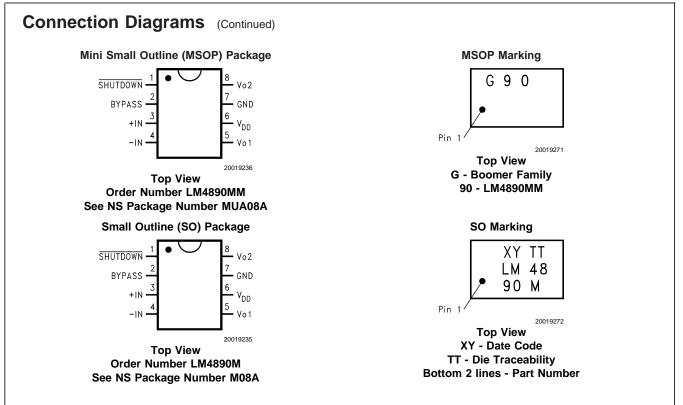

- Available in space-saving packages: micro SMD, MSOP, SOIC, and LLP

- Ultra low current shutdown mode

- BTL output can drive capacitive loads

- Improved pop & click circuitry eliminates noises during turn-on and turn-off transitions

- 2.2 5.5V operation

- No output coupling capacitors, snubber networks or bootstrap capacitors required

- Unity-gain stable

- External gain configuration capability

# Applications

- Mobile Phones

- PDAs

- Portable electronic devices

Boomer® is a registered trademark of National Semiconductor Corporation.

© 2002 National Semiconductor Corporation DS200192

www.national.com

LM4890 1 Watt Audio Power Amplifier

G

Ε

20019270

Х Т

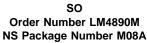

**Top View** X - Date Code

E - LM4890IBP

**Top View** Z - Assembly Plant Date Code (M for Malacca) XY - Digit Date Code TT - Die Traceability L4890 - LM4890LD

#### Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (Note 11)                  | 6.0V                           |

|-------------------------------------------|--------------------------------|

| Storage Temperature                       | –65°C to +150°C                |

| Input Voltage                             | –0.3V to V <sub>DD</sub> +0.3V |

| Power Dissipation (Note 3)                | Internally Limited             |

| ESD Susceptibility (Note 4)               | 2000V                          |

| Junction Temperature                      | 150°C                          |

| Thermal Resistance                        |                                |

| $\theta_{\rm JC}$ (SOP)                   | 35°C/W                         |

| $\theta_{JA}$ (SOP)                       | 150°C/W                        |

| $\theta_{JA}$ (8 Bump micro SMD, Note 12) | 220°C/W                        |

| $\theta_{JA}$ (9 Bump micro SMD, Note 12)     | 180°C/W |  |  |

|-----------------------------------------------|---------|--|--|

| $\theta_{JC}$ (MSOP)                          | 56°C/W  |  |  |

| $\theta_{JA}$ (MSOP)                          | 190°C/W |  |  |

| $\theta_{JA}$ (LLP)                           | 220°C/W |  |  |

| Soldering Information                         |         |  |  |

| See AN-1112 'microSMD Wafers Level Chip Scale |         |  |  |

Package.'

See AN-1187 'Leadless Leadframe Package (LLP).'

# **Operating Ratings**

#### **Temperature Range**

| $T_{MIN} \leq T_A \leq T_{MAX}$ | $-40^{\circ}C \le T_A \le 85^{\circ}C$ |

|---------------------------------|----------------------------------------|

| Supply Voltage                  | $2.2V \leq V_{DD} \leq 5.5V$           |

**Electrical Characteristics**  $V_{DD} = 5V$  (Notes 1, 2, 8) The following specifications apply for the circuit shown in Figure 1 unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

|                      |                                  |                                       | LM4890        |              | 11.26             |

|----------------------|----------------------------------|---------------------------------------|---------------|--------------|-------------------|

| Symbol               | Parameter                        | Conditions                            | Typical       | Limit        | Units<br>(Limite) |

|                      |                                  |                                       | (Note 6)      | (Notes 7, 9) | (Limits)          |

| I <sub>DD</sub>      | Quiescent Power Supply Current   | $V_{IN} = 0V, I_o = 0A, No Load$      | 4             | 8            | mA (max)          |

|                      |                                  | $V_{IN} = 0V, I_o = 0A, 8\Omega$ Load | 5             | 10           | mA (max)          |

| I <sub>SD</sub>      | Shutdown Current                 | V <sub>SHUTDOWN</sub> = 0V            | 0.1           | 2.0          | μA (max)          |

| V <sub>SDIH</sub>    | Shutdown Voltage Input High      |                                       |               | 1.2          | V (min)           |

| V <sub>SDIL</sub>    | Shutdown Voltage Input Low       |                                       |               | 0.4          | V (max)           |

| V <sub>os</sub>      | Output Ofsett Voltage            |                                       | 7             | 50           | mV (max)          |

| R <sub>OUT-GND</sub> | Resistor Output to GND (Note 10) |                                       | 0.5           | 9.7          | kΩ (max)          |

|                      |                                  |                                       | 8.5           | 7.0          | kΩ (min)          |

| Po                   | Output Power (8Ω)                | THD = 2% (max); f = 1 kHz             | 1.0           | 0.8          | W                 |

| T <sub>WU</sub>      | Wake-up time                     |                                       | 170           | 220          | ms (max)          |

| T <sub>SD</sub>      | Thermal Shutdown Temperature     |                                       | 170           | 150          | °C (min)          |

|                      |                                  |                                       | 170           | 190          | °C (max)          |

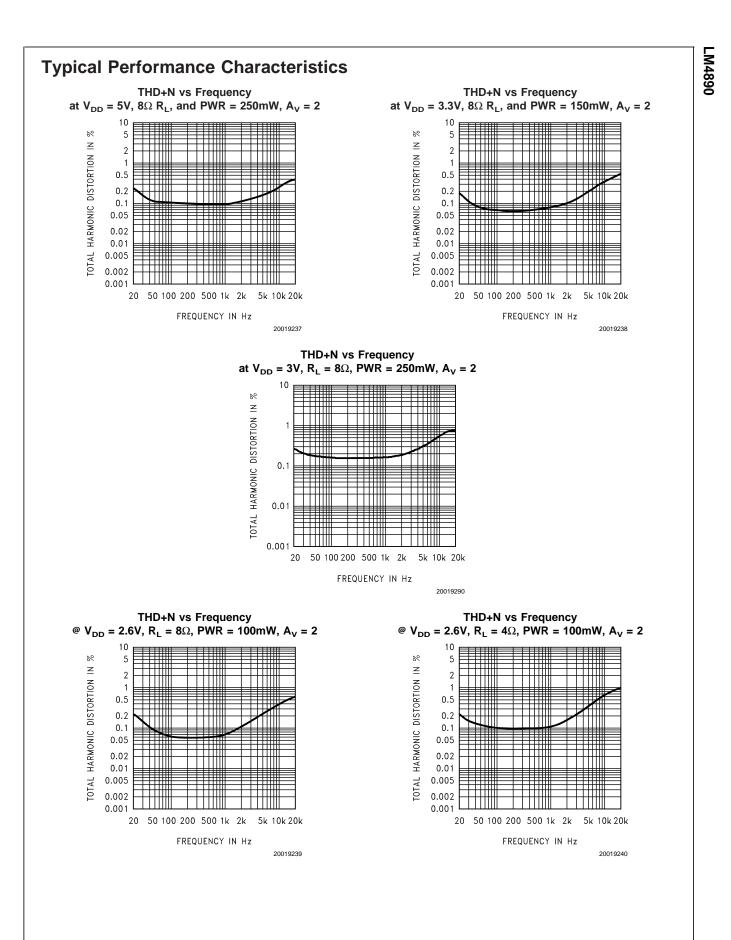

| THD+N                | Total Harmonic Distortion+Noise  | $P_o = 0.4$ Wrms; f = 1kHz            | 0.1           |              | %                 |

| PSRR                 | Power Supply Rejection Ratio     | V <sub>ripple</sub> = 200mV sine p-p  | 62 (f =       | 55           | dB (min)          |

|                      | (Note 14)                        | Input Terminated with 10 ohms to      | 217Hz)        |              |                   |

|                      |                                  | ground                                | 66 (f = 1kHz) |              |                   |

**Electrical Characteristics**  $V_{DD} = 3V$  (Notes 1, 2, 8) The following specifications apply for the circuit shown in Figure 1 unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

|                      |                                  |                                       | LM4      | LM4890       |                   |  |

|----------------------|----------------------------------|---------------------------------------|----------|--------------|-------------------|--|

| Symbol               | Parameter                        | Conditions                            | Typical  | Limit        | Units<br>(Limits) |  |

|                      |                                  |                                       | (Note 6) | (Notes 7, 9) | (Linits)          |  |

| I <sub>DD</sub>      | Quiescent Power Supply Current   | $V_{IN} = 0V, I_o = 0A, No Load$      | 3.5      | 7            | mA (max)          |  |

|                      |                                  | $V_{IN} = 0V, I_o = 0A, 8\Omega$ Load | 4.5      | 9            | mA (max)          |  |

| I <sub>SD</sub>      | Shutdown Current                 | V <sub>SHUTDOWN</sub> = 0V            | 0.1      | 2.0          | μA (max)          |  |

| V <sub>SDIH</sub>    | Shutdown Voltage Input High      |                                       |          | 1.2          | V(min)            |  |

| $V_{SDIL}$           | Shutdown Voltage Input Low       |                                       |          | 0.4          | V(max)            |  |

| Vos                  | Output Offset Voltage            |                                       | 7        | 50           | mV (max)          |  |

| R <sub>OUT-GND</sub> | Resistor Output to Gnd (Note 10) |                                       | 8.5      | 9.7          | kΩ (max)          |  |

|                      |                                  |                                       | 0.0      | 7.0          | k $\Omega$ (min)  |  |

| T <sub>WU</sub>      | Wake-up time                     |                                       | 120      | 180          | ms (max)          |  |

**Electrical Characteristics**  $V_{DD} = 3V$  (Notes 1, 2, 8) The following specifications apply for the circuit shown in Figure 1 unless otherwise specified. Limits apply for  $T_A =$ 25°C. (Continued)

|                 |                                 |                                      | LM4890        |              | 11                |

|-----------------|---------------------------------|--------------------------------------|---------------|--------------|-------------------|

| Symbol          | Parameter                       | Conditions                           | Typical       | Limit        | Units<br>(Limits) |

|                 |                                 |                                      | (Note 6)      | (Notes 7, 9) | (Linits)          |

| Po              | Output Power ( $8\Omega$ )      | THD = 1% (max); f = 1kHz             | 0.31          | 0.28         | W                 |

| T <sub>SD</sub> | Thermal Shutdown Temperature    |                                      | 170           | 150          | °C(min)           |

|                 |                                 |                                      | 170           | 190          | °C(max)           |

| THD+N           | Total Harmonic Distortion+Noise | $P_o = 0.15$ Wrms; f = 1kHz          | 0.1           |              | %                 |

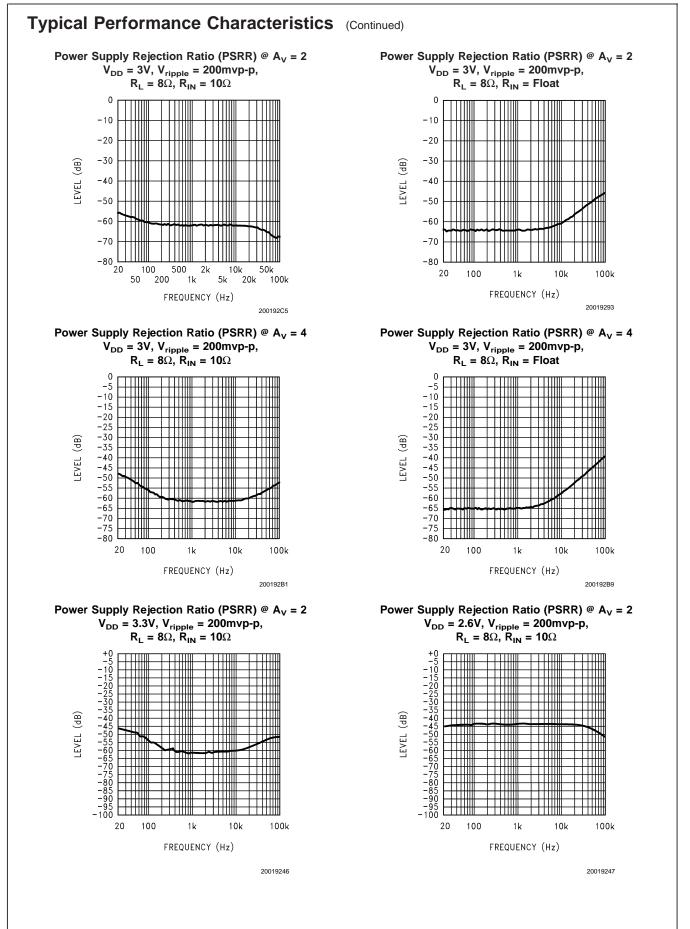

| PSRR            | Power Supply Rejection Ratio    | V <sub>ripple</sub> = 200mV sine p-p | 56 (f =       | 45           | dB(min)           |

|                 | (Note 14)                       | Input terminated with 10 ohms to     | 217Hz)        |              |                   |

|                 |                                 | ground                               | 62 (f = 1kHz) |              |                   |

# Electrical Characteristics V<sub>DD</sub> = 2.6V (Notes 1, 2, 8)

The following specifications apply for for the circuit shown in Figure 1 unless otherwise specified. Limits apply for  $T_A = 25$  °C.

|                 |                                 |                                      | LM4890                   |              | Unite             |

|-----------------|---------------------------------|--------------------------------------|--------------------------|--------------|-------------------|

| Symbol          | Parameter                       | Conditions                           | Typical                  | Limit        | Units<br>(Limits) |

|                 |                                 |                                      | (Note 6)                 | (Notes 7, 9) | (Emits)           |

| I <sub>DD</sub> | Quiescent Power Supply Current  | $V_{IN} = 0V, I_o = 0A, No Load$     | 2.6                      |              | mA (max)          |

| I <sub>SD</sub> | Shutdown Current                | V <sub>SHUTDOWN</sub> = 0V           | 0.1                      |              | µA (max)          |

| P <sub>0</sub>  | Output Power ( $8\Omega$ )      | THD = 1% (max); f = 1 kHz            | 0.2                      |              | W                 |

|                 | Output Power ( $4\Omega$ )      | THD = 1% (max); f = 1 kHz            | 0.22                     |              | W                 |

| THD+N           | Total Harmonic Distortion+Noise | $P_o = 0.1$ Wrms; f = 1kHz           | 0.08                     |              | %                 |

| PSRR            | Power Supply Rejection Ratio    | V <sub>ripple</sub> = 200mV sine p-p | 44 (f =                  |              | dB                |

|                 | (Note 14)                       | Input Terminated with 10 ohms to     | 217Hz)                   |              |                   |

|                 |                                 | ground                               | 44 (f = $1 \text{kHz}$ ) |              |                   |

Note 1: All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

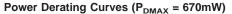

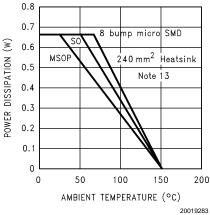

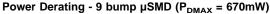

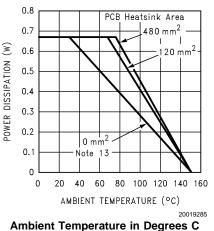

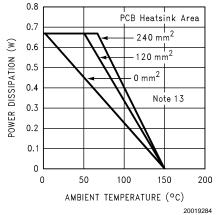

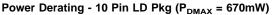

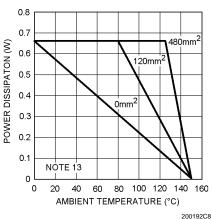

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by TJMAX,  $\theta_{JA}$ , and the ambient temperature TA. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub>-T<sub>A</sub>)/θ<sub>JA</sub> or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4890, see power derating curves for additional information.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Machine Model, 220 pF-240 pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: For micro SMD only, shutdown current is measured in a Normal Room Environment. Exposure to direct sunlight will increase ISD by a maximum of 2µA. Note 9: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 10: ROUT is measured from each of the output pins to ground. This value represents the parallel combination of the 10k ohm output resistors and the two 20k ohm resistors.

Note 11: If the product is in shutdown mode and V<sub>DD</sub> exceeds 6V (to a max of 8V V<sub>DD</sub>), then most of the excess current will flow through the ESD protection circuits. If the source impedance limits the current to a max of 10 ma, then the part will be protected. If the part is enabled when VDD is greater than 5.5V and less than 6.5V, no damage will occur, although operational life will be reduced. Operation above 6.5V with no current limit will result in permanent damage.

Note 12: All bumps have the same thermal resistance and contribute equally when used to lower thermal resistance. All bumps must be connected to achieve specified thermal resistance.

Note 13: Maximum power dissipation (P<sub>DMAX</sub>) in the device occurs at an output power level significantly below full output power. P<sub>DMAX</sub> can be calculated using Equation 1 shown in the Application section. It may also be obtained from the power dissipation graphs

Note 14: PSRR is a function of system gain. Specifications apply to the circuit in Figure 1 where A<sub>V</sub> = 2. Higher system gains will reduce PSRR value by the amount of gain increase. A system gain of 10 represents a gain increase of 14dB. PSRR will be reduced by 14dB and applies to all operating voltages.

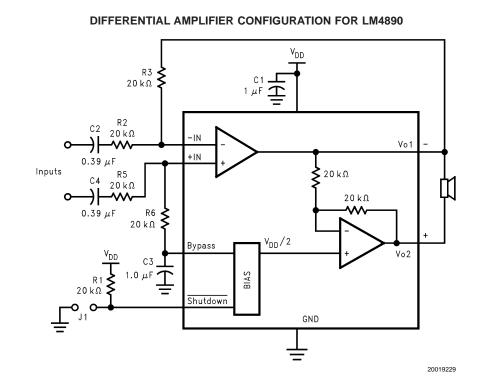

# External Components Description (Figure 1)

| Components                                                                                                                   |                 | Functional Description                                                                                                     |  |  |

|------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| 1. R <sub>IN</sub> Inverting input resistance which sets the closed-loop gain in conjunction with R <sub>f</sub> . This resi |                 | Inverting input resistance which sets the closed-loop gain in conjunction with R <sub>f</sub> . This resistor also forms a |  |  |

|                                                                                                                              |                 | high pass filter with $C_{IN}$ at $f_C = 1/(2\pi R_{IN}C_{IN})$ .                                                          |  |  |

| 2.                                                                                                                           | C <sub>IN</sub> | Input coupling capacitor which blocks the DC voltage at the amplifier's input terminals. Also creates a                    |  |  |

|                                                                                                                              |                 | highpass filter with $R_{IN}$ at $f_c = 1/(2\pi R_{IN}C_{IN})$ . Refer to the section, <b>Proper Selection of External</b> |  |  |

|                                                                                                                              |                 | <b>Components</b> , for an explanation of how to determine the value of C <sub>IN</sub> .                                  |  |  |

| 3.                                                                                                                           | R <sub>f</sub>  | Feedback resistance which sets the closed-loop gain in conjunction with R <sub>IN</sub> .                                  |  |  |

| 4.                                                                                                                           | Cs              | Supply bypass capacitor which provides power supply filtering. Refer to the section, <b>Power Supply</b>                   |  |  |

|                                                                                                                              |                 | Bypassing, for information concerning proper placement and selection of the supply bypass capacitor,                       |  |  |

|                                                                                                                              |                 | C <sub>BYPASS</sub> .                                                                                                      |  |  |

| 5.                                                                                                                           | CBYPASS         | Bypass pin capacitor which provides half-supply filtering. Refer to the section, Proper Selection of External              |  |  |

|                                                                                                                              |                 | <b>Components</b> , for information concerning proper placement and selection of C <sub>BYPASS</sub> .                     |  |  |

www.national.com

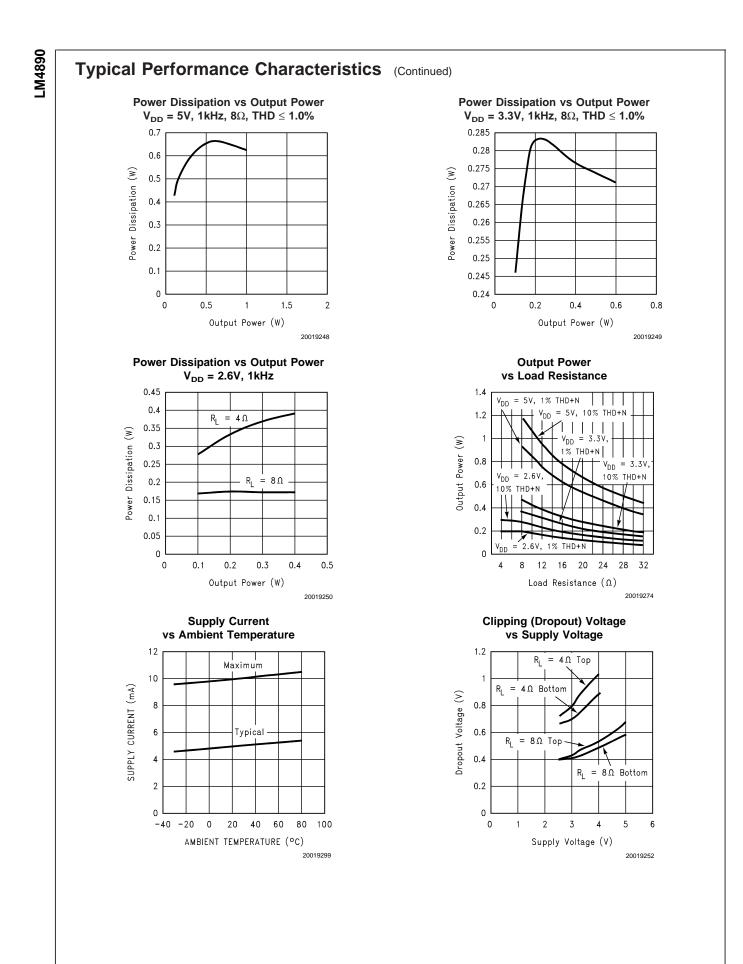

## Typical Performance Characteristics (Continued)

Ambient Temperature in Degrees C Note: ( $P_{DMAX}$  = 670mW for 5V, 8 $\Omega$ )

Note: ( $P_{DMAX} = 670$ mW for 5V, 8 $\Omega$ )

#### Power Derating - 8 bump µSMD (P<sub>DMAX</sub> = 670mW)

Ambient Temperature in Degrees C Note:  $(P_{DMAX} = 670 \text{mW} \text{ for 5V}, 8\Omega)$

Ambient Temperature in Degrees C Note: ( $P_{DMAX}$  = 670mW for 5V, 8 $\Omega$ )

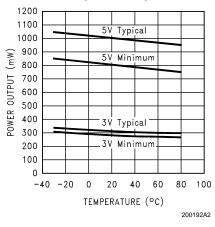

**Power Output vs Temperature**

www.national.com

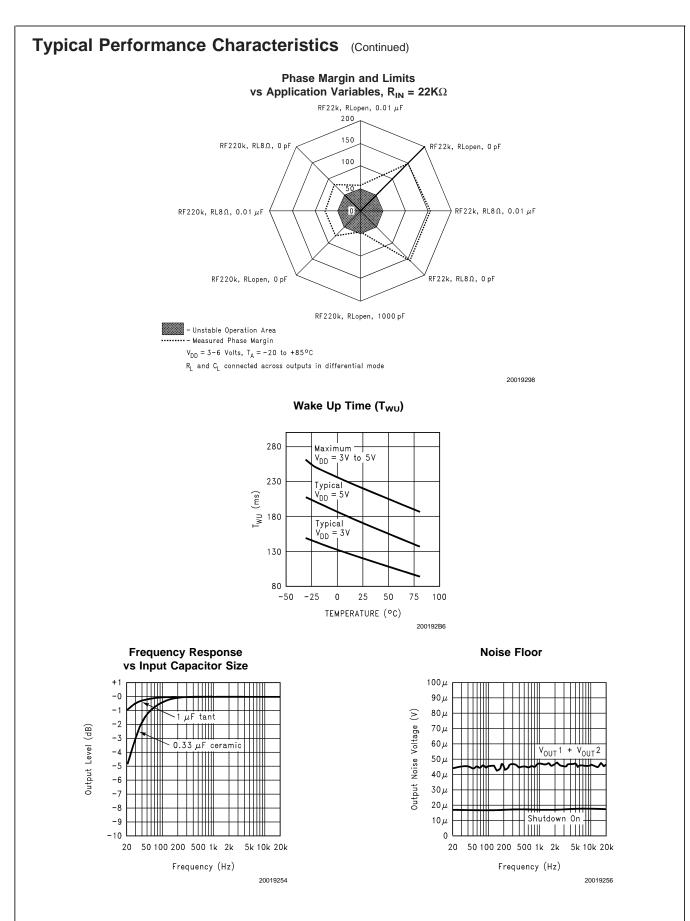

#### Typical Performance Characteristics (Continued) Max Die Temp Max Die Temp at P<sub>DMAX</sub> (9 bump microSMD) at P<sub>DMAX</sub> (8 bump microSMD) DIE TEMPERATURE @ 25°C AMBIENT (°C) 200 25°C AMBIENT (°C) 200 180 180 Maximum Die Temperature 160 160 Maximum Die Temperature - 150°C 150°C 140 140 @ 5V PDMAX P<sub>DMAX</sub>@5V P<sub>DMAX</sub> @ 3.6V P<sub>DMAX</sub> @ 3.6V 120 120 100 100 @ 4.2 PDMAX **TEMPERATURE** ( P<sub>DMAX</sub> @ 4.2V 80 80 60 60 40 40 P<sub>DMAX</sub> @ 3.3V P<sub>DMAX</sub> @ 3.3V 20 20 P<sub>DMAX</sub> @ 3V Р<sub>DMAX</sub> @ 3V Note 13 Note 13 Ы 0 0 100 150 200 250 100 150 200 250 0 50 300 0 50 300 PCB HEATSINK AREA $(mm^2)$ PCB HEATSINK AREA $(mm^2)$ 20019286 20019287 **Output Offset Voltage Supply Current** vs Shutdown Voltage 60 3.5 $V_{DD} = 5V$ 3 = 3.3V V<sub>DD</sub> Maximum 2.5 OFFSET VOLTAGE (mV) Supply Current (mA) $V_{DD} = 3V$ to 5V40 2 = 2.6V V<sub>DD</sub> 1.5 1 0.5 20 Typical 0 $V_{DD} = 3V$ to 5V -0.5 0 -1 -40 -20 100 0 20 40 60 80 0 0.5 1.5 2 2.5 1 3 TEMPERATURE (°C) Shutdown Voltage (V) 200192B7 20019253 Shutdown Hysterisis Voltage Shutdown Hysterisis Voltage $V_{DD} = 5V$ $V_{DD} = 3V$ 3 3 SUPPLY CURRENT (MA) Supply Current (mA) 2 2 ON OFF OFF ON 1 1 0 0 0 2 3 0 2 3 1 1 Shutdown Voltage (V) SHUTDOWN VOLTAGE (V) 20019279 20019280

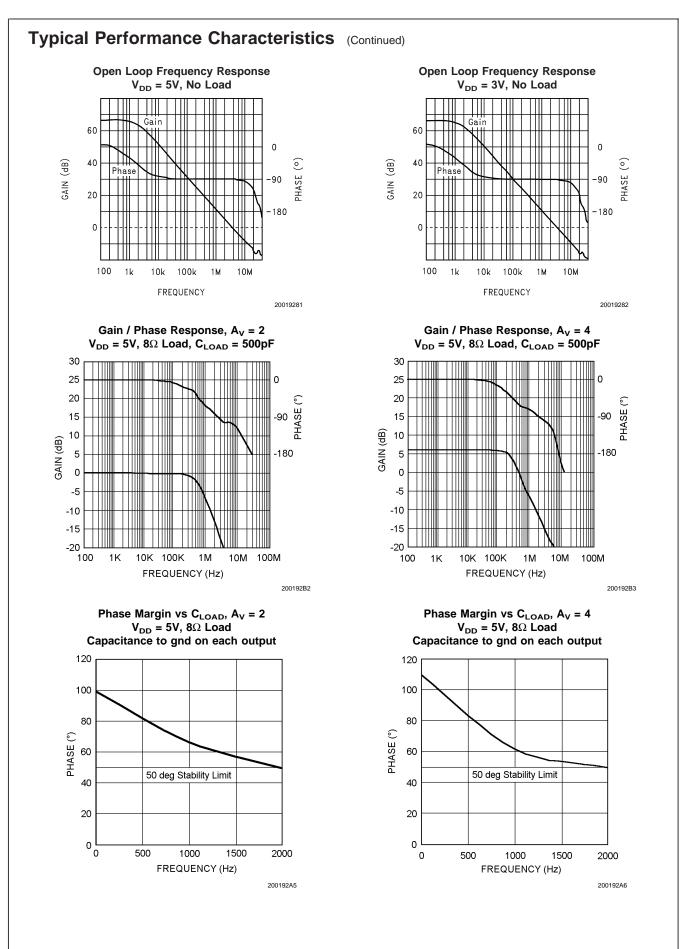

# **Application Information**

#### **BRIDGED CONFIGURATION EXPLANATION**

As shown in *Figure 1*, the LM4890 has two operational amplifiers internally, allowing for a few different amplifier configurations. The first amplifier's gain is externally configurable, while the second amplifier is internally fixed in a unity-gain, inverting configuration. The closed-loop gain of the first amplifier is set by selecting the ratio of R<sub>f</sub> to R<sub>IN</sub> while the second amplifier's gain is fixed by the two internal  $20k\Omega$  resistors. *Figure 1* shows that the output of amplifier one serves as the input to amplifier two which results in both amplifiers producing signals identical in magnitude, but out of phase by 180°. Consequently, the differential gain for the IC is

#### $A_{VD} = 2 (R_f/R_{IN})$

By driving the load differentially through outputs Vo1 and Vo2, an amplifier configuration commonly referred to as "bridged mode" is established. Bridged mode operation is different from the classical single-ended amplifier configuration where one side of the load is connected to ground.

A bridge amplifier design has a few distinct advantages over the single-ended configuration, as it provides differential drive to the load, thus doubling output swing for a specified supply voltage. Four times the output power is possible as compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or clipped. In order to choose an amplifier's closed-loop gain without causing excessive clipping, please refer to the **Audio Power Amplifier Design** section.

A bridge configuration, such as the one used in the LM4890, also creates a second advantage over single-ended amplifiers. Since the differential outputs, Vo1 and Vo2, are biased at half-supply, no net DC voltage exists across the load. This eliminates the need for an output coupling capacitor which is required in a single supply, single-ended amplifier configuration. Without an output coupling capacitor, the half-supply bias across the load would result in both increased internal IC power dissipation and also possible loudspeaker damage.

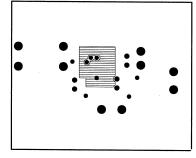

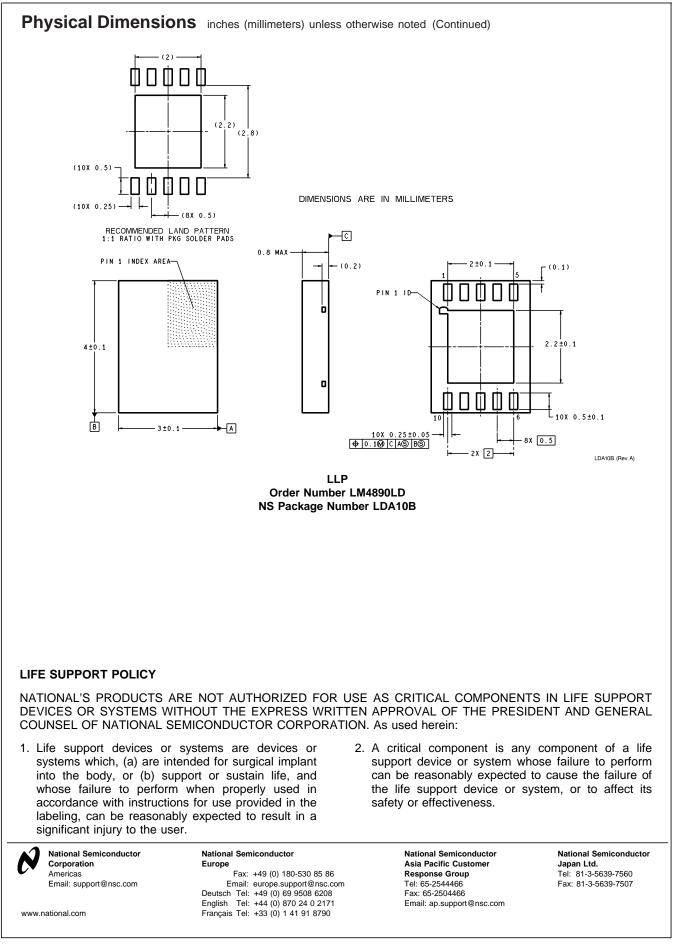

#### EXPOSED-DAP PACKAGE PCB MOUNTING CONSIDERATIONS FOR THE LM4890LD

The LM4890LD's exposed-DAP (die attach paddle) package (LD) provides a low thermal resistance between the die and the PCB to which the part is mounted and soldered. The LM4890LD package should have its DAP soldered to the grounded copper pad (heatsink) under the LM4890LD (the NC pins, no connect, and ground pins should also be directly connected to this copper pad-heatsink area). The area of the copper pad (heatsink) can be determined from the LD Power Derating graph. If the multiple layer copper heatsink areas are used, then these inner layer or backside copper heatsink areas should be connected to each other with 4 (2 x 2) vias. The diameter for these vias should be between 0.013 inches and 0.02 inches with a 0.050inch pitch-spacing. Ensure efficient thermal conductivity by plating through and solderfilling the vias. Further detailed information concerning PCB layout, fabrication, and mounting an LLP package is available from National Semiconductor's Package Engineering Group under application note AN1187.

#### POWER DISSIPATION

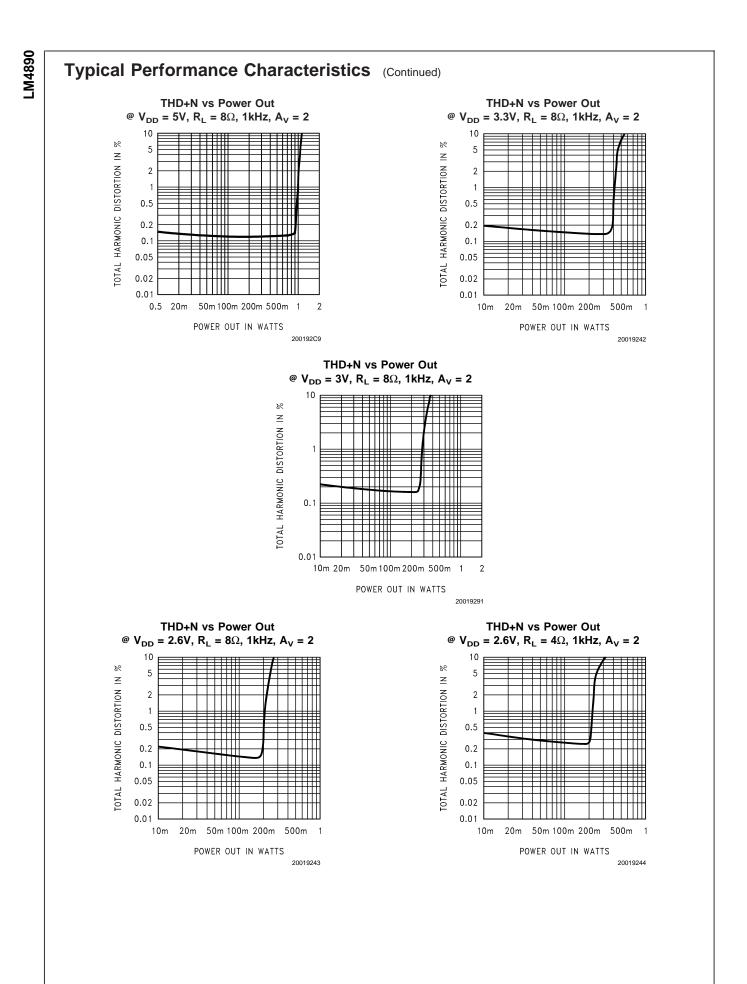

Power dissipation is a major concern when designing a successful amplifier, whether the amplifier is bridged or single-ended. A direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation. Since the LM4890 has two operational amplifiers in one package, the maximum internal power dissipation is 4 times that of a single-ended amplifier. The maximum power dissipation for a given application can be derived from the power dissipation graphs or from Equation 1.

$$P_{DMAX} = 4^{*}(V_{DD})^{2}/(2\pi^{2}R_{L})$$

(1)

It is critical that the maximum junction temperature  $T_{JMAX}$  of 150°C is not exceeded.  $T_{JMAX}$  can be determined from the power derating curves by using  $P_{DMAX}$  and the PC board foil area. By adding additional copper foil, the thermal resistance of the application can be reduced, resulting in higher  $P_{DMAX}$ . Additional copper foil can be added to any of the leads connected to the LM4890. Refer to the **APPLICATION IN-FORMATION** on the LM4890 reference design board for an example of good heat sinking. If  $T_{JMAX}$  still exceeds 150°C, then additional changes must be made. These changes can include reduced supply voltage, higher load impedance, or reduced ambient temperature. Internal power dissipation is a function of output power. Refer to the **Typical Performance Characteristics** curves for power dissipation information for different output powers and output loading.

#### POWER SUPPLY BYPASSING

As with any amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. The capacitor location on both the bypass and power supply pins should be as close to the device as possible. Typical applications employ a 5V regulator with 10  $\mu$ F tantalum or electrolytic capacitor and a ceramic bypass capacitor which aid in supply stability. This does not eliminate the need for bypassing the supply nodes of the LM4890. The selection of a bypass capacitor, especially C<sub>BYPASS</sub>, is dependent upon PSRR requirements, click and pop performance (as explained in the section, **Proper Selection of External Components**), system cost, and size constraints.

#### SHUTDOWN FUNCTION

In order to reduce power consumption while not in use, the LM4890 contains a shutdown pin to externally turn off the amplifier's bias circuitry. This shutdown feature turns the amplifier off when a logic low is placed on the shutdown pin. By switching the shutdown pin to ground, the LM4890 supply current draw will be minimized in idle mode. While the device will be disabled with shutdown pin voltages less than  $0.5V_{DC}$ , the idle current may be greater than the typical value of  $0.1\mu$ A. (Idle current is measured with the shutdown pin grounded).

In many applications, a microcontroller or microprocessor output is used to control the shutdown circuitry to provide a quick, smooth transition into shutdown. Another solution is to use a single-pole, single-throw switch in conjunction with an external pull-up resistor. When the switch is closed, the shutdown pin is connected to ground and disables the amplifier. If the switch is open, then the external pull-up resistor will enable the LM4890. This scheme guarantees that the shutdown pin will not float thus preventing unwanted state changes.

#### Application Information (Continued)

#### SHUTDOWN OUTPUT IMPEDANCE

For  $R_f = 20k$  ohms:

$Z_{OUT1}$  (between Out1 and GND) = 10k||50k||R\_f =  $6k\Omega$

$Z_{OUT2}$  (between Out2 and GND) = 10k||(40k+(10k||R\_{\rm f})) = 8.3k\Omega

$Z_{\text{OUT1-2}}$  (between Out1 and Out2) = 40k||(10k+(10k||R\_{\text{f}})) = 11.7k $\Omega$

The -3dB roll off for these measurements is 600kz

#### PROPER SELECTION OF EXTERNAL COMPONENTS

Proper selection of external components in applications using integrated power amplifiers is critical to optimize device and system performance. While the LM4890 is tolerant of external component combinations, consideration to component values must be used to maximize overall system quality.

The LM4890 is unity-gain stable which gives the designer maximum system flexibility. The LM4890 should be used in low gain configurations to minimize THD+N values, and maximize the signal to noise ratio. Low gain configurations require large input signals to obtain a given output power. Input signals equal to or greater than 1Vrms are available from sources such as audio codecs. Please refer to the section, **Audio Power Amplifier Design**, for a more complete explanation of proper gain selection.

Besides gain, one of the major considerations is the closed-loop bandwidth of the amplifier. To a large extent, the bandwidth is dictated by the choice of external components shown in *Figure 1*. The input coupling capacitor,  $C_{\rm IN}$ , forms a first order high pass filter which limits low frequency response. This value should be chosen based on needed frequency response for a few distinct reasons.

#### Selection Of Input Capacitor Size

Large input capacitors are both expensive and space hungry for portable designs. Clearly, a certain sized capacitor is needed to couple in low frequencies without severe attenuation. But in many cases the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 100Hz to 150Hz. Thus, using a large input capacitor may not increase actual system performance.

In addition to system cost and size, click and pop performance is effected by the size of the input coupling capacitor,  $C_{\rm IN}$ . A larger input coupling capacitor requires more charge to reach its quiescent DC voltage (nominally  $1/2~V_{\rm DD}$ ). This charge comes from the output via the feedback and is apt to create pops upon device enable. Thus, by minimizing the capacitor size based on necessary low frequency response, turn-on pops can be minimized.

Besides minimizing the input capacitor size, careful consideration should be paid to the bypass capacitor value. Bypass capacitor,  $C_{BYPASS}$ , is the most critical component to minimize turn-on pops since it determines how fast the LM4890 turns on. The slower the LM4890's outputs ramp to their quiescent DC voltage (nominally  $1/2V_{DD}$ ), the smaller the turn-on pop. Choosing  $C_{BYPASS}$  equal to  $1.0\mu$ F along with a small value of  $C_{IN}$ , (in the range of  $0.1\mu$ F to  $0.39\mu$ F), should

produce a virtually clickless and popless shutdown function. While the device will function properly, (no oscillations or motorboating), with C<sub>BYPASS</sub> equal to 0.1µF, the device will be much more susceptible to turn-on clicks and pops. Thus, a value of C<sub>BYPASS</sub> equal to 1.0µF is recommended in all but the most cost sensitive designs.

#### AUDIO POWER AMPLIFIER DESIGN

#### A 1W/8Ω AUDIO AMPLIFIER

Given:

| Power Output    | 1 Wrms                  |

|-----------------|-------------------------|

| Load Impedance  | 8Ω                      |

| Input Level     | 1 Vrms                  |

| Input Impedance | 20 kΩ                   |

| Bandwidth       | 100 Hz–20 kHz ± 0.25 dB |

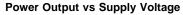

A designer must first determine the minimum supply rail to obtain the specified output power. By extrapolating from the Output Power vs Supply Voltage graphs in the **Typical Performance Characteristics** section, the supply rail can be easily found. A second way to determine the minimum supply rail is to calculate the required  $V_{opeak}$  using Equation 2 and add the output voltage. Using this method, the minimum supply voltage would be ( $V_{opeak} + (V_{OD_{TOP}} + V_{OD_{BOT}})$ ), where  $V_{OD_{BOT}}$  and  $V_{OD_{TOP}}$  are extrapolated from the Dropout Voltage vs Supply Voltage curve in the **Typical Performance Characteristics** section.

$$V_{\text{opeak}} = \sqrt{(2R_{\text{L}}P_{\text{O}})}$$

5V is a standard voltage which in most applications is chosen for the supply rail. Extra supply voltage creates headroom that allows the LM4890 to reproduce peaks in excess of 1W without producing audible distortion. At this time, the designer must make sure that the power supply choice along with the output impedance does not violate the conditions explained in the **Power Dissipation** section.

Once the power dissipation equations have been addressed, the required differential gain can be determined from Equation 3.

$$A_{VD} \ge \sqrt{(P_0 R_L)} / (V_{IN}) = V_{orms} / V_{inrms}$$

(3)

$$R_f/R_{IN} = A_{VD}/2$$

From Equation 3, the minimum  $A_{VD}$  is 2.83; use  $A_{VD}$  = 3.

Since the desired input impedance is 20 kΩ, and with an A<sub>VD</sub> gain of 3, a ratio of 1.5:1 of R<sub>f</sub> to R<sub>IN</sub> results in an allocation of R<sub>IN</sub> = 20 kΩ and R<sub>f</sub> = 30 kΩ. The final design step is to address the bandwidth requirements which must be stated as a pair of -3 dB frequency points. Five times away from a -3 dB point is 0.17 dB down from passband response which is better than the required ±0.25 dB specified.

$f_{L} = 100Hz/5 = 20Hz$

$$f_{H} = 20kHz * 5 = 100kHz$$

(2)

# Application Information (Continued)

As stated in the **External Components** section,  ${\sf R}_{\sf IN}$  in conjunction with  ${\sf C}_{\sf IN}$  create a highpass filter.

$C_{\text{IN}} \geq$  1/(2 $\pi^{*}20~k\Omega^{*}20\text{Hz})$  = 0.397 $\mu\text{F};$  use 0.39 $\mu\text{F}$

The high frequency pole is determined by the product of the desired frequency pole,  $f_{\rm H},$  and the differential gain,  $A_{\rm VD}.$

With a  $A_{VD}$  = 3 and  $f_{H}$  = 100kHz, the resulting GBWP = 300kHz which is much smaller than the LM4890 GBWP of 2.5MHz. This calculation shows that if a designer has a need to design an amplifier with a higher differential gain, the LM4890 can still be used without running into bandwidth limitations.

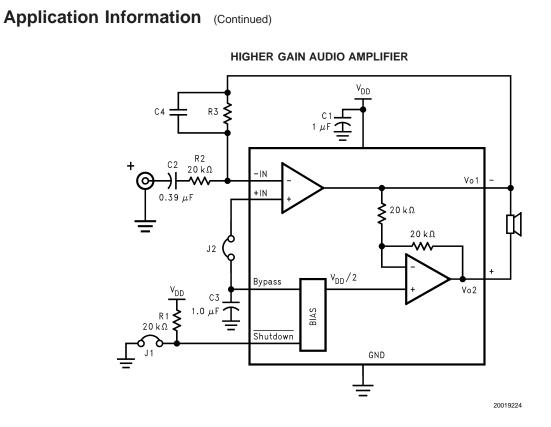

The LM4890 is unity-gain stable and requires no external components besides gain-setting resistors, an input coupling capacitor, and proper supply bypassing in the typical application. However, if a closed-loop differential gain of greater than 10 is required, a feedback capacitor (C4) may be needed as shown in **Figure 2** to bandwidth limit the amplifier. This feedback capacitor creates a low pass filter that elimi-

nates possible high frequency oscillations. Care should be taken when calculating the -3dB frequency in that an incorrect combination of R<sub>3</sub> and C<sub>4</sub> will cause rolloff before 20kHz. A typical combination of feedback resistor and capacitor that will not produce audio band high frequency rolloff is R<sub>3</sub> = 20k $\Omega$  and C<sub>4</sub> = 25pf. These components result in a -3dB point of approximately 320 kHz.

# Application Information (Continued)

FIGURE 3.

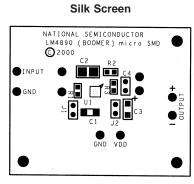

#### Application Information (Continued) **REFERENCE DESIGN BOARD and LAYOUT - micro SMD** $V_{DD}$ R3 C4\* C 1 20 kΩ 1 μF 🕇 C2 20 kΩ + -IN 카 Vo 1 0 7 +|N 0.39 μF 8 20 kΩ 20 kΩ $\sim$ J2 $V_{\rm DD}/2$ Bypass 3 4 Vo2 V<sub>DD</sub> С3 1.0 µF BIAS 20 kΩ Shutdown GND 2 \* not stuffed \_ 20019225

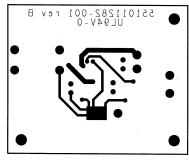

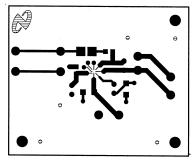

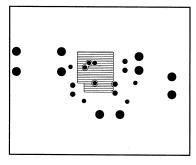

# Application Information (Continued) LM4890 micro SMD BOARD ARTWORK

20019257

20019259

Inner Layer Ground

20019261

Top Layer

20019258

20019260

#### Application Information (Continued) REFERENCE DESIGN BOARD and PCB LAYOUT GUIDELINES - MSOP & SO Boards $V_{DD}$ R3 C4\* C 1 20 kΩ 1 μF **T** C2 R2 20 kΩ + -IN 카 ~~~~ Vo1 0 3 +|N 0.39 μF 5 20 kΩ 20 kΩ $\sim$ J2 $V_{\rm DD}/2$ Bypass 2 8 Vo2 ′<sub>DD</sub> С3 1.0 µF BIAS 20 kΩ Shutdown GND 7 \* not stuffed 20019268

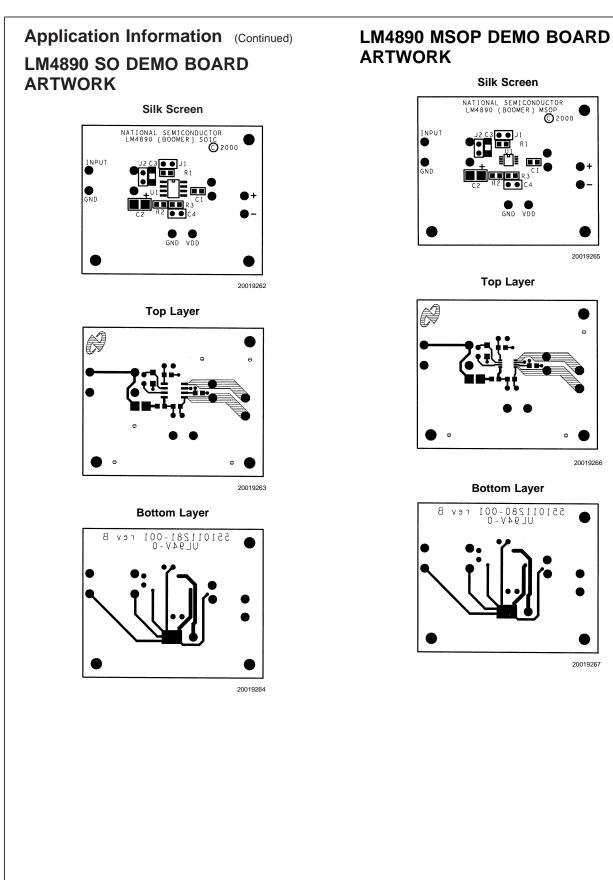

## Application Information (Continued)

#### Mono LM4890 Reference Design Boards Bill of Material for all 3 Demo Boards

| Item | Part Number   | Part Description                       | Qty | Ref Designator |

|------|---------------|----------------------------------------|-----|----------------|

| 1    | 551011208-001 | LM4890 Mono Reference Design Board     | 1   |                |

| 10   | 482911183-001 | LM4890 Audio AMP                       | 1   | U1             |

| 20   | 151911207-001 | Tant Cap 1uF 16V 10                    | 1   | C1             |

| 21   | 151911207-002 | Cer Cap 0.39uF 50V Z5U 20% 1210        | 1   | C2             |

| 25   | 152911207-001 | Tant Cap 1uF 16V 10                    | 1   | C3             |

| 30   | 472911207-001 | Res 20K Ohm 1/10W 5                    | 3   | R1, R2, R3     |

| 35   | 210007039-002 | Jumper Header Vertical Mount 2X1 0.100 | 2   | J1, J2         |

#### PCB LAYOUT GUIDELINES

This section provides practical guidelines for mixed signal PCB layout that involves various digital/analog power and ground traces. Designers should note that these are only 'rule-of-thumb' recommendations and the actual results will depend heavily on the final layout.

# GENERAL MIXED SIGNAL LAYOUT RECOMMENDATIONS

#### **Power and Ground Circuits**

For 2 layer mixed signal design, it is important to isolate the digital power and ground trace paths from the analog power and ground trace paths. Star trace routing techniques (bringing individual traces back to a central point rather than daisy chaining traces together in a serial manner) can have a major impact on low level signal performance. Star trace routing refers to using individual traces to feed power and ground to each circuit or even device. This technique will require a greater amount of design time but will not increase the final price of the board. The only extra parts required will be some jumpers.

#### **Single-Point Power / Ground Connections**

The analog power traces should be connected to the digital traces through a single point (link). A 'Pi-filter' can be helpful in minimizing High Frequency noise coupling between the analog and digital sections. It is further recommended to put digital and analog power traces over the corresponding digital and analog ground traces to minimize noise coupling.

#### **Placement of Digital and Analog Components**

All digital components and high-speed digital signals traces should be located as far away as possible from analog components and circuit traces.

#### Avoiding Typical Design / Layout Problems

Avoid ground loops or running digital and analog traces parallel to each other (side-by-side) on the same PCB layer. When traces must cross over each other do it at 90 degrees. Running digital and analog traces at 90 degrees to each other from the top to the bottom side as much as possible will minimize capacitive noise coupling and cross talk.

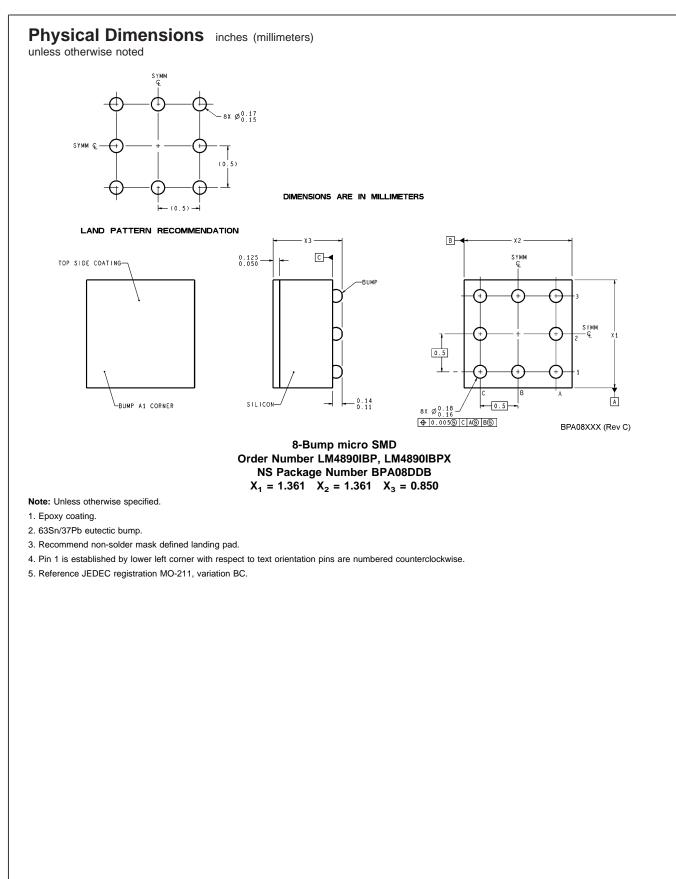

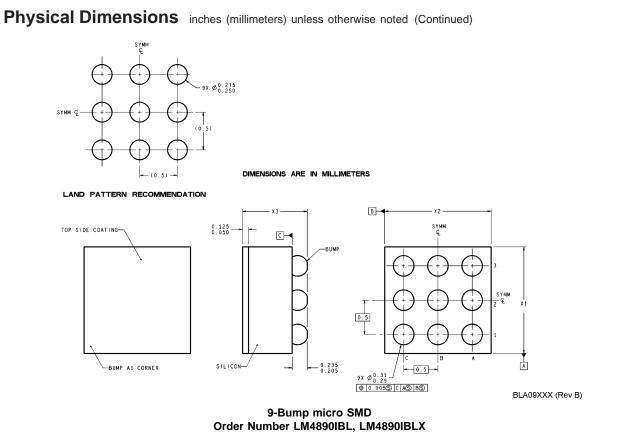

NS Package Number BLA09AAB  $X_1 = 1.514$   $X_2 = 1.514$   $X_3 = 0.945$

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.