#### ■ 6249827 0015336 T62 ■ MIT3 MITSUBISHI BIPOLAR DIGITAL ICs 查询M54956P供应商 MITSUBISHI (DGTL LOGIC) 並多邦,专业PCB打样工「MS型956P

### PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS

## DESCRIPTION

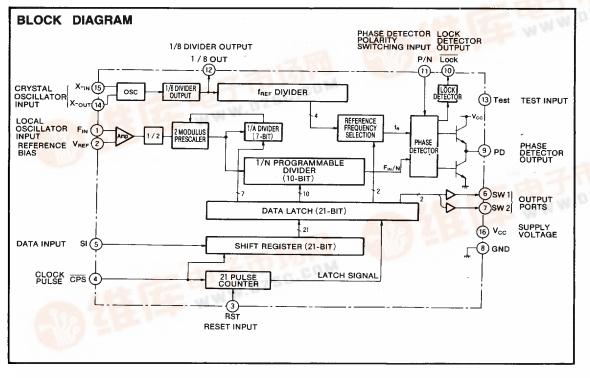

The M54956P is a single-chip semiconductor integrated circuit consisting of a PLL frequency synthesizer for personal radio.

### FEATURES

- Built-in 1/256 and 1/258 modulus prescaler (fmax=1.0GHz)

- Low power dissipation (I<sub>cc</sub>=40mA, at V<sub>cc</sub>=5 V)

- Choice of four comparator frequency types (50k, 25k, 12. 5k, 6. 25k)

- Wide variety of division ratio (32768~262142, binary code)

- 1/8 Clock pulse output for reference oscillator frequency (TTL level)

- Output display for PLL lock/unlock

- Output port status can be set by date transferred from the controller

- Serial data input (three data transfer lines)

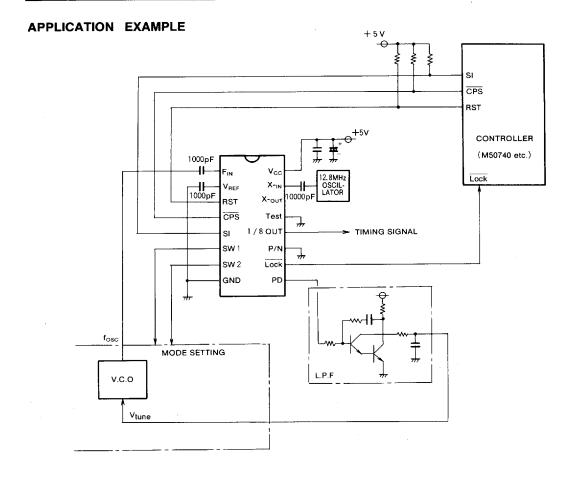

#### APPLICATION

Personal radios, mobile radio telephones, MCA equipment

63E

🖿 6249827 0015337 9T9 🎟 MIT3 MITSUBISHI BIPOLAR DIGITAL ICs

M54956P

## MITSUBISHI (DGTL LOGIC)

## PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS

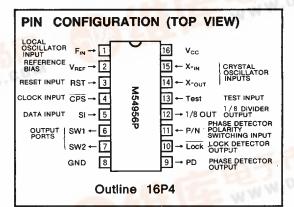

### **PIN DESCRIPTION**

| Pin no. | Symbol           | Pin name                          | Description                                                                                                                                                              |

|---------|------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Fin              | Local oscillator input            | Local oscillator frequency (V.C.O) input. fmax=1000MHz                                                                                                                   |

| 2       | VREF             | Reference blas                    | Connbct to ground through a 1000pF capacitor                                                                                                                             |

| 3       | RST              | Reset input                       | Reset input of 21-pulse counter                                                                                                                                          |

| 4       | CPS              | Clock input                       | Clock input for shift register                                                                                                                                           |

| 5       | SI               | Data input                        | Data input pin for shift register                                                                                                                                        |

| 6       | SW1              |                                   |                                                                                                                                                                          |

| 7       | SW2              | Output port                       | Open-collector output port can be set by data tranferred from the controller.                                                                                            |

| 8       | GND              | Ground                            | 0 V                                                                                                                                                                      |

| 9       | PD               | Phase detector output             | Three-state                                                                                                                                                              |

| 10      | Lock             | Lock detector output              | Low when the PLL is locked, high when unlocked. Open collector.                                                                                                          |

| 11      | P/N              | Phase detector polarity switching | When P/N is high, the output at PD pin becomes high when the phase is advanced and low when the phase is retarded. When P/N is low, the logic states are inverted.       |

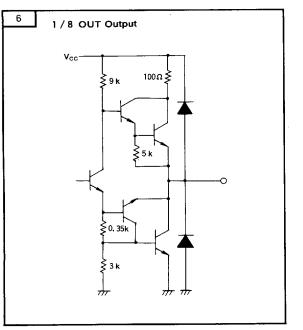

| 12      | 1/80UT           | 1/8 divider output                | TTL level                                                                                                                                                                |

| 13      | Test             | Test input                        | Normally set low. When set high, $f_{\rm H}$ (the comparator frequency) is output at SW1 (pin 6) and the $f_{\rm IN}/N$ (programmable divider) is output at SW2 (pin 7). |

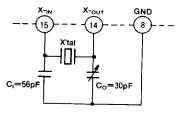

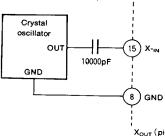

| 14      | Х-олт            |                                   | The output from 12.8MHz reference oscillator is supplied to X-IN.                                                                                                        |

| 15      | Х- <sub>IN</sub> | Crystal oscillator input          | Oscillation is generated by an externally connected crystal oscillator.                                                                                                  |

| 16      | Vcc              | Supply voltage pin                | 4.5~5.5V                                                                                                                                                                 |

## **FUNCTION**

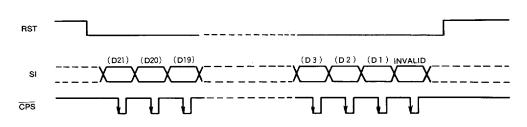

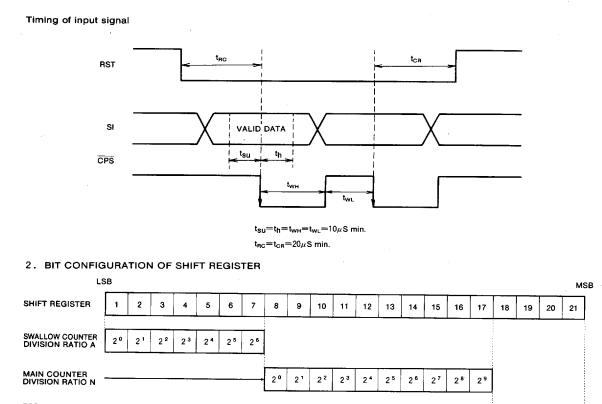

#### 1. DATA INPUT

Configuration of input signal

Note 1 : The status of input SI is read by the shift register at the failing edge of the clock signal at CPS. 2 : All data (N value, port, comparator frequency) are set at the failing edge of the 21st pulse at CPS.Subsequent clock pulse at CPS are ignored.

3 : Pulses are accepted at neither CPS nor SI while RST is high.

63E

# 🖿 6249827 0015338 835 MIT3 MITSUBISHI BIPOLAR DIGITAL ICs

## MITSUBISHI (DGTL LOGIC)

# M54956P

#### PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS

PORT SETTING REFERENCE FREQUENCY SELECTION

Note 4 : Total division ratio M is given by  $M = 2 \times (A + 128N)$ . 5 : Comparator frequency is selected by D<sub>A</sub> and D<sub>B</sub>.

| oquonoy | is sciected by Dr                    |

|---------|--------------------------------------|

| ata     | Reference                            |

| De      | frequency                            |

| L       | 50k                                  |

| L       | 25k                                  |

| н       | 12. 5k                               |

| н       | 6.25k                                |

|         | ata<br>D <sub>B</sub><br>L<br>L<br>H |

| Note | 6 | : | Output port is set by D <sub>c</sub> and D <sub>p</sub> . |  |

|------|---|---|-----------------------------------------------------------|--|

| Ante | Q | • | Output port is set by D <sub>C</sub> and D <sub>D</sub> . |  |

| De | ita | Outp | ut port |  |  |

|----|-----|------|---------|--|--|

| Dc | DD  | SW1  | SW2     |  |  |

| L  | L   | L    | L       |  |  |

| н  | L   | н    | L       |  |  |

| L  | н   | L    | н       |  |  |

| н  | н   | н    | н       |  |  |

D, DB  $\mathbf{D}_{\mathsf{C}}$  $D_D$

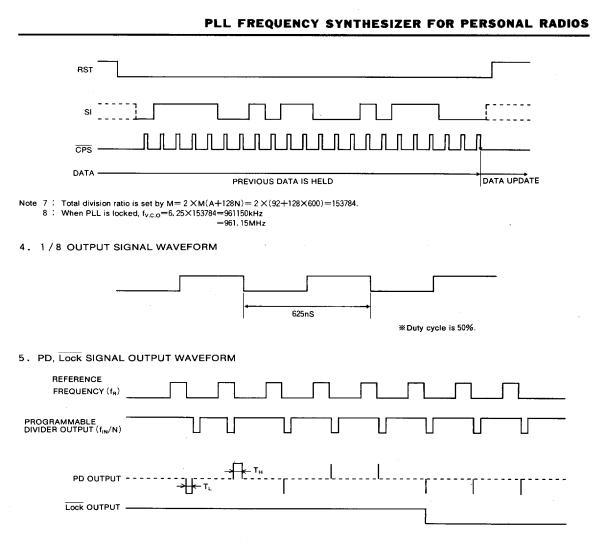

#### 3. DATA CODING EXAMPLE

When reference frequency is 6. 25kHz, M is 153784, SW1 is high and SW2 is low.

|                | LSE | 3  |      |      |                          |    |   |   |        |    |    |                 |    |    |    |      |    |                                        |              |              |    |                   |

|----------------|-----|----|------|------|--------------------------|----|---|---|--------|----|----|-----------------|----|----|----|------|----|----------------------------------------|--------------|--------------|----|-------------------|

| SHIFT REGISTER | 1   | 2  | 3    | 4    | 5                        | 6  | 7 | 8 | 9      | 10 | 11 | 12              | 13 | 14 | 15 | 16   | 17 | 18                                     | 19           | 20           | 21 | ]                 |

| DATA           | L   | L  | н    | н    | н                        | L  | н | L | L      | L  | н  | н               | L  | н  | L  | L    | н  | н                                      | н            | н            | L  | 1                 |

|                | C   | S١ | VALL | ow c | ETTIN<br>DUNTI<br>⁴+ 2 ⁵ | ER | 8 |   | DIVISI |    |    | ETTIN<br>+ 2 ⁴+ |    |    |    | JNTE | 3  | REFER<br>FREQI<br>6.254<br>is<br>selec | UENCY<br>(Hz | SW1<br>SET H |    | SW2 IS<br>SET LOW |

## MITSUBISHI BIPOLAR DIGITAL ICs

# 🔲 6249827 OO15339 771 🎟 MIT3

# M54956P

MITSUBISHI (DGTL LOGIC)

Note 9: The PD output is low when the phase of the programmable divider output (f<sub>IN</sub>/N) follows the phase of reference frequency (f<sub>R</sub>) and is high when the phase f<sub>IN</sub>/N leads that of f<sub>R</sub>.

10 Broken lines indicate the high-impedance state.

11 : When phase variance  $T_L$  and  $T_H$  are less than 625ns for a period of rerence frequency ( $f_R$ ), the lock output becomes low.

The above description applies while P/N (pin 11) is high.

While P/N input is low, the logic state of the PD output is inverted.

## MITSUBISHI BIPOLAR DIGITAL ICs

# 🖿 6249827 0015340 493 🎟 MIT3

MITSUBISHI (DGTL LOGIC)

M54956P

### PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS

# 1 2 RST, CPS, SI, P/N, Test Inputs PD Output $v_{cc}$ 80,µA O ₹8ĸ 500 Ω $\bigcirc$ $\sim$ **≩** 30k ≨ 200Ω 3 О FIN, VREF Inputs Vcc ₹200Ω 0 250Ω≹ **⊲**∨ bias 250Ω≹ 4 5 SW1, SW2, Lock Outputs **OSC Circuit** V<sub>cc</sub>-≩12k $v_{cc}$ 1 k M $\cap$ X-OUT () 1 k X-IN () ~~~ ≩ 14k ᅏ

## **I/O CIRCUIT DIAGRAM**

# L3E L249827 0015341 32T ■MIT3 MITSUBISHI BIPOLAR DIGITAL ICs MITSUBISHI (DGTL L0GIC) M54956P

# PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS

Note 12: Resistance and current are typical values when  $V_{cc} = 5 V$  and  $T_a = -20 \sim +75$ °C.

## **ABSOLUTE MAXIMUM RATINGS** ( $T_a = -20 \sim +75$ °C, unless otherwise noted)

٠

|        |                       |                     | Rati | Ratings |      |  |  |

|--------|-----------------------|---------------------|------|---------|------|--|--|

| Symbol | Parameter             | Conditions          | Min  | Max     | Unit |  |  |

| Vcc    | Supply voltage        |                     | -0.5 | 6.0     | v    |  |  |

| V      | Input voltage         | Each input          | -0.5 | 6.0     | V    |  |  |

| Vo     | Output voltage        | Each input          | -0.5 | 6.0     | V    |  |  |

| Pd     | Power dissipation     | T <sub>a</sub> =75℃ |      | 500     | m٧   |  |  |

| Topr   | Operating temperature |                     | -20  | +75     | °C   |  |  |

| Tstg   | Storage temperature   |                     | -40  | +125    | °C   |  |  |

#### **RECOMMENDED OPERATING CONDITIONS** ( $v_{cc} = 4.5 \sim 5.5v$ , $T_a = -20 \sim +75$ <sup>°</sup>C unless otherwise noted)

|                   |                                 |                                       |     | Limits | Unit | Remark            |           |

|-------------------|---------------------------------|---------------------------------------|-----|--------|------|-------------------|-----------|

| Symbol            | Parameter                       | Conditions                            | Min | Тур    | Max  | Unit              | Remark    |

| Vcc               | Supply voltage                  |                                       | 4.5 | 5      | 5.5  | v                 |           |

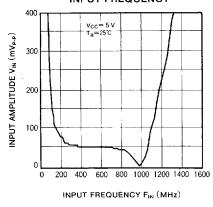

| VIN               | Input amplitude                 | F <sub>IN</sub> =100~1000MHz          | 400 |        | 1200 | mV <sub>P⁻P</sub> |           |

| F <sub>IN1</sub>  | Input frequency                 | V <sub>IN</sub> =400mV <sub>P-P</sub> | 100 |        | 1000 | MHz               |           |

| IOL               | Low-level output current        | SW1, SW2, Lock output                 |     |        | 5    | mА                |           |

| V <sub>X-IN</sub> | X-IN input amplitude            | Note 14                               | 1   |        | 2    | V <sub>P-P</sub>  | Sine wave |

| fosc              | Reference oscillation frequency | Note 13, Note 14                      |     | 12.8   |      | MHz               |           |

# E 🖬 6249827 0015342 266 MIT3 MITSUBISHI BIPOLAR DIGITAL ICs

# MITSUBISHI (DGTL LOGIC)

# M54956P

## PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS

Note 13: Connection of crystal vibrator

Load capacitance of crystal oscillator Valid resistance  $100\,\Omega$  or less

Note 14 : Connection of crystal oscillator

X<sub>OUT</sub> (pin 14) should be left open.

## **ELECTRICAL** CHARACTERISTICS ( $\tau_a = -20 \sim +75$ °C, unless otherwise noted)

| Symbol          | Parameter                    |                 | Test conditions                                 |     |     |           |            |  |

|-----------------|------------------------------|-----------------|-------------------------------------------------|-----|-----|-----------|------------|--|

| V               |                              | Test pin        | rest conditions                                 | Min | Тур | Max       | Unit       |  |

| VIH             | High-level input voltage     | 3, 4, 5, 11, 13 | V <sub>cc</sub> =5.5V                           | 2.0 |     |           | v          |  |

| VIL             | Low-level input voltage      | 3, 4, 5, 11, 13 | V <sub>cc</sub> =5.5V                           |     |     | 0.6       | <br>v      |  |

| Ьн              | High-level input current     | 3, 4, 5, 11, 13 | V <sub>cc</sub> =5.5V, V <sub>IH</sub> =5.5V    |     |     | 30        | μA         |  |

| I <sub>IL</sub> | Low-level input current      | 3, 4, 5, 11, 13 | $V_{cc}=4.5V, V_{IL}=0V$                        |     |     | -160      | μΑ         |  |

| Vol             | Low-level output current     | 6, 7, 10, 12    | $V_{cc}=4.5V, I_{OL}=5 mA$                      |     |     | 0.5       | V          |  |

| VOHP1           | PD high-level output voltage | 9               | V <sub>CC</sub> =4.5V, I <sub>OH</sub> =-1 mA   | 3.0 |     | 0.0       | v          |  |

| VOHP2           | PD low-level output voltage  | 9               | $V_{cc} = 5 V, I_{OH} = -0.1 mA$                | 4.0 |     |           | v          |  |

| VOLPI           | PD low-level output current  | 9               | $V_{CC} = 4.5V, I_{OL} = 1 \text{ mA}$          |     |     | 1.5       |            |  |

| VOLP2           | PD low-level output current  | 9               | $V_{CC} = 5 V, I_{OL} = 0.1 mA$                 |     |     | 1.0       | v          |  |

| PD1             | PD leak current              | 9               | V <sub>cc</sub> =5.5V, V <sub>o</sub> =0.8~4.7V |     |     | ±1.0      | ųА         |  |

| IPD2            | PD leak current              | 9               | $V_{cc} = 5V, V_0 = 2.5V$                       |     |     | $\pm 100$ | <u>μ</u> Α |  |

| lcc             | Supply voltage               | 16              | Vcc=5.5V                                        |     | 40  | 60        | mA         |  |

| OLK             | Output leak current          | 6, 7, 10        | V <sub>CC</sub> =5.5V, V <sub>DH</sub> =5.5V    |     |     | 30        | A          |  |

| V <sub>oн</sub> | High-level output voltage    | 12              | V <sub>CC</sub> =4.5V, I <sub>DH</sub> =-1V     | 2.0 |     |           | <u>µ</u> A |  |

Note 15 : The GND pin (pin 8) for voltages in this circuit is based on the reference voltage (0)

16: What the currents flowing into the circuit are positive (no sings) and the currents flowing out from the circuit are negative (negative sign) and the minimum and maximum are shown in absolute values.

17 : Typical values are at V<sub>cc</sub>= 5 V, and T<sub>a</sub>=25  $^\circ$ C

# L3E L249827 0015343 172 MITSUBISHI BIPOLAR DIGITAL ICs MITSUBISHI (DGTL L0GIC) M54956P

## PLL FREQUENCY SYNTHESIZER FOR PERSONAL RADIOS