### Features

- **BELL 202 FSK demodulation**

- Ring detection input and output

- Carrier detection output

- Low battery detection input and output

#### Applications

- Feature phones

- Adjunct boxes

- Power down mode

- High input sensitivity

- 3.58MHz crystal or ceramic resonator

Fax and answering machines

Computer interface products

### **General Description**

The HT9030 calling line identification receiver is a low power CMOS integrated circuit designed for receiving physical layer signals transmitted according to Bellcore TR-NWT-000030 specifications. The primary application for this device is in products that are to be used to receive and display the calling number, or

message waiting indicator sent to subscribers from central office facilities. The device also provides a low battery detection circuit, a power down circuit, a carrier detection circuit and a ring detection circuit for easier system applications.

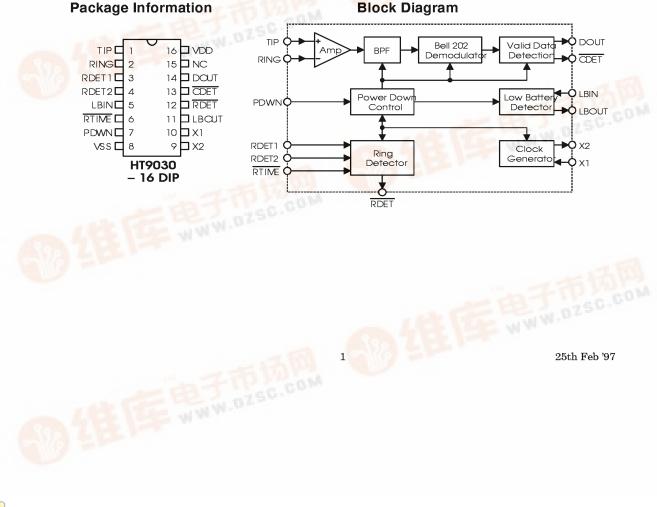

### **Block Diagram**

# **Pin Description**

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                                                                                                  |

|---------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | TIP      | Ι   | This input pin is connected to the tip side of the twisted pair wires. It is internally biased to $1/2$ VDD when the device is in power up mode. This pin must be DC isolated from the line.                                                                                 |

| 2       | RING     | Ι   | This input pin is connected to the ring side of the twisted pair wires.<br>It is internally biased to 1/2 VDD when the device is in power up<br>mode.This pin must be DC isolated from the line.                                                                             |

| 3       | RDET1    | Ι   | It detects ring energy on the line through an attenuating network and enables the oscillator and ring detection.                                                                                                                                                             |

| 4       | RDET2    | Ι   | It couples ring signal to the precision ring detector through an attenuating network. $\overline{\text{RDET}}$ ="0" if a valid ring signal is detected.                                                                                                                      |

| 5       | LBIN     | Ι   | Input for low battery detector                                                                                                                                                                                                                                               |

| 6       | RTIME    | 0   | An RC network may be connected to this pin in order to hold this pin<br>voltage below 2.2V between the peaks of the ringing signal. This pin<br>controls internal power up and activates partial circuitry needed to<br>determine whether the incoming ring is valid or not. |

| 7       | PDWN     | Ι   | A logic "1" on this pin puts the chip in power down mode.<br>When a logic "0" is on this pin, the chip is activated.                                                                                                                                                         |

| 8       | VSS      | _   | Power supply ground                                                                                                                                                                                                                                                          |

| 9       | X2       | 0   | A 3.58MHz crystal or ceramic resonator should be connected to this pin and X1.                                                                                                                                                                                               |

| 10      | X1       | I   | A 3.58MHz crystal or ceramic resonator should be connected to this pin and X2.                                                                                                                                                                                               |

| 11      | LBOUT    | 0   | This pin will be set to "1" when the voltage on LBIN pin is lower than the internal reference voltage. Otherwise this pin stays at "0".                                                                                                                                      |

| 12      | RDET     | 0   | This open drain output goes low when valid ringing signal is detected.<br>When connected to PDWN pin, this pin can be used for auto power up.                                                                                                                                |

| 13      | CDET     | 0   | This open drain output goes low indicating that a valid carrier is<br>present on the line. An hysteresis is built-in to allow for a momentary<br>drop out of the carrier. When connected to PDWN pin, this pin can be<br>used for auto power up.                             |

| 14      | DOUT     | 0   | This pin presents the output of the demodulator whenever $\overline{\text{CDET}}$ pin is low. This data stream includes the alternate "1" and "0" pattern, and the 150ms of marking, which precedes the data. At all other times, this pin is held high.                     |

| 15      | NC       |     | No connect                                                                                                                                                                                                                                                                   |

| 16      | VDD      |     | Positive power supply                                                                                                                                                                                                                                                        |

25th Feb '97

$\mathbf{2}$

## **Absolute Maximum Ratings**

| Voltages referenced to VSS, except where noted. |

|-------------------------------------------------|

| DC Supply Voltage0.5V to 6.0V                   |

| Operating Temperature Range 0°C to 70°C         |

| Power Dissipation                | $.25 \mathrm{mW}$ |

|----------------------------------|-------------------|

| Storage Temperature Range40°C to | • 150°C           |

**Electrical Characteristics**

(Crystal=3.58MHz, Ta=0~70°C unless otherwise noted)

| Gh -1                        | Baramatar                          |               | Test Condition                                | Min.               | Тур. | Max.                  | Unit |

|------------------------------|------------------------------------|---------------|-----------------------------------------------|--------------------|------|-----------------------|------|

| Symbol                       | Parameter                          | VDD           | Condition                                     |                    |      |                       |      |

| V <sub>DD</sub>              | DC Supply Voltage                  | 5V            | _                                             | 3.5                | 5    | 5.5                   | v    |

| $\mathbf{I}_{\mathbf{STBY}}$ | Stand-by Current                   | 5V            | PDWN=1, RTIME=1<br>All outputs unloaded       | _                  |      | 1                     | μA   |

| I <sub>DD1</sub>             | Operating Current                  | 5V            | PDWN=1, RTIME=0<br>All outputs unloaded — 1   |                    | _    | mA                    |      |

| $I_{DD2}$                    | Operating Current                  | 5V            | PDWN=0, RTIME=0 or<br>1, All outputs unloaded | _                  | 2.5  | _                     | mA   |

| $V_{\mathrm{IL}}$            | Input Low Voltage                  | 5V            | —                                             | _                  |      | $0.2 \mathrm{V_{DD}}$ | v    |

| $V_{\mathrm{IH}}$            | Input High Voltage                 | 5V            | _                                             | 0.8V <sub>DD</sub> | _    | _                     | v    |

| $I_{OL}$                     | Output High Sourcing<br>Current    | 5V            | V <sub>OH</sub> =0.9V <sub>DD</sub>           | 0.8                |      |                       | mA   |

| $I_{OH}$                     | Output Low Sinking<br>Current      | $5\mathrm{V}$ | V <sub>OL</sub> =0.1V <sub>DD</sub>           | 2                  |      | _                     | mA   |

| $I_{IN}$                     | Input Leakage Current              | 5V            | —                                             | _                  | _    | $\pm 1$               | μA   |

| $\mathbf{V}_{\mathrm{T-}}$   | Input Low Threshold<br>Voltage     | $5\mathrm{V}$ | _                                             | _                  | 2.2  | _                     | v    |

| $V_{T+}$                     | Input High Threshold<br>Voltage    | 5V            |                                               | _                  | 2.9  | _                     | v    |

| $\mathrm{V_{RD2}}$           | RDET2 Threshold<br>Voltage         | $5\mathrm{V}$ |                                               | _                  | 1.2  | _                     | v    |

| $\mathbf{R}_{\mathbf{IN}}$   | Tip/Ring Input DC<br>Resistance    | $5\mathrm{V}$ | _                                             | _                  | 500  | _                     | KΩ   |

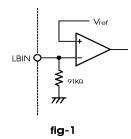

| $\mathbf{R}_{\mathrm{LBIN}}$ | Pull Low Resistance<br>on pin LBIN | 5V            | (see fig-1)                                   | _                  | 91   | _                     | KΩ   |

| Vref                         | Internal Reference<br>Voltage      | 5V            | (see fig-1)                                   | _                  | 1.2  |                       | v    |

| fosc                         | Operating Frequency                | 5V            |                                               |                    | 3.58 |                       | MHz  |

25th Feb '97

3

# **Analog Characteristics**

$V_{DD}{=}5V, V_{SS}{=}0V, Crystal{=}3.58MHz,$  Ta=0 to 70°C, 0dBm=0.7746Vrms@600 $\Omega$

| Characteristics                                                    |                                                | Min. | Тур.                           | Max. | Unit |

|--------------------------------------------------------------------|------------------------------------------------|------|--------------------------------|------|------|

| Input Sensitivity: Tip and Ring                                    |                                                |      | -40                            | _    | dBm  |

| Band Pass Filter Frequency Response<br>(Relative to 1700Hz @ 0dBm) | 60Hz<br>1200Hz<br>2200Hz<br>5000Hz<br>≥10000Hz | _    | $-54 \\ 0 \\ +1 \\ -19 \\ -35$ |      | dB   |

| Carrier Detect ON Sensitivity                                      |                                                |      | -52                            | -48  | dBm  |

| Carrier Detect OFF Sensitivity                                     |                                                | _    | -55                            | _    | dBm  |

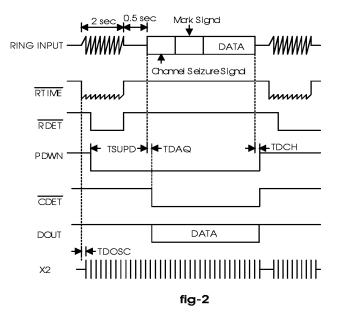

## **Switching Characteristics**

$V_{DD}{=}5V, V_{SS}{=}0V, Crystal{=}3.58MHz, Ta{=}25^{\circ}C, C_{L}{=}50_{P}F$

| Symbol            | Description                          | Min. | Тур. | Max. | Unit          |

|-------------------|--------------------------------------|------|------|------|---------------|

| $T_{\text{DOSC}}$ | Oscillator Startup                   |      | 2    | —    | $\mathbf{ms}$ |

| T <sub>SUPD</sub> | Power Up to Decode FSK (Set Up Time) |      | 8    | _    | ms            |

| T <sub>DAQ</sub>  | Carrier Detect Acquisition Time      |      | 7    | _    | ms            |

| T <sub>DCH</sub>  | End of Data to Carrier Detect High   |      | 9    | _    | $\mathbf{ms}$ |

$\mathbf{4}$

25th Feb '97

#### **Timing Diagram**

Note:

The HT9030 is only a CLID receiver for receiving the physical layer FSK signals. The higher layers of data transmission, data link layer and message assembly layer, are well defined in TR-NMT-000030 and TR-NMT-00031. Please refer to these two documents for more details about the higher layer protocols.

$25 \mathrm{th}$  Feb '97

$\mathbf{5}$

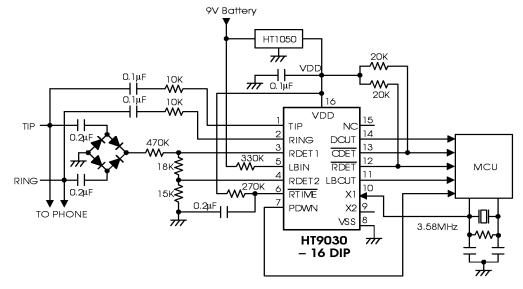

# **Application Circuit**

fig-3

6

25th Feb '97