### General Description

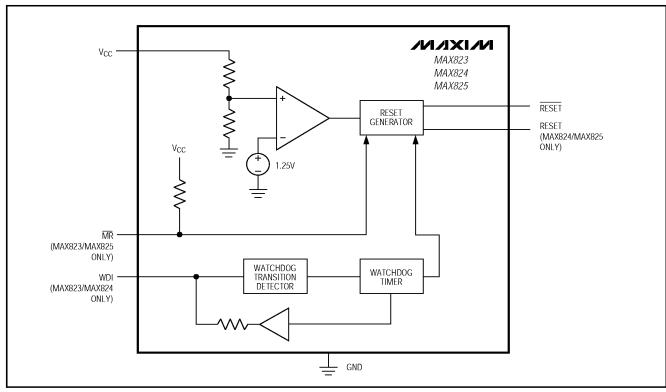

The MAX823/MAX824/MAX825\* microprocessor ( $\mu P$ ) supervisory circuits combine reset output, watchdog, and manual-reset input functions in a 5-pin SOT23-5 package. They significantly improve system reliability and accuracy compared to separate ICs or discrete components. The MAX823/MAX824/MAX825 are specifically designed to ignore fast transients on VCC.

Five preprogrammed reset threshold voltages are available, designated by the following package suffixes: L = 4.63V, M = 4.38V, T = 3.08V, S = 2.93V, and R = 2.63V. All three devices have an active-low reset output, which is guaranteed to be in the correct state for  $V_{CC}$  down to 1V. The MAX824/MAX825 also have an active-high reset output. The following *Selector Guide* explains the functions offered in this series of parts

## Applications

Battery-Powered Computers and Controllers

Embedded Controllers

Intelligent Instruments

Automotive Systems

Critical µP Monitoring

Portable/Battery-Powered Equipment

#### **Selector Guide**

| FUNCTION           | MAX823 | MAX823 MAX824 |       |

|--------------------|--------|---------------|-------|

| Active-Low Reset   | ~      | ~             | ~     |

| Active-High Reset  |        | ~             | ~     |

| Watchdog Input     | ~      | ~             | - E07 |

| Manual-Reset Input | ~      |               | V     |

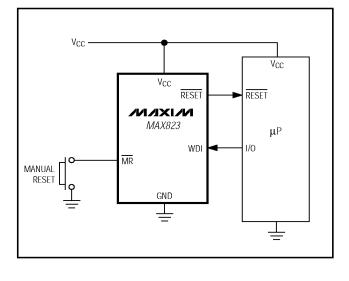

Typical Operating Circuit appears at end of data sheet.

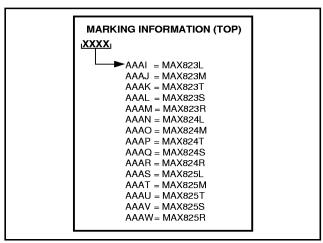

Marking Information appears at end of data sheet.

#### **Features**

- Precision Monitoring of +3V, +3.3V, and +5V

Power Supplies

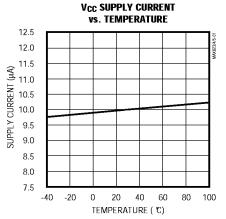

- Operating Current: 10μA (MAX823L/M) 3μA (MAX825T/S/R)

- ◆ Fully Specified Over Temperature

- ♦ 140ms Min Power-On Reset

- ♦ Guaranteed RESET Valid to V<sub>CC</sub> = 1V

- **♦ Power-Supply Transient Immunity**

- Watchdog Timer with 1.6sec Timeout (MAX823/MAX824)

- ♦ Manual-Reset Input (MAX823/MAX825)

- No External Components

#### **Ordering Information**

| PART <sup>†</sup> | TEMP. RANGE    | PIN-PACKAGE |

|-------------------|----------------|-------------|

| MAX823_EUK        | -40 ℃ to +85 ℃ | 5 SOT23-5   |

| MAX824_EUK        | -40 ℃ to +85 ℃ | 5 SOT23-5   |

| MAX825_EUK        | -40 ℃ to +85 ℃ | 5 SOT23-5   |

†Insert the desired suffix letter (from the table below) into the blank to complete the part number.

| SUFFIX | RESET<br>THRESHOLD (V) |

|--------|------------------------|

|        | 4.63                   |

| М      | 4.38                   |

| T      | 3.08                   |

| S      | 2.93                   |

| R      | 2.63                   |

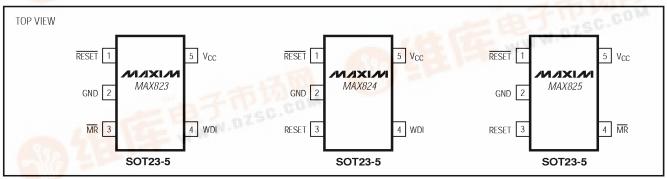

## Pin Configurations

\*Patents Pending

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Vcc0.3V to                                            | 0.0V + c |

|-------------------------------------------------------|----------|

| All Other Pins0.3V to (VCC                            | + 0.3V)  |

| Input Current, All Pins Except RESET and RESET        | 20mA     |

| Output Current, RESET, RESET                          | 20mA     |

| Rate of Rise, Vcc                                     | 100V/µs  |

| Continuous Power Dissipation (T <sub>A</sub> = +70 ℃) |          |

| SOT23-5 (derate 7.1mW/ ℃ above +70 ℃)                 | 571mW    |

| Operating Temperature Range  |                |

|------------------------------|----------------|

| MAX82_EUK                    | 40 ℃ to +85 ℃  |

| Storage Temperature Range    | 65 ℃ to +160 ℃ |

| Lead Temperature (soldering, | 10sec)+300 ℃   |

|                              |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VCC = +4.75V to +5.5V for MAX82\_L, VCC = +4.5V to +5.5V for MAX82\_M, VCC = +3.15V to +3.6V for MAX82\_T, VCC = +3V to +3.6V for MAX82\_S, VCC = +2.7V to +3.6V for MAX82\_R,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$  °C.) (Note 1)

| PARAMETER                                  | SYMBOL          | CONDITIONS                    |                                 | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------|-----------------|-------------------------------|---------------------------------|------|------|------|-------|

| Operating Voltage Range                    | \/              | T <sub>A</sub> = 0 ℃ to +70 ℃ |                                 | 1.0  |      | 5.5  | V     |

| Operating voltage Range                    | Vcc             | TA = -40 °C to +85 °C         |                                 | 1.2  |      |      | \ \ \ |

|                                            |                 | WDI and MR<br>unconnected     | MAX823L/M,<br>MAX824L/M         |      | 10   | 24   | μΑ    |

| Supply Current                             | ISUPPLY         |                               | MAX823T/S/R,<br>MAX824T/S/R     |      | 5    | 12   |       |

|                                            |                 | MR unconnected                | MAX825L/M                       |      | 4.5  | 12   |       |

|                                            |                 | IVIR unconnected              | MAX825T/S/R                     |      | 3    | 8    |       |

|                                            |                 | MAX82_L                       | TA = +25 ℃                      | 4.56 | 4.63 | 4.70 | V     |

|                                            |                 |                               | T <sub>A</sub> = -40 ℃ to +85 ℃ | 4.50 |      | 4.75 |       |

|                                            | VRST            | MAX82_M                       | TA = +25 ℃                      | 4.31 | 4.38 | 4.45 |       |

|                                            |                 |                               | T <sub>A</sub> = -40 ℃ to +85 ℃ | 4.25 |      | 4.50 |       |

| Reset Threshold                            |                 | MAX82_T                       | TA = +25 ℃                      | 3.04 | 3.08 | 3.11 |       |

| Reset Tileshold                            |                 |                               | T <sub>A</sub> = -40 ℃ to +85 ℃ | 3.00 |      | 3.15 |       |

|                                            |                 | MAX82_S                       | T <sub>A</sub> = +25 ℃          | 2.89 | 2.93 | 2.96 |       |

|                                            |                 |                               | T <sub>A</sub> = -40 ℃ to +85 ℃ | 2.85 |      | 3.00 |       |

|                                            |                 | MAX82_R                       | T <sub>A</sub> = +25 ℃          | 2.59 | 2.63 | 2.66 |       |

|                                            |                 |                               | T <sub>A</sub> = -40 ℃ to +85 ℃ | 2.55 |      | 2.70 |       |

| Reset Threshold Hysteresis                 |                 | MAX82_L/M                     |                                 |      | 10   |      | mV    |

| Neset Theshold Trysteresis                 |                 | MAX82_T/S/R                   |                                 |      | 5    |      | IIIV  |

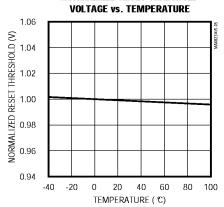

| Reset Threshold Temperature<br>Coefficient |                 |                               |                                 |      | 40   |      | ppm/℃ |

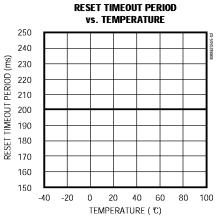

| Reset Timeout Period                       | ton             | MAX82_L/M                     |                                 | 140  | 200  | 280  | ms    |

| Neset Timeout Fellod                       | t <sub>RP</sub> | MAX82_T/S/R                   |                                 | 140  | 200  | 280  | 1115  |

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{CC}$  = +4.75V to +5.5V for MAX82\_L,  $V_{CC}$  = +4.5V to +5.5V for MAX82\_M,  $V_{CC}$  = +3.15V to +3.6V for MAX82\_T,  $V_{CC}$  = +3V to +3.6V for MAX82\_S,  $V_{CC}$  = +2.7V to +3.6V for MAX82\_R,  $V_{CC}$  = TMIN to TMAX, unless otherwise noted. Typical values are at  $V_{CC}$  = +25  $V_{CC}$  (Note 1)

| PARAMETER                                     | SYMBOL          | CONDITIONS                                                                                                                              | MIN                   | TYP       | MAX                | UNITS |  |

|-----------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|--------------------|-------|--|

|                                               | Vон             | MAX82_L/M, V <sub>CC</sub> = V <sub>RST</sub> max,<br>I <sub>SOURCE</sub> = 120μA                                                       | V <sub>CC</sub> - 1.5 | Vcc - 1.5 |                    |       |  |

|                                               |                 | MAX82_T/S/R, V <sub>CC</sub> = V <sub>RST</sub> max,<br>ISOURCE = 30µA                                                                  | 0.8V <sub>CC</sub>    |           |                    |       |  |

| RESET Output Voltage                          | N.              | MAX82_L/M, V <sub>CC</sub> = V <sub>RST</sub> min,<br>I <sub>SINK</sub> = 3.2mA                                                         |                       |           | 0.4                | V     |  |

| neser output voltage                          |                 | $\begin{aligned} &MAX82\_T/S/R,  V_{CC} = V_{RST}  min, \\ &I_{SINK} = 1.2 mA \end{aligned}$                                            |                       |           | 0.3                | V     |  |

|                                               | V <sub>OL</sub> | T <sub>A</sub> = 0 °C to +70 °C, V <sub>CC</sub> = 1V,<br>V <sub>CC</sub> falling, I <sub>SINK</sub> = 50µA                             |                       |           | 0.3                |       |  |

|                                               |                 | $T_A = -40  \text{C}$ to $+85  \text{C}$ , $V_{CC} = 1.2 \text{V}$ , $V_{CC}$ falling, $V_{BATT} = 0 \text{V}$ , $I_{SINK} = 100 \mu A$ |                       |           | 0.3                |       |  |

| RESET Output Short-Circuit                    | ISOURCE         | $MAX82\_L/M$ , $\overline{RESET} = 0V$ , $V_{CC} = 5.5V$                                                                                |                       |           | 800                | μА    |  |

| Current (Note 2)                              |                 | MAX82_T/S/R, $\overline{RESET} = 0V$ , $V_{CC} = 3.6V$                                                                                  |                       |           | 400                | μл    |  |

| RESET Output Voltage                          | Voн             | $V_{CC} > 1.8V$ , $I_{SOURCE} = 150\mu A$                                                                                               | 0.8V <sub>CC</sub>    |           |                    |       |  |

|                                               | V <sub>OL</sub> | MAX824L/M, MAX825L/M,<br>VCC = VRST max, ISINK = 3.2mA                                                                                  |                       |           | 0.4                | V     |  |

|                                               |                 | MAX824T/S/R, MAX825T/S/R,<br>VCC = VRST max, ISINK = 1.2mA                                                                              |                       |           | 0.3                |       |  |

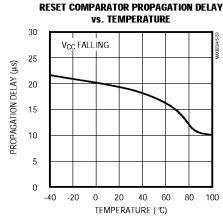

| V <sub>CC</sub> to RESET Delay                |                 | V <sub>RST</sub> - V <sub>CC</sub> = 100mV                                                                                              |                       | 20        |                    | μs    |  |

| WATCHDOG INPUT (MAX823/M                      | AX824)          |                                                                                                                                         |                       |           |                    |       |  |

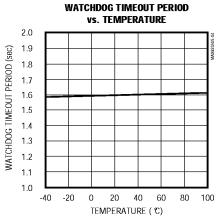

| Watchdog Timeout Period                       | t <sub>WD</sub> |                                                                                                                                         | 1.12                  | 1.60      | 2.40               | sec   |  |

| WDI Pulse Width                               | twoı            | V <sub>IL</sub> = 0.4V, V <sub>IH</sub> = 0.8V <sub>CC</sub>                                                                            | 50                    |           |                    | ns    |  |

| MELL THE LICENSE                              | VIL             | V <sub>CC</sub> = 5V                                                                                                                    |                       |           | 0.3V <sub>CC</sub> |       |  |

| WDI Input Threshold (Note 3)                  | VIH             |                                                                                                                                         | 0.7V <sub>CC</sub>    |           |                    | V     |  |

| 14/D11                                        |                 | WDI = V <sub>CC</sub> , time average                                                                                                    |                       | 120       | 160                | Δ.    |  |

| WDI Input Current (Note 4)                    |                 | WDI = 0V, time average                                                                                                                  | -20                   | -15       |                    | μA    |  |

| MANUAL-RESET INPUT (MAX82                     | 23/MAX825       | )                                                                                                                                       |                       |           |                    |       |  |

| MR Input Threshold                            | VIL             |                                                                                                                                         | 0.3V <sub>CC</sub>    |           |                    |       |  |

|                                               | VIH             |                                                                                                                                         |                       |           | 0.7V <sub>CC</sub> | V     |  |

| MR Pulse Width                                |                 |                                                                                                                                         | 1.0                   |           |                    | μs    |  |

| MR Noise Immunity (pulse width with no reset) |                 |                                                                                                                                         |                       | 100       |                    | ns    |  |

| MR to Reset Delay                             |                 |                                                                                                                                         |                       | 500       |                    | ns    |  |

| MR Pull-Up Resistance (internal)              |                 |                                                                                                                                         | 35                    | 52        | 75                 | kΩ    |  |

**Note 1:** Over-temperature limits are guaranteed by design and not production tested.

Note 2: The RESET short-circuit current is the maximum pull-up current when RESET is driven low by a µP bidirectional reset pin.

**Note 3:** WDI is internally serviced within the watchdog period if WDI is left unconnected.

Note 4: The WDI input current is specified as the average input current when the WDI input is driven high or low. The WDI input is designed to drive a three-stated-output device with a 10μA maximum leakage current and a maximum capacitive load of 200pF. This output device must be able to source and sink at least 200μA when active.

### \_Typical Operating Characteristics

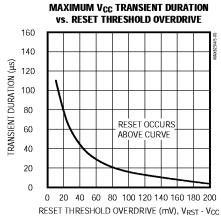

(MAX823L,  $V_{CC} = +5V$ ,  $T_A = +25 \, ^{\circ}$ C, unless otherwise noted.)

NORMALIZED RESET THRESHOLD

## Pin Description

| PIN    |        | PIN    |       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX823 | MAX824 | MAX825 | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                           |

| 1      | 1      | 1      | RESET | Active-Low Reset Output. Pulses low for 200ms when triggered, and remains low whenever V <sub>CC</sub> is below the reset threshold or when MR is a logic low. It remains low for 200ms after one of the following occurs: V <sub>CC</sub> rises above the reset threshold, the watchdog triggers a reset, or MR goes low to high.                                                                 |

| 2      | 2      | 2      | GND   | Ground. 0V reference for all signals.                                                                                                                                                                                                                                                                                                                                                              |

| 3      | _      | 4      | MR    | Manual-Reset Input. A logic low on $\overline{\text{MR}}$ asserts reset. Reset remains asserted as long as $\overline{\text{MR}}$ is held low and for 200ms after $\overline{\text{MR}}$ returns high. The active-low input has an internal $52k\Omega$ pull-up resistor. It can be driven from a CMOS-logic line or shorted to ground with a switch. Leave open or connect to $V_{CC}$ if unused. |

| _      | 3      | 3      | RESET | Active-High Reset Output. Inverse of RESET.                                                                                                                                                                                                                                                                                                                                                        |

| 4      | 4      | _      | WDI   | Watchdog Input. If WDI remains either high or low for longer than the watchdog timeout period, the internal watchdog timer runs out and a reset is triggered. The internal watchdog timer clears whenever reset is asserted, or whenever WDI sees a rising or falling edge. If WDI is left unconnected or is connected to a three-stated buffer output, the watchdog feature is disabled.          |

| 5      | 5      | 5      | Vcc   | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 1. Functional Diagram

#### Detailed Description

#### RESET Output

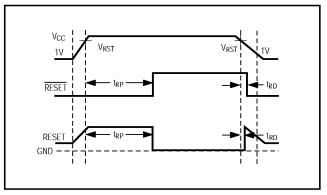

A microprocessor's ( $\mu$ P's) reset input starts the  $\mu$ P in a known state. The MAX823/MAX824/MAX825  $\mu$ P supervisory circuits assert a reset to prevent code-execution errors during power-up, power-down, and brownout conditions. RESET is guaranteed to be a logic low for VCC down to 1V. Once VCC exceeds the reset threshold, an internal timer keeps RESET low for the specified reset timeout period (t<sub>RP</sub>); after this interval, RESET returns high (Figure 2).

If a brownout condition occurs (VCC dips below the reset threshold),  $\overline{\text{RESET}}$  goes low. Each time  $\overline{\text{RESET}}$  is asserted it stays low for the reset timeout period. Any time VCC goes below the reset threshold the internal timer restarts.  $\overline{\text{RESET}}$  both sources and sinks current. RESET on the MAX824/MAX825 is the inverse of  $\overline{\text{RESET}}$ .

#### Manual-Reset Input (MAX823/MAX825)

Many  $\mu P$ -based products require manual-reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. On the MAX823/MAX825, a logic low on  $\overline{\text{MR}}$  asserts reset. Reset remains asserted while  $\overline{\text{MR}}$  is low, and for tree (200ms nominal) after it returns high.  $\overline{\text{MR}}$  has an internal 52k $\Omega$  pull-up resistor, so it can be left open if not used. This input can be driven with CMOS-logic levels or with open-drain/collector outputs. Connect a normally open momentary switch from  $\overline{\text{MR}}$  to GND to create a manual-reset function; external debounce circuitry is not required. If  $\overline{\text{MR}}$  is driven from long cables or the device is used in a noisy environment, connect a 0.1 $\mu F$  capacitor from  $\overline{\text{MR}}$  to GND to provide additional noise immunity.

#### Watchdog Input (MAX823/MAX824)

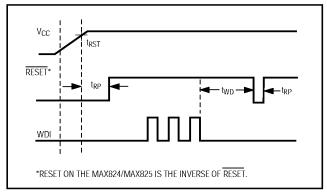

In the MAX823/MAX824, the watchdog circuit monitors the  $\mu$ P's activity. If the  $\mu$ P does not toggle the watchdog input (WDI) within twD (1.6sec), reset asserts. The internal 1.6sec timer is cleared by either a reset pulse or by toggling WDI, which detects pulses as short as 50ns. While reset is asserted, the timer remains cleared and does not count. As soon as reset is released, the timer starts counting (Figure 3).

Disable the watchdog function by leaving WDI unconnected or by three-stating the driver connected to WDI. The watchdog input is internally driven low during the first 7/8 of the watchdog timeout period and high for the last 1/8 of the watchdog timeout period. When WDI is left unconnected, this internal driver clears the 1.6sec timer every 1.4sec. When WDI is three-stated or unconnected, the maximum allowable leakage current is 10µA and the maximum allowable load capacitance is 200pF.

#### **Applications Information**

#### **Watchdog Input Current**

The MAX823/MAX824 WDI inputs are internally driven through a buffer and series resistor from the watchdog counter (Figure 1). When WDI is left unconnected, the watchdog timer is serviced within the watchdog timeout period by a low-high-low pulse from the counter chain. For minimum watchdog input current (minimum overall power consumption), leave WDI low for the majority of the watchdog timeout period, pulsing it low-high-low once within the first 7/8 of the watchdog timeout period to reset the watchdog timer. If WDI is externally driven high for the majority of the timeout period, up to 160µA can flow into WDI.

Figure 2. Reset Timing Diagram

Figure 3. MAX823/MAX824 Watchdog Timing Relationship

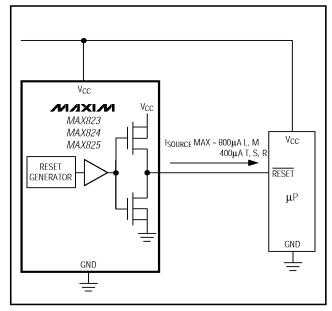

#### Interfacing to µPs with Bidirectional Reset Pins

The  $\overline{\text{RESET}}$  output maximum pull-up current is 800 $\mu$ A for L/M versions (400 $\mu$ A for T/S/R versions). This allows  $\mu$ Ps with bidirectional resets, such as the 68HC11, to force  $\overline{\text{RESET}}$  low when the MAX823/MAX824/MAX825 are pulling  $\overline{\text{RESET}}$  high (Figure 4).

#### **Negative-Going Vcc Transients**

These supervisors are relatively immune to short-duration, negative-going  $V_{\rm CC}$  transients (glitches), which usually do not require the entire system to shut down. Resets are issued to the  $\mu P$  during power-up, power-down, and brownout conditions.

The Typical Operating Characteristics show a graph of the MAX823L's Maximum VCC Transient Duration vs. Reset Threshold Overdrive, for which reset pulses are not generated. The graph was produced using negative-going VCC pulses, starting at 5V and ending below the reset threshold by the magnitude indicated (reset threshold overdrive). The graph shows the maximum pulse width that a negative-going VCC transient can typically have without triggering a reset pulse. As the amplitude of the transient increases (i.e., goes farther below the reset threshold), the maximum allowable pulse width decreases. Typically, a VCC transient that goes 100mV below the reset threshold and lasts for 15µs or less will not trigger a reset pulse.

An optional 0.1 $\mu$ F bypass capacitor mounted close to  $V_{CC}$  provides additional transient immunity.

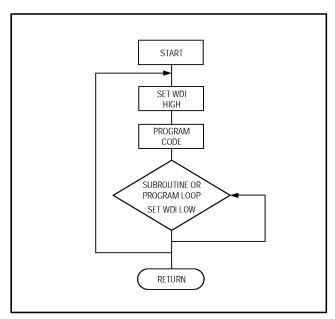

## Watchdog Software Considerations (MAX823/MAX824)

One way to help the watchdog timer monitor software execution more closely is to set and reset the watchdog input at different points in the program, rather than pulsing the watchdog input high-low-high or low-high-low. This technique avoids a stuck loop, in which the watchdog timer would continue to be reset inside the loop, keeping the watchdog from timing out.

Figure 5 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the beginning of every subroutine or loop, then set high again when the program returns to the beginning. If the program should hang in any subroutine, the problem would quickly be corrected, since the I/O is continually set low and the watchdog timer is allowed to time out, causing a reset or interrupt to be issued. As described in the Watchdog Input Current section, this scheme results in higher time average WDI input current than does leaving WDI low for the majority of the timeout period and periodically pulsing it low-high-low.

Figure 4. Interfacing to µPs with Bidirectional Resets

Figure 5. Watchdog Flow Diagram

#### \_Typical Operating Circuit

### Chip Information

TRANSISTOR COUNT: 607

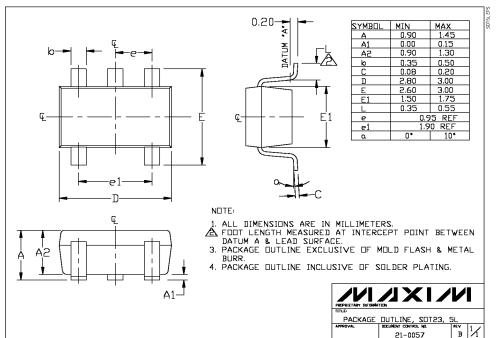

### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-377-7600

8