7997076 0011721 写识PCB打样工厂,24小时加

SANYO SEMICONDUCTOR

CMOS LSI

# High-voltage, Two-channel Electronic Attenuator

©2443C

### **OVERVIEW**

The LC7535 is a two-channel electronic attenuator for volume, balance and loudness controls in stereo audio applications.

The LC7535 reads data from a three-line serial bus to control attenuation in 1 dB steps over an 80 dB range, up to a maximum of 98 dB. It features a center tap at 20 dB attenuation for a loudness control using a minimum of external components. A device select pin allows two devices to be connected to the serial bus.

The LC7535 operates from 5 V and ±16 V supplies and is available in 22-pin DIPs.

#### **FEATURES**

- Three-line serial control

- Two device select

- Tap at 20 dB attenuation for a loudness control

- 80 dB attenuation range adjustable in 1 dB steps

- 98 dB maximum attenuation

- 75 dB crosstalk rejection

- 0.011% total harmonic distortion

- 47  $k\Omega$  input impedance

- 5 V and ±16 V supplies

- 22-pin DIP

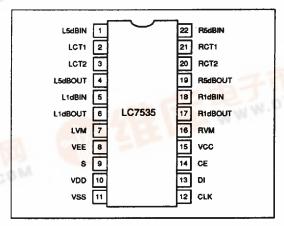

## **PINOUT**

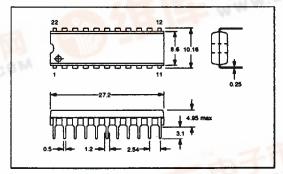

## PACKAGE DIMENSIONS

Unit: mm

3010A-DIP22

## **BLOCK DIAGRAM**

## SANYO SEMICONDUCTOR CORP

## PIN DESCRIPTION

| Number | Name    | Description                                                                               |  |  |  |

|--------|---------|-------------------------------------------------------------------------------------------|--|--|--|

| 1      | L5dBIN  | Left-channel 5 dB attenuation step input. Low-impedance drive. 75 kΩ total resistance     |  |  |  |

| 2      | LCT1    | Left-channel loudness compensation inputs                                                 |  |  |  |

| 3      | LCT2    |                                                                                           |  |  |  |

| 4      | L5dBOUT | Left-channel 5 dB attenuation step output. Approximately 1 MΩ load resistance             |  |  |  |

| 5      | L1dBIN  | Left-channel 1 dB attenuation step input. Low-impedance drive                             |  |  |  |

| 6      | L1dBOUT | Left-channel 1 dB attenuation step output. 47 k $\Omega$ to 1 M $\Omega$ load resistance  |  |  |  |

| 7      | LVM     | Left-channel volume control common. Normally connected to ground                          |  |  |  |

| 8      | VEE     | -16 V supply                                                                              |  |  |  |

| 9      | S       | Address select input                                                                      |  |  |  |

| 10     | VDD .   | 16 V supply                                                                               |  |  |  |

| 11     | VSS     | Ground                                                                                    |  |  |  |

| 12     | CLK     | Clock input                                                                               |  |  |  |

| 13     | DI      | Serial data input                                                                         |  |  |  |

| 14     | CE      | Chip enable input                                                                         |  |  |  |

| 15     | VCC     | 5 V supply                                                                                |  |  |  |

| 16     | RVM     | Right-channel volume control common. Normally connected to ground                         |  |  |  |

| 17     | R1dBOUT | Right-channel 1 dB attenuation step output. 47 k $\Omega$ to 1 M $\Omega$ load resistance |  |  |  |

| 18     | R1dBIN  | Right-channel 1 dB attenuation step input. Low-impedance drive                            |  |  |  |

| 19     | R5dBOUT | Right-channel 5 dB attenuation step output. Approximately 1 MΩ load resistance            |  |  |  |

## LAZT ■ TIT ESTIGOO 1707PPT ■ C 3EA

#### LC7535

| Number | Marne  | Description                                                                            |  |  |  |

|--------|--------|----------------------------------------------------------------------------------------|--|--|--|

| 20     | RCT2   | Disk should be described                                                               |  |  |  |

| 21     | RCT1   | Right-channel loudness compensation inputs                                             |  |  |  |

| 22     | R5dBIN | Right-channel 5 dB attenuation step input. Low-impedance drive. 75 kΩ total resistance |  |  |  |

## **SPECIFICATIONS**

## SANYO SEMICONDUCTOR CORP

## **Absolute Maximum Ratings**

| Parameter                          | Symbol           | Rating                                         | Unit |

|------------------------------------|------------------|------------------------------------------------|------|

|                                    | V <sub>DD</sub>  | 0 to 18                                        |      |

| Supply voltage ranges              | VEE              | -18 to 0                                       | v    |

|                                    | Vœ               | 0 to 7                                         |      |

| CLK, DI and CE input voltage range | V <sub>11</sub>  | 0 to V <sub>CC</sub> + 0.3                     | ٧    |

| Analog input voltage range         | V <sub>12</sub>  | V <sub>EE</sub> - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |

| Select pin input voltage range     | V <sub>I3</sub>  | V <sub>CC</sub> - 0.3 to V <sub>DO</sub> + 0.3 | ٧    |

| Power dissipation                  | P <sub>D</sub>   | 250                                            | mW   |

| Operating temperature range        | T <sub>opg</sub> | -30 to 75                                      | °C   |

| Storage temperature range          | T <sub>stg</sub> | -40 to 125                                     | °C   |

## **Recommended Operating Conditions**

$T_a = 25$  °C,  $V_{SS} = 0$  V

| Parameter                      | Symbol          | Rating                        | Unit |

|--------------------------------|-----------------|-------------------------------|------|

| Analog supply voltage ranges   | V <sub>DD</sub> | V <sub>CC</sub> + 4.5 to 16.0 | ٧    |

| Palatog supply voitage latiges | V <sub>EE</sub> | -16 to 0                      | ٧    |

| Logic supply voltage           | Vœ              | 5                             | ٧    |

| Logic supply voltage range     | Vα              | 4.5 to 5.5                    | ٧    |

## **Electrical Characteristics**

$T_a = 25$  °C,  $V_{SS} = 0$  V

| Parameter                           | Symbol           | Condition | Rating                                                             |     |                                                                    | Unit             |

|-------------------------------------|------------------|-----------|--------------------------------------------------------------------|-----|--------------------------------------------------------------------|------------------|

| ·                                   |                  |           | min                                                                | typ | max                                                                | URR              |

| Supply currents                     | I <sub>DD</sub>  |           | -                                                                  | _   | 1                                                                  | mA               |

| Supply currents                     | lœ               |           | -                                                                  | _   | 1                                                                  |                  |

| Serial bus LOW-level input voltage  | V <sub>IL1</sub> |           | Vss                                                                | _   | 0.2Vcc                                                             | ٧                |

| Serial bus HIGH-level input voltage | V <sub>IH1</sub> |           | 0.8V <sub>CC</sub>                                                 | _   | Vcc                                                                | ٧                |

| Select pin LOW-level input voltage  | V <sub>IL2</sub> |           | Vœ                                                                 | _   | 0.2 × (V <sub>DO</sub><br>- V <sub>CC</sub> ) +<br>V <sub>CC</sub> | ٧                |

| Select pin HIGH-level input voltage | V <sub>1H2</sub> |           | 0.8 × (V <sub>00</sub><br>- V <sub>00</sub> ) +<br>V <sub>00</sub> | _   | V <sub>D0</sub>                                                    | ٧                |

| Input voltage                       | ViN              |           | VEE                                                                | -   | V <sub>DO</sub>                                                    | V <sub>p-p</sub> |

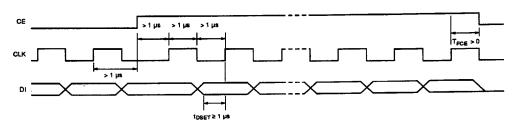

| Input pulsewidth                    | lew              |           | 1 1                                                                | -   | -                                                                  | μs               |

| Parameter                 | Symbol         |                                                                                                                         | Rating |       |     | Unit |

|---------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------|--------|-------|-----|------|

|                           |                | Condition                                                                                                               | min    | typ   | max | VIII |

| Setup time                | teetup         |                                                                                                                         | 1      |       | -   | μs   |

| Hold time                 | thold          |                                                                                                                         | 1      | _     | -   | μs   |

| Operating frequency       | fopg           |                                                                                                                         | -      | -     | 500 | kHz  |

| Output leakage current    | loff           | Analog switches OFF                                                                                                     | -10    |       | 10  | μΑ   |

| Total harmonic distortion |                | V <sub>IN</sub> = 1 V, f = 1 kHz,<br>V <sub>DD</sub> V <sub>EE</sub> = 32 V,<br>V <sub>R</sub> = V <sub>R</sub> (max)   | _      | 0.003 | -   | %    |

|                           | THD            | V <sub>IN</sub> = 1 V, f = 1 kHz,<br>V <sub>DD</sub> - V <sub>EE</sub> = 32 V,<br>V <sub>R</sub> = V <sub>R</sub> (max) | -      | 0.011 | -   |      |

| Crosstalk rejection       | Ст             | f = 20 kHz, V <sub>IN</sub> = 1 V                                                                                       | 60     | 75    | -   | dB   |

| Maximum attenuation       | V <sub>o</sub> | f = 20 kHz, V <sub>IN</sub> = 1 V                                                                                       | -      | 98    | -   | dB   |

## **Timing**

## SANYO SEMICONDUCTOR CORP

## **FUNCTIONAL DESCRIPTION**

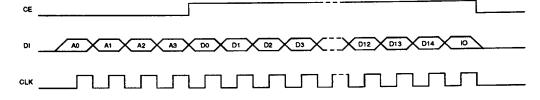

## **Data Control**

## Data is clocked into a 20-bit shift register. When 20 bits have been received, the data is latched and then passed to a level shifter.

## **Data Format**

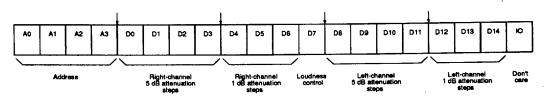

The 20-bit data word comprises a 4-bit address code, two 4-bit 5 dB attenuation step selectors, two 3-bit 1 dB attenuation step selectors and a loudness control ON/OFF bit as shown in figure 1.

Figure 1. Data format

The voltage on the select input determines the address of the device as shown in table 1.

Table 1. Address codes

| Select pin | A0 | A1 | A2 | <b>A</b> 3 |

|------------|----|----|----|------------|

| VDD        | 1  | 0  | 0  | 1          |

| VCC        | 0  | 0  | 0  | 1          |

Data bits D0 to D3 select the right-channel attenuation in 5 dB steps as shown in table 2. Similarly, bits D8 to D11 select the left-channel attenuation in 5 dB steps. Table 2. Right-channel 5 dB steps

| Attenuation (dB) | D0 | D1 | D2 | D3 |

|------------------|----|----|----|----|

| 0                | 1  | 1  | 1  | 1  |

| 5                | 0  | 1  | 1  | 1  |

| 10               | 1  | 0  | 1  | 1  |

| 15               | 0  | 0  | 1  | 1  |

| 20               | 1  | 1  | 0  | 1  |

| 25               | 0  | 1  | 0  | 1  |

| 30               | 1  | 0  | 0  | 1  |

| 35               | 0  | 0  | 0  | 1  |

| 40               | 1  | 1  | 1  | 0  |

| 45               | 0  | 1  | 1  | 0  |

| 50               | 1  | 0  | 1  | 0  |

| 55               | 0  | 0  | 1  | 0  |

| 60               | 1  | 1  | 0  | 0  |

| 65               | 0  | 1  | 0  | 0  |

| 70               | 1  | 0  | 0  | 0  |

| 75               | 0  | 0  | 0  | 0  |

Data bits D4 to D6 select the right-channel attenuation in 1 dB steps as shown in table 3. Similarly, bits D12 to D14 select the left-channel attenuation in 1 dB steps.

Table 3. Right-channel 1 dB steps

| Attenuation (dB) | D4 | D5 | D6 |

|------------------|----|----|----|

| 0                | 0  | 1  | 1  |

| Dummy. See note. | 1  | 0  | 0  |

| 1                | 1  | 0  | 1  |

| 2                | 0  | 0  | 1  |

| 3                | 1  | 1  | 0  |

| 4                | 0  | 1  | 0  |

| •                | 0  | 0  | 0  |

#### Note

Dummy data is inserted to give 79 dB to infinity attenuation during switchover.

Data bit D7 selects loudness control. When D7 is 1, loudness control is ON, and when 0, loudness control is OFF.

## **Audio Signal**

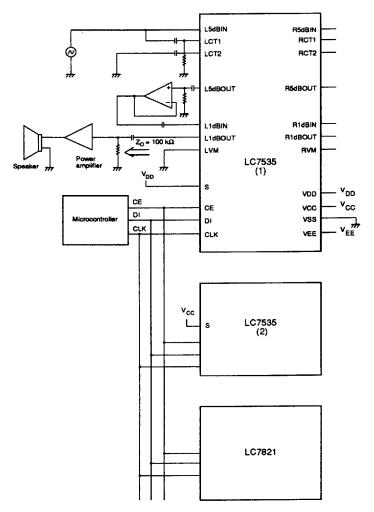

The right-channel audio input signal is input on R5dBIN (5 dB attenuation steps). The output, R5dBOUT, is fed back to R1dBIN (1 dB attenuation steps). The right-channel audio output is on R1dBOUT. The left-channel audio signal flow is identical.

SANYO SEMICONDUCTOR CORP

## TYPICAL APPLICATION

## SANYO SEMICONDUCTOR CORP

Figure 2. Typical application