#### 查询LC78211供应商

CMOS LSI

# LC78211, 78212, 78213

## **Analog Function Switch**

## **Applications**

Function switching under serial data control in amplifiers, receivers, and other electronic equipment

WWW.DZSC.CO

## **Features**

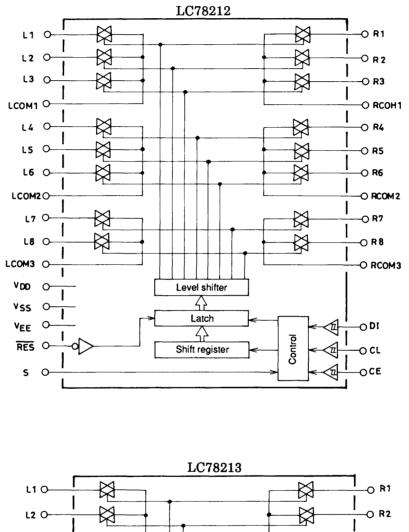

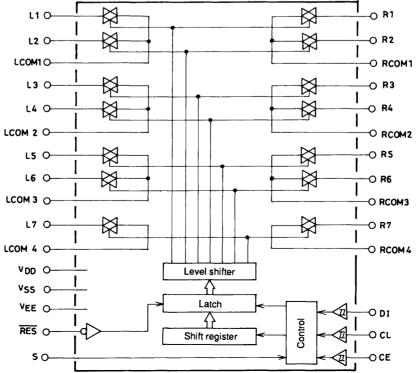

- Two sets of eight (or in the LC78213, seven) built-in circuits with three switching configurations available based on differing internal connections

- · Control according to serial data sent from a microprocessor, and easy connection to 5 V microprocessors

- Two identical products can be connected to a shared bus due to the provision of a select pin (S).

- A reset pin that turns off all analog switches

- A  $\pm 20$  V withstand voltage rating allows these products WWW.DZSC.COM to provide a wide dynamic range.

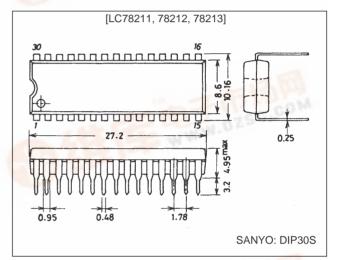

# Package Dimensions

unit: mm

#### 3061-DIP30S

## **Specifications** Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                                  | Symbol              | Conditions                                         | Ratings                          | Unit |

|--------------------------------------------|---------------------|----------------------------------------------------|----------------------------------|------|

| Maximum augustu valtaga                    | V <sub>DD</sub> max | V <sub>DD</sub>                                    | -0.3 to +20                      | V    |

| Maximum supply voltage                     | V <sub>EE</sub> max | VEE                                                | -20 to +0.3                      | V    |

| 14 · · · · · · · · · · · · · · · · · · ·   | V <sub>I</sub> 1    | DI, CL, CE, S, RES                                 | -0.3 to +20                      | V    |

| Maximum input voltage                      | V <sub>I</sub> 2    | L1 to L8, R1 to R8, LCOM1 to LCOM4, RCOM1 to RCOM4 | $V_{EE} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Analog switch potential difference when on | ΔV <sub>ON</sub>    | With the switch on                                 | 0.5                              | V    |

| Allowable power dissipation                | Pd max              | Ta ≤ 75°C                                          | 100                              | mW   |

| Operating temperature range                | Topr                |                                                    | -30 to +75                       | °C   |

| Storage temperature range                  | Tstg                |                                                    | -40 to +125                      | °C   |

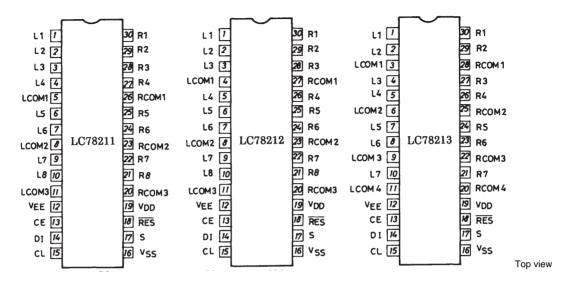

## **Pin Assignments**

## Allowable Operating Ranges at Ta = 25°C, $V_{SS}$ = 0 V, $\mid V_{DD} \mid \, \geq \, \mid V_{EE} \mid$

| Parameter                            | Symbol              | Conditions min typ                                    |                     | max | Unit                |    |

|--------------------------------------|---------------------|-------------------------------------------------------|---------------------|-----|---------------------|----|

| Maximum aupply voltage               | V <sub>DD</sub>     | $V_{DD} - V_{EE} \ge 12 \text{ V: } V_{DD}$           | 6.0                 |     | 18.5                | V  |

| Maximum supply voltage               | V <sub>EE</sub>     | $V_{DD} - V_{EE} \ge 12 \text{ V: } V_{EE}$           | -18.5               |     | 0                   | V  |

| Input high lovel veltage             | V <sub>IH</sub> 1   | DI, CL, CE                                            | 4.0                 |     | 18.5                | V  |

| Input high level voltage             | V <sub>IH</sub> 2   | S, RES                                                | 0.7 V <sub>DD</sub> |     | V <sub>DD</sub>     | V  |

| Input low level voltage              | V <sub>IL</sub> 1   | DI, CL, CE                                            | 0                   |     | 0.7                 | V  |

|                                      | V <sub>IL</sub> 2   | S, RES                                                | 0                   |     | 0.3 V <sub>DD</sub> | V  |

| Analog switch input<br>voltage range | V <sub>IN</sub>     | L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4 | V <sub>EE</sub>     |     | V <sub>DD</sub>     | V  |

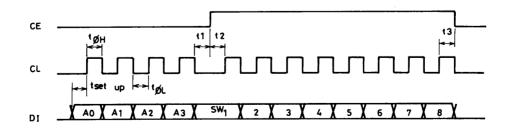

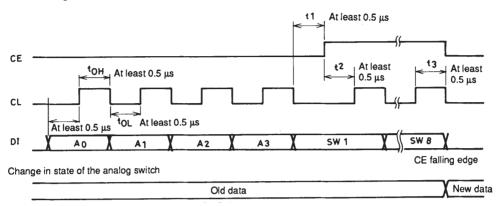

| Low level clock pulse width          | t <sub>øL</sub>     | CL                                                    | 0.5                 |     |                     | μs |

| High level clock pulse width         | t <sub>øH</sub>     | CL                                                    | 0.5                 |     |                     | μs |

| Setup time                           | t <sub>set up</sub> | CL, DI                                                | 0.5                 |     |                     | μs |

|                                      | t1*                 | CL, CE                                                | 0.5                 |     |                     | μs |

|                                      | t2*                 | CL, CE                                                | 0.5                 |     |                     | μs |

|                                      | t3*                 | CL, CE                                                | 0.5                 |     |                     | μs |

| Minimum reset pulse width            | twRES               | $V_{DD} \ge 6 \text{ V}: \overline{\text{RES}}$       | 1.0                 |     |                     | μs |

| Hysteresis                           | V <sub>H</sub>      | CL, CE, DI                                            | 0.3                 |     |                     | V  |

Note: \* CE, CL and DI waveforms

## Electrical Characteristics at Ta = 25°C, $V_{SS}$ = 0 V

| Parameter                                    | Symbol            | Conditions min                                                                                                                          |     | typ    | max  | Unit |

|----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|------|

|                                              | R <sub>ON</sub> 1 | I = 1 mA, $V_{DD} - V_{EE}$ = 12 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4                                            |     | 150    |      | Ω    |

| Analog switch on resistance                  | R <sub>ON</sub> 2 | I = 1 mA, $V_{DD} - V_{EE}$ = 37 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4                                            |     | 70     |      | Ω    |

| <b>-</b>                                     | THD1              | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, V <sub>DD</sub> - V <sub>EE</sub> = 37 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4 |     | 0.0015 | 0.01 | %    |

| Total harmonic distortion                    | THD2              | $V_{IN}$ = 0.1 Vrms, f = 1 kHz, $V_{DD} - V_{EE}$ = 37 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4                      |     | 0.01   | 0.05 | %    |

| Feedthrough                                  | F <sub>TH</sub>   | V <sub>IN</sub> = 0 dBV, f = 10 kHz, V <sub>DD</sub> - V <sub>EE</sub> = 37 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4 |     | 55     |      | dB   |

| Crosstalk                                    | СТ                | V <sub>IN</sub> = 0 dBV, f = 10 kHz, V <sub>DD</sub> - V <sub>EE</sub> = 37 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4,<br>RCOM1 to RCOM4 |     | 75     |      | dB   |

| Input high level current                     | IIH               | V <sub>I</sub> = 18.5 V: DI, CL, CE, S, <del>RES</del>                                                                                  |     |        | +10  | μA   |

| Input low level current                      | IIL               | V <sub>I</sub> = 0 V: DI, CL, CE, S, RES                                                                                                | -10 |        |      | μA   |

| Analog switch leakage current<br>(off state) | I <sub>OFF</sub>  | V <sub>I</sub> = V <sub>EE</sub> to V <sub>EE</sub> + 37 V:<br>L1 to L8, R1 to R8, LCOM1 to LCOM4, -10<br>RCOM1 to RCOM4                |     |        | +10  | μA   |

| Current drain                                | I <sub>DD</sub>   | V <sub>DD</sub>                                                                                                                         |     |        | 1.0  | mA   |

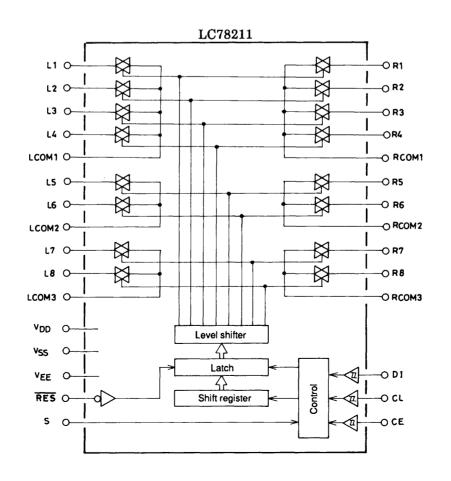

## **Equivalent Circuit Block Diagrams**

Continued from preceding page.

## **Pin Functions**

| The address is set                                                                                                                       | Schmitt buffe<br>k input<br>enable<br>f two chips            | r)                                                            | n the table                                                             | below acc                                                                         | ording to                                             |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------|

| Serial data input (<br>CLCloc<br>DIData<br>CEChip<br>Selection of one o<br>The address is set                                            | Schmitt buffe<br>k input<br>enable<br>f two chips            | r)                                                            | n the table                                                             | below acc                                                                         | ording to                                             |

| CLCloc<br>DIData<br>CEChip<br>Selection of one o<br>The address is set                                                                   | k input<br>input<br>enable<br>f two chips<br>t to the values |                                                               | n the table                                                             | below acc                                                                         | ording to                                             |

| The address is set                                                                                                                       | to the value                                                 | s shown ir                                                    | n the table                                                             | below acc                                                                         | ording to                                             |

| Selection of one of two chips<br>The address is set to the values shown in the table below according to<br>the level input to the S pin. |                                                              |                                                               |                                                                         |                                                                                   |                                                       |

| Product                                                                                                                                  | S pin<br>level                                               | $A_0$ $A_1$ $A_2$ $A_3$                                       |                                                                         |                                                                                   |                                                       |

|                                                                                                                                          | _                                                            | ů                                                             | · ·                                                                     | -                                                                                 | 1                                                     |

| LC78211                                                                                                                                  |                                                              |                                                               |                                                                         | -                                                                                 | 1                                                     |

|                                                                                                                                          |                                                              |                                                               | -                                                                       | -                                                                                 | 1                                                     |

| LC78212                                                                                                                                  |                                                              | -                                                             | -                                                                       | 1                                                                                 | 1                                                     |

|                                                                                                                                          | L                                                            | 0                                                             | 1                                                                       | 1                                                                                 | 1                                                     |

| LC78213                                                                                                                                  | Н                                                            | 1                                                             | 1                                                                       | 1                                                                                 | 1                                                     |

|                                                                                                                                          | LC78212<br>LC78213<br>Reset input<br>The states of the a     | LC78211 L<br>LC78212 L<br>LC78212 H<br>LC78213 L<br>LC78213 H | LC78211 L 0   LC78212 H 1   LC78213 L 0   LC78213 H 1   Reset input H 1 | LC78211 L 0 1   LC78212 H 1 1   LC78212 H 1 0   LC78213 L 0 1   Reset input H 1 1 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

## Operation

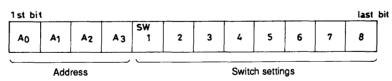

1. Data Input Procedure

The LC78211, LC78212 and LC78213 are controlled by inputting specified data to the CL, DI and CE pins. The input data consists of 12 bits, of which four bits are address and eight bits are data.

Bits correspond to the L1 to L8 and R1 to R8 analog switches, and a value of one turns the corresponding switch on, and a value of zero turns it off.

0.....Off

1.....On

The address is used when the chip is connected to a shared bus. The data (address) that must be transmitted depends on the S pin and the particular product as shown in the table below.

| Product | S pin | Address        |                |                |                |  |  |

|---------|-------|----------------|----------------|----------------|----------------|--|--|

|         | level | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> |  |  |

| LC78211 | L     | 0              | 1              | 0              | 1              |  |  |

|         | Н     | 1              | 1              | 0              | 1              |  |  |

| LC78212 | L     | 0              | 0              | 1              | 1              |  |  |

|         | Н     | 1              | 0              | 1              | 1              |  |  |

| LC78213 | L     | 0              | 1              | 1              | 1              |  |  |

|         | Н     | 1              | 1              | 1              | 1              |  |  |

Note: The bit for switch eight in the LC78213 is a "don't care" bit, that is it can be either 0 or 1 without affecting chip function. This is because the LC78213 has two sets of seven (not eight) circuits.

#### 2. DI, CL and CE Timing

Data is read in on the rising edge of CL and latched on the falling edge of CE.

3. Notes on the Reset Pin

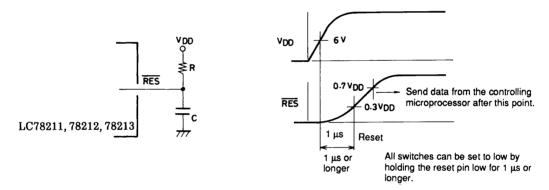

The states of the analog switches are undefined when power is first applied. However, it is possible to use the reset pin to force all switches to the off state by connecting an RC circuit to this pin.

4. Using a CCB Bus with Multiple ICs

The LC78211, LC78212 and LC78213 retain their prior state until they receive data with a matching address.

#### 5. Replacing Earlier Models

Caution is required when replacing an LC7821N, LC7823N and LC7823N with an LC78211, LC78212 and LC78213, since the S pin threshold levels differ.

#### 6. Handling of Unused Input Pins

We recommend connecting any unused switch pin to  $V_{SS}$  through a resistor of up to a few 100 k $\Omega$  to prevent damage from static electricity.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 1996. Specifications and information herein are subject to change without notice.