### TC5032P 6-DIGIT DECADE COUNTER

TC5032P is six digit decimal counter whose BCD output of each digit is dynamically output in sequence from the higher order digit on BCD OUTPUT in synchronism with SCAN input. As the carry outputs are available from all the digits, other counters and control circuits can be easily driven.

WWW.B

By using BC (Blanking Control) input, leading zero suppress from arbitrary digit can be achieved without external circuits.

Since the first stage counter can respond up to 10MHz (VDD=5 volts), this is also suitable for counting and frequency dividing of high frequency pulses.

#### ARSOLUTE MAXIMUM RATINGS

| CHARACTERISTIC               | SYMBOL            | RATING                       | UNIT |  |

|------------------------------|-------------------|------------------------------|------|--|

| DC Supply Voltage            | $v_{\mathrm{DD}}$ | Vss-0.5~Vss+10               | · v  |  |

| Input Voltage                | VIN               | $V_{SS}-0.5 \sim V_{DD}+0.5$ | v    |  |

| Output Voltage               | VOUT              | $V_{SS}-0.5 \sim V_{DD}+0.5$ | v    |  |

| DC Input Current             | IIN               | ±10                          | mA   |  |

| Power Dissipation            | PD                | 300                          | mW   |  |

| Storage Temperature<br>Range | Tstg              | -55~125                      | °C   |  |

| Lead Temp./Time              | Tsol              | 260°C · 10sec                |      |  |

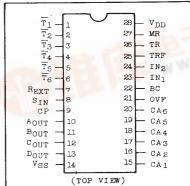

#### PIN ASSIGNMENT

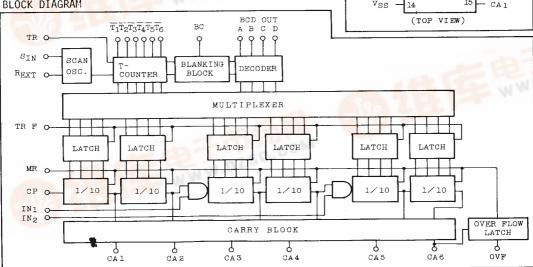

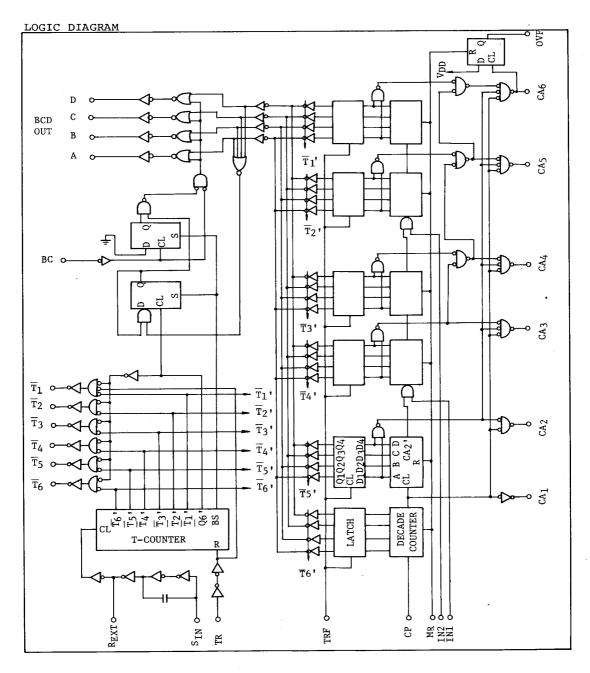

#### BLOCK DIAGRAM

PIN FUNCTION & NAME

| Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIN NO.  | SYMBOL                              | NAME                 | FUNCTION                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| through Dour, the Sequence is descending order from TI  with TR="H", all of TI through T6 become "H", and when TR falls, T1 becomes "L". Then, "L" is shifted in sequence TR, T5 T5  T5 T5 T6  T6 T6  T6 T6  RESISTOR EXTERNAL by externall clock is available, clock can be generated by externally connecting a resistor between S <sub>TM</sub> and R <sub>EYT</sub> . T-COUNTER CLOCK input. T-COUNTER changes its state at the rising edge of S <sub>TM</sub> .  PC CLOCK INPUT Decimal counter BCD output. When T1="L", the highest order digit (6th digit) is output. Then, 5th digit is output with T2="L", buring BLANKING, all the outputs become "H".  A-OUTPUT D-OUTPUT T6="L". During BLANKING, all the outputs become "H".  A-OUTPUT T6="L". During BLANKING, all the outputs become "H".  CA3 CARRY 1 Carry output "L" when count is "xxxxx6"—"xxxxxxy9" otherwise "H".  CA4 CARRY 4 digit "L" when count is "xxxxx6"—"xxxxxy9" otherwise "H".  CA5 CARRY 5 OVER FLOW OVER FLOW OVER FLOW  Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA5 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA6 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA5 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA7 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA7 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA7 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", otherwise "H".  CA7 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the counter is absoluted.  CA7 CARRY 6 Detection terminal of OVER FLOW condition of counter. When the digits are counted.  CA8 CARRY 6 THE | 1        | $\overline{\overline{\mathtt{T1}}}$ | <u>T1</u>            | Outputs to indicate the digit of output signals A                                                                                              |

| 3   T3   T4   T4   T4   T4   T5   T5   T5   T5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2        |                                     |                      | through D the Sequence is descending order from my                                                                                             |

| The fights of the counter of the lowest order digit.   The fights of the counter advances of the fights are counted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3        | m2                                  | <u></u>              | With TP="H" all of Tl through T6 become "HI and also                                                                                           |

| Text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | L        |                                     |                      | TP falls T1 becomes "I" Then "I" is shifted in account                                                                                         |

| Reststor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5        |                                     |                      | T2 T3 by each 4 clocks of S                                                                                                                    |

| REXT   RESISTOR   EXTERNAL   Leave open when an external clock is applied from S IN.   When no external clock is available, clock can be generated by externally connecting a resistor between S IN and R R IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                     |                      | In.                                                                                                                                            |

| SAT   SATE   When no external clock is available, clock can be generated by externally connecting a resistor between SIN and RENT. T-COUNTER CLOCK input. T-COUNTER changes its state at the rising edge of SIN.    10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6        | Т6.                                 | <u>T6</u>            |                                                                                                                                                |

| T-COUNTER CLOCK input. T-COUNTER changes its state at the rising edge of S <sub>IN</sub> .  The rising edge of S <sub>IN</sub> .  Decimal counter BCD output. When TI="L", the highest order digit.  A-OUTPUT D-OUTPUT C-OUTPUT D-OUTPUT          | 7        | R <sub>EXT</sub>                    |                      | When no external clock is available, clock can be generated by externally connecting a resistor between S <sub>TM</sub> and R <sub>PVT</sub> . |

| Decimal counter BCD output. When T1="L", the highest order digit (6th digit) is output. Then, 5th digit is output order digit (6th digit) is output. Then, 5th digit is output with T2="L", 4th digit with T3="L",, 1st digit with T6="L". During BLANKING, all the outputs become "H".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8        | SIN                                 | SCAN INPUT           | T-COUNTER CLOCK input. T-COUNTER changes its state at                                                                                          |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9        | CP                                  | CLOCK INPUT          | Decimal counter clock input for the lowest order digit.                                                                                        |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11<br>12 | A<br>BOUT<br>COUT<br>DOUT           | B-OUTPUT<br>C-OUTPUT | order digit (6th digit) is output. Then, 5th digit is output with T2="L", 4th digit with T3="L",, 1st digit with                               |

| CA1   CARRY 1   CARRY 2   CARRY 2   CARRY 2   CARRY 2   CARRY 3   The count is "xxxxx96"\"xxxxy99", otherwise "H".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14       |                                     | V                    | (CND)                                                                                                                                          |

| CARRY 2   CARRY 2   CARRY 2   Towns   Carry output   Carry output   Towns   Carry output                                   |          |                                     |                      |                                                                                                                                                |

| 17   CA3   CARRY 3   from n-th digit   Tu when count is "xxx996"\"xxx9999", otherwise "H".     19   CA5   CARRY 5       20   CA6   CARRY 6       21   OVF   OVER FLOW   Detection terminal of OVER FLOW condition of counter.     When the count is "y99996"\"y999999", otherwise "H".     Once it has become "H", only MR can restore it to "L".     22   BC   BLANKING CONTROL   "H"   Zero suppress for all the digits.     "L" No zero suppress.   If Tn is connected to BC, zero suppress is activated for the higher order digits than (n-1)th digit.     23   IN1   INPUT 1   "H"   All the digits are counted.     "L" Only the lower order two digits are counted.     "L" Only the lower order four digits are counted.     "L" Only the lower order four digits are counted.     "L" Only the lower order four digits are counted.     "L" Counter output is transferred to the multiplexer as it is.     "L" Counter output at the falling edge of TRF is latched.     T-COUNTER RESET                                    |          |                                     |                      |                                                                                                                                                |

| CA4   CARRY 4   digit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | CAZ                                 | CARRY Z              | output "L" when count is "xxxx96"~"xxxx99", otherwise "H".                                                                                     |

| CAS   CARRY 5   digit   L when count is "x99996" x99999", otherwise "H".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1/       |                                     | CARRY 3              | "L" when count is "xxx996"\"xxx999", otherwise "H".                                                                                            |

| CARRY 6  CARRY 6  CARRY 6  OVER FLOW  Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", it becomes "H". Once it has become "H", only MR can restore it to "L".  BC BLANKING CONTROL  "H" Zero suppress for all the digits. "L" No zero suppress. "L" No zero suppress. "If Tn is connected to BC, zero suppress is activated for the higher order digits than (n-1)th digit.  INPUT 1  "H" All the digits are counted. "H" All the digits are counted. "H" All the digits are counted. "H" Decimal counter output is transferred to the multiplexer as it is. "L" Counter output at the falling edge of TRF is latched.  T-counter is initialized to Tl by "H" level input and Tretains "H" level only for the period of TR="H".  "H" level input resets the counter to count "000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18       |                                     |                      | L when count is xxyyyo ~ xxyyyy otherwise "H".                                                                                                 |

| Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", it becomes "H". Once it has become "H", only MR can restore it to "L".  BC BLANKING CONTROL "H" all the digits. "L" No zero suppress. "L" No zero suppress. If Tn is connected to BC, zero suppress is activated for the higher order digits than (n-1)th digit.  INPUT 1 "H" All the digits are counted.  INPUT 2 "H" All the digits are counted.  "IT Only the lower order two digits are counted.  "IT Only the lower order four digits are counted.  "H" Decimal counter output is transferred to the multiplexer as it is.  "L" Counter output at the falling edge of TRF is latched.  T-counter is initialized to Tl by "H" level input and Tl retains "H" level only for the period of TR="H".  "H" Level input resets the counter to count "0000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | CA5                                 | CARRY 5              | L' when count is "xyyyy6" vxyyyyy", otherwise "H".                                                                                             |

| Detection terminal of OVER FLOW condition of counter. When the counter advances by one from "999999", it becomes "H". Once it has become "H", only MR can restore it to "L".  BC BLANKING CONTROL "H" Zero suppress for all the digits. "L" No zero suppress.  IND INPUT 1 "H" All the digits are counted.  "L" Only the lower order two digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "H" Decimal counter output is transferred to the multiplexer as it is. "L" Counter output at the falling edge of TRF is latched.  T-counter is initialized to Tl by "H" level input and Tl retains "H" level only for the period of TR="H".  "H" Level input resets the counter to count "0000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20       | CA6                                 | CARRY 6              | "L" when count is "999996"~"999999", otherwise "H".                                                                                            |

| 22 BC CONTROL "L" No zero suppress. press is activated for the higher order digits than (n-1)th digit.  23 IN1 INPUT 1 "H" All the digits are counted.  "L" Only the lower order two digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "H" Decimal counter output is transferred to the multiplexer as it is.  "L" Counter output at the falling edge of TRF is latched.  26 TR T-COUNTER RESET T-counter is initialized to Tl by "H" level input and Tl retains "H" level only for the period of TR="H".  27 MR MASTER RESET "H" level input resets the counter to count "0000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21       | OVF                                 | OVER FLOW            | When the counter advances by one from "999999", it becomes "H". Once it has become "H", only MR can restore it to "L".                         |

| INPUT 2  "L" Only the lower order two digits are counted.  "H" All the digits are counted.  "L" Only the lower order four digits are counted.  "L" Only the lower order four digits are counted.  "H" Decimal counter output is transferred to the multiplexer as it is.  "L" Counter output at the falling edge of TRF is latched.  T-counter is initialized to Tl by "H" level input and Tl retains "H" level only for the period of TR="H".  MR MASTER RESET "H" level input resets the counter to count "0000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22       | ВС                                  |                      | all the digits.  press is activated for the higher                                                                                             |

| INPUT 2   "H" All the digits are counted.   "L" Only the lower order four digits are counted.   "L" Only the lower order four digits are counted.   "H" Decimal counter output is transferred to the multiplexer as it is.   "L" Counter output at the falling edge of TRF is latched.   TR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23       | IN1                                 | INPUT 1              |                                                                                                                                                |

| TRANSFER  "H" Decimal counter output is transferred to the multiplexer as it is.  "L" Counter output at the falling edge of TRF is latched.  TRESET  T-COUNTER RESET  T-counter is initialized to Tl by "H" level input and Tl retains "H" level only for the period of TR="H".  "H" Decimal counter output is transferred to the multiplexer as it is.  "L" Counter output at the falling edge of TRF is latched.  T-counter is initialized to Tl by "H" level input and of TR="H".  "H" level input resets the counter to count "0000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24       | IN2                                 | INPUT 2              | "H" All the digits are counted. "L" Only the lower order four digits are counted.                                                              |

| RESET Tl retains "H" level only for the period of TR="H".  MR MASTER RESET "H" level input resets the counter to count "0000000" and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25       | TRF                                 | TRANSFER             | "H" Decimal counter output is transferred to the multiplexer as it is.                                                                         |

| and OVER FLOW to "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26       | TR                                  |                      |                                                                                                                                                |

| 28 V <sub>DD</sub> V <sub>DD</sub> power supply (3-8 volts)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27       |                                     | RESET                | "H" level input resets the counter to count "000000" and OVER FLOW to "L".                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28       | $v_{_{ m DD}}$                      | V <sub>DD</sub>      | V <sub>DD</sub> power supply (3~8 volts)                                                                                                       |

#### OPERATING CONSIDERATION

#### \* Count Operation

Set input terminals IN1, IN2 and TRANSFER to "H" and apply "H" level to M-RESET terminal, then return it to "L" level. If pulse is fed to CLOCK terminal in this condition, the counter advances its count at the rising edge of CLOCK up to 999999.

Since CARRY outputs from all the digits are output in negative logic, the control of other CMOS logics can be easily achieved.

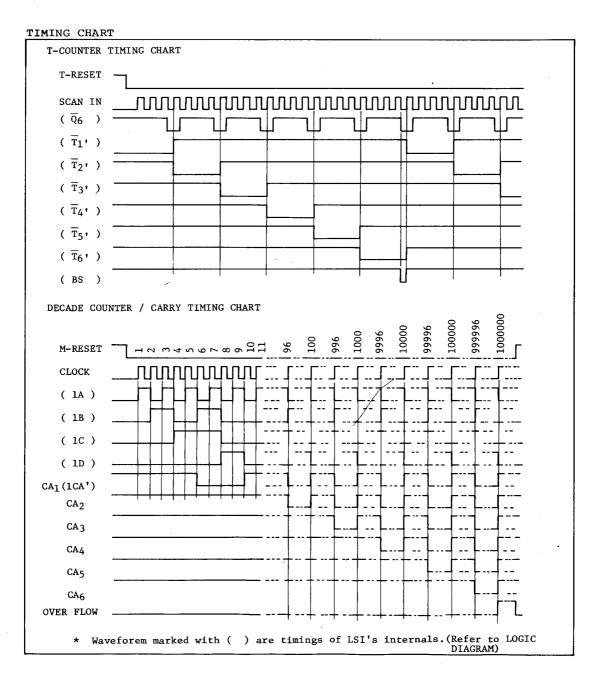

$\overline{\text{CA1}}$  -  $\overline{\text{CA6}}$  are output with "L" level for four clock periods. (Refer to the timing chart.)

If one more clock is given in the count of 999999, OVER FLOW terminal becomes "H" indicating the overflow condition of COUNTER. Once OVER FLOW terminal has become "H", it will never return to "L" unless M-RESET is applied.

#### \* Latch Operation

When the level of TRANSFER terminal is "H", the counter output is transferred to the multiplexer as it is with the output always indicating the counter output, but if TRANSFER terminal changes the level from "H" to "L", the count output which has been being output immediately prior to the falling edge of TRANSFER is stored in the latch and even if the counter output varies,  $A_{\rm OUT}$  -  $D_{\rm OUT}$  will not vary.

If TRANSFER terminal is returned to "H" again, the correct counter output appears on AQUT - DQUT.

#### Scan Operation

BCD outputs of all digits are output to common  $A_{\rm OUT}$  -  $D_{\rm OUT}$  on the time sharing basis and the basic clock for this operation is fed from outside to SCAN IN (leaving  $R_{\rm EXT}$  open in this case) or obtained by connecting a resistor between  $R_{\rm EXT}$  and SCAN IN.

BCD output for each digit appears on AOUT - DOUT corresponding to each digit of 6 digit scan signals (digit signals) which are in synchronism with the rising edge of SCAN IN. The digit output for digit selection is output with "L" level on  $\overline{T_1}$  -  $\overline{T_6}$ . As BCD outputs are output starting from the highest order digit  $(\overline{T_1}-6\text{th}\ \text{digit},\ldots,\overline{T_6}-1\text{st}\ \text{digit})$ , data transfer can be easily achieved.

\* The relationship between external resistor between REXT and SCAN IN and oscillating frequency is given below

$$f \ \ \stackrel{\cdot}{\div} \ \ \frac{1}{44 \times R} \times \ 10^{12} \ \ [\text{Hz}]$$

## \* Blanking

By controlling BLANKING CONTROL terminal, leading zero suppress to an arbitrary digit can be easily achieved. When zero suppress is activated, all of  $A_{\rm OUT}$  -  $D_{\rm OUT}$  become "H".

BC Terminal and Zero Suppress

| BRANKING CONTROL                    | Leading Zero Suppress                                                                             |   |

|-------------------------------------|---------------------------------------------------------------------------------------------------|---|

| L                                   | No zero suppress                                                                                  |   |

| Н                                   | Zero suppress for all digits                                                                      | * |

| Connected to T6                     | Zero suppress for five higher order digits and no zero suppress for the lowest order digit.       | * |

| Connected to T5                     | Zero suppress for four higher order digits and no zero suppress for two lower order digits.       | * |

| Connected to $\overline{\text{T4}}$ | Zero suppress for three higher order digits and no zero suppress for three lower order digits.    |   |

| Connected to T <sub>3</sub>         | Zero suppress for two higher order digits and no zero suppress for four lower order digits.       | * |

| Connected to $\overline{T_2}$       | Zero suppress for the highest order digit<br>and no zero suppress for five lower order<br>digits. | * |

<sup>\*</sup> When carry is generated from lower order digit, the normal output may not be obtained only one cycle of T-COUNTER.

# RECOMMENDED OPERATING CONDITIONS ( $V_{SS}^{=OV}$ )

| CHARACTERISTIC                       | SYMBOL          | MIN. | TYP. | MAX.            | UNIT |

|--------------------------------------|-----------------|------|------|-----------------|------|

| Supply Voltage                       | V <sub>DD</sub> | 3    | -    | 8               | V    |

| Input Voltage                        | v <sub>IN</sub> | 0    | -    | V <sub>DD</sub> | V    |

| Operating Temperature                | Topr            | -30  | _    | 85              | °C   |

| R <sub>EXT</sub> External Registance | e R<br>EXT      | 20K  | -    | 10M             | Ω    |

# ELECTRICAL CHARACTERISTICS $(V_{SS}=OV)$

|                                  |            |                      | 55                          |                 |      |       |      |                  |       |      |      |      |

|----------------------------------|------------|----------------------|-----------------------------|-----------------|------|-------|------|------------------|-------|------|------|------|

| CHARACTERISTIC                   |            | CVIMO                | TEST                        | V <sub>DD</sub> | -3   | 30°C  |      | 25°C             |       | 85   | °C   | UNIT |

| CHARACT                          | EKISTIC    | SYMBOL               | CONDITIONS                  | (V)             | MIN. | MAX.  | MIN. | TYP.             | MAX.  | MIN. | MAX. | 1    |

| Output                           | High Level | V <sub>OH</sub>      | I <sub>OH</sub> =-1μA       | 5               | 4.95 | -     | 4.95 | _                | -     | 4.95 | -    | v    |

| Voltage                          | Low Level  | $v_{OL}$             | I <sub>OL</sub> =1µA        | 5               | -    | 0.05  | -    | -                | 0.05  | _    | 0.05 | 1 '  |

| Output                           | High Level | IOH                  | $V_{OH} = 2.5V$             | 5               | -0.7 | -     | -0.6 | -2               | _     | -0.5 | _    |      |

| Current                          | Low Level  | IOI                  | $v_{OL} = 0.4v$             | 5               | 0.52 | -     | 0.44 | 1.3              | _     | 0.36 | _    | mA   |

| Input                            | High Level | V <sub>TH</sub>      | V <sub>OUT</sub> =0.5V,4.5V | 5               | 3.5  | -     | 3.5  | 2.75             | _     | 3.5  | _    |      |

| Voltage                          | Low Level  | $v_{_{\mathbf{IL}}}$ | $V_{OUT}^{=0.5V,4.5V}$      | 5               | _    | 1.5   | -    | 2.25             | 1.5   | _    | 1.5  | V    |

| Input                            | High Level | I                    | V <sub>IH</sub> =8V         | 8               | -    | 0.15  | -    | _                | 0.15  | -    | 1.0  | μA   |

| Current                          | Low Level  | IL                   | V <sub>IL=0V</sub>          | 8               | 1    | -0.15 | -    | _                | -0.15 | _    | -1.0 | μΩ   |

| Quiescent Current<br>Consumption |            | I <sub>DD</sub>      | At all                      | 5               | -    | 0.4   | _    | 10-5             | 0.4   | -    | 0.8  | mA   |

|                                  |            | עע                   | conditions                  | 8               |      | 0.5   | _    | 10 <sup>-5</sup> | 0.5   | _    | 1.0  | uu 1 |

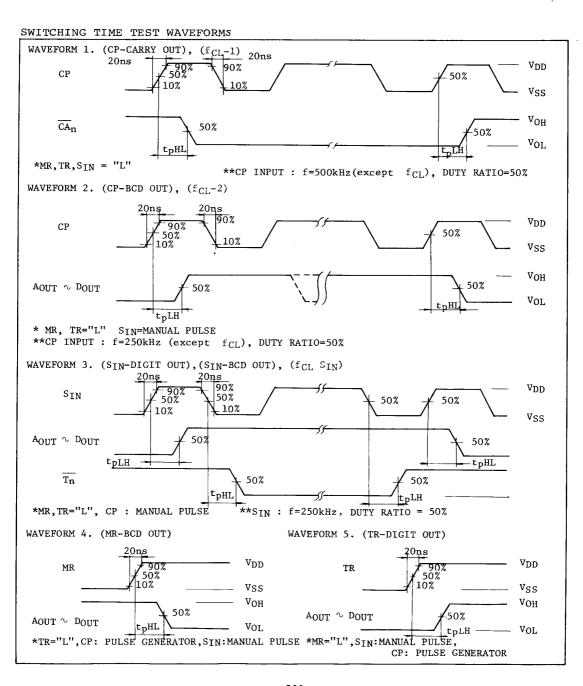

# SWITCHING CHARACTERISTICS (Ta=25°C, $V_{SS}$ =OV, $C_L$ =15 $_p$ F)

|                      |                    | 22                                    | <u> </u>            |      |       |      |      |

|----------------------|--------------------|---------------------------------------|---------------------|------|-------|------|------|

| CHARACTERISTIC       | SYMBOL             | TEST CONDITIONS                       | V <sub>DD</sub> (V) | MIN. | TYP.  | MAX. | UNIT |

| Propagation Delay    | l t                | $(\overline{T6} = L)$                 | 5                   | -    | 800   | 2000 |      |

| Time                 | pLH,               | $(\overline{T5} = L)$                 | 5                   |      | 1000  | 2200 |      |

| (CD DCD OVEN)        | t                  | $(\overline{T4} = L)$                 | 5                   | -    | 1250  | 2500 |      |

| (CP - BCD OUT)       | PHL                | $(\overline{T3} = L)$                 | 5                   | -    | 1500  | 3000 | ns   |

|                      |                    | $(\overline{T2} = L)$                 | 5                   | _    | 1750  | 3500 |      |

|                      |                    | (T1 = L)                              | 5                   | -    | 2000  | 4000 |      |

| Propagation Delay    |                    | CA1                                   | 5                   |      | (200) | 500  |      |

| Time                 | t <sub>pLH</sub> , | CA2                                   | 5                   | _    | (200) | 500  |      |

| (GD GARRY CYTT)      | pLn,               | CA3                                   | 5                   | _    | (250) | 750  | ns   |

| (CP - CARRY OUT)     | t <sub>pHL</sub>   | CA4                                   | 5                   | -    | (250) | 750  | 113  |

|                      | ',                 | CA5                                   | 5                   | -    | (300) | 1000 | ı    |

|                      |                    | CA6                                   | 5                   | -    | (300) | 1000 |      |

| Max. Clock Rise Time | trø                | CD IN IN                              | 5                   | 20   | _     | _    | μs   |

| Max. Clock Fall Time | t <sub>fø</sub>    | CP, IN <sub>1</sub> , IN <sub>2</sub> |                     | 20   | _     | -    | μΒ   |

| Min. Clear Pulse     | tw(MR)             | MASTER RESET                          | 5                   | -    | -     | 500  |      |

| Width                | tw(TR)             | T-COUNTER RESET                       |                     | -    | - 1   | 400  | ns   |

| SWITCHING | CHARACTERISTICS | $(Ta=25^{\circ}C,$ | $v_{ss} = ov$ , | $C_{T} = 15_{p}F$ |

|-----------|-----------------|--------------------|-----------------|-------------------|

|-----------|-----------------|--------------------|-----------------|-------------------|

|                    |             |                                    |                 | <u> </u>            | <u> </u> |      |      |      |  |

|--------------------|-------------|------------------------------------|-----------------|---------------------|----------|------|------|------|--|

| CHARACTE           | ERISTIC     | SYMBOL                             | TEST CONDITIONS | V <sub>DD</sub> (V) | MIN.     | TYP. | MAX. | UNIT |  |

| Propaga-           | (High-Low   | tpHL                               | MR-BCD OUT      | 5                   | _        | _    | 2000 |      |  |

| tion<br>Delay Time | (Low-High   | ) t <sub>pLH</sub>                 | TR-DIGIT OUT    | 5                   | -        | _    | 1500 |      |  |

| Í                  | Propagation |                                    | SIN-BCD OUT     | 5                   | _        | 1000 | 2500 | ns   |  |

| Delay T            |             | t <sub>pLH</sub> ,t <sub>pHL</sub> | SIN-DIGIT OUT   | 5                   | -        | 500  | 1000 |      |  |

|                    |             |                                    | CLOCK IN *      | 5                   | 10.0     | 14.0 |      |      |  |

| Max. Frequency     |             | f <sub>CL</sub> -2                 | 22001111        | 5                   | 1.0      | 2.0  | _    | MHz  |  |

|                    |             | f <sub>CL</sub> S <sub>IN</sub>    | SCAN IN         | 5                   | 0.5      | -    | -    |      |  |

<sup>\*</sup> f<sub>CL</sub>-1; Clock burst mode.

f<sub>CL</sub>-2; BCD outputs enable.

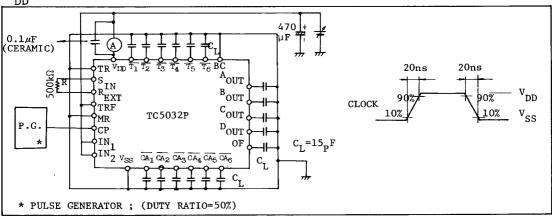

I DD TEST CIRCUIT

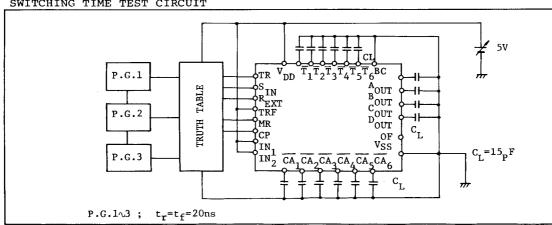

### SWITCHING TIME TEST CIRCUIT