查询Q3236I20N供应商

# Q3236

# PHASE-LOCKED LOOP FREQUENCY SYNTHESIZER

捷多邦,专业PCB打样工厂,24小时加急出货

#### **FEATURES**

- Backwards Compatible with the Q3036 and Q3216 PLL Chips

- Phase Noise Contributions as Low as

-154 dBc/Hz at 100 Hz from Carrier

- < 0.6 W Power Consumption Nominal</li>

- On-chip +10/11 Prescaler

- Single +5 V Supply Operation

- Wide Input Sensitivity Range:

-10 to +3.5 dBm

- Programmable via 16 TTL/CMOS-Compatible

Parallel Inputs, 8-Bit Data Bus, or Serial Loading

- 100 MHz Phase/Frequency Detector

- High Gain Linearized Phase/Frequency Detector (No Dead Zone): 302 mV/Rad

- · Out-of-Lock Indication

- VCO Division Ratios in Unit Steps:

For Serial and 8-bit Bus Mode:

2 to 5135 up to 300 MHz or

90 to 5135 to 2.0 GHz

For Direct Parallel Mode:

2 to 1295 up to 300 MHz or 90 to 1295 to 2.0 GHz

- Reference Division Ratios of 1 to 16 in Direct Parallel Mode, or 1 to 64 in Serial and 8-bit Bus Mode

- Programmability for Faster Multiplexing between Two Pre-loaded Frequencies

- Evaluation Board Available Q0420

## **APPLICATIONS**

- Cellular Base Stations

- Mobile/Airborne Communications

- Frequency Hopping Systems

- · Digital Radios and Modems

- · High Performance Test Equipment

- Local Oscillator Generation for VSAT, DBS, and GPS Applications

- RADAR and Missile Local Oscillators

- Paging Systems

8-1 QUALCOMM Incorporated, ASIC Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA Synthesizer Products Data Book, 80-24127-1 A, 8/97 Data Subject to Change Without Notice

f.dzsc.com

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556

# **CONTENTS**

| GENERAL DESCRIPTION                                            | 8-4  |

|----------------------------------------------------------------|------|

| FUNCTIONAL OVERVIEW                                            |      |

| Differential Line Receivers                                    | 8-5  |

| VCO Divider                                                    | 8-6  |

| Reference Divider                                              | 8-7  |

| Digital Phase/Frequency Detector                               | 8-7  |

| Digital Processor Interface (DPI) Modes                        |      |

| Enhanced Operation or Q3036 Mode                               | 8-9  |

| Direct Parallel Input Mode                                     | 8-9  |

| 8-bit Bus Mode                                                 | 8-9  |

| Serial Bus Mode                                                | 8-9  |

| 8-bit Bus or Serial Bus Frequency Multiplexing: Ping-Pong Mode | 8-10 |

| TECHNICAL SPECIFICATIONS                                       | 8-12 |

| INPUT/OUTPUT SIGNALS                                           | 8-17 |

| APPLICATION INFORMATION                                        | 8-21 |

| General                                                        | 8-21 |

| VCO/Reference Input Connections                                | 8-21 |

| Programming the Binary Counters                                |      |

| Calculating Loop Filter Component Values                       | 8-21 |

| Loop Stability Analysis                                        | 8-22 |

| Op Amp Finite Gain/Bandwidth                                   | 8-23 |

| Pre-Integrator Filtering                                       | 8-23 |

| Digital Phase Detector Sampling Delay                          | 8-24 |

| Additional Reference Suppression Filtering                     | 8-24 |

| Stability Analysis (Revisited) and Closed Loop Response        | 8-26 |

| Synthesizer Output Spectrum                                    | 8-29 |

| FREQUENCY SYNTHESIZER DESIGN CONSIDERATIONS WITH THE Q3236     | 8-30 |

| General Electromagnetic Issues                                 | 8-30 |

| VCO And Reference Line Receiver Input Minimum Edge Rates       | 8-31 |

| Phase/Frequency Detector Considerations                        | 8-32 |

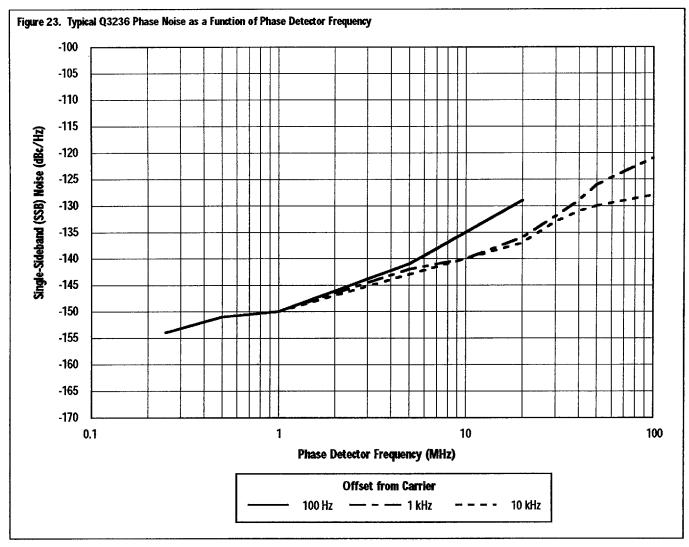

| Phase Noise Performance Considerations                         | 8-33 |

| Settling Time Considerations                                   | 8-36 |

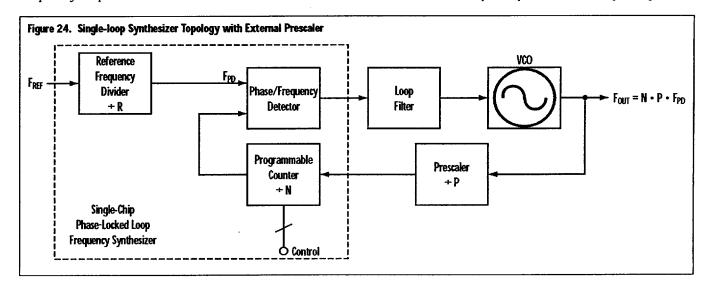

| Using External Prescalers for Higher Frequency Translation     |      |

| Q3036 TO Q3236 MIGRATION                                       | 8-39 |

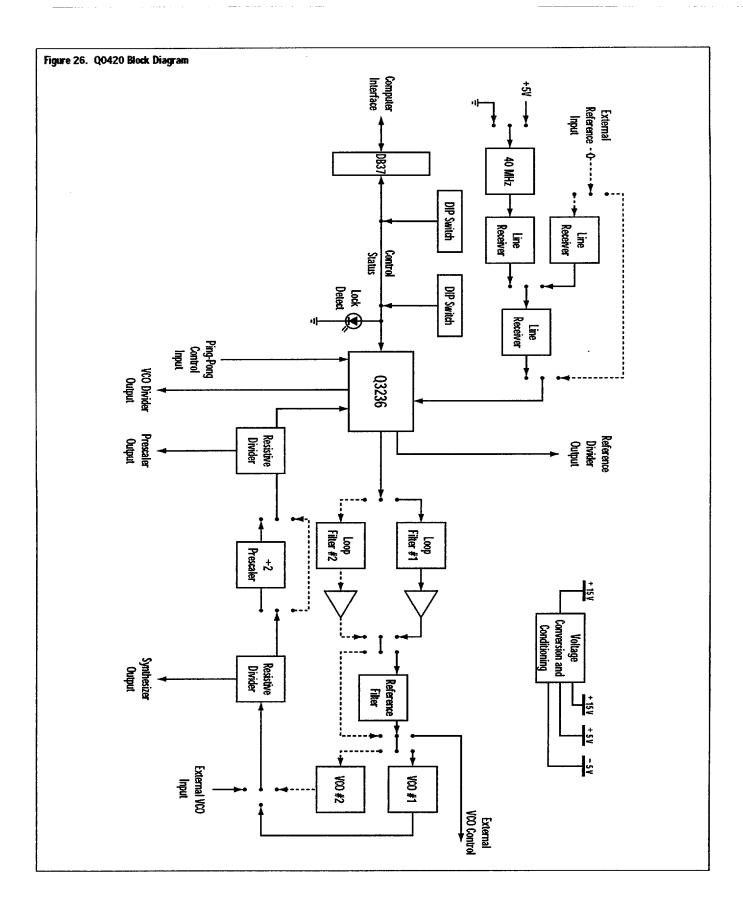

| Q0420 PLO EVALUATION SYSTEM                                    | 8-40 |

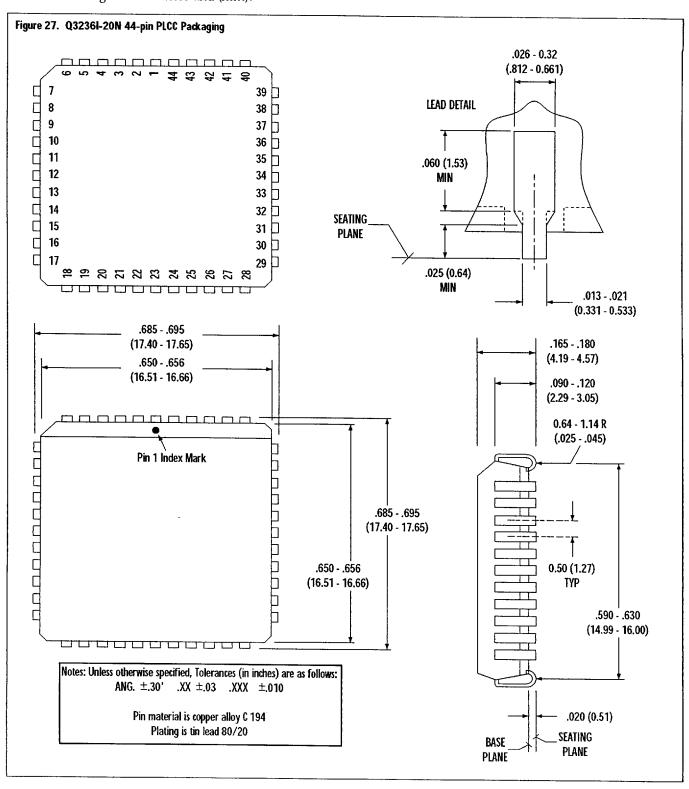

| PLCC PACKAGING                                                 | 8-42 |

| RECOMMENDED SOCKETS                                            | 8-43 |

| REFERENCES                                                     | 8-43 |

QUALCOMM Incorporated, ASIC Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA Synthesizer Products Data Book, 80-24127-1 A, 8/97 Data Subject to Change Without Notice 8-2 http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556

#### GENERAL DESCRIPTION

The Q3236 is a low power, single chip solution for Phase-Locked Loop (PLL) Frequency Synthesizers. Requiring only a single +5 V supply, the Q3236 contains all the necessary elements – with the exception of the VCO and loop filter components – to build a PLL frequency synthesizer operating from UHF through L-Band, and is also backwards compatible with the Q3036 and Q3216 devices as a replaceable part.

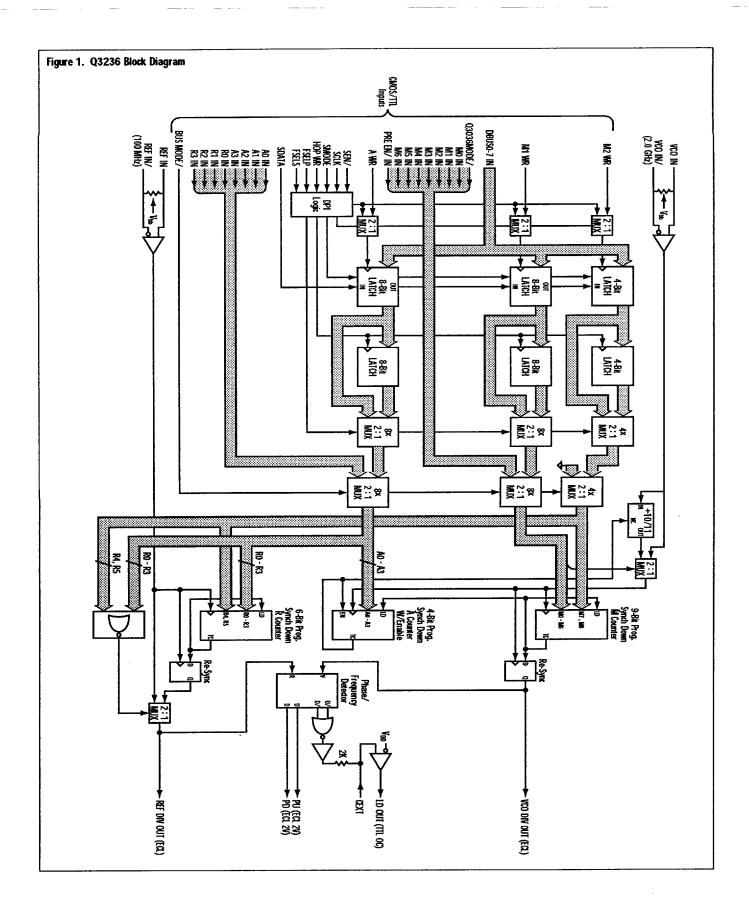

The block diagram for the Q3236 is shown in Figure 1. Its major components, listed below, are described in detail in the *Functional Overview* section.

- High Speed Line Receivers

- +10/11 Dual Modulus Prescaler

- 9-bit M and 4-bit A Pulse Swallow Counters

- 6-bit Reference Counter

- Digital Phase/Frequency Comparator

- Out-of-Lock Detection Circuitry

- TTL/+5 V CMOS-Compatible Parallel, Serial, or 8-bit Data Bus Interface.

The Q3236 is fabricated using a three metalization layer, single polysilicon oxide-isolated Bi-CMOS process. Its architecture provides breakthrough prescaler performance for high frequency operation,

permitting PLL designs with smaller VCO division ratios. The Q3236 design makes possible wider loop bandwidths yielding faster settling times and lower VCO phase noise contributions.

The parallel interface permits hardwiring the Q3236 for applications without the requirement of a processor. The +10/11 prescaler can be bypassed selectively to make two divide modes possible. When the +10/11 prescaler is enabled, frequency divide ratios can be achieved from 90 to 5135, in unit steps, from DC to 2.0 GHz when operating in Serial or 8-bit Bus Interface Modes. Direct Parallel interface allows divide ratios from 90 to 1295 in unit steps up to 2.0 GHz. In the Non-prescaler Mode, it is possible to divide inputs directly up to 300 MHz by 2 to 512, in unit steps when operating in Serial or 8-bit Bus interface and from 2 to 128 using Direct Parallel interface.

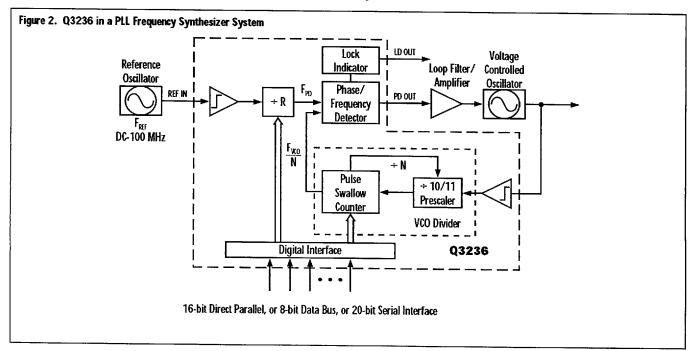

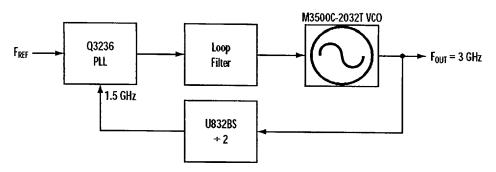

Similarly, the reference counter allows the reference input frequency to be divided directly in ratios of 1 to 64 with the Serial or 8-bit Bus interface and from 1 to 16 using Direct Parallel interface. As shown in Figure 2, the Q3236's highly integrated architecture greatly simplifies the design of UHF through L-Band synthesizers.

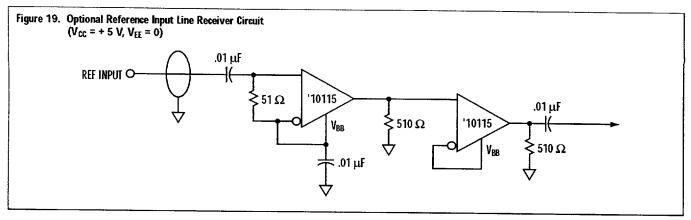

# FUNCTIONAL OVERVIEW DIFFERENTIAL LINE RECEIVERS

The VCO and reference frequency divider chains are clocked by their respective input clock signals, which have been processed by their differential line receivers. The line receiver inputs are externally AC coupled and can be driven differentially or single ended, where the unused input is de-coupled to ground.

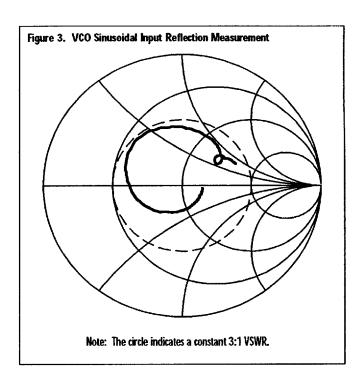

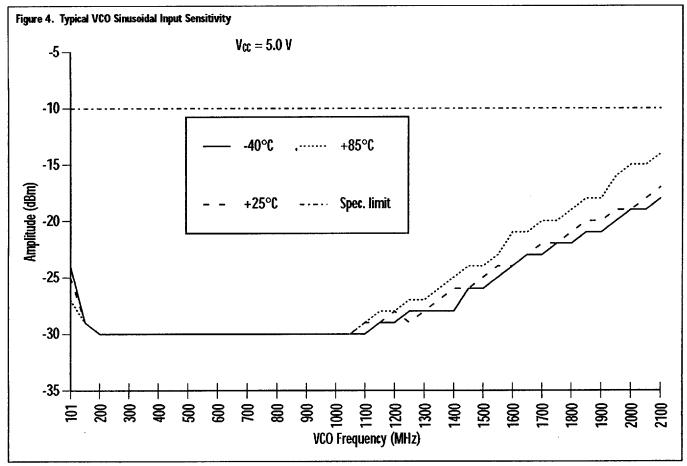

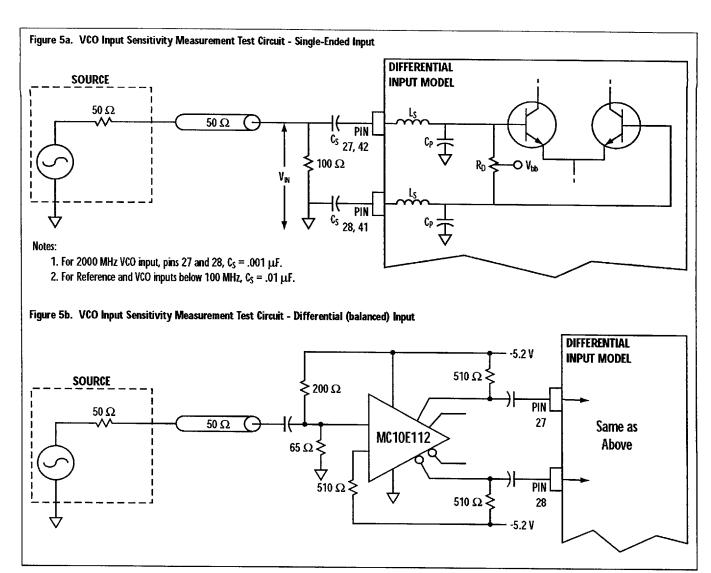

When configured this way, the VCO input has a guaranteed sinusoidal input sensitivity of -10 dBm (200 mV<sub>P-P</sub> from a 50  $\Omega$  source) in the range 20 MHz to 2.0 GHz, and an input VSWR of less than 3:1. Typical VSWR and sensitivity measurements are shown in Figures 3 and 4. They were obtained using the test circuit in Figure 5a. The reference input operates in a similar manner in the range 20 MHz to 100 MHz. Below 20 MHz, square wave signals are recommended (see Frequency Synthesizer Design Considerations with the Q3236section).

# **VCO DIVIDER**

The VCO frequency division chain is used to divide the VCO IN (pin 27) frequency,  $F_{VCO}$ , down to the phase detector frequency,  $F_{PD}$ . It operates in two modes. In the first mode, Prescaler Mode (PRE EN/ = "Low") up to 2.0 GHz, frequency division is accomplished with a pulse-swallow counter made up of the 10/11 front-end dual modulus prescaler (DMP), the 4-bit A counter and the 9-bit M counter. This mode, selected by the pulse-swallow counter, effectively implements a programmable divide-by N counter at the VCO frequency, even though only the DMP is operating at that frequency. The total VCO input frequency division ratio, N, obtained from programming the binary M and A counters is given by:

$$N = F_{VCO}/F_{PD}$$

= 10 \* (M + 1) + A, for A \le M + 1, M \neq 0 (1)

When operating in the Prescaler Mode, programming of control inputs via the 8-Bit Bus or Serial Bus interface utilizes access to all nine M counter bits, M0 - M8, and provides continuous integer divide ratios from 90 to 5135. Programming of control inputs via the Direct Parallel interface does not utilize the M7 and M8 counter bits since these are not provided from external inputs. Therefore, the Direct Parallel Mode allows the resulting 7-bit M counter to provide continuous integer divide ratios from 90 to 1295.

With the M counter set to a binary value of "0", the VCO input division chain is disabled; this, in turn, will cause the phase detector outputs, PD U and

8-6

PD D, to go to an ECL 2 V "High" and "Low' state, respectively. However, the following non-continuous division ratios in the Prescaler Mode are possible:

Given a value for N, the binary values, M and A, are determined as follows:

$$M = integer \{N/10\} - 1$$

(2)

and

$$A = N - 10 * (M + 1)$$

(3)

In the alternate mode, Non-prescaler Mode, (PRE EN/ = "High"), the prescaler is bypassed so that the VCO input frequency is divided directly by the M counter. The counter operates at frequencies up to 300 MHz. In this mode, frequency division ratio is determined by:

$$(F_{VCO}/F_{PD}) = M + 1, M \neq 0$$

(4)

Where M=1,...,511 is the binary value programmed to the M0 - M8 inputs of the M counter and the values programmed to the A0 - A3 inputs of the A counter are ignored.

As in the previous mode, programming via the 8-Bit Bus or Serial Bus interface will allow divide ratios of 2 to 512, while programming via the Direct Parallel interface will allow divide ratios of 2 to 128. Finally, the output of the VCO frequency division chain is available as the VCO DIV OUT signal (pin 30). It is a pseudo ECL-level emitter follower output, which requires a pull down resistor (between 500 and 1000  $\Omega$  typical) and directly interfaces to ECL logic. It is referenced to +5 V and GND. The waveform is a digital pulse with a frequency of  $F_{PD}$  and duty cycle of 10/N in Prescaler Mode, and 1/N in Non-prescaler Mode.

# REFERENCE DIVIDER

The reference frequency division chain is used to divide the REF IN (pin 42) frequency,  $F_{REF}$ , down to the phase detector frequency,  $F_{PD}$ , using the 6-bit R counter. The counter operates at frequencies up to 100 MHz and frequency division ratio is determined by

$$(F_{REF}/F_{PD}) = R + 1 \tag{5}$$

Where R = 0,..., 63 is the binary value programmed to the R0 - R5 inputs of the R counter.

As in the case with the VCO Divider, programming of control inputs via the 8-Bit Bus or Serial Bus interface utilizes access to all six R counter bits and permits divide ratios of 1 to 64. Programming of control inputs via the Direct Parallel interface does not utilize the R4 and R5 counter bits since these are not provided from external inputs. Therefore, this allows the resulting 4-bit R counter to provide divide ratios from 1 to 16. The divided result is available at REF DIV OUT (pin 39), and is similar to VCO DIV OUT.

# **DIGITAL PHASE/FREQUENCY DETECTOR**

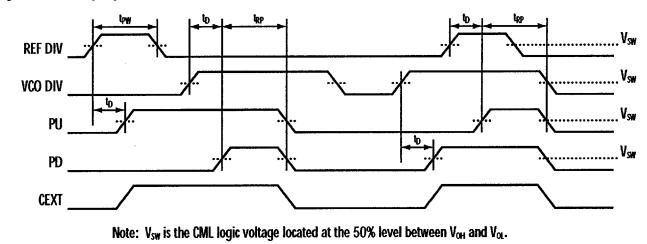

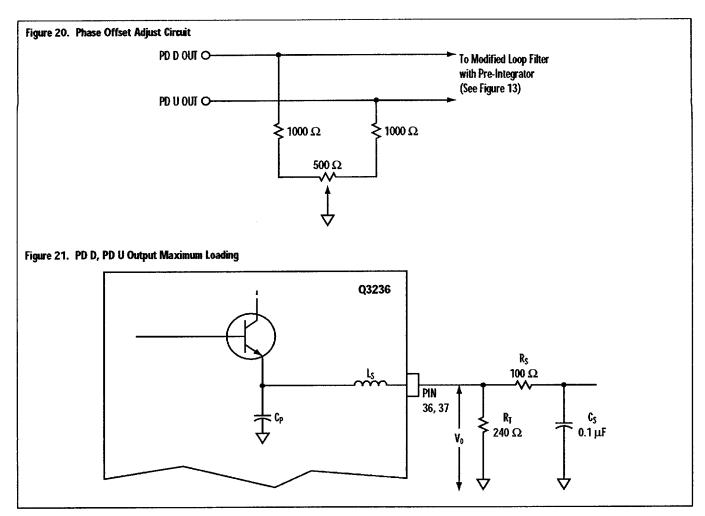

The Q3236 has a digital phase/frequency detector capable of up to 100 MHz operation and a phase detector gain constant of 302 mV/Rad. This high gain suppresses the active loop filter noise floor. Additionally, the high phase detector gain permits wider loop bandwidths, which yield faster settling times and lower VCO phase noise contributions. The outputs of the VCO and reference frequency divider chains are connected to an internal digital phase/ frequency detector (PFD). The PFD is triggered by the rising edges of these signals and has three outputs. (Refer to Figure 6.)

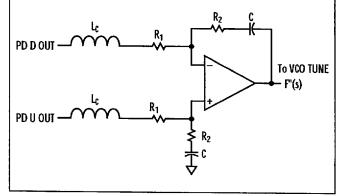

Two of these outputs make up a double-ended PFD output. The two signals corresponding to this output are PD U OUT (Phase Detector Pulse Up) and PD D OUT (Phase Detector Pulse Down). The first output, PD U OUT (pin 36), pulses "High" approximately 1.9 V when the divided VCO lags behind the divided reference in phase or frequency. The pulse begins at the rising edge of the REF DIV input and is terminated on the rising edge of the divided VCO signal, VCO DIV. Conversely, PD D OUT (pin 37) pulses "High" in the same manner when the divided VCO leads the divided reference in phase of frequency. The pulse begins at the rising edge of the VCO DIV input and terminates on the rising edge of the divided reference signal, REF DIV. Thus, the phase error is encoded as a

pulse-width modulated waveform, whose DC average is proportional to its duty cycle which equals the phase error. In typical differential phase detector output applications, PD U OUT is subtracted from PD D OUT in a differential OP-AMP active loop integrator filter, as shown in Figure 13. Therefore, it is only necessary that the differential output power between the two phase detector outputs, PU and PD, be linearly proportionate to the phase difference between the VCO DIV and REF DIV input rising edges. A residual pulse width, t<sub>RP</sub>, is also added onto both phase detector outputs after the rising edge of the lagging input to mitigate the usual "dead zone" nonlinearity. This works as follows: as long as this residual pulse is kept above a minimum duration, then the phase detector outputs will always reach full amplitude all the way down to zero phase difference, thereby maintaining output power which stays linearly proportionate to the time skew between the phase detector inputs.

The third output, LD OUT (pin 43), is used for an out-of-lock indication. It pulses "Low" when either PD U OUT or PD D OUT is pulsing "High". Lock detection is performed by NORing the phase detector PD U and PD D output signals. The result is a signal which pulses for a duration equal to the time skew between the VCO DIV and REF DIV rising edges. These pulses are integrated with an internal 2K series resistor, and a shunt capacitor connected to the CEXT output (pin 34). When the PLL is out of lock and there is pulsing on the PFD outputs sufficient to bring the voltage on CEXT above an internal comparator threshold, then the open collector output, LD OUT. will turn on, sinking up to 25mA. LD OUT can be wired to an open-collector fault bus or used to drive an LED, indicating an out-of-lock condition. The phase/ frequency detector waveforms are shown in Figure 6.

Certain conditions may produce electrical overstress (EOS) to pin 43 and damage the LD OUT. Such an occurance would typically be the result of capacitive discharge with insufficient current limiting resistance with respect to LD OUT and how out-of-lock conditions are indicated within a particular system design. Careful attention to proper current limiting will eliminate any EOS potential.

# DIGITAL PROCESSOR INTERFACE (DPI) MODES

The Q3236 can be programmed using one of three operating modes including a Direct Parallel Input Mode, 8-bit Bus Mode, or Serial Bus Mode. All of the DPI data and control inputs operate at either static or low speeds relative to the rest of the device and are to be compatible with CMOS/TTL levels, whose characteristics are described in Table 6. The DPI outputs consist of twenty counter programming bits. M0 - M8, A0 - A3, R0 - R5 as well as the prescaler enable control input, PRE EN/. An Enhanced Operation Mode option for the 8-bit Bus and Serial Bus Modes is provided to enable access to all of these counter programming bits and is described below. A Frequency Multiplexing Mode option for the 8-bit Bus and Serial Bus Modes is also provided to allow rapid toggling between stored programmed frequencies and is described below the following sections of these two respective interface modes.

The interface modes are selected in the following manner: when the external DPI control signal, BUSMODE/(pin 22), is "High", the DPI is in the Direct Parallel Mode. When the BUSMODE/ input is "Low", the DPI is in either the 8-bit Bus or Serial Bus Mode. depending on the "Low" or "High" state, respectively, of the SMODE input (pin 21). Serial Mode addressing is accomplished in a standard fashion using three signals: SDATA, SCLK, and SEN/. DPI Mode selection is summarized in Table 1. In order to consolidate the utility of as many of the package pins as possible, most of the CMOS/TTL inputs are multi-functional as denoted in Figure 10. This is possible because some of the DPI Modes and the inputs are mutually exclusive. Internally, these differing control signal inputs are logically OR'ed to avoid contention.

| Table 1. | Digital Processor | Interface | (DPI) | Mode Sel | ection |

|----------|-------------------|-----------|-------|----------|--------|

| -        | <del> </del>      |           |       |          |        |

| BUSMODE/<br>INPUT | SMODE<br>INPUT | DPI MODE              |

|-------------------|----------------|-----------------------|

| LOW               | LOW            | 8-BIT BUS             |

| LOW               | HIGH           | SERIAL BUS            |

| HIGH              | Х              | DIRECT PARALLEL INPUT |

## **ENHANCED OPERATION or Q3036 MODE**

An enhanced operation mode control signal, Q3036 MODE/(pin 44), is referenced after QUALCOMM's original single-chip PLL, the Q3036. It allows the Q3236 to maintain identical DPI Modes and divider ratios as the Q3036 for backwards compatibility, or be set for expanded divider capability and DPI operation. When the Q3036 MODE/ input is "High", this enables access to all twenty counter programming bits for operation only in the 8-bit Bus or Serial Bus Modes if the additional M7, M8 or R4, R5 counter bits are required for larger division ratios. This allows for programmability to the full range of divider ratios as described in the *Functional Overview* section under the *VCO Divide* and *Reference Divider* subsections.

When the Q3036 MODE/ input is "Low", all of the counter programming bits except M7, M8, R4, and R5 are available in all three interface modes, with a corresponding reduction in the available range of divider ratios as mentioned in the previous section. When operating with Q3036 MODE/ set "Low", the M7, M8, R4, and R5 inputs are set internally to the "Low" state. This allows any previously designed synthesizer circuits using the Q3036 to be directly replaced with the Q3236 device.

Additionally, all external CMOS/TTL inputs will register as a "High" or "Low" state when left floating, according to the "Low" or "High" state of the Q3036 MODE/ input, respectively. This however, means that when operating in 8-bit Bus Mode or Serial Bus Mode when pin 44 is tied "Low", the FSELP and FSELS inputs (pins 18 and 16, respectively) must also be tied "Low" so that the data loaded into the primary registers can remain inactive until after the HOP WR input is asserted. (See section under 8-bit Bus or Serial Bus Frequency Multiplexing: Ping-Pong Mode for further details.)

# **DIRECT PARALLEL INPUT MODE**

With the BUSMODE/ input set "High" and the Q3036 MODE/ input set "Low", all of the DPI outputs except M7, M8, R4, and R5 are taken directly from external inputs, as listed in the pin assignment/descriptions in Table 8J. Referring to the Q3236 Block

Diagram (Figure 1), BUSMODE/ is really the select input to a row of 20 x 2:1 MUXes. Each of the inputs are connected to the external inputs, with the exception of the M7, M8, R4, and R5 signals. This mode allows the device to be hardwired for fixed frequency phase-locked oscillators as well as parallel-loaded fast frequency hopping applications.

#### **8-BIT BUS MODE**

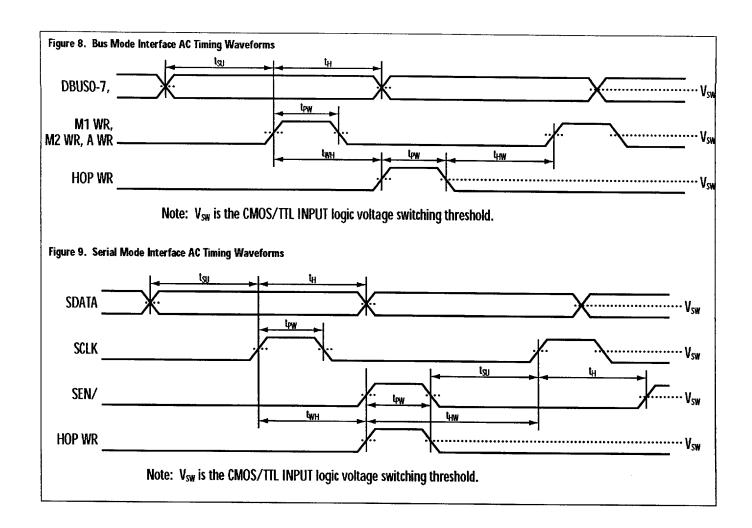

With the BUSMODE/ input "Low" and the SMODE input "Low", the 8-bit Bus Mode is selected and the external DBUS0-7 inputs are latched into one of the three primary registers, with the AWR, M1 WR, or M2 WR external control inputs according to the timing requirements shown in Figure 8. In the 8-bit Bus Mode, the interface is double-buffered consisting of a set of primary registers and secondary registers. The primary registers are programmed in parallel fashion without affecting the inputs to the counters. The contents from the primary registers are loaded into the secondary registers on the rising edge of the HOP WR input and are then immediately available to the counters and prescaler as DPI outputs. The DPI outputs are simply the secondary register outputs. A mapping of the DBUS0-7 inputs to the primary registers for all twenty counter programming bits is shown in Table 2, and listed in the pin assignment/ descriptions in Table 8H. Note however, that when operating in the 8-bit Bus Mode and the Q3036 Mode (pin 44 tied "Low"), it is necessary to also tie "Low" the R2 and R3 external reference counter inputs (pins 4 and 5, respectively) in order for the 8-bit bus to program correctly. This requirement is due to the DBUS0-1 inputs sharing the R2-3 input pads which automatically register to the opposite logic state of pin 44 when left floating. A failure to set pins 4 and 5 "Low" when operating this way will result in the internal M0-1 and A0-1 programming counter bits being stuck in a logic "High" condition.

# **SERIAL BUS MODE**

With the BUSMODE/ input "Low" and the SMODE input "High", the Serial Bus Mode is selected and data is shifted serially into the SDATA input on the

Table 2. 8-bit Bus Mode Primary Register Map

| EXTERNAL | INTERNAL            | PRIMARY REGISTER     | MAPPING              |

|----------|---------------------|----------------------|----------------------|

| INPUT    | A WR<br>Rising edge | M1 WR<br>Rising Edge | M2 WR<br>Rising Edge |

| DBUS0    | A0                  | Mo                   | M7                   |

| DBUS1    | <b>A</b> 1          | M1                   | M8                   |

| DBUS2    | A2                  | M2                   | R4                   |

| DBUS3    | A3                  | M3                   | R5                   |

| DBUS4    | RO                  | M4                   | N/A                  |

| DBUS5    | R1                  | M5                   | N/A                  |

| DBUS6    | R2                  | M6                   | N/A                  |

| DBUS7    | R3                  | PRE EN/              | N/A                  |

rising edge of the SCLK input, while the active "Low" shift enable control input, SEN/, is "Low". In the same manner as the 8-bit Bus Mode, the interface is double-buffered consisting of a set of primary registers and secondary registers. The data for all twenty counter programming bits is shifted into the primary registers in accordance to the sequence shown in Table 3, starting with R5 and ending with A0. When operating in the Q3036 Mode (pin 44 tied "Low"), all twenty serial data bits still need to be shifted into the SDATA input even though the M7-8 and R4-5 counter bits cannot be utilized. In this case, a logic "0" should be used for the first four data bits of the SDATA input. The contents from the primary registers are shifted into the secondary registers on the rising edge of either the SEN/ input or the HOP WR input asserted according to the timing requirements shown in Figure 9, and are then immediately available to the counters and prescaler as DPI outputs. A list of the respective Serial Bus Mode pin assignment/ descriptions is shown in Table 8I.

# 8-BIT BUS OR SERIAL BUS FREQUENCY MULTIPLEXING: PING-PONG MODE

The Ping-Pong Mode is a subset of both the 8-bit Bus

and Serial Bus Modes which enables the Q3236 to be multiplexed between two pre-loaded frequencies for applications involving random frequency hopping, lowdata-rate FSK modulation, or half-duplex transceiving operation using a single synthesizer. ATE system environments requiring multiple frequencies also use fast switching synthesizers to greatly increase system throughput, and they are increasingly being used as the reference oscillator in commercial Magnetic Resonance Imaging (MRI) systems. In either interface mode, this is carried out by toggling between two different VCO division ratios in the primary and secondary registers, since the counter programming bits in the primary registers may be updated while the ones in the secondary registers are controlling the programmable divider.

The so-called "ping-pong" frequency selection is controlled by the external input signal, FSELP in the 8-bit Bus Mode, and FSELS in the Serial Mode.

As noted in the 8-bit Bus Mode subsection, after the DBUS0-7 inputs are latched into the three primary registers, they are then only loaded into the secondary registers after the HOP WR input is asserted. This means that the contents of the primary registers can be updated with a new frequency word while the

| Table 3. | Serial | Mode Data | Programming | Sequence |

|----------|--------|-----------|-------------|----------|

|----------|--------|-----------|-------------|----------|

| BIT NO.        | 1  | 2  | 3  | 4  | 5          | 6          | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

|----------------|----|----|----|----|------------|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| SDATA<br>Input | R5 | R4 | M8 | M7 | PRE<br>En/ | <b>M</b> 6 | M5 | M4 | МЗ | M2 | M1 | MO | R3 | R2 | R1 | RO | А3 | A2 | A1 | AO |

8-10 http://www.qualcomm.com/ProdTech/asic

E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556

secondary registers retain control of the DPI outputs with the previously loaded data. An external frequency multiplexing control input, FSELP (pin 18), enables the device to be toggled between these two pre-loaded frequencies as noted in the pin assignment/descriptions, Table 8H. When the FSELP input is "High", the synthesizer output frequency is obtained from the frequency word stored in the primary registers, and when the FSELP input is "Low", the output frequency is obtained from the frequency word stored in the secondary registers. The DPI outputs are simply the multiplexed output of either the primary or secondary register outputs selected by the control signal FSELP.

As noted in the *Serial Bus Mode* subsection, after the data for all twenty counter programming bits is shifted into the primary registers, they are then only loaded into the secondary registers after the SEN/ and HOP WR inputs are asserted. In the same manner as in the 8-bit Bus Mode, an external frequency multiplexing control input, FSELS (pin 16), enables the device to be toggled between these two pre-loaded

frequencies as noted in the pin assignment/ descriptions in Table 8I. The synthesizer output frequency is simply the multiplexed output of either the primary or secondary register outputs selected by the "High" or "Low" state, respectively, of the control signal FSELS.

For Q3236 implementation using the Ping-Pong Mode for FSK modulation of the synthesizer's output, the data rate limitation of the loop will be a function of the natural frequency,  $\omega_n$ , since a second-order PLL is able to track for phase and frequency modulations of the reference signal as long as the modulation frequencies remain within an angular frequency band roughly between zero and  $\omega_n$ . When using the Ping-Pong Mode for a frequency hopping synthesizer, or as a transmit and receive synthesizer for half-duplex operation, the synthesizer's switching speed performance, otherwise known as it's settling time characteristics, will essentially govern the achievable switching or hop rate, although the 20-bit load period for the respective interface mode used should also be taken into account.

# **TECHNICAL SPECIFICATIONS**

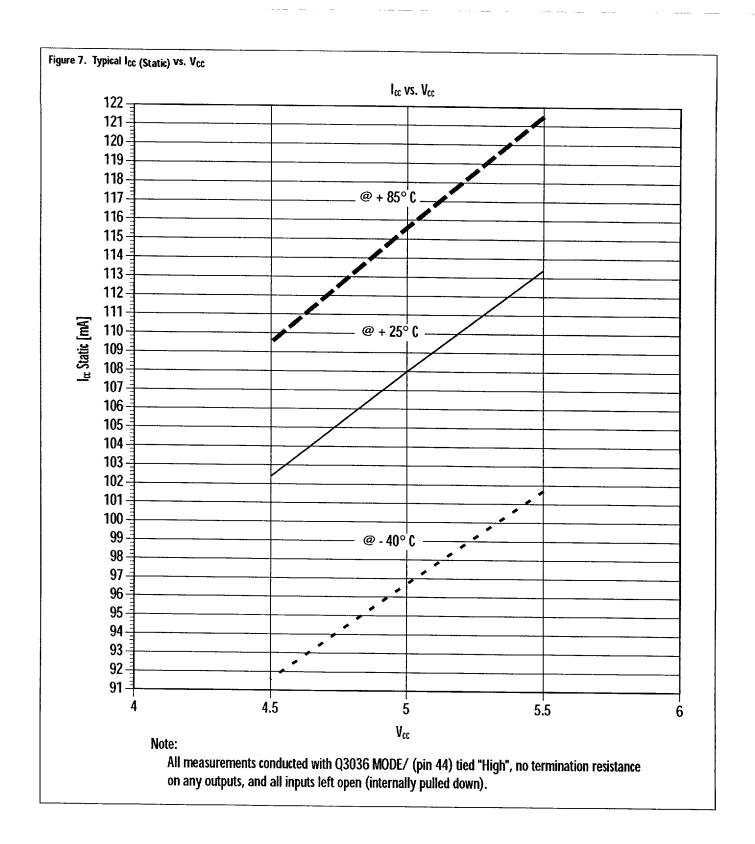

Tables 1 through 4 contain technical specifications for the Q3236 PLL. Figures 6, 8 and 9 contain timing specifications for the Q3236. Figure 7 shows the typical Q3236 supply current as a function of  $V_{CC}$  and temperature.

Stresses above those listed in this Absolute Maximum Ratings table may cause permanent and functional damage to the Q3236 device. This is a stress rating only. Functional operation of the Q3236 at these or any other conditions beyond the min/max ranges indicated in the operational sections of this specification is not implied. Exposure exceeding absolute maximum rating conditions for extended periods may affect Q3236 reliability.

Table 4. Absolute Maximum Ratings: Q3236I-20N

| PARAMETER                                                                   | SYMBOL           | MIN    | MAX                   | UNITS            | NOTES |

|-----------------------------------------------------------------------------|------------------|--------|-----------------------|------------------|-------|

| Storage Temperature                                                         | T <sub>510</sub> | - 55   | + 150                 | °C               | _     |

| Junction Temperature                                                        | Ţj               | - 55   | + 150                 | °C               | _     |

| Supply Voltage (Relative to VEE)                                            | Vcc              | _      | + 7.0                 | ٧                | -     |

| Voltage on Any Non Differential Input<br>Pin (Relative to V <sub>EE</sub> ) | V <sub>IN</sub>  | - 0.5  | V <sub>CC</sub> + 0.5 | ٧                | _     |

| Continuous Output Current                                                   | l <sub>out</sub> | 25     | -                     | mA               | 1     |

| Surge Output Current                                                        | lout             | 200    | -                     | mA               | 1     |

| AC Coupled Voltage on Any<br>Differential Input                             | V <sub>IN</sub>  | _      | 1275                  | mV <sub>PP</sub> | _     |

| Bipolar Latchup Insensitivity                                               | ITRIG            | ± 100  | -                     | mA               | 2     |

| ESD Protection                                                              | V <sub>ESD</sub> | ± 2000 | -                     | ٧                | 3     |

## Notes:

- 1. ECL and ECL 2V outputs terminated with 510  $\Omega$  to  $V_{\text{EE}}$ .

- 2. Method meets the intent of JEDEC STD 17 Publication. This is the maximum allowable current flow through the input and output protection diodes.

- 3. Method meets the intent of MIL-STD-883, Method 3015.

**Table 5. Operating Conditions**

| PARAMETER                                        | SYMBOL | MIN  | TYPICAL | MAX  | UNITS | NOTES |

|--------------------------------------------------|--------|------|---------|------|-------|-------|

| Operating Ambient Temperature                    | TA     | -40  | -       | +85  | °C    | -     |

| Operating Voltage (Relative to V <sub>EE</sub> ) | Vcc    | +4.5 | -       | +5.5 | V     |       |

| Junction to Case Resistance                      | θις    | -    | 19      | -    | °C/W  | 1     |

| Junction to Ambient Resistance                   | θμ     | _    | 51      | _    | °C/W  | 2     |

- 1.  $\theta_{\text{JC}}$  measured with package held against an "infinite" heatsink test condition.

- 2.  $\theta_{JA}$  measured in still-air, room temperature test condition.

**Table 6. DC Electrical Specifications**

| PARAMETER                                           | SYMBOL                | MIN                    | MAX                    | UNITS | NOTES |

|-----------------------------------------------------|-----------------------|------------------------|------------------------|-------|-------|

| ECL "High" Output Voltage                           | V <sub>OH</sub>       | V <sub>CC</sub> - 1150 | V <sub>CC</sub> - 850  | m۷    | 1     |

| ECL "Low" Output Voltage                            | Vol                   | V <sub>CC</sub> - 2030 | V <sub>cc</sub> - 1620 | m۷    | 1     |

| ECL 2V "High" Output Voltage                        | V <sub>OH</sub>       | V <sub>CC</sub> - 1150 | V <sub>CC</sub> - 650  | m۷    | 1     |

| ECL 2V "Low" Output Voltage                         | Vol                   | V <sub>CC</sub> - 3250 | V <sub>CC</sub> - 2610 | m۷    | 1     |

| CEXT "High" Output Voltage                          | V <sub>OH</sub>       | V <sub>CC</sub> - 1150 | V <sub>CC</sub> - 700  | m۷    | 2     |

| CEXT "Low" Output Voltage                           | Vol                   | V <sub>CC</sub> - 2100 | V <sub>cc</sub> - 1500 | mV    | 2     |

| Open Collector "Low" Output Voltage                 | Vol                   | -                      | 500                    | m۷    | 3     |

| Open Collector "High" Output Current                | lot                   | -2                     | +2                     | μA    | 4     |

| CMOS/TTL "High" Input Current                       | TL I <sub>H</sub>     | +225                   | +400                   | μA    | 5     |

| CMOS/TTL "Low" Input Current                        | TILIR                 | -100                   | 0                      | μΑ    | 6     |

| CMOS/TTL "High" Input Voltage                       | V <sub>IH</sub>       | 2.0                    | -                      | ٧     | 7     |

| CMOS/TTL "Low" Input Voltage                        | VIL                   | -                      | 0.800                  | V     | 7     |

| Q3036 MODE/ "High" Input Current                    | Q3036/ I <sub>H</sub> | +400                   | +800                   | μА    | 8     |

| Q3036 MODE/ "Low" Input Current                     | Q3036/ I <sub>L</sub> | -400                   | -200                   | μА    | 9     |

| Supply Current (V <sub>CC</sub> - V <sub>EE</sub> ) | loc                   | -                      | 160                    | mA    | 10    |

- 1. Outputs terminated through 510  $\Omega$  to  $V_{EE}$ .

- 2. Outputs measured directly with no termination resistance.

- 3. While open collector output is sinking 20 mA.

- 4.  $V_{cc}^* = +5.5 \text{ V}$ ,  $V_{out} = V_{cc} 10 \text{ mV}$ .

- 5.  $V_{cc}^* = +5.5 \text{ V}$ ,  $V_{IN} = V_{cc} 10 \text{ mV}$ , Input Q3036 MODE/ =  ${}^{m}V_{Ec}^{*}$ .

- 6.  $V_{cc}^* = +5.5 \text{ V}$ ,  $V_{IN} = V_{EE} + 10 \text{ mV}$ , Input Q3036 MODE/ = " $V_{EE}$ ".

- All CMOS/TTL inputs will register as a "High" or "Low" state when left floating, according to the "Low" or "High" state of the Q3036 MODE/ input, respectively.

- 8.  $V_{cc}^* = +5.5 \text{ V}$ ,  $V_{IN} = V_{cc} 10 \text{ mV}$ .

- 9.  $V_{\text{CC}}{}^* = +5.5 \text{ V, } V_{\text{IN}} = V_{\text{EE}} + 10 \text{ mV}.$

- 10.  $V_{cc}^*$  = +5.5 V (ECL, ECL 2 V Outputs terminated through 510  $\Omega$  to  $V_{EE}$ . \*All  $V_{CC}$  values relative to  $V_{EE}$ .

Figure 6. Phase/Frequency Detector Waveforms

**Table 7. AC Electrical Specifications**

| PARAMETER                                   | SYMBOL          | MIN   | MAX      | UNITS | NOTES   |  |

|---------------------------------------------|-----------------|-------|----------|-------|---------|--|

| VCO IN, REF IN Differential Inputs          |                 |       |          |       |         |  |

| Cincidat or Consum Maria Insul Considerate  | V <sub>IN</sub> | 200   | 950      | mVpp  |         |  |

| Sinusoidal or Square Wave Input Sensitivity | VIN             | (-10) | (+3.5)   | dBm   |         |  |

| Input VSWR                                  |                 |       | 3:1      |       |         |  |

| VCO IN Frequency Range                      | Fyco            | 20    | 2000     | MHz   | 1, 2, 3 |  |

| REF IN Frequency Range                      | FREF            | 20    | 100      | MHz   | 1, 2    |  |

| 10/11 Prescaler Frequency                   | F <sub>P</sub>  | 20    | 2000     | MHz   | 1, 2    |  |

| M Counter Frequency                         | F <sub>M</sub>  | 20    | 300      | MHz   | 1, 2    |  |

| A Counter Frequency                         | FA              | 20    | 182      | MHz   | 1, 2    |  |

| R Counter Frequency                         | F <sub>R</sub>  | 20    | 100      | MHz   | 1, 2    |  |

| Phase Detector Input Pulse Width,           | tpw             | 4     | _        | ns    | 6       |  |

| REF DIV, VCO DIV                            | Ψ₩              | 7     |          | cii   | 0       |  |

| Phase Detector Output Residual Pulse        | 1               | 3.2   |          | ns    | 5, 6    |  |

| Width                                       | l <sub>RP</sub> | J.2   |          | 113   |         |  |

| Phase Detector Propogation Delay            | to              | _     | 2.5      | ns    | 5, 6    |  |

| DBUSO-7 Valid to M1 WR, M2 WR,              | tsu             | 50    | _        | ns    | 4       |  |

| A WR Rising                                 | 30              | 30    | <u> </u> | 113   | ,       |  |

| DBUSO-7 Valid after M1 WR, M2 WR,           | in the          | 50    | l _      | ns    | 4       |  |

| A WR Rising                                 | 41              | - 50  |          | 113   | •       |  |

| SDATA Valid to SCLK Rising                  | tsu             | 50    |          | ns    | 4       |  |

| SDATA Valid after SCLK Rising               | ч               | 50    | -        | ns    | 4       |  |

| SEN/ Setup to SCLK Rising                   | tsu             | 50    |          | ns    | 4       |  |

| SEN/ Hold after SCLK Rising                 | ŧн              | 50    | -        | ns    | 4       |  |

| SCLK, M1 WR, M2 WR,                         | <b></b>         | 50    | _        | ns    | 4       |  |

| A WR Rising to HOP WR, SEN/ Rising          | twiH            | 30    |          | 113   | 7       |  |

| Pulse Width SCLK, M1 WR, M2 WR,             |                 | 50    |          | ne    | 4       |  |

| A WR, HOP WR, and SEN/                      | фw              | 30    |          | ns    |         |  |

| HOP WR Rising to SCLK, M1 WR,               |                 | 0     | _        | ns    | 4       |  |

| M2 WR, A WR Rising                          | \$HW            | U     |          | 112   | 4       |  |

| CMOS/TTL Input Capacitance                  | C <sub>IN</sub> | _     | 2        | рF    | 7       |  |

- 1. For square wave inputs with edge rates of at least 200mV/25ns, there shall be no lower frequency limit.

- 2. Per input loading of Figure 5a.

- 3. The Q32361-20N will operate up to 2200 MHz typical with 0  $\leq$   $T_A$   $\leq$  70°C and 4.75  $\leq$   $V_{CC}$   $\leq$  5.25 V.

- 4. Timing is referenced at the CMOS/TTL input logic voltage switching threshold.

- 5. Outputs PD D, PD U loaded per Figure 21.

- 6. Timing is referenced at the 50% level between VoH and VoL.

- 7. Guaranteed by design; not tested in production.

# **INPUT/OUTPUT SIGNALS**

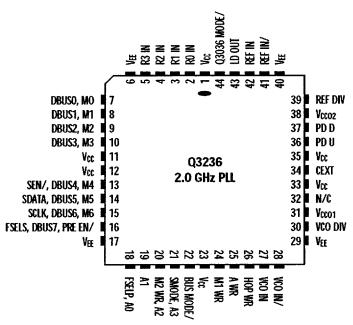

Figure 10 provides the pin configuration of the Q3236

PLL package and Tables 8-17 provide summaries of the input/output signal pin assignments.

Figure 10. Q3236 44-pin Configuration

**Table 8. Differential Line Receiver Input Pin Functions**

| SYMBOL  | PINS | I/O TYPE           | FUNCTION                                          |

|---------|------|--------------------|---------------------------------------------------|

| VCO IN  | 27   | Differential INPUT | VCO Driven Differential Input                     |

| VCO IN/ | 28   | Differential INPUT | VCO Driven Complimentary Differential Input       |

| REF IN  | 42   | Differential INPUT | Reference Driven Differential Input               |

| REF IN/ | 41   | Differential INPUT | Reference Driven Complimentary Differential Input |

Table 9. Enhanced Operation Mode Control Input Pin Functions

| SYMBOL              | PINS | I/O TYPE                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q3236 <b>M</b> ODE/ | 44   | V <sub>CC</sub> /V <sub>EE</sub> INPUT | Q3036 MODE. When configured "Low" ( $V_{\rm EE}$ ), internal M-Counter Bits [8:7] and R-Counter Bits [5:4] set to logic "0". External CMOS/TTL inputs "pulled up" internally through > 50 k $\Omega$ resistors. When configured "High" ( $V_{\rm CC}$ ), internal M-Counter Bits [8:7] and R-Counter bits [5:4] programmable in Serial or 8-bit Bus Mode. External CMOS/TTL inputs "pulled down" internally through > 50 k $\Omega$ resistors. |

**Table 10. Divider Output Pin Functions**

| SYMBOL  | PINS       | I/O TYPE  | FUNCTION                                                                                |  |

|---------|------------|-----------|-----------------------------------------------------------------------------------------|--|

| VCO DIV | VCO DIV 30 | ECL 100 k | VCO Divided Output. Provides output with frequency equal to VCO IN frequency divided by |  |

| ACO DIA |            | OUTPUT    | VCO IN division ratio.                                                                  |  |

| REF DIV | 39         | ECL 100 k | Reference Divided Output. Provides output with frequency equal to REF IN frequency      |  |

| KET DIV |            | OUTPUT    | divided by REF IN division ratio.                                                       |  |

# **Table 11. Phase Detector Output Pin Functions**

| SYMBOL | PINS | I/O TYPE                | FUNCTION                                                             |  |

|--------|------|-------------------------|----------------------------------------------------------------------|--|

| PD U   | 36   | ECL 2 V 100 k<br>Output | Phase Detect Pulse "Up". Pulses "High" when VCO DIV lags REF DIV.    |  |

| PD D   | 37   | ECL 2 V 100 k<br>Output | Phase Detect Pulse "Down". Pulsed "High" when VCO DIV leads REF DIV. |  |

# Table 12. Phase Lock Detect Output Pin Functions

| SYMBOL | SYMBOL PINS I/O TYPE |  | FUNCTION                                                                                                                                                                                                                                                                                                                      |  |

|--------|----------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LD OUT |                      |  | Lock Detect. High impedance during phase-locked operation, low impedance during phase unlocked operation.                                                                                                                                                                                                                     |  |

| CEXT   | 34                   |  | C EXTERNAL. OR'd output of PD and PU provided by 100 k ECL emitter follower terminated through 2 k, on chip, series resistance. External attachment of 0.1 µF capacitor acts to low pass filter OR'd output of PD and PU signals. Output drives inverting differential input of on-chip comparator used for switching LD OUT. |  |

# **Table 13. Unconnected Pin Functions**

| SYMBOL | PINS | I/O TYPE | FUNCTION        |

|--------|------|----------|-----------------|

| -      | 32   | N/C      | Unconnected Pin |

# **Table 14. Voltage Supply Pin Functions**

| SYMBOL            | PINS                  | I/O TYPE | FUNCTION                                                               |

|-------------------|-----------------------|----------|------------------------------------------------------------------------|

| Vcc               | 1, 11, 12, 23, 33, 35 | Power    | Core Circuitry V <sub>CC</sub> POWER SUPPLY                            |

| V <sub>cco1</sub> | 31                    | Power    | Output Drivers V <sub>CC</sub> POWER SUPPLY for VCO DIV OUT and CEXT   |

| Vccoz             | 38                    | Power    | Output Drivers Vcc POWER SUPPLY for PD U OUT, PD D OUT and REF DIV OUT |

| $V_{EE}$          | 6, 17, 29, 40         | Power    | V <sub>EE</sub> POWER SUPPLY                                           |

# Table 15. Digital Processor Interface (DPI) 8-bit Bus Mode Pin Functions

| SYMBOL      | PINS                                       | I/O TYPE       | FUNCTION                                                                                                                            |  |

|-------------|--------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| BUSMODE/    | 22                                         | CMOS/TTL INPUT | BUSMODE. Used with SMODE to select one of three possible DPI modes of operation.                                                    |  |

| SMODE       | 21                                         | CMOS/TTL INPUT | SMODE Selects SERIAL RUS MODE (RUSMODE / "Low" CMODE "Ligh") or O his DUS                                                           |  |

| DBUS7-DBUS0 | 16 (MSB), 15, 14, 13,<br>10, 9, 8, 7 (LSB) | CMOS/TTL INPUT | DATA BUS bit 7 (MSB) - DATA bus bit 0 (LSB)                                                                                         |  |

| M1 WR       | 24                                         | CMOS/TTL INPUT | M1 WRITE. Rising edge active. Latches DATA BUS bits [7:0] (PRE EN/ and M[6:0]) to primary register.                                 |  |

| M2 WR       | 20                                         | CMOS/TTL INPUT | M2 WRITE. Rising edge active. Latches DATA BUS bits [3:0] (R[5:4] and M[8:7]) to primary register.                                  |  |

| A WR        | 25                                         | CMOS/TTL INPUT | A WRITE. Rising edge active. Latches DATA BUS bits [7:0] (R[3:0] and A[3:0]) to primary register.                                   |  |

| HOP WR      | 26                                         | CMOS/TTL INPUT | HOP WRITE. Rising edge active. Latches primary register data previously latched with M1 WR, M2 WR, and A WR, to secondary register. |  |

| FSELP       | 18                                         | CMOS/TTL INPUT | Provides option of selecting DPI information stored in primary registers (FSLEP = "1") or secondary registers (FSELP = "0").        |  |

Table 16. Digital Processor Interface (DPI) Serial Bus Mode Pin Functions

| SYMBOL | PINS | I/O TYPE       | FUNCTION                                                                                                                                                                                                                          |

|--------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDATA  | 14   | CMOS/TTL INPUT | SERIAL DATA. Data is shifted serially into input SDATA on rising edge of SCLK signal.                                                                                                                                             |

| SEN/   | 13   | CMOS/TTL INPUT | SHIFT ENABLE. Active "Low" for SERIAL DATA loading with input SDATA. Also latches primary registers SERIAL DATA into secondary registers. SEN/ or HOP WR must be asserted "High" when loading SERIAL DATA to secondary registers. |

| SCLK   | 15   | CMOS/TTL INPUT | SHIFT CLOCK. Rising edge active. Shifts serial data into input SDATA with each rising edge (SEN/ = "Low").                                                                                                                        |

| HOP WR | 26   | CMOS/TTL INPUT | HOP WRITE. Rising edge active. Latches primary registers SERIAL DATA into secondary registers. SEN/ or HOP WR must be asserted "High" when loading SERIAL DATA to secondary registers.                                            |

| FSELS  | 16   | CMOS/TTL INPUT | Provides option of selecting DPI information stored in primary registers (FSELS = "1") or secondary registers (FSELS = "0").                                                                                                      |

Table 17. Digital Processor Interface (DPI) Direct Parallel Input Mode Pin Functions

| SYMBOL  | PINS                                   | I/O TYPE       | FUNCTION                                                           |

|---------|----------------------------------------|----------------|--------------------------------------------------------------------|

| M[6:0]  | 15 (MSB), 14, 13, 10,<br>9, 8, 7 (LSB) | CMOS/TTL INPUT | M-COUNTER BITS 6 (MSB) - 0 (LSB)                                   |

| A[3:0]  | 21 (MSB), 20, 19,<br>18 (LSB)          | CMOS/TTL INPUT | A-COUNTER BITS 3 (MSB) - 0 (LSB)                                   |

| R[3:0]  | 5 (MSB), 4, 3, 2 (LSB)                 | CMOS/TTL INPUT | R-COUNTER BITS 3 (MSB) - 0 (LSB)                                   |

| PRE EN/ | 16                                     | CMOS/TTL INPUT | PRESCALER ENABLE. Enables Divide-by 10/11 Prescaler (Active "Low") |

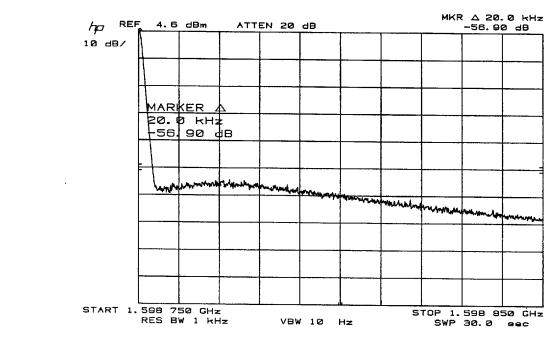

Figure 11b. Output Spectrum - Phase Noise

# APPLICATION INFORMATION GENERAL

A high performance frequency synthesizer can be designed by connecting loop filter components, a VCO and reference oscillator to the Q3236.

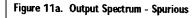

As a sample application, a PLL frequency synthesizer can be designed to generate output frequencies from 900 to 1600 MHz in 1.25 MHz steps while phase locked to a 10 MHz reference oscillator input. The 1.25 MHz frequency step size requires a phase detector comparison frequency,  $F_{PD} = 1.25$  MHz. See Figure 11 for output spectrum.

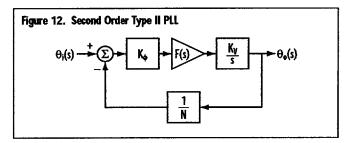

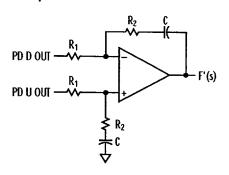

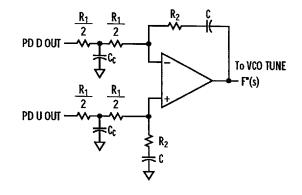

The following sections describe how to connect the Q3236 for this application, calculate the R, M and A values for programming the Q3236, construct the active loop filter, and analyze loop stability. Refer to Figures 12, 13, and 14.

#### **VCO/REFERENCE INPUT CONNECTIONS**

When using a single-ended input signal, VCO IN (pin 27) is AC-coupled with a high frequency 1000 pF capacitor. The other input, VCO IN/(pin 28), is AC-coupled to ground in the same manner as shown in Figure 5a. Because the input impedance between the two is approximately 80  $\Omega$  plus reactance, an external shunt  $100 \Omega$  input termination resistor matches the input to a 50  $\Omega$  source as shown in the measured plot of Figure 3. If the VCO is in close proximity to the PLL chip, the 100  $\Omega$  terminating resistor may not be necessary if the connecting trace is short enough not to warrant transmission line design considerations. In a balanced 50  $\Omega$  configuration, both double-ended VCO outputs should be AC-coupled to pins 27 and 28. An example of implementing a differential input signal is shown in Figure 5b. Additionally, the output noise performance can sometimes be improved by experimenting with lower values for the AC-coupling capacitors to pins 27 and 28. The idea here is that smaller-value caps will effectively differentiate the signal into VCO IN thereby providing a modicum of high pass filtering and improved lower frequency noise immunity.

## PROGRAMMING THE BINARY COUNTERS

For a synthesizer output frequency of  $F_{VCO} = 1598.75$  MHz, the total divide ratio is:

$$N = F_{VCO}/F_{PD} = 1598.75/1.25 = 1279$$

(6)

The binary values in which to program the binary R, M and A counters are given by:

$$R = (F_{REF}/F_{PD}) - 1 = 7$$

(R0 to R2 = "High"; R3 to R5 = "Low" (7)

$M = Integer \{N/10\} - 1 = 126$

$$(M0 = "Low"; M1 \text{ to } M6 = "High";$$

$$M7. M8 = "Low"$$

(8)

$$A = N - (10 * (M + 1)) = 9$$

$(A1, A2 = "Low"; A0, A3 = "High")$  (9)

## **CALCULATING LOOP FILTER COMPONENT VALUES**

Figure 12 shows a block diagram of a PLL feedback control system.

A second order type II PLL has two perfect integrators (poles on the imaginary axis). The tuning voltage-to-frequency conversion of the VCO implements integration with respect to phase, and the other integrator is obtained with the active loop filter shown in Figure 13 whose transfer function is given by:

$$F(s) = \frac{(1 + s * T_2)}{s * T_1}$$

(10)

The transfer function of output phase to input phase in terms of frequency is given by:

$$\frac{\theta_{o}(s)}{\theta_{i}(s)} = \frac{N * (1 + s * T_{2})}{s^{2} * N * T_{1}} + s * T_{2} + 1$$

(11)

8-21 QUALCOMM Incorporated, ASIC Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA Synthesizer Products Data Book, 80-24127-1 A, 8/97 Data Subject to Change Without Notice Where  $K_V$  (Rad/V) is the VCO tuning sensitivity,  $K_{\phi}(V/Rad)$  is the phase detector gain constant, N is the VCO-to-phase detector comparison frequency divide ratio and:

$$T_1 = R_1 * C \text{ and } T_2 = R_2 * C$$

are time constants based on the active loop filter components.

Using standard control theory, this can be rewritten as:

$$\frac{\theta_{o}(s)}{\theta_{i}(s)} = \frac{\frac{N * (1 + s * T_{2})}{s^{2}}}{\frac{s^{2}}{\omega_{n}^{2}} + \frac{2 * s * \zeta}{\omega_{n}} + 1}$$

(12)

Where the "natural frequency",  $\omega n$  and damping factor,  $\zeta$  are given by:

$$\omega_{\rm n} = \sqrt{\frac{K_{\rm V} * K_{\phi}}{N * T_{\rm 1}}} \tag{13}$$

and

$$\zeta = \frac{\omega_n * T_2}{2} \tag{14}$$

For this application,

$$K_V = 2 * \pi$$

(80 MHz/V), VCO specification

$K\varphi = 0.302$  V/Rad

$\omega_n$  and  $\zeta$  are usually constrained by the noise performance, stability, and settling time requirements of the loop.

In this example,

$$\omega_n = 2*\pi*20kRad/s \ (F_n = 20 \ kHz)$$

and

$$\zeta = 0.85.$$

These values correspond to the synthesizer output at 1600 MHz, or N = 1280.

If C is chosen to be 4700 pF, then  $R_1$  and  $R_2$  are left to be calculated from:

$$R_1 = \frac{K_V * K_{\phi}}{\omega_n^2 * N * C} = 1598 \Omega$$

(15)

and

$$R_2 = \frac{2 * \zeta}{\omega_n * C} = 2878 \Omega \tag{16}$$

Figure 13a. Active Loop Filter Circuit

- Loop Filter

Figure 13b. Active Loop Filter Circuit

- Modified Loop Filter with Pre-Integrator

Figure 13c. Active Loop Filter Circuit

- Alternative Loop Filter with Pre-Integrator

# LOOP STABILITY ANALYSIS

There are many different methods of analyzing the stability of feedback control networks. The approach used here is to derive the total open loop transfer function of the network and perform a Bode analysis. The open loop transfer function of the PLL with an ideal loop filter with no other delays, T(s), is given by:

$$T(s) = \frac{K_V * K_{\phi} * F(s)}{N * s} \tag{17}$$

8-22

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556

QUALCOMM Incorporated, ASIC Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA Synthesizer Products Data Book, 80-24127-1 A, 8/97 Data Subject to Change Without Notice Substituting (10) for F(s),  $s = j\omega$  and converting to magnitude and phase,

$$|T(j\omega)|^2 = \frac{(K_V * K_{\phi}/\omega * N)^2 * (1 + \omega^2 * T_2^2)}{\omega^2 * T_1^2}$$

(18)

$$\angle T(j\omega) = -180 + tan^{-1}(\omega * T_2)$$

(19)

In a Bode analysis, the phase margin is the difference between -180 degrees and the phase angle of  $T(j\omega)$  at the frequency where  $|T(j\omega)|$  is equal to unity. Although a phase margin greater than zero theoretically yields a stable loop, it is desirable to have at least 40° of phase margin to limit "peaking" in the frequency response and "ringing" in the transient response of the loop. In the example, evaluating (18) and (19) yields a phase margin of 71.6° at a unity magnitude frequency of 35.5 kHz.

It is important to note that the above results apply strictly to the ideal second order type 2 loop. However, a practical design has op-amp finite gain/bandwidth effects, additional poles and zeros for filtering, and other delays in the loop. If these additional effects are neglected during the analysis, the consequences can be severe.

Therefore, the following sections have been included to describe many of these additional effects, to re-analyze loop stability and to analyze closed loop frequency response.

#### OP AMP FINITE GAIN/BANDWIDTH

The open loop transfer function, (17), includes an ideal loop filter with a perfect integrator, which implies an op-amp with infinitely large signal voltage gain and bandwidth. The open-loop response of a typical op-amp is predominantly described by:

$$A_0(s) = \frac{A_0}{1 + s * T_0} \tag{20}$$

Where  $T_0$ , the dominant pole, is given by:

$$T_0 = \frac{A_0}{2 * \pi * GBW}$$

(21)

The large signal voltage gain,  $A_{\text{o}}$ , and the gain-bandwidth product, GBW, are specified in the op-amp

manufacturer's data sheets. For this implementation, we use OP-27 whose  $A_0$  and GBW specifications are  $2*10^6$  and 8 MHz respectively.

With the op-amp response taken into account, the loop filter transfer function becomes:

$$F''(s) = \frac{(1+s*T_2)}{s*T_1+[1+s(T_1+T_2)](1+s*T_0)/A_0}$$

(22)

Further evaluation of (22) reveals that the finite gain and bandwidth of the op-amp effectively add another pole to the loop filter response (the PLL overall open loop transfer function). The frequency of this pole is reduced by the amount of gain required of the op-amp ( $R_2/R_1$  feedback ratio). However, for a given amount of gain, the pole is farther out for an op-amp with a higher GBW. Depending on the gain of the loop filter and the op-amp GBW, this significantly impacts the phase margin of the loop and (22) should be used in the stability analysis. In some very wide loop bandwidth applications, it may be necessary to take the higher order op-amp poles into account.

## PRE-INTEGRATOR FILTERING

The Q3236 digital phase detector supplies error information by generating pulses at the reference frequency with a duty cycle proportional to the phase error. Voltage offsets between the phase detector and VCO – caused by component mismatches, op-amp input offsets, or other imbalances – are transformed into a steady state phase-error. This results in error pulses of large amplitude and short duration that contain high power at many harmonics of  $F_{PD}$ . The active loop filter is being relied on to filter linearly the DC averages of these pulses. However, high frequency, large amplitude signals on the inputs of an op-amp can cause non-linear saturation in the amplifier, greatly reducing its GBW. This effect can be devastating to wide-bandwidth PLLs.

One solution is to pre-filter the error pulses before they reach the active filter by inserting an RC lowpass section by splitting  $R_1$ . The modified loop filter with the "pre-integrator" filter is shown in Figure 13b. The addition of this circuit adds another pole, which can potentially degrade the phase margin. The time constant,  $T_C$ , and frequency,  $F_C$ , of the pole are given by:

$$T_C = \frac{R_1 * C_C}{4} \tag{23}$$

and

$$F_{\rm C} = \frac{1}{2 * \pi * T_{\rm C}} \tag{24}$$

The loop filter transfer function with the pre-integrator pole included is given by

$$F''(s) = \frac{(1 + s * T_2)/(1 + s * T_C)}{s * T_1 + 2[1 + s(T_1/2 + T_2)](1 + s * T_0)/A_0}$$

(25)

The pole should be placed far enough below the reference frequency to pre-filter the phase detector pulses enough to keep the op-amp response linear and attenuate the reference spurs on the synthesizer output, while keeping it far enough above  $\omega_n$  so as not to degrade the phase margin. A rule of thumb is to place  $F_C$  greater than 10 times  $F_n$ . Accordingly, we set  $C_C$  = 2000pF. However, this imposes a degradation in phase margin.

Another possible solution for pre-integrator filtering is to use a series LR section in place of the RC type previously described. This alternative scheme is shown in Figure 13c. Like with the RC type pre-integrator filter, the addition of this circuit adds a pole which can potentially degrade the phase margin. The time constant,  $T_{C'}$ , and frequency,  $F_{C'}$ , of the pole are given by:

$$T_{C'} = \frac{L_C}{R_1} \tag{26}$$

and

$$F_{C'} = \frac{1}{2 * \pi * T_{C'}}$$

(27)

The loop filter transfer function with the series LR preintegrator pole included is given as follows:

$$F''(s) = \frac{(1+s*T_2)/(1+s*T_{C'})}{s*T_1+[1+s(T_1+T_2)]*(1+s*T_0)/A_0}$$

(28)

All related design guidelines apply as with the RC type pre-integrator filter scheme.

## DIGITAL PHASE DETECTOR SAMPLING DELAY

In the above analysis, the frequency divider and phase detector were treated as constant, linear gain elements (1/N and  $K_{\phi}$ , respectively) with no frequency response. In fact, there is a finite propagation delay through the counters that implement the frequency divider. In the frequency domain, this fixed time delay corresponds to a phase shift which increases linearly with frequency.

Similarly, the digital phase detector responds to the edges of the frequency-divided reference and VCO signals. Thus, it cannot be treated in a continuous-time fashion. There is an inherent sampling delay of one-half the period of the phase comparison frequency. Generally, this delay is at least an order of magnitude greater than the frequency divider delay. Therefore, the divider delay may be neglected.

Because the phase error is encoded using pulsewidth modulation, there is an associated output spectrum, with a DC component equal to the duty cycle of the pulse or phase error. If the higher frequency components of the output are neglected, the phase detector is modeled with a linear transfer function of

$$K_{\phi}'(s) = K_{\phi} * e^{-[s/(2 * F_{PD})]}$$

(29)

Which contributes a phase delay of:

$$\angle K_{\phi}'(\omega) = \frac{\omega}{2 * F_{PD}}$$

(30)

Where  $F_{PD}$  is the phase detector comparison frequency and  $K_{\phi}$  is the phase detector gain constant.

# ADDITIONAL REFERENCE SUPPRESSION FILTERING

The higher frequency components of the phase detector output pulses have the effect of modulating the VCO at the harmonics of  $F_{PD}$ , creating sidebands on the synthesizer output known as "reference spurs". The pre-integrator filtering can help reduce these spurs to meet very low spurious requirements. But it may be necessary to include a higher degree of filtering. This increases attenuation at the phase comparison frequency,  $F_{PD}$ , while maintaining low insertion phase and loss down inside the loop bandwidth so as not to degrade the phase margin.

8-24

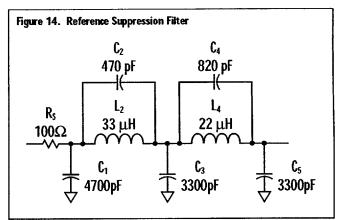

One example is the LC low-pass filter network, shown in Figure 14.

The voltage transfer function of this network is:

$$F_{R}(s)^{-1} = \left(1 + \frac{s^{2} * L_{4} * C_{5}}{1 + s^{2} * L_{4} * C_{4}}\right)$$

$$* \left(1 + \frac{s^{2} * L_{2} * C_{3}}{1 + s^{2} * L_{2} * C_{2}}\right)$$

$$* (1 + s * C_{1} * R_{5})$$

$$+ \left(\frac{s^{2} * L_{2} * C_{5}}{1 + s^{2} * L_{2} * C_{2}}\right)$$

$$* (1 + s * C_{1} * R_{5})$$

$$+ \left(1 + \frac{s^{2} * L_{4} * C_{5}}{1 + s^{2} * L_{4} * C_{4}}\right)$$

$$* (s * C_{3} * R_{5}) + (s * C_{5} * R_{5})$$

$$(31)$$

A series  $100\Omega$  resistor at the output of the op-amp establishes the source resistance. The filter drives the varactor tuning network of the VCO, which is modeled as a low value shunt capacitance. The filter is singly terminated, driving a high impedance.

A high ripple (reflection coefficient = 50%) Cauer-Chebyshev response is selected from a filter design handbook (e.g., Handbook of Filter Synthesis) to yield a

steep rolloff. This allows placement of the cutoff frequency very near  $F_{PD}$  to keep the poles far away from the loop bandwidth and to minimize their impact on the phase margin. The high ripple is not detrimental as long as the response is flat down in the PLL loop bandwidth.

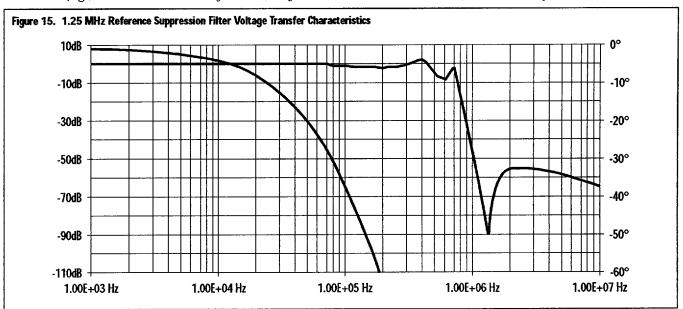

Finally, the frequency of the transmission zeros are adjusted (by changing  $C_2$  and  $C_4$ ) in such a way as to create a wide "notch" response at  $F_{PD}$  = 1.25 MHz and the rest of the filter was optimized to use standard component values.

The filter's resulting voltage transfer function magnitude and phase response vs. frequency, shown in Figure 15, indicate an insertion phase of -14° at 35.5 kHz, and a -90 dB notch at 1.25 MHz. In practice, the filter achieves about 60 dB of attenuation, due to limitation of the Q-value of the practical filter

8-25

QUALCOMM Incorporated, ASIC Products

6455 Lusk Boulevard, San Diego, CA 92121-2779, USA

Synthesizer Products Data Book, 80-24127-1 A, 8/97

Data Subject to Change Without Notice

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556 components and physical layout.

The parallel-resonant LC tanks, which make the transmission zeros, are inherently high impedances at the notch frequency and without proper shielding, can actually pick up switching noise at the notch frequency via RF-coupling.

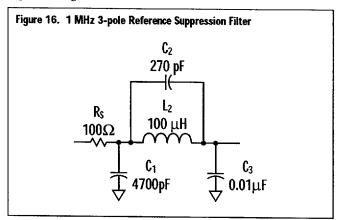

A 3-pole elliptic filter designed to suppress reference energy from an  $F_{PD}=1$  MHz is shown in Figure 16. Using the same source and termination impedance as in the previous example, this simpler topology allows direct scaling of component values to accommodate sideband suppression for different phase comparison frequencies, albeit with somewhat less attenuation effect and reduced phase margin than the 5-pole design.

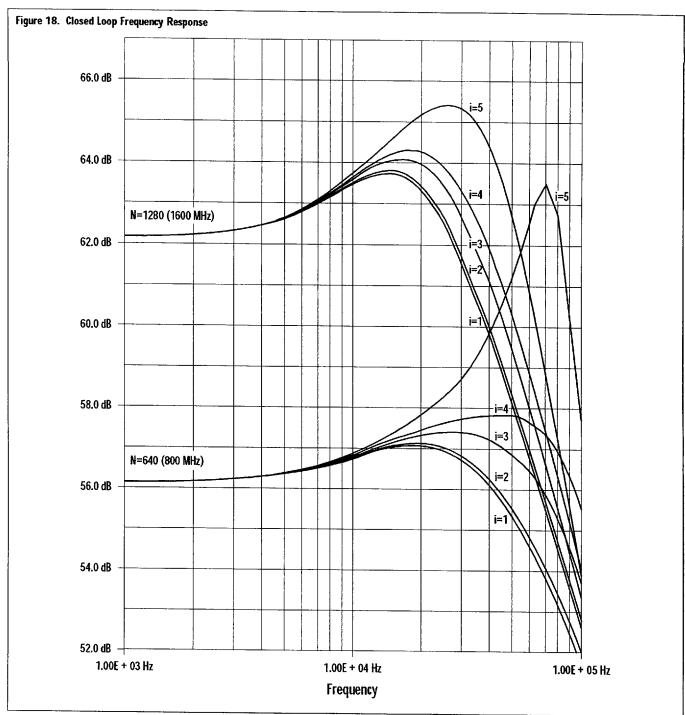

# STABILITY ANALYSIS (REVISITED) AND CLOSED LOOP RESPONSE

The stability analysis is repeated, calculating the unity gain frequency,  $F_0$  dB, of the open loop transfer function, T(s), and evaluating the phase margin,  $\phi_m$ , at

that frequency for loops which include the effects described above. Also evaluated is the closed loop frequency response in terms of the total open loop gain and loop divisor, N, given by:

$$\frac{\theta_{o}(s)}{\theta_{i}(s)} = \frac{T(s)}{[1 + T(s)/N]}$$

(32)

Peaking in the closed loop response is defined as the ratio of its maximum magnitude to its magnitude at DC. However, the DC value of the open loop response is equal to N:

$$\frac{\theta_o(DC)}{\theta_i(DC)} = N \tag{33}$$

Thus,

Peaking = 20 \* log

$$\frac{\max \left\{ \frac{\theta_o(s)}{\theta_i(s)} \right\}}{N}$$

(34)

In general, as the phase margin decreases, the peaking in the closed loop response increases.

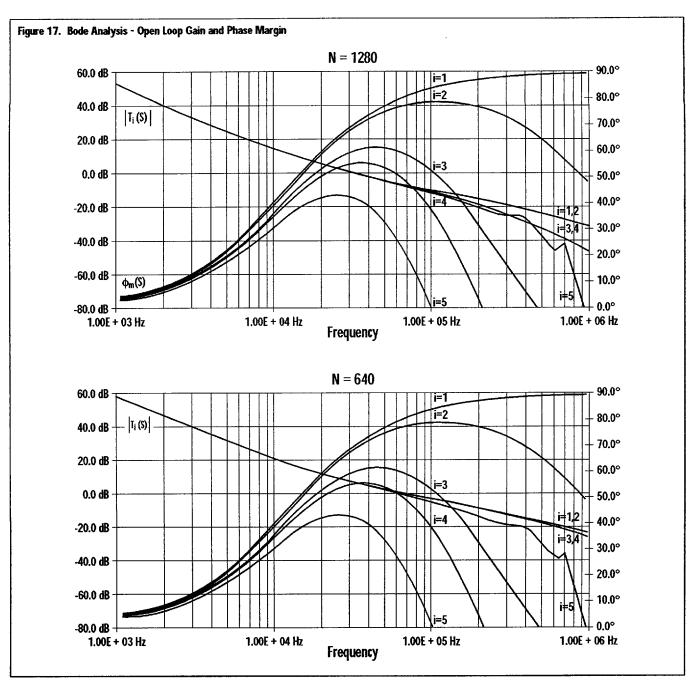

The phase margin and closed loop frequency response are evaluated for five different cases. These cases begin with the ideal second order type II loop,  $T_1(s)$ , then cumulatively add the effects to the op-amp finite gain/bandwidth,  $T_2(s)$ , pre-integrator filter pole,  $T_3(s)$ , phase detector sampling delay,  $T_4(s)$ , and reference suppression filter,  $T_5(s)$ .

The results are shown in Table 18 and plotted in Figures 17 and 18 for two cases of loop divisors:

$$N = 1280 (F_{VCO} = 1600 MHz)$$

| EXPRESSION                                                | DESCRIPTION                                             | N    | F <sub>0</sub> dB | φ <sub>m</sub> | PEAKING |

|-----------------------------------------------------------|---------------------------------------------------------|------|-------------------|----------------|---------|

| $T_1(s) = \frac{K_V * K_{\phi} * F(s)}{s}$                | Standard 2nd Order Type II Loop                         | 1280 | 35.6 kHz          | 71.7°          | 1.5 dB  |

| N * S                                                     | $\omega_n = 2\pi \cdot 20 \text{ kRad/s}, \zeta = 0.85$ | 640  | 69.0 kHz          | 80.3°          | 1.0 dB  |

| $T_2(s) = \frac{K_V * K_{\phi} * F'(s)}{N}$               | Adds Op-amp Characteristics                             | 1280 | 35.6 kHz          | 70.0°          | 1.6 dB  |

| N * s                                                     | $A_0 = 2 \times 10^6$ , GBW = 8 MHz                     | 640  | 68.5 kHz          | 77.0°          | 1.1 dB  |

| $T_3(s) = \frac{K_V * K_{\phi} * F''(s)}{s}$              | Adds Pre-integrator Capacitor                           | 1280 | 35.0 kHz          | 60.4°          | 1.9 dB  |

| N * s                                                     | $C_{c} = 2000 \text{ pF}$                               | 640  | 65.0 kHz          | 59.35°         | 1.3 dB  |

| $T_4(s) = \frac{K_V * K'_{\phi}(s) * F''(s)}{s}$          | Adds PFD Sample Delay                                   | 1280 | 35.0 kHz          | 55.3°          | 2.1 dB  |

| N * S                                                     | Κ' <sub>Φ</sub> (s)                                     | 640  | 65.0 kHz          | 50.1°          | 1.7 dB  |

| $T_5(s) = \frac{K_V * K'_{\phi}(s) * F''(s) * F_R(s)}{s}$ | Adds Reference Suppression Filter                       | 1280 | 34.5 kHz          | 41.5°          | 3.2 dB  |

| N * s                                                     | Response, F <sub>R</sub> (s)                            | 640  | 62.5 kHz          | 26.5°          | 7.4 dB  |

and, N = 640 (F<sub>VCO</sub> = 800 MHz)

First, at the lower end of the synthesizer output frequency range, 800 MHz, N decreases by a factor of 2 to 640. On inspecting (13) and (14) it is clear that both  $\omega_n$  and  $\zeta$  increase by a factor of  $\sqrt{2}$ . A recollection of servo theory on a second type II loop suggests that an increase in damping always improves the phase margin and, hence, the stability of the loop. The results show

that for this ideal case the phase margin increases from  $\phi_m$  = 71.7° at  $F_0$  dB = 35.6 kHz at N = 1280 to  $\phi_m$  = 80.3° at  $F_0$  dB = 69.0 kHz at N = 640. As expected, the peaking drops from 1.5 dB to 1.0 dB.

For the case of  $T_2(s)$ , the op-amp finite gain/bandwidth effects degrade the phase margin by 1.7°, where  $\phi_m$  = 70.0° for N = 1280. Where N = 640, the phase margin is degraded by 3.3° with  $\phi_m$  = 77.0°.

With the incorporation of the pre-integrator filter,

8-27 QUALCOMM Incorporated, ASIC Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA Synthesizer Products Data Book, 80-24127-1 A, 8/97 Data Subject to Change Without Notice

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556

the results for  $T_3(s)$  show a more pronounced impact on the phase margin and peaking.

When the phase detector sampling delay is added, it is evident that although it does not effect the magnitude of the open loop gain,  $|T_4(s)|$ , the phase margin is degraded by the added phase delay of 9.4° at the unity gain frequency,  $F_0$  dB = 65.0 kHz, for N = 640,

and 5.1° at  $F_0$  dB = 35.0 kHz, for N = 1280.

Up to this point, the results of this example have indicated that although the added poles and delays have begun to impact the phase margin and induce peaking in the closed-loop frequency response, the loop is still behaving approximately like the second order loop in that for the larger  $\omega_n$  and  $\zeta$  in the N=640 case,

8-28

http://www.qualcomm.com/ProdTech/asic E-mail: asic-products@qualcomm.com Telephone: (619) 658-5005 Fax: (619) 658-1556 the phase margin and peaking are less. This is due to the fact that up to this point, the pole and zero of the loop filter,  $R_1 * C$  and  $R_2 * C$ , are still dominating the response.

However, this is not the general case. For example, if the loop bandwidth were higher, it would require more gain out of the op-amp (larger  $R_2/R_1$  ratio), and the op-amp pole would be more dominant. Also, the pre-integrator pole and detector sampling delays would be relatively higher and thus have more impact.

Finally, the results show that by adding the reference suppression filter in  $T_5$  (s), the impact on the phase margin and peaking is quite severe in both cases,  $\phi_m = 41.5^\circ$  for N = 1280, and  $\phi_m = 26.5^\circ$  for N = 640.

It is extremely important to note that the impact is more pronounced for the case N=640 (see Figure 18). This is significant in that it contradicts the results of the second loop theory. This is caused by the loop no longer approximating the second order loop. In fact, the higher order effects cause the natural loop bandwidth and damping to lose their meaning in terms of loop stability.

Although the phase margin of 41.5° at  $F_{VCO}$  = 1600 MHz (N = 1280) is still acceptable, the results at N = 640 pose a few problems when operating at the frequency  $F_{VCO}$  = 800 MHz.

First, the low phase margin of 26.5° is not enough to allow for component tolerances and drift due to age, temperature, etc. Therefore, under some conditions the loop could become unstable and lose lock completely.

Also, the high amount of peaking (7.4 dB) in the closed loop response corresponds to a higher "overshoot" in the transient response of the loop. For the loop to remain linear in operation, the VCO must have a wider tuning range, and the loop amplifier must have a wider dynamic range in order to accommodate for this overshoot.

Finally, this excessive peaking in the loop frequency response amplifies both the VCO and reference phase noise contributions at frequency offsets where the peaking occurs. Therefore, it can heavily degrade the expected phase noise performance at those frequencies.

In summary, the results show that the cumulative effects of all these additional factors greatly degrades the stability when compared with an ideal second order loop. Therefore, a different design approach is in order when operating over the entire frequency range  $F_{VCO} = 800$ -1600 MHz. For example, using a reference suppression filter technique which has less insertion phase, such as a third order LC, or a twin T notch at 1.25 MHz would reduce its insertion phase delay, although it may require in-circuit tuning to achieve adequate rejection. Alternatively, the effect of decreasing N in the loop gain could be equalized by non-linearizing the VCO tuning sensitivity over the frequency range.

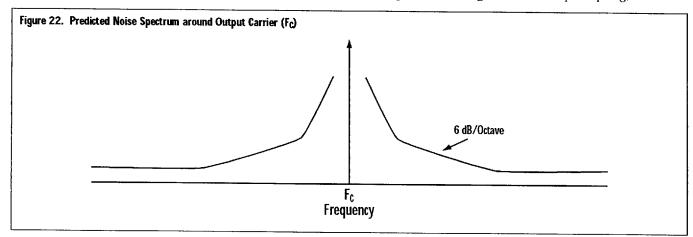

#### SYNTHESIZER OUTPUT SPECTRUM

Figure 11a shows the output spectrum of a synthesizer programmed to 1598.75 MHz (N = 1279) at a span of 5 MHz, indicating the 1.25 MHz reference spurious outputs are less than -74 dBc.

At frequency offsets less than the loop bandwidth, the synthesizer output phase noise consists of the reference phase noise, the Q3236 frequency divider/phase detector noise floor and the op-amp active loop filter's noise, all multiplied up by the loop divisor:

$$N = 1279 \text{ or } 20 * \log 10(N) = 62 \text{ dB}$$

Figure 11b shows the synthesizer output phase noise measured in a 1 kHz bandwidth at frequency offsets up to 100 kHz. The plot shows that at a 20 kHz offset, the output phase noise is about -87 dBc/Hz. The Q3236 phase noise contribution at that offset is less than or equal to:

$$-87 - 62 = -149 \, dBc/Hz @ 20 \, kHz$$

The Q3236 PLL is an ECL device. This calculation substantiates a phase noise floor of an ECL device to be > -150 dBc.

# FREQUENCY SYNTHESIZER DESIGN CONSIDERATIONS WITH THE Q3236

#### **GENERAL ELECTROMAGNETIC ISSUES**

Proper power supply biasing and grounding are critical to the design of frequency synthesizers for high performance communications systems. Power supply and digital bus noise can couple into the PLL circuitry and degrade phase noise performance. Additionally, PLL divider switching noise and phase detector pulses coupling onto power supply lines can create EMI problems and couple into high-gain/wideband IF amplifier chains.