| 查询LH151<br><b>S</b> 子 | BAF供应商<br><b>计ARP</b>       | 捷多邦,专业PCB打样工厂,24小时加急出货                                                                                                       |

|-----------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| CO 2                  | WWW.DE                      | SPEC No.         E L 0 6 8 1 0 6           I S S U E:         Aug. 31. 1994                                                  |

| <u>T</u>              | EBJ TBBB                    | Billing www.ozsc.com                                                                                                         |

| @2B                   | SPECI                       | FICATIONS                                                                                                                    |

|                       | Product Type <u>100 Out</u> | put LCD Common Driver                                                                                                        |

| m 181                 | Nodel No. L                 | H 1 5 1 3 A F                                                                                                                |

|                       |                             | ontains <u>17 pages</u> including the cover and appendix.<br>Se contact us before issuing purchasing order.                  |

|                       | CUSTONERS ACCEPTANCE        | AN 2EIF                                                                                                                      |

|                       | DATE:                       |                                                                                                                              |

| -45                   | DY: UNIN DISC.              | PRESENTED                                                                                                                    |

|                       |                             | BY: <u>J. Lanc</u><br>Y. S.NYO<br>Dept. General Manager                                                                      |

|                       |                             | H. Michicka, S. Marsharki                                                                                                    |

| CO 2B                 |                             | Engineering Dept. 1<br>Logic Engineering Centrol 2.1.95.<br>Integrated Circuits Group MALL Love *<br>SHARP CORPORATION GROUP |

|                       | ■ 8180798                   | 0027575 T68 🔳                                                                                                                |

#### LH1513AF

1

|     | Contents                                   | Page |

|-----|--------------------------------------------|------|

| 1.  | Summary                                    |      |

| 2.  | Features                                   | 2    |

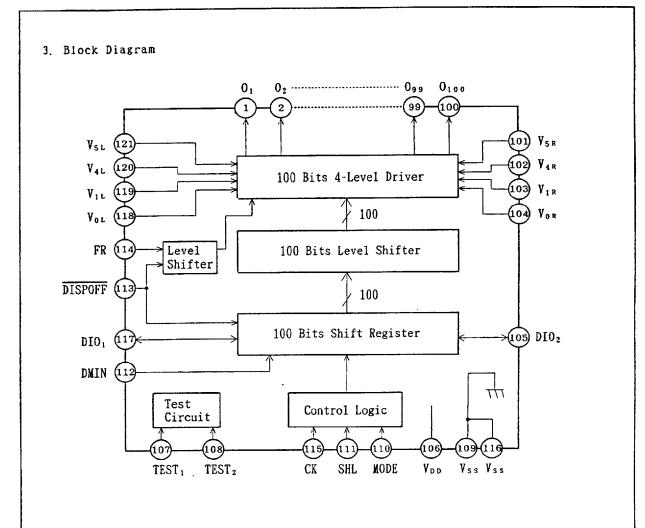

| 3.  | Block Diagram ••••••                       | 3    |

| 4.  | Functional Operations of Each Block        | 3    |

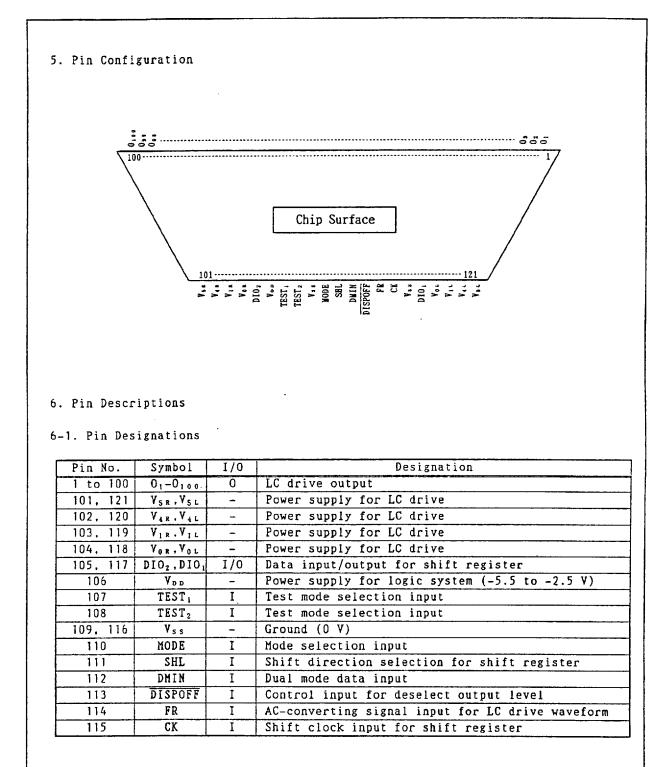

| 5.  | Pin Configuration                          | • 4  |

| 6.  | Pin Descriptions                           | • 4  |

| 7.  | Description of Functional Operations       | 6    |

| 8.  | Precaution                                 | 10   |

| 9.  | Absolute Maximum Ratings                   | 11   |

| 10. | Recommended Operating Conditions           | 11   |

| 11. | Electrical Characteristics                 | 11   |

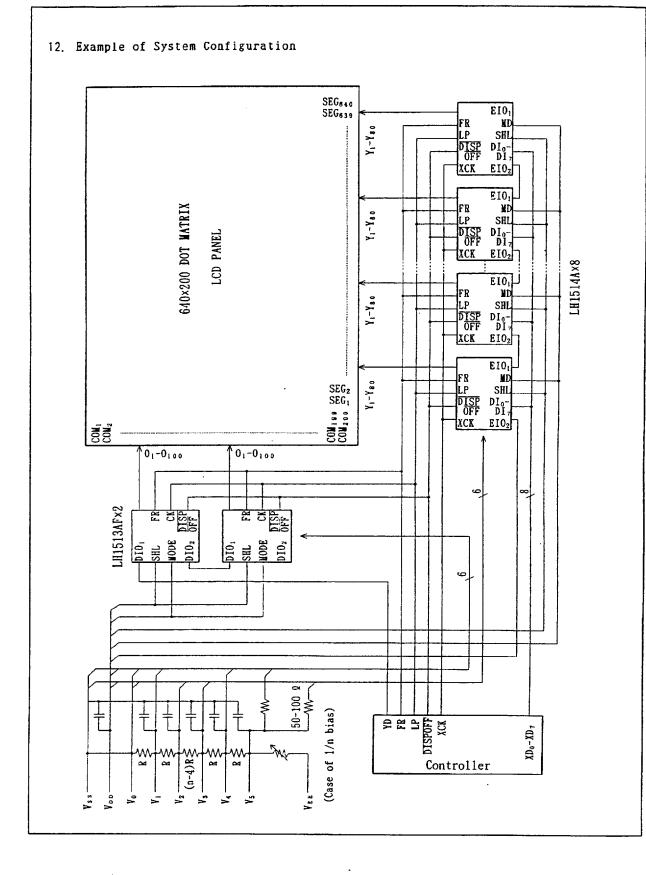

| 12. | Example of System Configuration            | 13   |

| 13. | Example of Typical Characteristic •••••••• | 14   |

| 14. | Package and Packing Specification          | 15   |

|     |                                            |      |

#### [Note]

This document contains confidential information such as copyright and know-how belonging to Sharp Corporation. The information herein shall therefore be used exclusively for the design of systems utilizing this product and may not be used for any other purpose. This document shall not be reprinted or disclosed to any third party without the prior written consent of Sharp Corporation. This product is designed to be used in electrical products such as office equipment, audio-visual equipment and other consumer products. You are requested to contact Sharp Corporation if you intend to use this product for specific applications such as automobiles, trains or aircraft which have critical control or safety requirements, antidisaster, anticrime systems or any other applications which require extremely high reliability. This product shall not be used in any medical equipment which affects human life.

#### 🔳 8180798 0027576 9T4 💻

LH1513AF

2

```

1. Summary

```

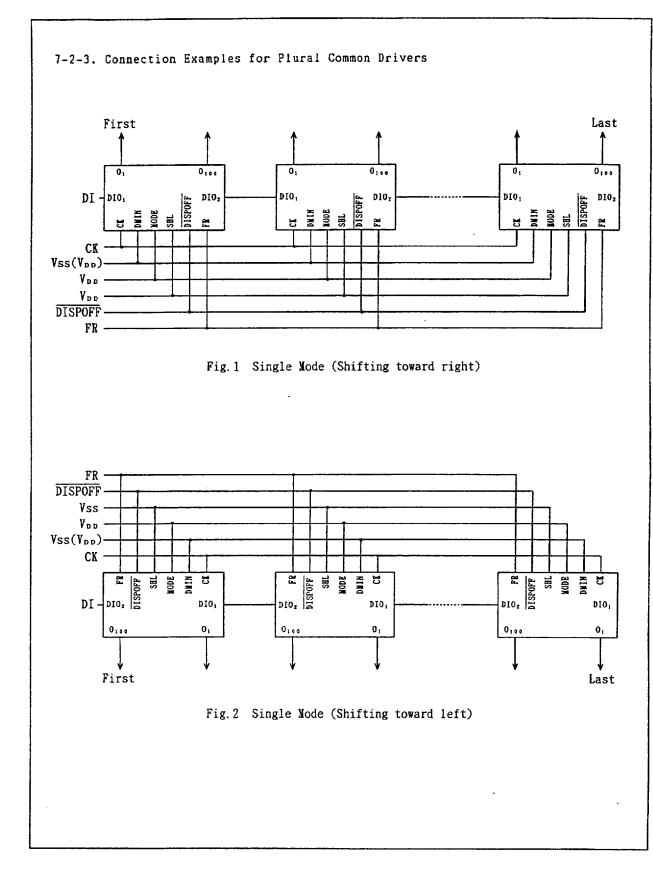

The LH1513AF is a 100 output common driver LSI suitable for driving black and white dot matrix LC panels. Through the use of SST (Super Slim TCP) technology, it is ideal for substantially decreasing the size of the frame section of the LC module. The LH1513AF is particularly well suited to driving black and white LC panels used for palmtop personal computers because of its low-voltage operation (Supply voltage for logic system : -5.5 to -2.5 V). When combined with the LH1514A Segment Driver, a low power consuming, high-precision LC panel display can be assembled. Data input/output pins are bidirectional, four data shift directions are pin-selectable.

#### 2. Features

```

• Supply voltage for the logic system : -5.5 to -2.5 V

• Supply voltage for LC drive : -28.0 to -10.0 V

(absolute maximum rating -30.0 V)

Number of LC drive outputs

: 100

: 1.5 kg (Max.)

Low output impedance

• Shift Clock frequency

: 2.0 MHz (Max.)

Low power consumption

- Built-in 100-bits bidirectional shift register (divisible into 50-bits x2)

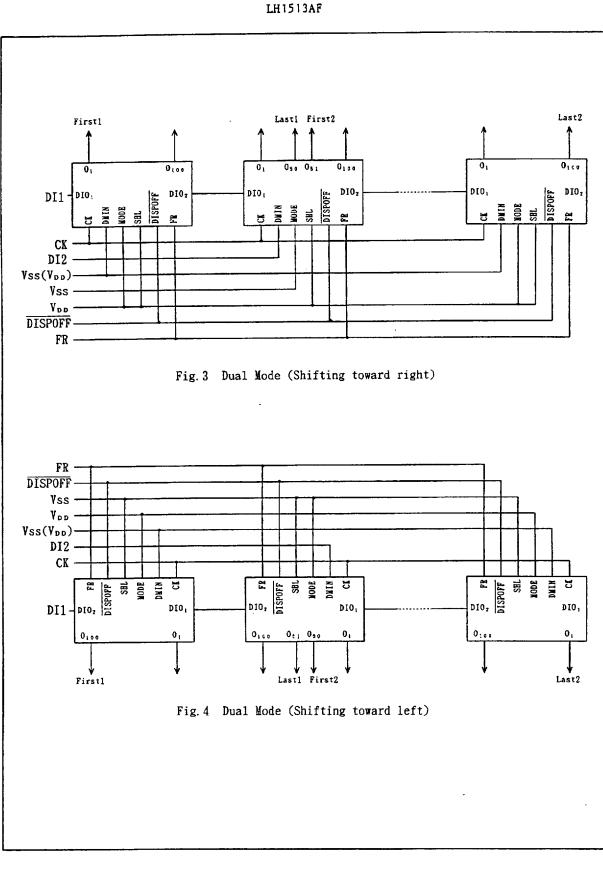

• Available in a single mode (100-bits shift register) or in a dual mode

(50-bits shift register x2)

\bigcirc \quad O_1 \quad \rightarrow \quad O_{100}

Single mode

0 \quad 0_{100} \rightarrow 0_1

.

0 0_1 \rightarrow 0_{50}, 0_{51} \rightarrow 0_{100}

Dual mode

(  0_{100} \rightarrow 0_{51}, 0_{50} \rightarrow 0_{1} )

The above 4 shift directions are pin-selectable

• Shift register circuit reset function when DISPOFF active

• Supports high capacity LC panel display when combined with the LH1514A

Segment Driver

CMOS process (N-type Silicon Substrate)

Package

: 121 pin TCP (Tape Carrier Package)

• Not designed or rated as radiation hardened

```

#### LH1513AF

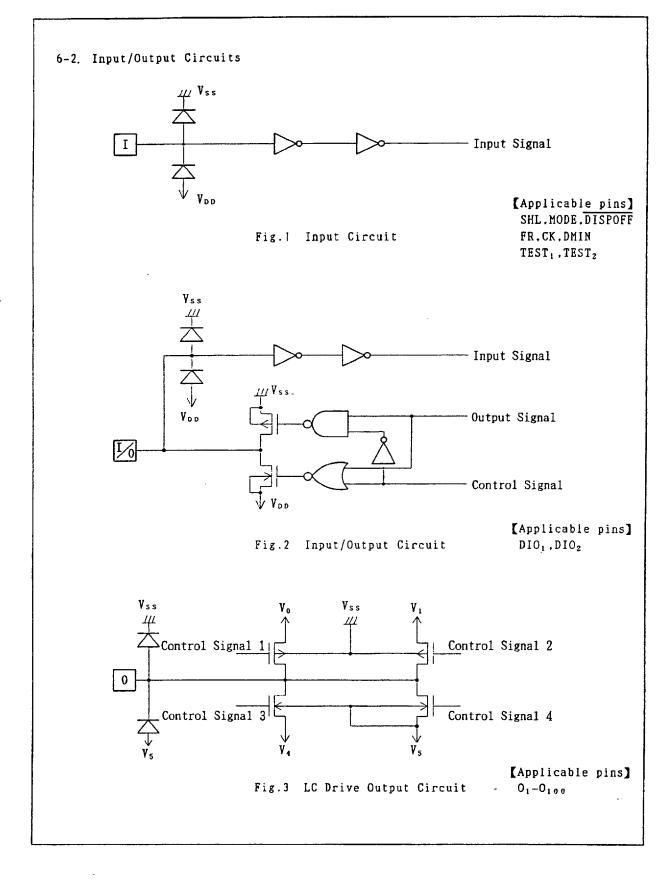

### 4. Functional Operation of Each Block

| Block          | Function                                                                                                                                                               |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift Register | Shifts data in from the data input pin on the falling edge of the CK signal, based on the data shift direction and mode setting received from the control logic block. |

| Level Shifter  | The logic voltage signal is level-shifted to the LC drive voltage level, and outputs to the driver block.                                                              |

| 4-Level Driver | Drives the LC driver output pins from the shift register data, selecting one of 4 levels $(V_0, V_1, V_4, V_5)$ based on the FR and DISPOFF signals.                   |

| Control Logic  | Controls the shift register's direction of data shift and mode setting in response to a SHL and MODE signal input.                                                     |

LH1513AF

#### 8180798 0027579 603 🖬

LH1513AF

B180798 0027580 325 📰

LH1513AF

7. Description of Functional Operations

7-1. Pin Functions

-----

| Symbol                             | Function                                                                            |

|------------------------------------|-------------------------------------------------------------------------------------|

| V <sub>DD</sub>                    | Logic system power supply pin connects to -5.5 to -2.5 V                            |

| Vss                                | Ground pin connects to 0 V                                                          |

| V <sub>OR</sub> ,V <sub>OL</sub>   | Power supply pin for LC driver voltage bias.                                        |

| V <sub>iR</sub> ,V <sub>iL</sub>   | •Normally, the bias voltage used is set by a resistor divider.                      |

| V <sub>4 R</sub> ,V <sub>4 L</sub> | •Ensure that voltages are set such that $V_{ss} \ge V_0 > V_1 > V_4 > V_5$ .        |

| V <sub>5 R</sub> ,V <sub>5 L</sub> | •To further reduce the difference between the output waveforms of L(                |

|                                    | driver output pins $0_1$ and $0_{100}$ , externally connect $V_{LR}$ and $V_{LL}$   |

|                                    | (i=0, 1, 4, 5).                                                                     |

| DIC1                               | Bidirectional shift register shift data input/output pin                            |

|                                    | •Input pin for right shift, output pin for left shift.                              |

| DIO2                               | Bidirectional shift register shift data input/output pin                            |

|                                    | •Input pin for left shift, output pin for right shift.                              |

| CK                                 | Bidirectional shift register shift clock pulse input pin                            |

|                                    | -Data is shifted on the falling edge of the clock pulse.                            |

| SHL                                | Bidirectional shift register shift direction selection pin                          |

|                                    | ·Data is shifted right when set to $V_{DD}$ level "L", and data is                  |

|                                    | shifted left when set to V <sub>ss</sub> level "H".                                 |

| DISPOFF                            | Control input pin for output deselect level                                         |

|                                    | •The input signal is level-shifted from logic voltage level to LC                   |

|                                    | drive voltage level, and controls LC drive circuit.                                 |

|                                    | •When set to $V_{DD}$ level "L", the LC drive output pins ( $O_1 - O_{100}$ ) are   |

|                                    | set to level $V_0$ .                                                                |

|                                    | •While set to "L", the contents of shift register are reset not                     |

|                                    | reading data. When the $\overline{	extsf{DISPOFF}}$ function is canceled,the driver |

|                                    | output deselect level ( $V_1$ or $V_4$ ), and the shift data is reading on          |

|                                    | the falling edge of the CK. That time,if DISPOFF removal time can                   |

|                                    | not keep regulation what is shown AC characteristics (Page12),the                   |

|                                    | shift data is not reading correctly.                                                |

| FR                                 | AC signal input for LC driving waveform                                             |

|                                    | •The input signal is level-shifted from logic voltage level to LC                   |

|                                    | drive voltage level, and Controls LC drive circut.                                  |

|                                    | <ul> <li>Normally, inputs a frame inversion signal.</li> </ul>                      |

|                                    | •The LC driver output pin's output voltage level can be set using                   |

|                                    | the shift register output signal and the FR signal.                                 |

|                                    | •Truth table is shown in 7-2-1.                                                     |

| MODE                               | Mode select pin                                                                     |

|                                    | •When set $V_{DD}$ level "L". Single Mode operation is selected, when set           |

|                                    | to V <sub>ss</sub> level "H", Dual Mode operation is selected.                      |

| DMIN                               | Dual Mode data input pin                                                            |

|                                    | According to the data shift direction of the data shift register,                   |

|                                    | data can be input starting from the 51st bit.                                       |

| TEST1                              | Test mode select pin                                                                |

| TEST <sub>2</sub>                  | •During normal operation, tie to $Y_{DD}$ level "L".                                |

6

•

LH1513AF

| Symbol          | Function                                                            |

|-----------------|---------------------------------------------------------------------|

| $0_1 - 0_{100}$ | LC driver output pins                                               |

|                 | •Corresponding directly to each bit of the shift register, one leve |

|                 | $(V_0, V_1, V_4, \text{ or } V_5)$ is selected and output.          |

7-2. Functional Operations

7-2-1. Truth Table

| FR | Latch Data | DISPOFF | Driver Output Voltage Level $(0_1 - 0_{100})$ |

|----|------------|---------|-----------------------------------------------|

| L  | L          | Ĥ       | V <sub>1</sub>                                |

| L  | H          | Н       | ۷ <sub>5</sub>                                |

| Н  | L          | H       | V 4                                           |

| Н  | Н          | Н       | V o                                           |

| x  | x          | L       | V <sub>0</sub>                                |

Here, V<sub>ss</sub>≥V<sub>0</sub>>V<sub>1</sub>>V<sub>4</sub>>V<sub>5</sub>. L: V<sub>pp</sub>(-5.5 to -2.5 V). H: V<sub>ss</sub>(0 V). x: Don't care [Note]"Don't care" should be fixed to "H" or "L", avoiding floating. There are two kinds of power supply (logic level voltage,LC drive voltage) for LCD driver, please supply regular voltage which assigned by specification for each power pin.

7-2-2. Relationship between the Data I/O Pins and Data Transfer Direction

| MODE     | SHL               | DIOI   | $DIO_2$ | DMIN  | Data Transfer Direction      |

|----------|-------------------|--------|---------|-------|------------------------------|

| L        | L(shift to right) | Input  | Output  | X     | $O_1 \rightarrow O_{100}$    |

| (Single) | H(shift to left)  | Output | Input   | X     | $O_{100} \rightarrow O_1$    |

|          | L(shift to right) | Input  | Output  | Input | $0_1 \rightarrow 0_{50}$     |

| н        |                   |        |         |       | $0_{51} \rightarrow 0_{100}$ |

| (Dual)   | H(shift to left)  | Output | Input   | Input | $0_{100} \rightarrow 0_{51}$ |

|          |                   |        |         |       | $0_{50} \rightarrow 0_1$     |

Here, L:  $V_{DD}$  (-5.5 to -2.5 V), H:  $V_{ss}$  (0 V), x: Don't care

[Note]"Don't care" should be fixed to "H" or "L", avoiding floating.

#### LH1513AF

I A180798 0027583 034 🎟

🛚 8180798 0027584 T70 📖

LH1513AF

8. Precaution

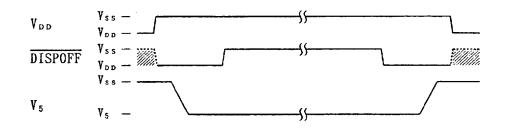

OPrecaution when connecting or disconnecting the power

This LSI has a high-voltage LCD driver, so it may be permanently damaged by a high current which may flow if a voltage is supplied to the LC drive power supply while the logic system power supply is floating. The detail is as follows.

•When connecting the power supply, connect the LC drive power after connecting the logic system power. Furthermore, when disconnecting the power, disconnect the logic system power after disconnecting the LC drive power.

We recommend you connecting the serial resistor (50 to 100  $\Omega$ ) to the LC drive power V<sub>s</sub> of the system as a current limitter resistor. And set up the suitable value of the resistor in consideration of LC display grade.

And when connecting the logic power supply, the logic condition of this LSI inside is insecurity. Therefore connecting the LC drive power supply after resetting logic condition of this LSI inside on DISPOFF function. After that, cancel the DISPOFF function after the LC drive power supply has become stable. Furthermore, when disconnecting the power, set the LC driver output pins to level  $V_0$  on DISPOFF function. After that, disconnect the logic system power after disconnecting the LC drive power.

When connecting the power supply, show the following recommend sequence.

#### LH1513AF

#### 9. Absolute Maximum Ratings

| Parameter           | Symbol          | Conditions       | Applicable pins                                                    | Ratings                     | Unit |

|---------------------|-----------------|------------------|--------------------------------------------------------------------|-----------------------------|------|

| Supply voltage (1)  | V <sub>DD</sub> | Ta=25 C          | V <sub>DD</sub>                                                    | -7.0 to +0.3                | V    |

| Supply voltage (2)  | V <sub>o</sub>  | Referenced       | VOL, VOR                                                           | V <sub>5</sub> -0.3 to +0.3 | V    |

|                     | V <sub>1</sub>  | to $V_{ss}(0 V)$ | $V_{1L}, V_{1R}$                                                   | V <sub>5</sub> -0.3 to +0.3 | V    |

|                     | V <sub>4</sub>  | ] [              | $V_{4L}, V_{4R}$                                                   | $V_5 = 0.3$ to $+0.3$       | V    |

|                     | ۷,              | ] [              | V <sub>5L</sub> , V <sub>5R</sub>                                  | -30.0 to +0.3               | V    |

| Input voltage       | V <sub>1</sub>  |                  | DIO <sub>1</sub> ,DIO <sub>2</sub> ,DMIN,SHL<br>MODE,CK,FR,DISPOFF | $Y_{DD} = 0.3$ to +0.3      | V    |

| Storage temperature | T               |                  |                                                                    | -45 to +125                 | r    |

10. Recommended Operating Conditions

| Parameter            | Symbol         | Conditions       | Applicable                       | pins      | Min.  | Typ. | Max.  | Unit |

|----------------------|----------------|------------------|----------------------------------|-----------|-------|------|-------|------|

| Supply voltage (1)   | VDD            | Referenced       | V <sub>DD</sub>                  | •         | -5.5  |      | -2.5  | V    |

| Supply voltage (2)   | V <sub>5</sub> | to $V_{ss}(0 Y)$ | V <sub>5L</sub> ,V <sub>5R</sub> |           | -28.0 |      | -10.0 | V    |

| Operating temperatur | е Торт         |                  |                                  | - <u></u> | -20   |      | +85   | t    |

11. Electrical Characteristics

#### 11-1. DC Characteristics

| $(V_{s s} = V_0 = 0)$ | ) V, V <sub>r</sub> | o=-5.5 to -                                      | 2.5 V, $V_5 = -28.0$ to -          | 10.0 V,            | Ta=-20 | ) to +85     | ; t) |

|-----------------------|---------------------|--------------------------------------------------|------------------------------------|--------------------|--------|--------------|------|

| Parameter             | Symbol              | Conditions                                       | Applicable pins                    | Min.               | Typ.   | Max.         | Unit |

| Input voltage         | V <sub>1 H</sub>    |                                                  | DIO1.DIO2.DMIN.SHL                 | 0.2V <sub>DD</sub> |        |              | V    |

|                       | VIL                 |                                                  | MODE, CK, FR, DISPOFF              |                    |        | 0.8Vpp       | V    |

| Output voltage        | V <sub>он</sub>     | I <sub>он</sub> =-0.4 mA                         | DIO <sub>1</sub> ,DIO <sub>2</sub> | -0.4               |        |              | V    |

|                       | Vol                 | IoL=+0.4 mA                                      |                                    |                    |        | $V_{DD}+0.4$ | V    |

| Input leakage current | ILI                 | V <sub>ss</sub> ≧V <sub>1</sub> ≧V <sub>DD</sub> | DMIN, SHL, MODE, CK                |                    |        | ±10.0        | μA   |

|                       |                     |                                                  | FR, DISPOFF                        |                    |        |              |      |

| I/O leakage current   | I11/0               | V <sub>ss</sub> ≧V <sub>i</sub> ≧V <sub>dd</sub> | DIO <sub>1</sub> ,DIO <sub>2</sub> |                    |        | ±10.0        | μA   |

| Output resistance     | Ron                 | *1                                               | 01-0100                            |                    | 1.0    | 1.5          | kΩ   |

| Stand-by current      | Istb                | *2                                               | V <sub>ss</sub>                    |                    |        | 50.0         | μA   |

| Consumed current (1)  | IDD                 | V <sub>DD</sub> =-3 V,*3                         | V <sub>DD</sub>                    |                    |        | 20.0         | μA   |

|                       |                     | $V_{DD} = -5 V, *3$                              |                                    |                    |        | 30.0         | μA   |

| Consumed current (2)  | I <sub>5</sub>      | $V_{DD} = -3 V.*3$                               | V <sub>51</sub> , V <sub>5R</sub>  |                    |        | 50.0         | μA   |

|                       |                     | $V_{DD} = -5 \ V, *3$                            |                                    |                    |        | 50.0         | μA   |

[Note]

\*1:  $V_5 = -28.0$  to -10.0 V,  $|\Delta V_{0N}| = 0.5$  V

\*2:  $V_{DD} = -5.0$  V,  $V_{5} = -28.0$  V,  $V_{1H} = V_{SS}$ ,  $V_{1L} = V_{DD}$ ,  $TEST_{1} = TEST_{2} = V_{DD}$

\*3 :  $V_5 = -28.0$  V,  $f_{CK} = 19.2$  kHz,  $f_{FR} = 80$  Hz, No-load

(Consumed current is case of 1/240 duty operation)

#### LH1513AF

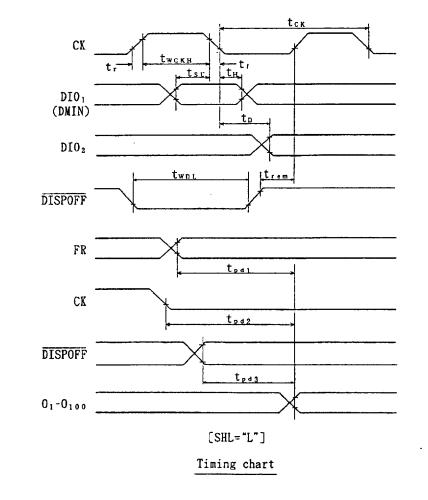

#### 11-2. AC Characteristics

| $(V_{ss}=V_0=0 V, V_{DD}=-5.5 to -2.5 V, V5=-28.0 to -10.0 V, Ta=-20 to +85 t)$ |                  |                       |      |      |      |      |  |

|---------------------------------------------------------------------------------|------------------|-----------------------|------|------|------|------|--|

| Parameter                                                                       | Symbol           | Conditions            | Min. | Typ. | Max. | Unit |  |

| Shift clock period                                                              | tcĸ              |                       | 500  |      |      | ns   |  |

| Shift clock "H" pulse width                                                     | tweeki           | e l                   | 65   |      |      | ns   |  |

| Data setup time                                                                 | tsu              |                       | 100  |      |      | ns   |  |

| Data hold time                                                                  | t <sub>H</sub>   |                       | 100  |      |      | ns   |  |

| DISPOFF "L" pulse width                                                         | twol             |                       | 1.2  |      |      | μs   |  |

| DISPOFF removal time                                                            | trem             |                       | 100  |      |      | ns   |  |

| Input signal rise time                                                          | t,               |                       |      |      | 50   | ns   |  |

| Input signal fall time                                                          | t,               |                       |      |      | 50   | ns   |  |

| Output delay time (1) CK to $DIO_1$ , $DIO_2$                                   | tp               | $C_L = 15 \text{ pF}$ |      |      | 350  | ns   |  |

| Output delay time (2) FR to $O_1 - O_{100}$                                     | tpd,             |                       |      |      | 1.2  | μs   |  |

| Output delay time (3) CK to $0_1 - 0_{100}$                                     | tpd <sub>2</sub> |                       |      |      | 1.2  | μs   |  |

| Output delay time (4) DISPOFF to $0_1 - 0_{100}$                                | tpd <sub>3</sub> | [                     |      |      | 1.2  | μs   |  |

11-3. Timing Diagram

۱

8180798 0027587 787 🖿

#### LH1513AF

• •

🛚 8180798 0027588 616 📰

#### LH1513AF

#### 13. Example of Typical Characteristic

| Parameter                  | Conditions                                 | Mim. | Typ. | Max. Uni |

|----------------------------|--------------------------------------------|------|------|----------|

| Typical Fundamental Rating | $Ta=+25$ °C, $V_{ss}=0$ V, $V_{DD}=-5.0$ V |      | 50   | ns       |

| Propagation Delay Time     |                                            |      |      |          |

:

#### LH1513AF

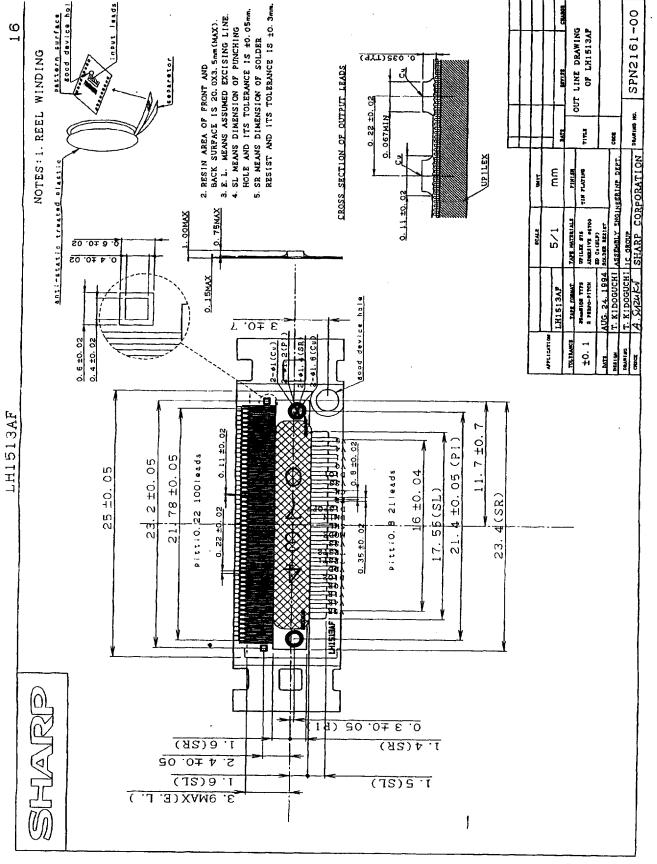

| 14. PACKAGE AND PACKING                                                                                                                                                                                                             | G SPECIFICATION                          |                                                                |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|

| <ol> <li>Package Outline Specification<br/>Refer to drawing No. SPN</li> <li>Markings<br/>The meanings of the devi</li> </ol>                                                                                                       | 2161-00                                  | be carrier package are as follows.                             |  |  |  |  |  |

| <ul> <li>(1) Date code (example) : 4/a) 3/7 ()/(a)</li> <li>a) denotes the last figure of Anno Domini (of production)</li> <li>b) denotes the week (of production)</li> <li>c) denotes the number of times of alteration</li> </ul> |                                          |                                                                |  |  |  |  |  |

| 3. Packing Specifications (1) Packing Materials                                                                                                                                                                                     |                                          |                                                                |  |  |  |  |  |

| Item                                                                                                                                                                                                                                | Material                                 | Purpose                                                        |  |  |  |  |  |

| Reel                                                                                                                                                                                                                                | Anti-static treated plastic (405mm dia.) | Packing of tape carrier package.                               |  |  |  |  |  |

| Separator                                                                                                                                                                                                                           | Anti-static treated PET (188/emt)        | Protects device and prevents<br>ESD (Electro Static Discharge) |  |  |  |  |  |

| Laminated aluminium bag                                                                                                                                                                                                             | $(520 \times 600 \text{mm})$             | Keeping dry.                                                   |  |  |  |  |  |

| Adhesive tape paper                                                                                                                                                                                                                 |                                          | Fixing of tape carrier package and sparator.                   |  |  |  |  |  |

| Carton                                                                                                                                                                                                                              | Cardboard(420x420x50mm)                  |                                                                |  |  |  |  |  |

| Label                                                                                                                                                                                                                               | Paper                                    | Indicates production name,<br>lot.No., and quantity.           |  |  |  |  |  |

| Desiccant                                                                                                                                                                                                                           | Silica gel                               | Drying of device                                               |  |  |  |  |  |

(2) Packing Form

- a) Tape carrier package(TCP) is wound on a reelwith separators 1 and 2 and the ends of them are fixed with adhesive tape.

- b) A label indicating production name, lot no. and quantity is stuck on one side of the reel.

c) The reel and silica gel is put in a laminated aluminium bag. Nitrogen gas is enclosed in the bag and the bag is sealed. The same label(b) is affixed to the bag. The bag is put in a carton and the same label(b) is affixed to one side of the carton. \* Specification of label

15

| ТҮРЕ      | PRODUCTION NAME<br>LOT NO. |

|-----------|----------------------------|

| QUANTITY  | QUANTITY                   |

| LOT(DATE) | SHIPPING DATE              |

4. Miscellaneous

- (1) The length of the tape carrier is  $34 \approx 46$  meters maximum per reel, and depends on shipping quantity.

- (2) Before unpacking, prepare a work bench equipped with anti-static devices. Also, the operater shoud ware anti-static wrist bands.

- (3) The device, once unpacked, should be stored in a nitrogen gas, room temperature atomosphere and used within 1 week.

| ISSUE DATE   | AUG.24.1994 | APROVE   | CHECK    | DESIGN      | (NOTE) |

|--------------|-------------|----------|----------|-------------|--------|

| ISSUE NUMBER | H6804       | 1 Could  |          | avila       |        |

| S/C NUMBER   |             | A-Sizuti | y. Hands | I. Audoguen |        |

### 🖬 8180798 0027590 274 🖿

8180798 0027591 100 🎟