# CMOS DOT MATRIX HIGH DUTY LCD DRIVER

# DESCRIPTION

The SED1180F and SED1181F are LCD Segment drivers which are used in conjunction with the SED1190F and SED1191F (LCD common drivers).

They can drive a large dot-matrix LCD display with a duty ratio of 1/64 or higher.

#### FEATURES

- 64-bit high voltage resistant output, LCD driver (Segment driver)

- Rightward shift suitable for a 1/64-duty panel

- Allows cascade-connection. Dasy-chain connection of enable pins can be used to minimize power consumption. (SED1180F only)

- SED1180F .....4-bit bus data transfer

- SED1181F .....Independent serial data input for each 32 segment

- Package

Operation Package

Operation

Soperation

Soperation

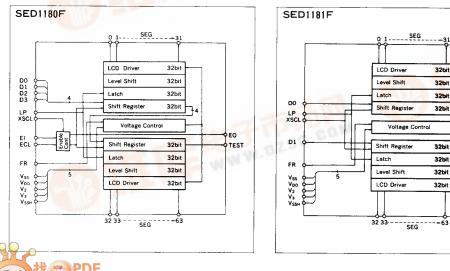

#### BLOCK DIAGRAM

D00

0001

# PIN DESCRIPTION

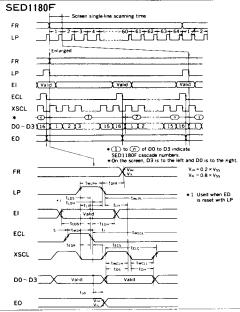

# SED1180F

| Pin Name     | Functions                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------|

| SEG0 to 63   | Outputs to Segment pins of LCD<br>Output level changes at each latch<br>pulse LP falling-edge.       |

| XSCL         | Shift clock for displayed data<br>Falling-edge trigger                                               |

| LP           | Latch pulse for displayed data<br>Falling-edge trigger                                               |

| FR           | LCD display frame signal                                                                             |

| EI           | Enable input ; enabled on "H", disabled<br>on "L"                                                    |

| ECL          | A clock pulse for propagation of enable<br>signals<br>Falling-edge trigger                           |

| EO           | Enable output<br>In cascade connection, EO of nth driver<br>is connected to EI of (n + 1)-th driver. |

| D0 to D3     | 4-bit display data input                                                                             |

| TEST         | Outputs shifted data input from D3                                                                   |

| Vdd, Vss     | Power supply for the logic,<br>V <sub>DD</sub> : 0V (GND), V <sub>SS</sub> : -5.0V                   |

| V2, V3, VSSH | Power supply for driving LCD,<br>V <sub>DD</sub> >V <sub>2</sub> >V <sub>3</sub> >V <sub>SSH</sub>   |

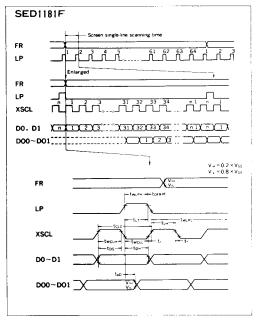

# SED1181F

| Pin Name                          | Functions                                                                                          |  |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SEG0 to 63                        | Outputs to Segment pins of LCD<br>Output level changes at each latch<br>pulse LP falling-edge      |  |  |  |  |  |  |

| XSCL                              | Shift clock for displayed data<br>Falling-edge trigger                                             |  |  |  |  |  |  |

| LP                                | Latch pulse for displayed data<br>Falling-edge trigger                                             |  |  |  |  |  |  |

| FR                                | LCD display frame signal                                                                           |  |  |  |  |  |  |

| DO0                               | Outputs serial display data input from D0.                                                         |  |  |  |  |  |  |

| D01                               | Outputs serial display data input from D1.                                                         |  |  |  |  |  |  |

| D0, D1                            | Input 2-bit serial display data (Data read at a XSCL falling-edge)                                 |  |  |  |  |  |  |

| V <sub>DD</sub> , V <sub>SS</sub> | Power supply for the logic,<br>V <sub>DD</sub> : 0V (GND), V <sub>SS</sub> : -5.0V                 |  |  |  |  |  |  |

| V2, V3, VSSH                      | Power supply for driving LCD,<br>V <sub>DD</sub> >V <sub>2</sub> >V <sub>3</sub> >V <sub>SSH</sub> |  |  |  |  |  |  |

Note :

D : serial display data corresponds to SEG0 to SEG31. D1 : serial display data corresponds to SEG32 to SEG63.

# PIN CONFIGURATION

| 00000                  |                                                            | 99990   |

|------------------------|------------------------------------------------------------|---------|

|                        |                                                            |         |

| <b>€</b><br><b>1</b> 0 | SED1180F                                                   | 35      |

|                        | SED1181F                                                   |         |

|                        | Index<br>10 15 2<br>赤永永永永永大大大大大大大大大大大大大大大大大大大大大大大大大大大大大大大大 |         |

| aaaaa                  | ann an                    | n i i i |

# 1.... SED1180F

| No. | NAME  | No. | NAME  | No. | NAME  | No. | NAME           |

|-----|-------|-----|-------|-----|-------|-----|----------------|

| 1   | SEG27 | 21  | SEG 7 | 41  | SEG36 | 61  | SEG56          |

| 2   | SEG26 | 22  | SEG 6 | 42  | SEG37 | 62  | SEG57          |

| 3   | SEG25 | 23  | SEG 5 | 43  | SEG38 | 63  | SEG58          |

| 4   | SEG24 | 24  | SEG 4 | 44  | SEG39 | 64  | SEG59          |

| 5   | SEG23 | 25  | SEG 3 | 45  | SEG40 | 65  | SEG60          |

| 6   | SEG22 | 26  | SEG 2 | 46  | SEG41 | 66  | SEG61          |

| 7   | SEG21 | 27  | SEG 1 | 47  | SEG42 | 67  | SEG62          |

| 8   | SEG20 | 28  | SEG 0 | 48  | SEG43 | 68  | SEG63          |

| 9   | SEG19 | 29  | EO    | 49  | SEG44 | 69  | VSSH           |

| 10  | SEG18 | 30  | D3    | 50  | SEG45 | 70  | V <sub>2</sub> |

| 11  | SEG17 | 31  | D2    | 51  | SEG46 | 71  | V3             |

| 12  | SEG16 | 32  | D1    | 52  | SEG47 | 72  | Vss            |

| 13  | SEG15 | 33  | D0    | 53  | SEG48 | 73  | VDD            |

| 14  | SEG14 | 34  | XSCL  | 54  | SEG49 | 74  | TEST           |

| 15  | SEG13 | 35  | LP    | 55  | SEG50 | 75  | El             |

| 16  | SEG12 | 36  | FR    | 56  | SEG51 | 76  | ECL            |

| 17  | SEG11 | 37  | SEG32 | 57  | SEG52 | 77  | SEG31          |

| 18  | SEG10 | 38  | SEG33 | 58  | SEG53 | 78  | SEG30          |

| 19  | SEG 9 | 39  | SEG34 | 59  | SEG54 | 79  | SEG29          |

| 20  | SEG 8 | 40  | SEG35 | 60  | SEG55 | 80  | SEG28          |

# SED1181F

| No. | NAME  | No. | NAME  | No. | NAME  | No. | NAME           |

|-----|-------|-----|-------|-----|-------|-----|----------------|

| 1   | SEG27 | 21  | SEG 7 | 41  | SEG36 | 61  | SEG56          |

| 2   | SEG26 | 22  | SEG 6 | 42  | SEG37 | 62  | SEG57          |

| 3   | SEG25 | 23  | SEG 5 | 43  | SEG38 | 63  | SEG58          |

| 4   | SEG24 | 24  | SEG 4 | 44  | SEG39 | 64  | SEG59          |

| 5   | SEG23 | 25  | SEG 3 | 45  | SEG40 | 65  | SEG60          |

| 6   | SEG22 | 26  | SEG 2 | 46  | SEG41 | 66  | SEG61          |

| 7   | SEG21 | 27  | SEG 1 | 47  | SEG42 | 67  | SEG62          |

| 8   | SEG20 | 28  | SEG 0 | 48  | SEG43 | 68  | SEG63          |

| 9   | SEG19 | 29  | D00   | 49  | SEG44 | 69  | VSSH           |

| 10  | SEG18 | 30  | NC    | 50  | SEG45 | 70  | V <sub>2</sub> |

| 11  | SEG17 | 31  | NC    | 51  | SEG46 | 71  | V <sub>3</sub> |

| 12  | SEG16 | 32  | D1    | 52  | SEG47 | 72  | Vss            |

| 13  | SEG15 | 33  | D0    | 53  | SEG48 | 73  | VDD            |

| 14  | SEG14 | 34  | XSCL  | 54  | SEG49 | 74  | D01            |

| 15  | SEG13 | 35  | LP    | 55  | SEG50 | 75  | NC             |

| 16  | SEG12 | 36  | FR    | 56  | SEG51 | 76  | NC             |

| 17  | SEG11 | 37  | SEG32 | 57  | SEG52 | 77  | SEG31          |

| 18  | SEG10 | 38  | SEG33 | 58  | SEG53 | 78  | SEG30          |

| 19  | SEG 9 | 39  | SEG34 | 59  | SEG54 | 79  | SEG29          |

| 20  | SEG 8 | 40  | SEG35 | 60  | SEG55 | 80  | SEG28          |

#### **MABSOLUTE MAXIMUM RATINGS**

```

(V_{DD} = \mathbf{0}V)

```

|                                |                                 |                             | (*00-) |  |

|--------------------------------|---------------------------------|-----------------------------|--------|--|

| Parameter                      | Symbol                          | Ratings                     | Unit   |  |

| Supply voltage (1)             | V <sub>SS</sub>                 | -7.0 to 0.3                 | v      |  |

| Supply voltage (2)             | V <sub>SSH</sub>                |                             | v      |  |

| Supply Voltage (2)             | V <sub>2</sub> , V <sub>3</sub> | -28.0 to $0.3$              |        |  |

| Input voltage                  | VI                              | V <sub>SS</sub> -0.3 to 0.3 | V      |  |

| Operating temperature          | T <sub>opr</sub>                | -20 to 75                   | Ĵ,     |  |

| Storage temperature            | T <sub>stg</sub>                | -65 to 150                  | Ĵ      |  |

| Soldering temperature and time | T <sub>sol</sub>                | 260°C • 10s (at lead)       |        |  |

# **BELECTRICAL CHARACTERISTICS**

# •DC Electrical Characteristics

| Parameter                    | Symbol               | Con                                    | ditions                                                                                                                           | Min                  | Тур  | Max                  | Unit |

|------------------------------|----------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|------|

| Supply voltage (1)           | Vss                  |                                        |                                                                                                                                   | -5.5                 | -5.0 | -4.5                 | v    |

|                              | V <sub>2</sub>       |                                        |                                                                                                                                   | V <sub>SSH</sub>     |      | V <sub>DD</sub>      | v    |

| Supply voltage (2)           | V <sub>3</sub>       | -                                      |                                                                                                                                   | V <sub>SSH</sub>     |      | V <sub>DD</sub>      | V    |

|                              | V.                   | Recomm                                 | ended V <sub>SSH</sub>                                                                                                            | -25.0                |      | -14.0                | v    |

|                              | V <sub>SSH</sub>     | Operab                                 | Operable V <sub>SSH</sub> *                                                                                                       |                      |      | -5.0                 | v    |

| High level input voltage     | VIH                  |                                        |                                                                                                                                   | 0.2V <sub>SS</sub>   |      | V <sub>DD</sub> +0.3 | v    |

| Low level input voltage      | VIL                  |                                        |                                                                                                                                   | V <sub>SS</sub> -0.3 |      | 0.8V <sub>SS</sub>   | v    |

| High level output voltage    | V <sub>OH</sub>      | I <sub>ОН</sub> =                      | -0.6mA                                                                                                                            | -0.4                 |      |                      | V    |

| Low level output voltage     | VOL                  | I <sub>OL</sub> =                      | 0.6mA                                                                                                                             | —                    |      | V <sub>SS</sub> +0.4 | v    |

| Input leak current           | I <sub>LI</sub>      | 0v≤                                    | V₁≦V <sub>SS</sub>                                                                                                                | _                    | 0.05 | 2.0                  | μA   |

| Output leak current          | ILO                  | 0v≤v                                   | V₀≦V <sub>SS</sub>                                                                                                                | _                    | 0.05 | 5.0                  | μA   |

| Shift clock                  | XSCL                 |                                        |                                                                                                                                   | _                    |      | 6.0                  | MHz  |

| Frame signal                 | FR                   |                                        |                                                                                                                                   | _                    | 1/60 | _                    | s    |

| Input capacitance            | Cı                   | Ta = 25°C                              |                                                                                                                                   | _                    | 5.0  | 8.0                  | pF   |

|                              | R <sub>SEG</sub>     | V V 0.6V                               | $V_{\rm SSH} = -20.0V$ $V_{\rm SSH} = -14.0V$                                                                                     | _                    | 1.9  | 2.9                  | kΩ   |

| Segment output               |                      | $V_{\alpha} = V_{\alpha\alpha} + 0.5V$ | $V_{SSH} = -14.0V$                                                                                                                | _                    | 2.4  | 3.9                  |      |

| on resistance                |                      |                                        | $V_{\rm SSH} = - 9.0V$                                                                                                            | _                    | 3.6  | 7.0                  |      |

|                              |                      | SEG / DIL                              | $V_{SSH} = -5.0V$                                                                                                                 |                      | 11.5 | 500.0                |      |

| Quiescent current            | l <sub>Q</sub>       | $V_{SSH} = -25V$ $V_1 = V_{DD}$        | $V_{\rm ss} = -5.5V$                                                                                                              | _                    | 0.05 | 30                   | μA   |

| Operating current            |                      | SED 16.7ms<br>1180 ECL cycle =         | LP cycle = 130µs<br>XSCL = 1.5MHz                                                                                                 | _                    | 90   | 200                  |      |

| for the logic                | 1550                 |                                        | (duty50%)<br>All data input reversed bit<br>by bit.<br>All output pins are opened.                                                | -                    | 850  | 1200                 | μA   |

| Operating current<br>for LCD | ing current Issно SE | FR cycle =                             | $V_{SS} = -4.5V, V_2 = -4.0V$<br>$V_1 = -16.0V, V_{SSH} = -20.0V$<br>$V_{1H} = V_{DD}, V_{1L} = V_{SS}$<br>LP cycle = $130 \mu s$ | _                    | 40   | 80                   |      |

|                              |                      | SED FR cycle =<br>1181 (duty50%)       | XSCL = 1.5MHz<br>(duty50%)<br>All data input reversed bit<br>by bit.<br>All output pins are opened.                               |                      | 70   | 100                  | μA   |

\* Operable VssH indicates its functionally operable range although the driver output ON resistance becomes higher than with recommended V<sub>SSH</sub>.

To determine the voltage, we recommend to test the driver with a liquid crystal panel.

| Parameter                      | Symbol           | Conditions | Min   | Тур | Max | Unit |

|--------------------------------|------------------|------------|-------|-----|-----|------|

| hift clock cycle               | t <sub>CLC</sub> |            | 166   |     |     | ns   |

| Shift clock "H" width          | twclh            |            | 63    | _   |     | ns   |

| Shift clock "L" width          | twcll            |            | 63    |     |     | ns   |

| Data setup time                | t <sub>DS</sub>  |            | 50    | —   | —   | ns   |

| Data hold time                 | t <sub>DH</sub>  |            | 30    |     |     | ns   |

| Enable clock "H" width         | twech            | * 3        | 100   |     |     | ns   |

| Enable clock "L" width         | twecl            | * 3        | 100   |     |     | ns   |

| Enable data setup time         | t <sub>EDS</sub> | * 3        | 50    |     | -   | ns   |

| Enable data hold time          | tedh             | * 3        | 20    |     |     | ns   |

| Enable clock delay time        | t <sub>EDR</sub> | * 3        | - 10  |     |     | ns   |

| Enable clock setup time        | t <sub>ECS</sub> | *3         | 70    |     |     | ns   |

| Latch pulse "H" width          | twlph            | *1         | 110   | -   |     | ns   |

| Latch pulse "L" width          | twlpl            |            | 220   |     |     | ns   |

| Latch timing                   | t <sub>LT</sub>  |            | 100   | _   |     | ns   |

| Latch hold time                | t <sub>LH</sub>  |            | 0     |     |     | ns   |

| Latch pulse data setup time    | t <sub>LDS</sub> | *2, *3     | 140   | -   |     | ns   |

| Latch pulse data hold time     | t <sub>LDH</sub> | *2, *3     | 50    | —   | -   | ns   |

| Permissible frame signal delay | t <sub>DFR</sub> |            | - 500 | _   | 500 | ns   |

| Input signal rise time         | tr               |            |       |     | *4  |      |

| Input signal fall time         | ti               |            |       | _   | *4  |      |

| Enable output delay            | t <sub>PD</sub>  | * 3        | 20    | _   | 150 | ns   |

| Serial data output delay       | t <sub>PO</sub>  |            | 20    | _   | 150 | ns   |

\*1 twLPH=160ns (Min) when LP is used as EI data.

\*3 Applicable to SED1180F only.

\*4 tr, tf <(tc\_c - twc\_l - twc\_l)/2, where tr, tf  $\leq$  50ns.

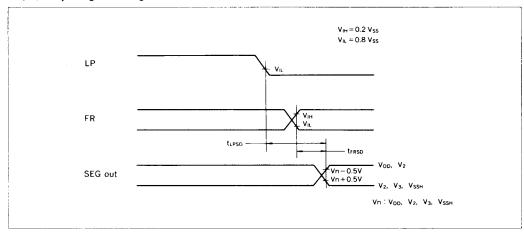

**•**SEG Output Signal Timing Characteristics

# $(V_{DD} = 0V, V_{SS} = -5V \pm 10\%, Ta = -20 \text{ to } 75^{\circ}\text{C})$

| Parameter                | Symbol            | Conditions                    | Min | Тур | Max | Unit |

|--------------------------|-------------------|-------------------------------|-----|-----|-----|------|

| LP-SEG output delay time | t <sub>LPSD</sub> | $V_{SSH} = -14.0$ to $-25.0V$ |     |     | 4.5 | μs   |

| FR-SEG output delay time | t <sub>FRSD</sub> | $C_L = 100 pF$                |     |     | 4.5 | μs   |

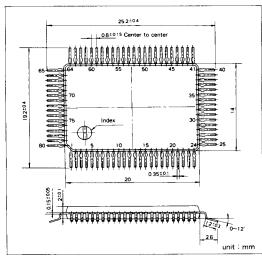

#### PACKAGE DIMENSIONS

\*Drawing is applicable to SED1180F<sub>0A</sub>/SED1181F<sub>0B</sub>. \*SED1180F<sub>5A</sub>/SED1181F<sub>5A</sub> are 2.7mm thick.

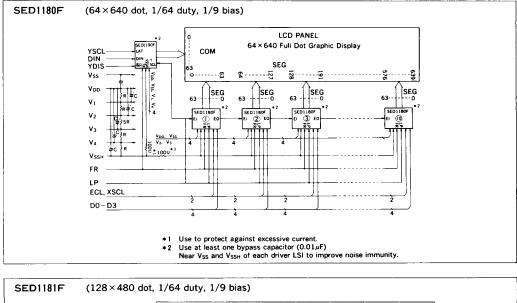

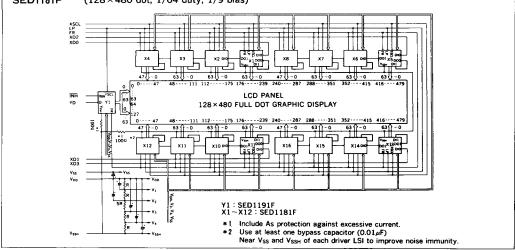

### **EXAMPLE OF APPLICATION**