E2D0017-27642 M66P54-xx,供应商

## 捷多邦,专业PCB打样工厂,24小时加急

**OKI** Semiconductor

出货 This version: Jan. 1998 Previous version: May. 1997

# MSM6652/53/54/55/56-xxx, MSM6652A/53A/ 54A/55A/56A/58A-xxx, MSM66P54-xx,

# MSM66P56-xx (Under development), MSM6650

Internal Mask ROM Voice Synthesis IC, Internal One-Time-Programmable (OTP) ROM Voice Synthesis IC, External ROM Drive Voice Synthesis IC

# **GENERAL DESCRIPTION**

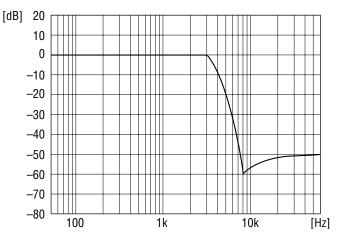

The MSM6650 family is the successor to OKI's MSM6375 family. To ensure high-quality voice synthesis, the MSM6650 family members offer adaptive differential pulse-code modulation (ADPCM) playback, pulse-code modulation (PCM) playback, 12-bit D/A conversion, and on-chip –40 dB/ octave low-pass filter (LPF).

The conventional "beep" tones and 2-channel playback are now easier to use. OKI has added additional functions such as melody play, fade-out, and random playback. OKI has improved external control by adding an Edit ROM. The Edit ROM can be used to form sentences by linking phrases.

The MSM6650 family members can support a variety of applications as it can function in either Standalone Mode or Microcontroller Interface Mode. In Microcontroller Interface Mode, serial input control is available. Serial input control minimizes the number of microcontroller port pins required for voice synthesis control. The MSM6650 family includes an internal mask ROM version, internal one-time-programmable (OTP) ROM version, and external ROM version. The features of the MSM6650 family devices are as follows.

• MSM6652/53/54/55/56-xxx

These devices are single-chip voice synthesizers with an on-chip mask ROM using the CMOS technology.

Standalone Mode or Microcontroller Interface Mode can be selected by mask option. • MSM6652A/53A/54A/55A/56A/58A-xxx

- The trial production period for these devices is shorter than those described above. These devices are suitable for developing prototype models and concept demonstration of new products. • MSM66P54-xx, MSM66P56-xx

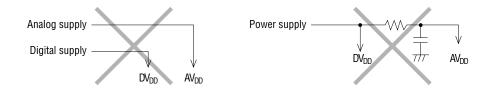

- The device is a single-chip CMOS voice synthesizer with one-time-programmable (OTP) ROM. Standalone and Microcontroller Interface Modes are selected by using a code (01-04). The user can easily write voice data using the development tool AR761 or AR762, or P54 adapter. Unlike the mask ROM version, the OTP version is suited to applications which requires a small lot production of different type devices or short delivery time.

- MSM6650

f.dzsc.com

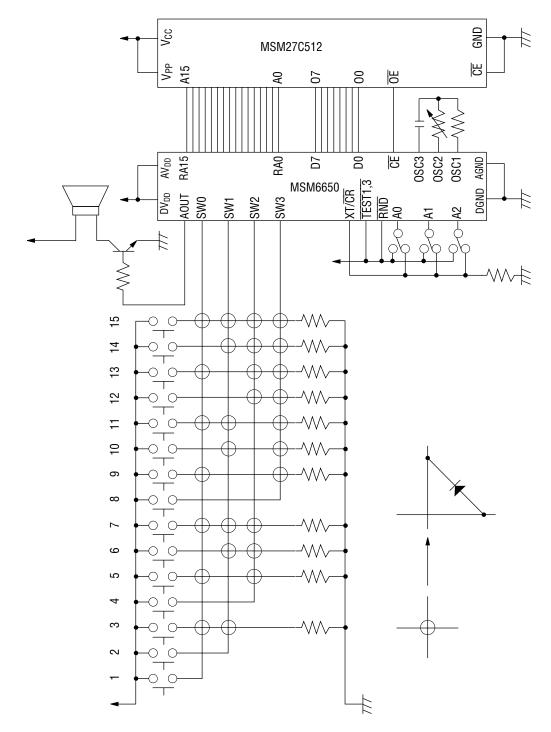

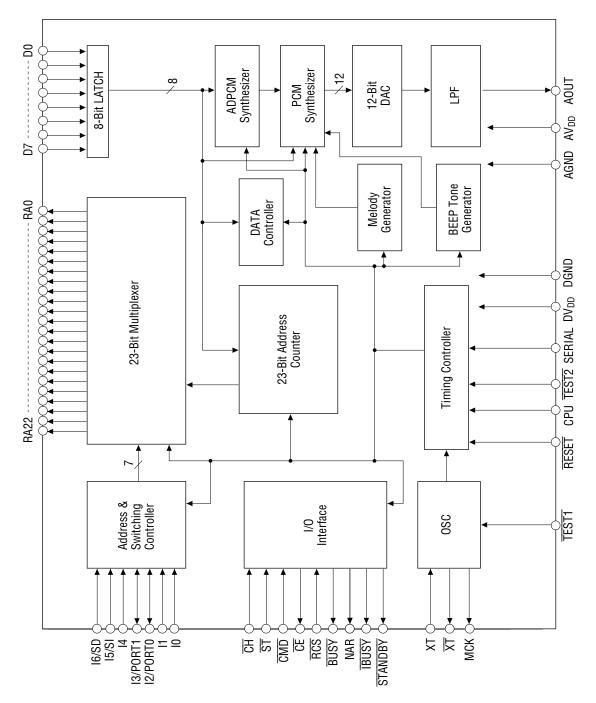

The MSM6650 device can directly connect external ROM or EPROM of up to 64 Mbits, which stores voice data.

This device is ideally suited to an evaluation IC for the MSM6650 family because its circuit configuration is identical to those of the mask ROM-based and OTP version devices.

# CONTENTS

#### **Standalone Mode**

| FEATURES                                | 5  |

|-----------------------------------------|----|

| BLOCK DIAGRAMS                          | 7  |

| PIN CONFIGURATION                       | 10 |

| PIN DESCRIPTIONS 1                      | 13 |

| ABSOLUTE MAXIMUM RATINGS 1              |    |

| RECOMMENDED OPERATING CONDITIONS 1      | 18 |

| ELECTRICAL CHARACTERISTICS 1            | 19 |

| TIMING DIAGRAMS                         | 21 |

| FUNCTIONAL DESCRIPTION                  | 23 |

| 1. PLAYBACK CODE SPECIFICATION 2        | 23 |

| 2. INTERNAL ROM USAGE AND DISABLED AREA | 23 |

| 3. PULL-UP/PULL-DOWN RESISTOR           | 23 |

| 4. OPTION(S)                            | 24 |

| 5. STANDALONE MODE                      | 24 |

| 6. SAMPLING FREQUENCY                   | 30 |

| 7. VOICE PLAYBACK TIME                  | 31 |

| 8. CHANNEL STATUS                       | 31 |

| 9. PLAYBACK METHOD                      |    |

| 10. STANDBY CONVERSION                  | 34 |

| 11. VOICE OUTPUT                        |    |

| 12. LOW-PASS FILTER POP NOISE           |    |

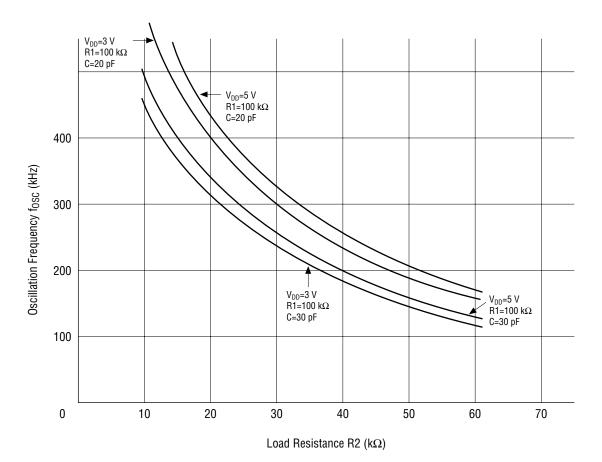

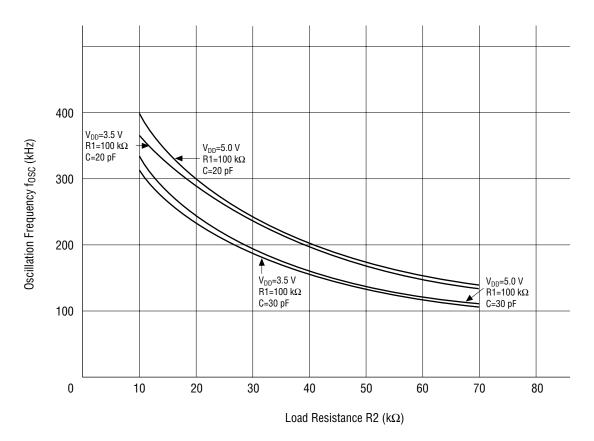

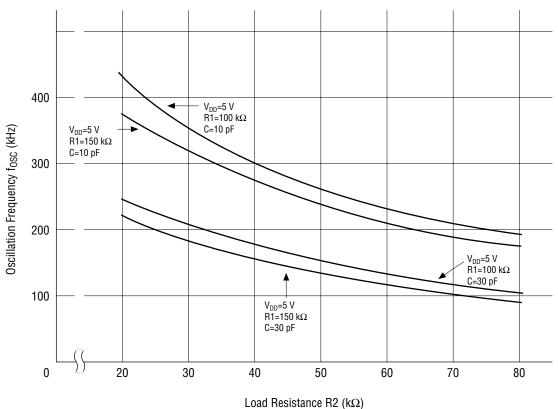

| 13. RC OSCILLATION                      | 37 |

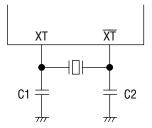

| 14. CERAMIC OSCILLATION 4               | 41 |

| 15. POWER SUPPLY 4                      | 42 |

| APPLICATION CIRCUITS 4                  | 43 |

#### Microcontroller Interface Mode

| FEATURES                                | . 47 |

|-----------------------------------------|------|

| BLOCK DIAGRAMS                          | . 49 |

| PIN CONFIGURATION                       | . 52 |

| PIN DESCRIPTIONS                        | . 55 |

| ABSOLUTE MAXIMUM RATINGS                |      |

| RECOMMENDED OPERATING CONDITIONS        | . 61 |

| ELECTRICAL CHARACTERISTICS              | . 62 |

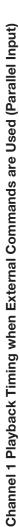

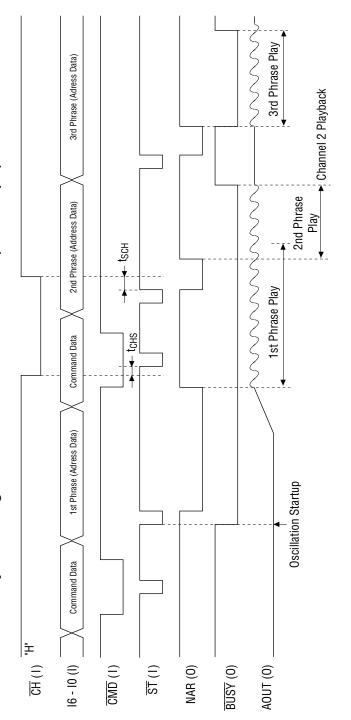

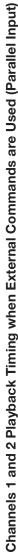

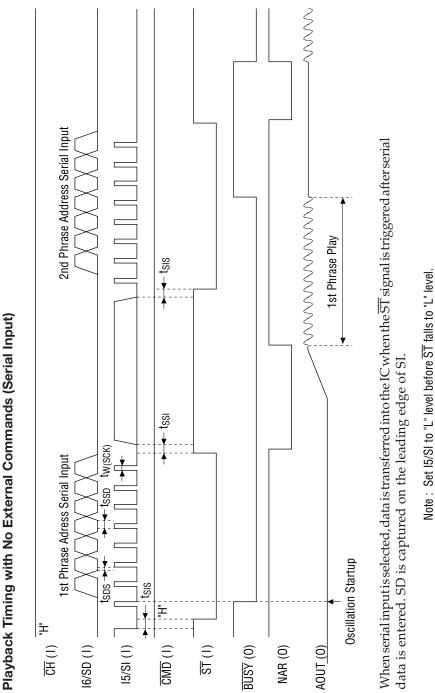

| TIMING DIAGRAMS                         | . 64 |

| FUNCTIONAL DESCRIPTION                  | . 70 |

| 1. PLAYBACK CODE SPECIFICATION          | . 70 |

| 2. INTERNAL ROM USAGE AND DISABLED AREA |      |

| 3. PULL-UP/PULL-DOWN RESISTOR           |      |

| 4. OPTIONS                              |      |

| 5. MICROCONTROLLER INTERFACE MODE       |      |

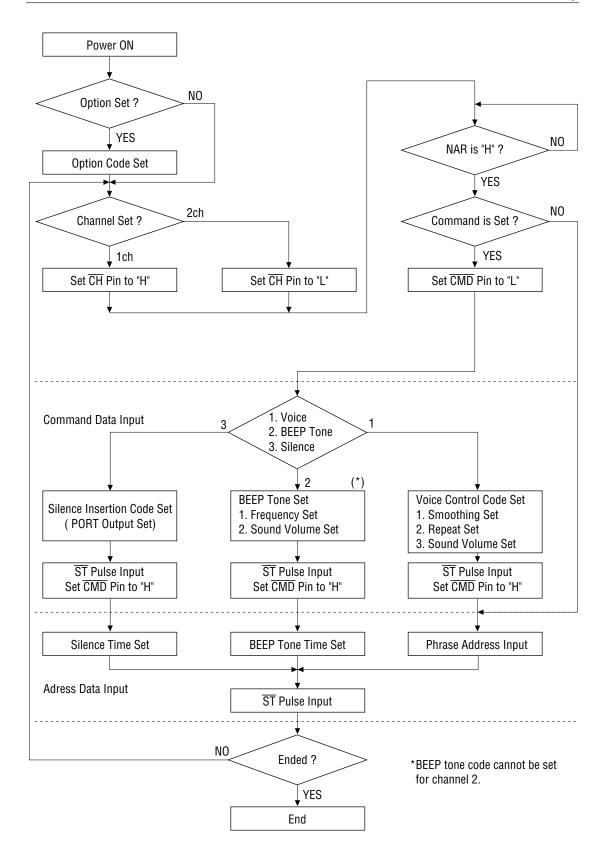

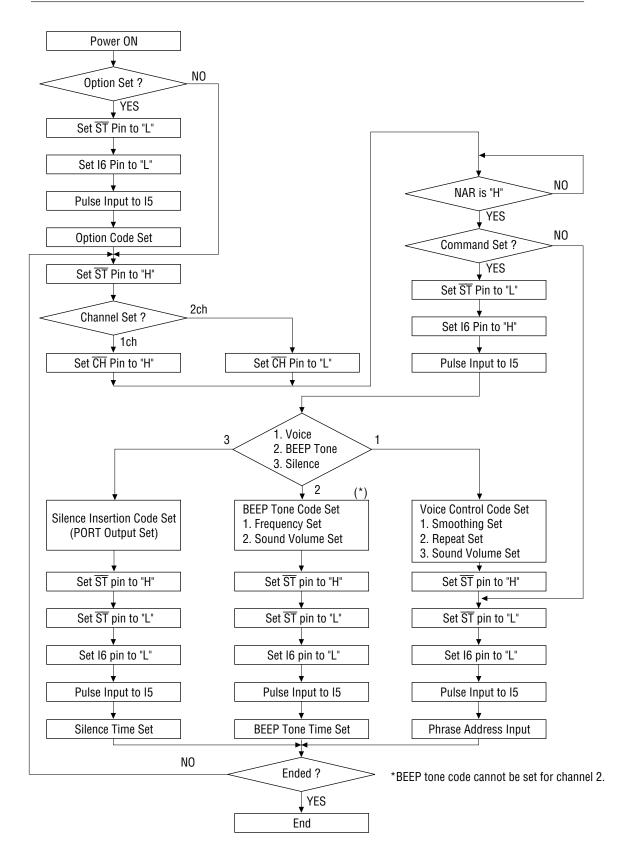

| 6. COMMAND DATA                         | . 78 |

| 7. ADDRESS DATA                         |      |

| 8. STOP CODE                            |      |

| 9. SAMPLING FREQUENCY                   |      |

| 10. VOICE PLAYBACK TIME                 |      |

| 11. CHANNEL STATUS                      | . 90 |

| 12. PLAYBACK METHOD                     |      |

| 13. STANDBY CONVERSION                  |      |

| 14. VOICE OUTPUT                        |      |

| 15. LOW-PASS FILTER POP NOISE           |      |

| 16. CERAMIC OSCILLATION                 |      |

| 17. POWER SUPPLY                        |      |

| 18. EXTERNAL ROM DRIVING TIMING         |      |

| APPLICATION CIRCUITS                    | 100  |

## Edit ROM

| EDIT ROM                                                | 104 |

|---------------------------------------------------------|-----|

| ECHO PLAYBACK OF A SINGLE PHRASE                        | 113 |

| ECHO PLAYBACK OF MULTIPLE PHRASES                       | 116 |

| ECHO PLAYBACK OF A SINGLE PHRASE WITHIN A PHRASE STRING | 117 |

The table below shows the major differences between the MSM6650 family and the MSM6375 family.

|                                                   | MSM6650 Family                                                                                         | MSM6375 Family                                                                                                                                               |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface                                         | Standalone mode/Microcontroller interface mode                                                         | SW input/CPU input interface                                                                                                                                 |

| Voice synthesis method                            | 4-bit ADPCM or 8-bit PCM/Melody PCM                                                                    | 4-bit ADPCM                                                                                                                                                  |

| "Beep" tone frequecy                              | 0.5, 1.0, 1.3, 2.0 kHz                                                                                 | 1.0 or 2.0 kHz, (User-specified length,                                                                                                                      |

| (length)                                          | Options (16 ms to 2100 ms)                                                                             | fixed at either 64, 128, 250, or 500 ms)                                                                                                                     |

| Sampling frequency (f <sub>SAM</sub> )            | Eight frequencies<br>(4.0, 5.3, 6.4, 8.0, 10.6, 12.8, 16.0, or 32.0 kHz)                               | Three frequencies at two oscillator frequencies<br>(4.0, 6.4, 8.0 kHz with f <sub>OSC</sub> =64 kHz;<br>16.0, 25.6, 32.0 kHz with f <sub>OSC</sub> =256 kHz) |

| Master clock frequency (fosc)                     | 256 kHz (RC)/4.096 MHz (ceramic/crystal)                                                               | 40 kHz to 256 kHz                                                                                                                                            |

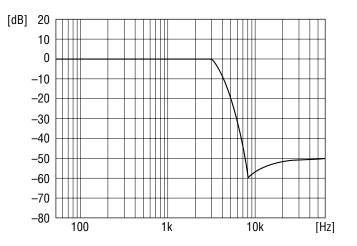

| LPF attenuation factor                            | -40 dB/octave                                                                                          | -24 dB/octave                                                                                                                                                |

| LPF cut-off frequency (f <sub>CUT</sub> ),<br>kHz | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                       |

| Maximum phrase number                             | 127                                                                                                    | 111                                                                                                                                                          |

| Pull-up/pull-down resistors                       | Built in                                                                                               | _                                                                                                                                                            |

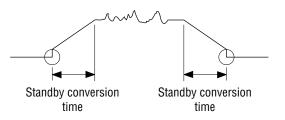

| Standby conversion time                           | 0.2 sec                                                                                                | 3 sec                                                                                                                                                        |

| Mask options                                      | 4 options                                                                                              | 14 options                                                                                                                                                   |

| Added function in edit ROM                        | Edit ROM<br>Fade-out<br>Random playback<br>Melody playback<br>PCM playback<br>Serial input/port output | _                                                                                                                                                            |

# **STANDALONE MODE**

# **FEATURES**

| Device name    | ROM size       | Maximum playback time (sec) |                           |                           |                          |  |

|----------------|----------------|-----------------------------|---------------------------|---------------------------|--------------------------|--|

|                | NOIVI SIZE     | f <sub>SAM</sub> =4.0 kHz   | f <sub>SAM</sub> =6.4 kHz | f <sub>SAM</sub> =8.0 kHz | f <sub>SAM</sub> =16 kHz |  |

| MSM6652, 6652A | 288 Kbits      | 16.9                        | 10.5                      | 8.4                       | 4.2                      |  |

| MSM6653, 6653A | 544 Kbits      | 31.2                        | 19.5                      | 15.6                      | 7.8                      |  |

| MSM6654, 6654A | 1 Mbit         | 63.8                        | 39.9                      | 31.9                      | 15.9                     |  |

| MSM6655, 6655A | 1.5 Mbits      | 96.5                        | 60.3                      | 48.2                      | 24.1                     |  |

| MSM6656, 6656A | 2 Mbits        | 129.1                       | 80.7                      | 64.5                      | 32.2                     |  |

| MSM6658A       | 4 Mbits        | 259.7                       | 162.9                     | 129.8                     | 64.9                     |  |

| MSM66P54       | 1 Mbit         | 63.8                        | 39.9                      | 31.9                      | 15.9                     |  |

| MSM66P56       | 2 Mbit         | 129.1                       | 80.7                      | 64.5                      | 32.2                     |  |

| MSM6650        | 64 Mbits (Max) | 4194.3                      | 2620.5                    | 2096.4                    | 1048.2                   |  |

Note: Actual voice ROM area is smaller by 22 Kbits.

- 4-bit ADPCM or 8-bit PCM sound generation

- Melody function

- Edit ROM function

- Two-channel mixing function

- Built-in random playback function

- Fade-out function via four-step sound volume attenuation

- Built-in beep tone of 0.5 kHz, 1.0 kHz, 1.3 kHz, or 2.0 kHz selectable with a specific code

- Sampling frequency of 4.0 kHz, 5.3 kHz, 6.4 kHz, 8.0 kHz, 10.6 kHz, 12.8 kHz, 16.0 kHz, or 32.0 kHz (32 kHz sampling is not possible when using RC oscillation)

- Up to 120 phrases

- Built-in 12-bit D/A converter

- Built-in -40 dB/octave low-pass filter

- Standby function

- Selectable RC or ceramic oscillation

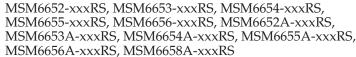

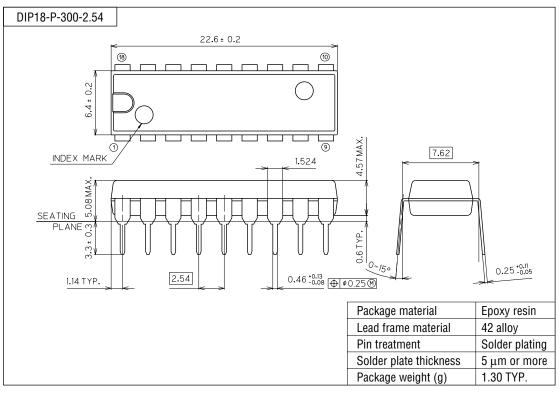

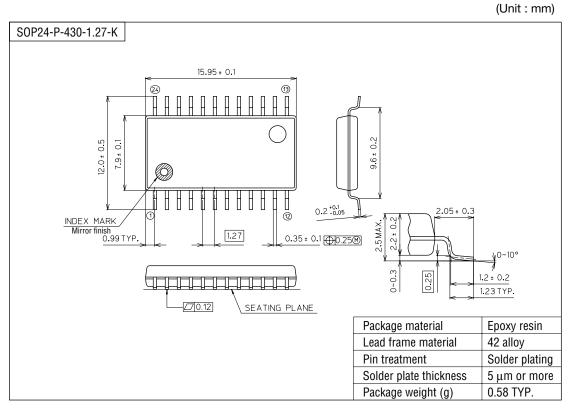

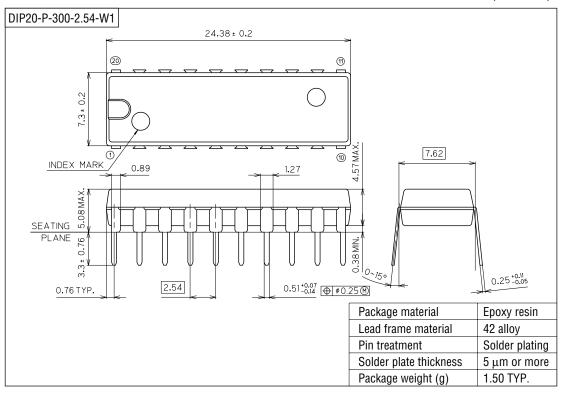

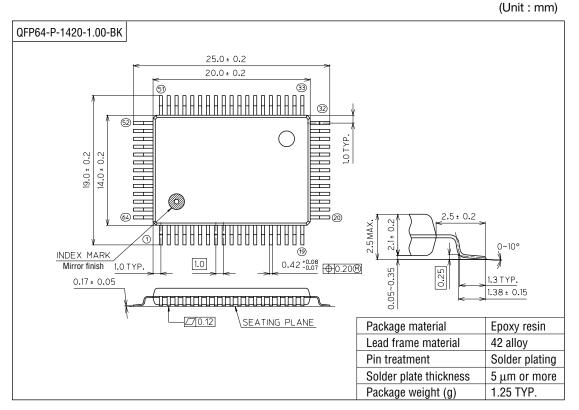

- Package options:

| i dekuge options.                        |                  |                                    |

|------------------------------------------|------------------|------------------------------------|

| 18-pin plastic DIP (DIP18-P-300-2.54)    | (Product name:   | MSM6652-xxxRS/MSM6653-xxxRS/       |

|                                          |                  | MSM6654-xxxRS/MSM6655-xxxRS/       |

|                                          |                  | MSM6656-xxxRS/MSM6652A-xxxRS/      |

|                                          |                  | MSM6653A-xxxRS/MSM6654A-xxxRS/     |

|                                          |                  | MSM6655A-xxxRS/MSM6656A-xxxRS/     |

|                                          |                  | MSM6658A-xxxRS)                    |

| 24-pin plastic SOP (SOP24-P-430-1.27-K)  | (Product name:   | MSM6652-xxxGS-K/MSM6653-xxxGS-K    |

|                                          |                  | MSM6654-xxxGS-K/MSM6655-xxxGS-K/   |

|                                          |                  | MSM6656-xxxGS-K/MSM6652A-xxxGS-K/  |

|                                          |                  | MSM6653A-xxxGS-K/MSM6654A-xxxGS-K/ |

|                                          |                  | MSM6655A-xxxGS-K/MSM6656A-xxxGS-K/ |

|                                          |                  | MSM6658A-xxxGS-K/MSM66P54-03GS-K/  |

|                                          |                  | MSM66P54-04GS-K/MSM66P56-03GS-K/   |

|                                          |                  | MSM66P56-04GS-K)                   |

| 20-pin plastic DIP (DIP20-P-300-2.54-W1) | (Product name:   | MSM66P54-03RS/MSM66P54-04RS/       |

|                                          |                  | MSM66P56-03RS/MSM66P56-04RS)       |

| 64-pin plastic QFP (QFP64-P-1420-1.00-BK | ) (Product name: | MSM6650GS-BK)                      |

• Option Table

|                              |          |              | Interface Mode | Standalo     | ne Mode    | -  |

|------------------------------|----------|--------------|----------------|--------------|------------|----|

|                              | Pin Name | Serial Input | Parallel Input | With Standby | No Standby | -  |

| MSM6652/53/54/55/56          |          | Mask Option  |                |              |            |    |

| MSM6652A/53A/54A/55A/56A/58A |          |              |                |              |            |    |

| MSM66P54/P56                 |          | -01          | -02            | -03          | -04        | *2 |

|                              | CPU      | "H"          | "H"            | "L"          | "L"        | -  |

| MSM6650                      | SERIAL   | "H"          | "L"            | "L"          | "L"        | -  |

|                              | STBY     |              | —              | "L"          | "H"        | -  |

\*1. The options for the mask ROM-based devices are mask options. The user should send OKI an option list before starting development. A sample of option list is shown below.

\*2. A code of OTP version device corresponds to one of the options. The user should specify either MSM66P54-03 or MSM66P54-04 or MSM66P56-03 or MSM66P56-04. (In this case, no option list is required.)

|              |                    |                         |                     |                    | Date: |

|--------------|--------------------|-------------------------|---------------------|--------------------|-------|

|              |                    | Optio                   | <u>n List</u>       |                    |       |

| You are req  | uested to develo   | o MSM665X-XXX on the fo | llowing conditions. |                    |       |

| 1. Options   |                    |                         |                     |                    |       |

|              | •                  | MSM6650 family.         |                     |                    |       |

| Choose and   | circle the desired | d option.               |                     |                    |       |

|              | Option             | Interface mode          | Input               | Standby conversion |       |

|              | Option A           | Microcontroller         | Serial              | _                  |       |

|              | Option B           | Microcontroller         | Parallel            | _                  |       |

|              | Option C           | Standalone              | _                   | Yes                |       |

|              | Option D           | Standalone              | _                   | No                 |       |

|              |                    | · · ·                   |                     |                    | •     |

| 0 Declara    |                    |                         |                     |                    |       |

| 2. Package a | inu quantity       |                         |                     |                    |       |

|                         | (circle t               | he desired one)         | Quantity | Note                   |                                                      |

|-------------------------|-------------------------|-------------------------|----------|------------------------|------------------------------------------------------|

| Ceramic<br>sample       | 18-pin DIP<br>(ceramic) | 24-pin SOP<br>(ceramic) | chip     | pcs                    | Up to 10 samples.<br>Operating temp. :<br>10 to 30°C |

| Mold<br>sample          | 18-pin DIP<br>(plastic) | 24-pin SOP<br>(plastic) | chip     | pcs                    | Up to 50 samples                                     |

| Mass<br>produc-<br>tion | 18-pin DIP<br>(plastic) | 24-pin SOP<br>(plastic) | chip     | pcs per lot<br>monthly |                                                      |

|                         |                         |                         |          |                        | Signed by                                            |

|                         |                         |                         |          |                        | Title ·                                              |

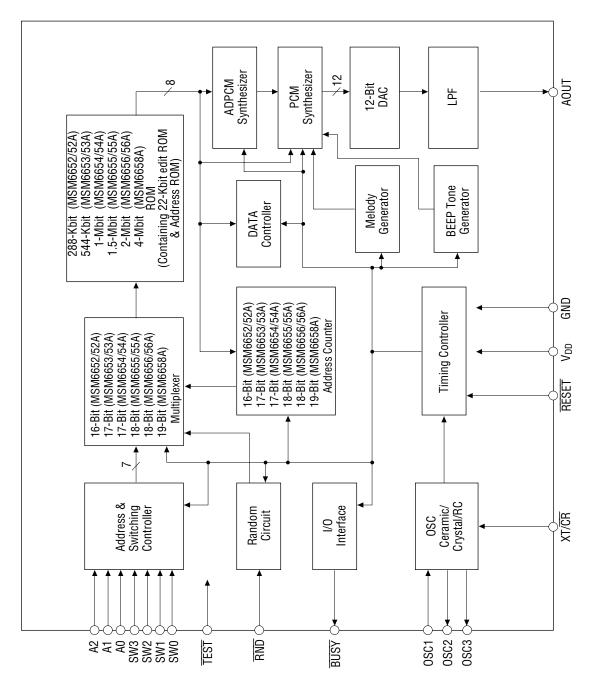

# **BLOCK DIAGRAMS**

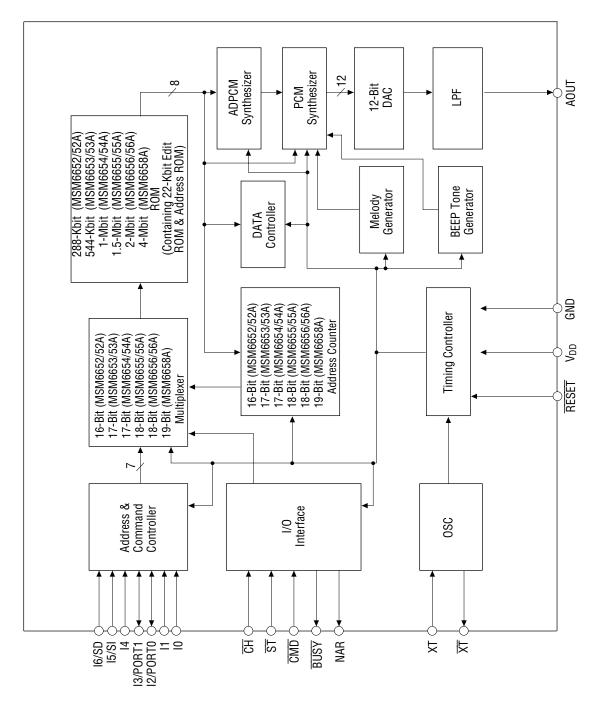

MSM6652/53/54/55/56-xxx MSM6652A/53A/54A/55A/56A/58A-xxx

#### MSM6650 Family

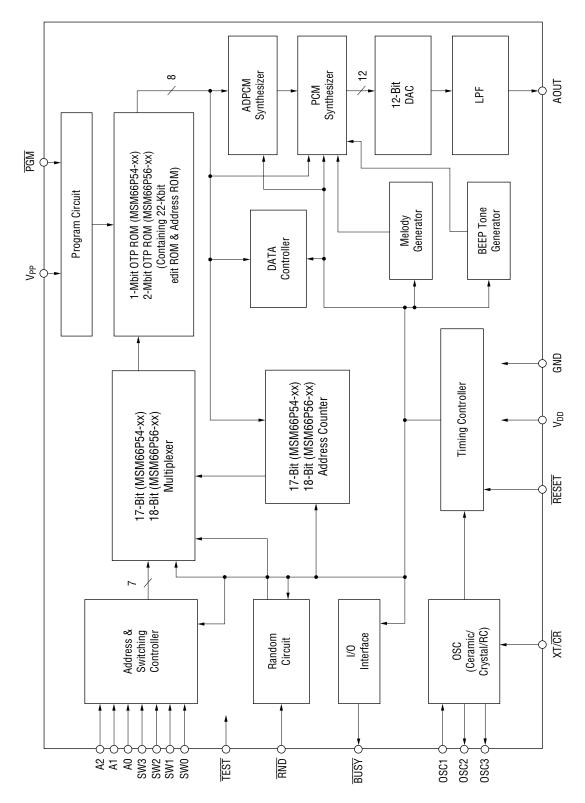

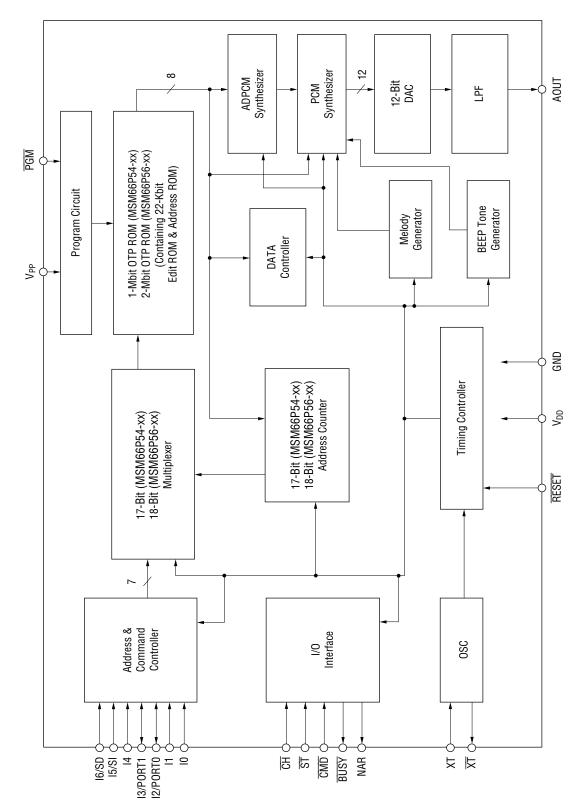

#### MSM66P54/P56-xx

#### MSM6650 Family

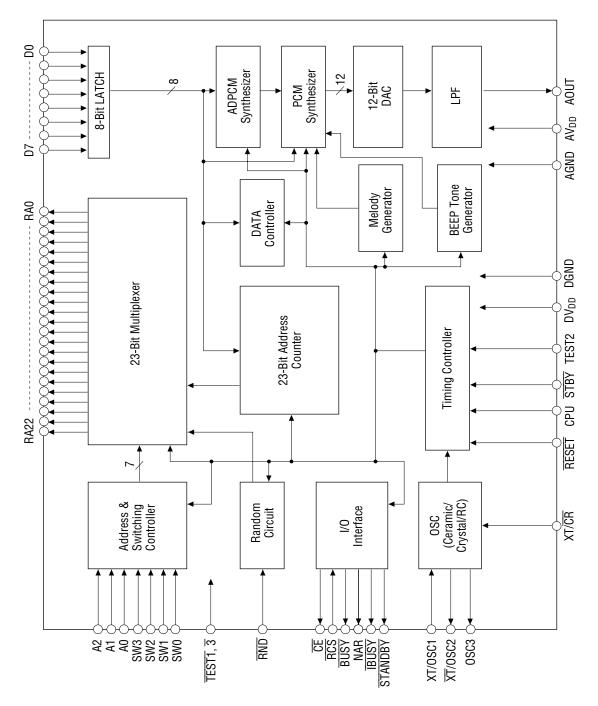

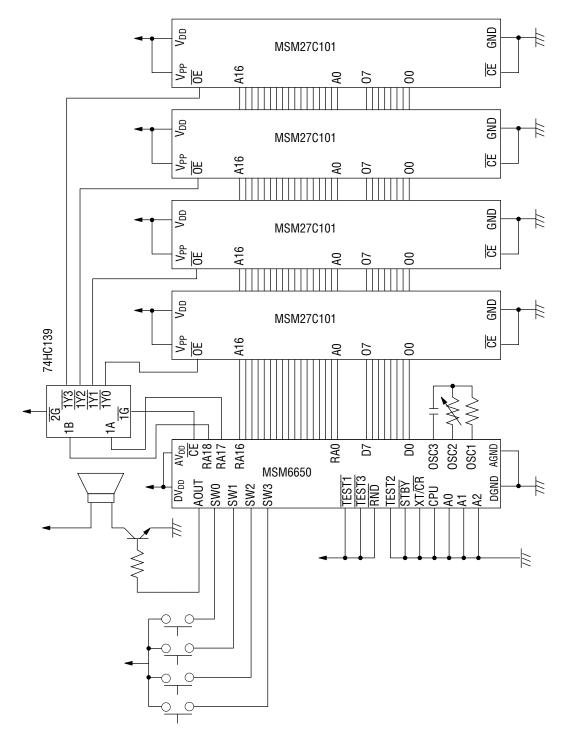

#### MSM6650

$\mathsf{V}_{\mathsf{D}\mathsf{D}}$

OSC1

OSC2

OSC3

NC 4

NC

NC 7

RND

SW0

SW1 10

SW2 11

SW3 12

1

2

3

5

6

8

9

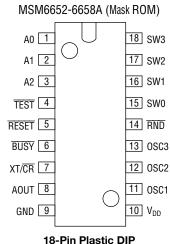

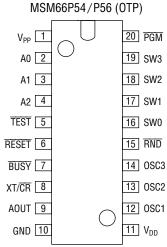

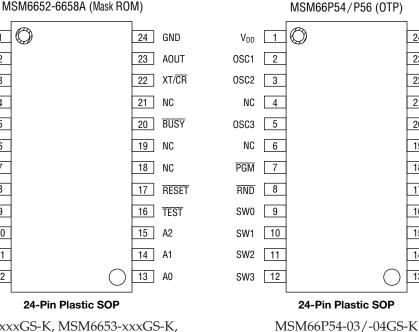

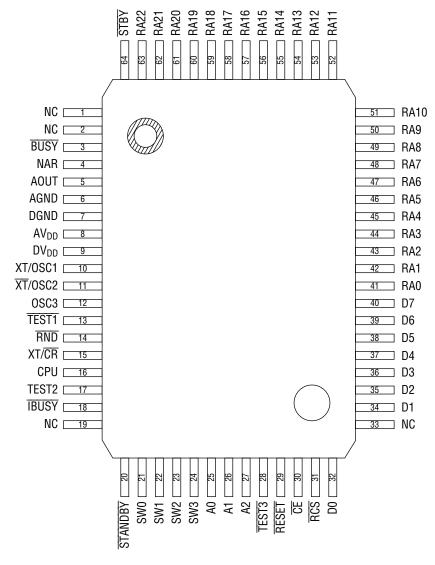

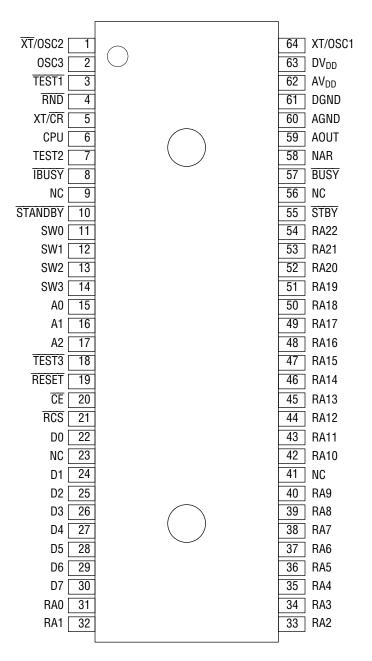

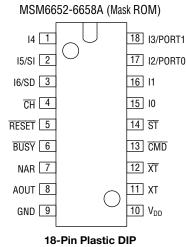

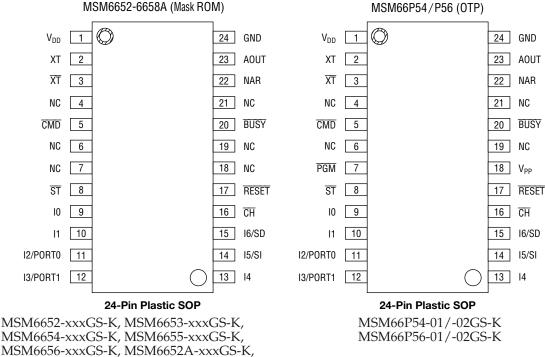

# PIN CONFIGURATION (TOP VIEW)

The MSM66P54-xx and MSM66P56-xx has two more pins than the MSM6652-6658A while their pin configurations are identical.

The additional two pins ( $V_{PP}$ ,  $\overline{PGM}$ ) of the MSM66P54-xx/P56-xx may be open at playback after completion of writing.

20-Pin Plastic DIP

GND

NC

18 V<sub>PP</sub>

24

23 AOUT 22 XT/CR

21 NC

20 BUSY

19

17 RESET

16 TEST

14 A1

13 A0

15 A2

MSM66P54-03/-04RS MSM66P56-03/-04RS

# MSM66P54/P56 (0TP)

MSM66P56-03/-04GS-K

MSM6652-xxxGS-K, MSM6653-xxxGS-K, MSM6654-xxxGS-K, MSM6655-xxxGS-K, MSM6656-xxxGS-K, MSM6652A-xxxGS-K, MSM6653A-xxxGS-K, MSM6654A-xxxGS-K, MSM6655A-xxxGS-K, MSM6656A-xxxGS-K,

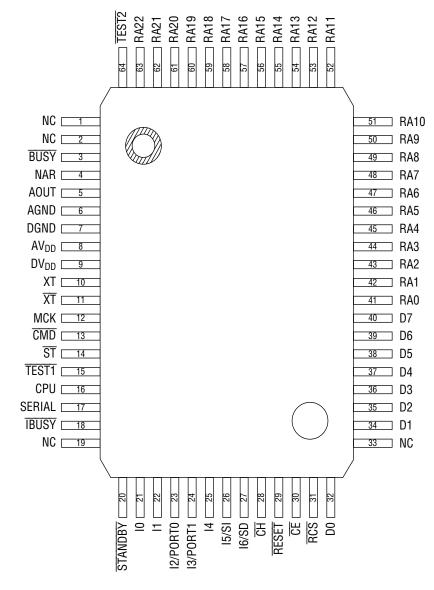

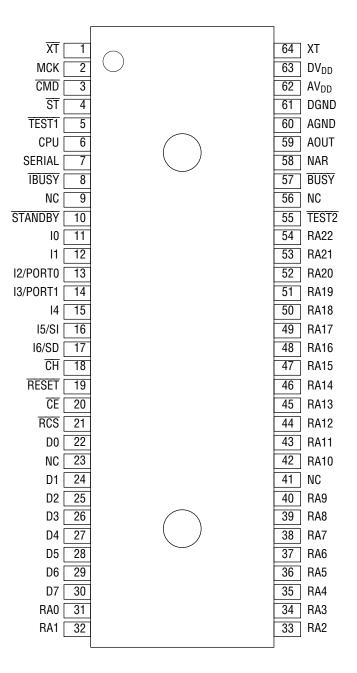

#### MSM6650

Product name: MSM6650GS-BK

NC : No connection

NC : No connection

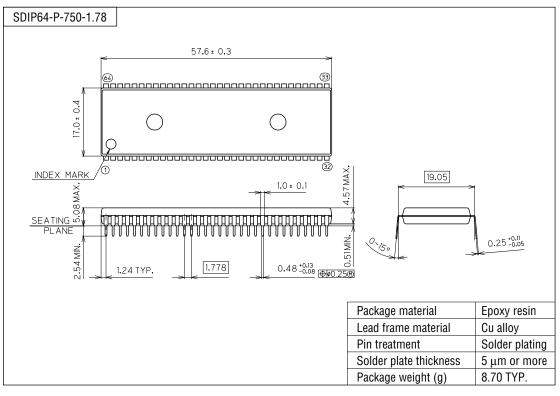

#### 64-Pin Plastic SDIP

# **PIN DESCRIPTIONS**

### 1. MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx 18-Pin plastic DIP

| Pin   | Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5     | RESET           | I    | <b>Reset.</b> Setting this pin to "L" puts the deveice in standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. The MSM6650 family devices have an internal power-on reset. To operate the power-on reset correctly, power should ramp up within 1 ms. If this is not possible, apply a RESET pulse when power is turned on. This pin has an internal pull-up resistor. |  |  |

| 6     | BUSY            | 0    | <b>Busy.</b> This pin outputs a "L" level during playback. At power-on, this pin is at "H" level.                                                                                                                                                                                                                                                                                                                         |  |  |

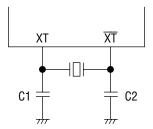

| 7     | XT/CR           | I    | <b>XT/CR</b> selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                                                                                                                                                                 |  |  |

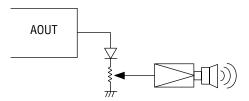

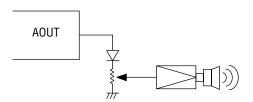

| 8     | AOUT            | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter.                                                                                                                                                                                                                                                                                                                                         |  |  |

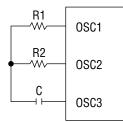

| 11    | OSC1            | I    | <b>Oscillator 1.</b> This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                                                                                                                                                           |  |  |

| 12    | OSC2            | 0    | <b>Oscillator 2.</b> This pin is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby stat                                                                                                                                                                             |  |  |

| 13    | OSC3            | 0    | <b>Oscillator 3.</b> Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level in standby status.                                                                                                                                                                                                                  |  |  |

| 14    | RND             | I    | <b>Random Playback.</b> Random playback starts when the $\overline{\text{RND}}$ pin is set to a "L" level. At the fall of $\overline{\text{RND}}$ , addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an internal pull-up resistor.                                                                                           |  |  |

| 15-18 | SW0-SW3         | I    | <b>Phrase Inputs.</b> These pins are phrase input pins corresponding to playback. If the input changes, SW0 to SW3 pins capture address data after 16 ms and speech playback commences. These pins have internal pull-down resistors.                                                                                                                                                                                     |  |  |

| 1-3   | A0-A2           | I    | <b>Phrase Inputs.</b> Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                                                                                                                                                                 |  |  |

| 9     | GND             | _    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 10    | V <sub>DD</sub> | _    | Power supply. Insert a $0.1\mu F$ or more bypass capacitor between this pin and GND.                                                                                                                                                                                                                                                                                                                                      |  |  |

| 4     | TEST            | Ι    | Test Mode. Set to "H" level. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 2.MSM66P54-xx, MSM66P56-xx |

|----------------------------|

| 20-Pin plastic DIP         |

| Pin   | Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6     | RESET           | I    | <b>Reset.</b> Setting this pin to "L" puts the deveice in standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. The MSM6650 family devices have an internal power-on reset. To operate the power-on reset correctly, power should ramp up within 1 ms. If this is not possible, apply a RESET pulse when power is turned on. This pin has an internal pull-up resistor. |

| 7     | BUSY            | 0    | Busy. This pin outputs a "L" level during playback. At power-on, this pin is at "H" level.                                                                                                                                                                                                                                                                                                                                |

| 8     | XT/CR           | I    | <b>XT/CR</b> selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                                                                                                                                                                 |

| 9     | AOUT            | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter                                                                                                                                                                                                                                                                                                                                          |

| 12    | OSC1            | I    | <b>Oscillator 1.</b> This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                                                                                                                                                           |

| 13    | OSC2            | 0    | <b>Oscillator 2.</b> This pin is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby status.                                                                                                                                                                          |

| 14    | OSC3            | 0    | <b>Oscillator 3.</b> Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level in standby status.                                                                                                                                                                                                                  |

| 15    | RND             | I    | <b>Random Playback.</b> Random playback starts when the $\overline{\text{RND}}$ pin is set to a "L" level. At the fall of $\overline{\text{RND}}$ , addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an internal pull-up resistor.                                                                                           |

| 16-19 | SW0-SW3         | I    | <b>Phrase Inputs.</b> These pins are phrase input pins corresponding to playback.<br>If the input changes, SW0 to SW3 pins capture address data after 16 ms and<br>speech playback commences. These pins have internal pull-down resistors.                                                                                                                                                                               |

| 2-4   | A0-A2           | I    | <b>Phrase Inputs.</b> Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                                                                                                                                                                 |

| 10    | GND             | _    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11    | V <sub>DD</sub> | _    | <b>Power supply.</b> Insert a $0.1\mu F$ or more bypass capacitor between this pin and GND                                                                                                                                                                                                                                                                                                                                |

| 5     | TEST            | Ι    | Test Mode. Set to "H" level. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                   |

| 1     | V <sub>PP</sub> |      | Power supply used when writing data to internal OTP ROM. Leave open or set to "H" level during playback.                                                                                                                                                                                                                                                                                                                  |

| 20    | PGM             | I    | Interface with voice analysis edit tool AR761 or AR762. Set to "L" level or leave open during playback.                                                                                                                                                                                                                                                                                                                   |

# 3.MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54-xx, MSM66P56-xx 24-Pin plastic SOP

| Pin   | Symbol            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 17    | RESET             | I    | <b>Reset.</b> Setting this pin to "L" puts the deveice in standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. The MSM6650 family devices have an internal power-on reset. To operate the power-on reset correctly, power should ramp up within 1 ms. If this is not possible, apply a RESET pulse when power is turned on. This pin has an internal pull-up resistor. |  |  |

| 20    | BUSY              | 0    | <b>Busy.</b> This pin outputs a "L" level during playback. At power-on, this pin is at "H" level.                                                                                                                                                                                                                                                                                                                         |  |  |

| 22    | XT/CR             | I    | <b>XT/CR</b> selectable pin. Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                                                                                                                                                                 |  |  |

| 23    | AOUT              | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter                                                                                                                                                                                                                                                                                                                                          |  |  |

| 2     | OSC1              | I    | <b>Oscillator 1.</b> This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                                                                                                                                                           |  |  |

| 3     | OSC2              | 0    | <b>Oscillator 2.</b> This pin is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby status.                                                                                                                                                                          |  |  |

| 5     | OSC3              | 0    | <b>Oscillator 3.</b> Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level in standby status.                                                                                                                                                                                                                  |  |  |

| 8     | RND               | I    | <b>Random Playback.</b> Random playback starts when the $\overline{\text{RND}}$ pin is set to a "L" level. At the fall of $\overline{\text{RND}}$ , addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an internal pull-up resistor.                                                                                           |  |  |

| 9-12  | SW0-SW3           | I    | <b>Phrase Inputs.</b> These pins are phrase input pins corresponding to playback.<br>If the input changes, SW0 to SW3 pins capture address data after 16 ms and<br>speech playback commences. These pins have internal pull-down resistors.                                                                                                                                                                               |  |  |

| 13-15 | A0-A2             | I    | <b>Phrase Inputs.</b> Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                                                                                                                                                                 |  |  |

| 24    | GND               | _    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1     | V <sub>DD</sub>   |      | <b>Power supply.</b> Insert a $0.1\mu F$ or more bypass capacitor between this pin and GM                                                                                                                                                                                                                                                                                                                                 |  |  |

| 16    | TEST              | I    | Test Mode. Set to "H" level. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 18    | V <sub>PP</sub> * |      | Power supply used when writing data to internal OTP ROM. Leave open or set to "H" level during playback.                                                                                                                                                                                                                                                                                                                  |  |  |

| 7     | PGM*              | Ι    | Interface with voice analysis edit tool AR761 or AR762. Set to "L" level or leave open during playback.                                                                                                                                                                                                                                                                                                                   |  |  |

\* Pins for MSM66P54/56-xx only

# 4.MSM6650

64-Pin plastic QFP (64-Pin plastic SDIP)

| Pin              | Symbol  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29(19)           | RESET   | I    | <b>Reset.</b> Setting this pin to "L" puts the deveice in standby status. At this time, oscillation stops, AOUT is pulled to GND, and the deveice is initialized. The MSM6650 family devices have an internal power-on reset. To operate the power-on reset correctly, power should ramp up within 1 ms. If this is not possible, apply a RESET pulse when power is turned on. This pin has an internal pull-up resistor. |

| 3(57)            | BUSY    | 0    | <b>Busy.</b> This pin outputs a "L" level during playback. At power-on, this pin is at "H" level.                                                                                                                                                                                                                                                                                                                         |

| 15(5)            | XT/CR   | I    | <b>XT/CR selectable pin.</b> Set to "H" level when using ceramic oscillation. Set to "L" level when using RC oscillation.                                                                                                                                                                                                                                                                                                 |

| 5 (59)           | AOUT    | 0    | Sound Output. This is the synthesized output pin of the internal low-pass filter                                                                                                                                                                                                                                                                                                                                          |

| 10(64)           | XT/OSC1 | I    | <b>Oscillator 1.</b> This pin is a ceramic oscillator connection pin when using ceramic oscillation. This pin is an RC connection pin when using RC oscillation. When using an external clock, use this pin as the clock input.                                                                                                                                                                                           |

| 11(1)            | XT/0SC2 | 0    | <b>Oscillator 2.</b> This pin is a ceramic oscillator connection pin when using a ceramic oscillator. This is an RC connection pin when using RC oscillation. Leave open if using an external clock. OSC2 outputs a "L" level in standby status.                                                                                                                                                                          |

| 12(2)            | OSC3    | 0    | <b>Oscillator 3.</b> Leave open if using a ceramic oscillator. This pin is the RC connection pin when using RC oscillation. When RC oscillation is selected, OSC3 outputs a "H" level in standby status.                                                                                                                                                                                                                  |

| 14(4)            | RND     | I    | <b>Random Playback.</b> Random playback starts when the $\overline{\text{RND}}$ pin is set to a "L" level. At the fall of $\overline{\text{RND}}$ , addresses from the random address playback circuit inside the IC are fetched. Set to a "H" level if random playback is not used. This pin has an internal pull-up resistor.                                                                                           |

| 21-24<br>(11-14) | SW0-SW3 | I    | <b>Phrase Inputs.</b> These pins are phrase input pins corresponding to playback.<br>If the input changes, SW0 to SW3 pins capture address data after 16 ms and<br>speech playback commences. These pins have internal pull-down resistors.                                                                                                                                                                               |

| 25-27<br>(15-17) | A0-A2   | I    | <b>Phrase Inputs.</b> Phrase input pins correspoding to playback. The A0 input becomes invalid when the random playback function is used.                                                                                                                                                                                                                                                                                 |

| Pin                      | Symbol           | Туре | Description                                                                                                                                                                                                                                                                                 |  |

|--------------------------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

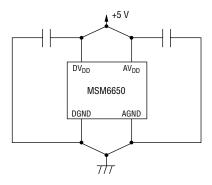

| 6 (60)                   | AGND             | _    | Analog ground pin.                                                                                                                                                                                                                                                                          |  |

| 7 (61)                   | DGND             | _    | Digital ground pin.                                                                                                                                                                                                                                                                         |  |

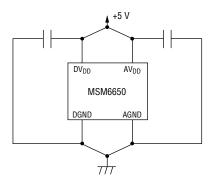

| 8 (62)                   | AV <sub>DD</sub> | _    | Analog power pin. Insert a 0.1 $\mu$ F or more bypass capacitor in between this pin and AGND                                                                                                                                                                                                |  |

| 9 (63)                   | DV <sub>DD</sub> | _    | Digiral power pin. Insert a 0.1 $\mu$ F or more bypass capacitor in between this pin and DGND                                                                                                                                                                                               |  |

| 16 (6)                   | CPU              | I    | <b>CPU Mode.</b> Set to "L" level to select Standalone Mode. Set to "H" level to select Microcontroller Interface Mode.                                                                                                                                                                     |  |

| 13, 28 (3, 18)           | TEST1, 3         | I    | <b>Test.</b> Set these pins to "H" level. The TEST1 and TEST3 pins have internal pull-up resistor.                                                                                                                                                                                          |  |

| 17 (7)                   | TEST2            | Ι    | Test. Set this pin to "L" level.                                                                                                                                                                                                                                                            |  |

| 18 (8)                   | IBUSY            | 0    | <b>I Busy.</b> Outputs a "L" level during voice playback (except during standby conversion time), or when the AOUT pin is at half V <sub>DD</sub> level.                                                                                                                                    |  |

| 20 (10)                  | STANDBY          | 0    | Standby Indicator. This output pin remains at "L" level during oscillation.                                                                                                                                                                                                                 |  |

| 30 (20)                  | CE               | 0    | <b>Chip Enable.</b> $\overline{CE}$ is a timing output pin to control read of external memory.<br>This pin outputs when $\overline{RCS}$ is at the "L" level. This pin goes high impedance when $\overline{RCS}$ is at the "H" level.                                                       |  |

| 31 (21)                  | RCS              | I    | <b>Read Chip Select.</b> The data bits D0-D7 are internally pulled down when $\overline{\text{RCS}}$ is high. Addresses and $\overline{\text{CE}}$ are output when $\overline{\text{RCS}}$ is at "L" level. The RA22-RA0 address pins and $\overline{\text{CE}}$ pin become high impedance. |  |

| 32, 34-40<br>(22, 24-30) | D0-D7            | I    | <b>External Memory Data Bus.</b> Data is input when $\overline{\text{RCS}}$ is low. When $\overline{\text{RCS}}$ is high, these pins become low due to internal pull-down resistors.                                                                                                        |  |

| 41-63<br>(31-40, 42-54)  | RA0-RA22         | 0    | External Memory Address. These are address pins for an external memor<br>output when RCS is low. These pins become high impedance status if RCS is i<br>'H" level.                                                                                                                          |  |

| 64 (55)                  | STBY             | I    | <b>Standby Contorl.</b> If set to "L" level, the MSM6650 enters standby mode 0.2 seconds after voice ends. If set to "H" level, the MSM6650 AOUT output maintains half $V_{DD}$ after voice ends.                                                                                           |  |

# **ABSOLUTE MAXIMUM RATINGS**

|                      |                  |           |                              | (GND=0 V) |

|----------------------|------------------|-----------|------------------------------|-----------|

| Parameter            | Symbol           | Condition | Rating                       | Unit      |

| Power supply voltage | V <sub>DD</sub>  | Ta = 25°C | -0.3 to +7.0                 | V         |

| Input voltage        | V <sub>IN</sub>  | 14 - 20 0 | -0.3 to V <sub>DD</sub> +0.3 | V         |

| Storage temperature  | T <sub>STG</sub> |           | -55 to +150                  | °C        |

# **RECOMMENDED OPERATING CONDITIONS**

|                          |                   |                        |      |            |      | (GND=0 V) |

|--------------------------|-------------------|------------------------|------|------------|------|-----------|

| Parameter                | Symbol            | Condition              |      | Range      |      | Unit      |

|                          |                   | MSM6652-56, MSM6650,   |      | 0 4 to 5 5 |      | V         |

| Power supply voltage     | V <sub>DD</sub>   | MSM6652A-56A           |      | 2.4 to 5.5 |      | V         |

|                          | V <sub>DD</sub>   | MSM6658A, MSM66P54/P56 |      | 3.5 to 5.5 |      | V         |

| Operating temperature    | T <sub>op</sub>   | _                      |      | -40 to +85 | 5    | °C        |

| Master clock frequency 1 |                   | When crystal selected  | Min. | Тур.       | Max. | MHz       |

| Master Clock Hequency I  | tosc1             | WHEN CLYSLAL SELECLEU  | 3.5  | 4.096      | 4.5  |           |

| Master clock frequency 2 | f <sub>OSC2</sub> | When RC selected (*)   | 200  | 256        | 300  | kHz       |

\* If RC oscillation is selected, 32kHz sampling frequency cannot be selected.

# **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

|                             |                  | (V                               | <sub>DD</sub> =5.0 V, ( | GND=0 V, | Ta=–40 to | +85°C) |

|-----------------------------|------------------|----------------------------------|-------------------------|----------|-----------|--------|

| Parameter                   | Symbol           | Condition                        | Min.                    | Тур.     | Max.      | Unit   |

| "H" input voltage           | VIH              | —                                | 4.2                     | _        | —         | V      |

| "L" input voltage           | V <sub>IL</sub>  | —                                | _                       | _        | 0.8       | V      |

| "H" output voltage          | V <sub>OH</sub>  | I <sub>0H</sub> =–1 mA           | 4.6                     | _        | —         | V      |

| "L" output voltage          | V <sub>OL</sub>  | I <sub>OL</sub> =2 mA            | —                       | —        | 0.4       | V      |

| "H" input current 1         | I <sub>IH1</sub> | V <sub>IH</sub> =V <sub>DD</sub> | —                       | —        | 10        | μA     |

| "H" input current 2         | I <sub>IH2</sub> | Internal pull-down resistance    | 30                      | 90       | 200       | μA     |

| "L" input current 1         | I <sub>IL1</sub> | V <sub>IL</sub> =GND             | -10                     | —        | —         | μA     |

| "L" input current 2 (note)  | I <sub>IL2</sub> | Internal pull-up resistance      | -200                    | -90      | -30       | μA     |

| Operating power consumption | I <sub>DD</sub>  | —                                | —                       | 6        | 10        | mA     |

| Standby power consumption   | 1.               | Ta=-40°C to +50°C                | —                       | —        | 10        | μA     |

|                             | IDS              | Ta=50°C to 85°C                  | —                       |          | 30        | μΑ     |

# **Analog Characteristics**

(V<sub>DD</sub>=5.0 V, GND=0 V, Ta=-40 to +85°C)

| Parameter                    | Symbol            | Condition                        | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------|----------------------------------|------|------|------|------|

| D/A output relative accuracy | V <sub>DAE</sub>  | When D/A output is selected      | —    | —    | 40   | mV   |

| D/A output impedance         | R <sub>DAO</sub>  | When D/A output is selected      | 15   | 25   | 35   | kΩ   |

| LPF driving resistance       | R <sub>AOUT</sub> | When LPF output is selected      | 50   | —    | —    | kΩ   |

| LPF output impedance         | R <sub>LPF</sub>  | I <sub>F</sub> =100 μA           |      | 1    | 3    | kΩ   |

| Harmonic wave distortion     | d <sub>H</sub>    | 2.0V <sub>PP</sub> sine wave     |      | 2.0  | 4.0  | %    |

|                              |                   | at 1kHz input waveform, fs=8kHz, |      |      |      |      |

|                              |                   | Harmonic wave distortion=        |      |      |      |      |

|                              |                   | 2nd-21st harmonic wave component |      |      |      |      |

|                              |                   | Signal component+2nd-21st        |      |      |      |      |

|                              |                   | harmonic wave component          |      |      |      |      |

| Noise during silence         | n <sub>s</sub>    | No load, input waveform mute     |      | 5    | 20   | mV   |

#### **DC Characteristics**

|                              |                  | (V                               | <sub>DD</sub> =3.1 V, ( | GND=0 V, | Ta=–40 to | +85°C) |

|------------------------------|------------------|----------------------------------|-------------------------|----------|-----------|--------|

| Parameter                    | Symbol           | Condition                        | Min.                    | Тур.     | Max.      | Unit   |

| "H" input voltage            | V <sub>IH</sub>  | —                                | 2.7                     | —        | _         | V      |

| "L" input voltage            | VIL              | —                                | —                       | —        | 0.5       | V      |

| "H" output voltage           | V <sub>OH</sub>  | I <sub>0H</sub> =–1 mA           | 2.6                     | —        | —         | V      |

| "L" output voltage           | V <sub>OL</sub>  | I <sub>OL</sub> =2 mA            | —                       | —        | 0.4       | V      |

| "H" input current 1          | I <sub>IH1</sub> | V <sub>IH</sub> =V <sub>DD</sub> | —                       | —        | 10        | μA     |

| "H" input current 2          | I <sub>IH2</sub> | Internal pull-down resistance    | 10                      | 30       | 100       | μA     |

| "L" input current 1          | I <sub>IL1</sub> | V <sub>IL</sub> =GND             | -10                     | —        | _         | μA     |

| "L" input current 2          | I <sub>IL2</sub> | Internal pull-up resistance      | -100                    | -30      | -10       | μA     |

| Operating power consumiption | I <sub>DD</sub>  | —                                | —                       | 4        | 7         | mA     |

| Standby power consumption    |                  | Ta=-40°C to +50°C                | —                       | —        | 5         | μA     |

|                              | IDS              | Ta=50°C to 85°C                  | —                       | —        | 20        | μA     |

| LPF driving resistance       | RAOUT            | When LPF output is selected      | 50                      |          | _         | kΩ     |

| LPF output impedance         | R <sub>LPF</sub> | I <sub>F</sub> =100 μA           | _                       | 1        | 3         | kΩ     |

#### **AC Characteristics**

#### (V<sub>DD</sub>=2.4 to 5.5 V, GND=0 V, Ta=-40 to +85°C) (V<sub>DD</sub>=3.5 to 5.5 V, GND=0 V, Ta=-40 to +85°C) (Note)

| Parameter                              | Symbol                           | Condition                      | Min. | Тур. | Max. | Unit |

|----------------------------------------|----------------------------------|--------------------------------|------|------|------|------|

| Master clock duty cycle                | f <sub>duty</sub>                |                                | 40   | 50   | 60   | %    |

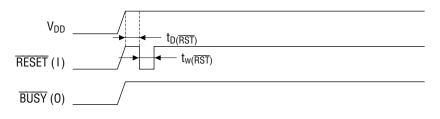

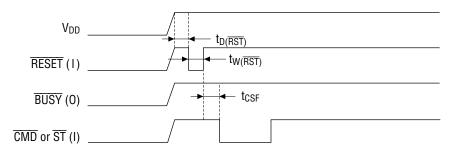

| <b>RESET</b> input pulse width         | tw(RST)                          | —                              | 10   |      |      | μs   |

| <b>RESET</b> input time after power-on | t <sub>D(RST)</sub>              | —                              | 0    |      |      | μs   |

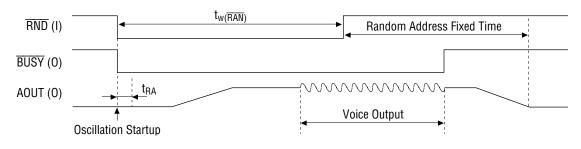

| RND input pulse width                  | tw(RAN)                          | See Functional Description 5.2 | 100  |      |      | μs   |

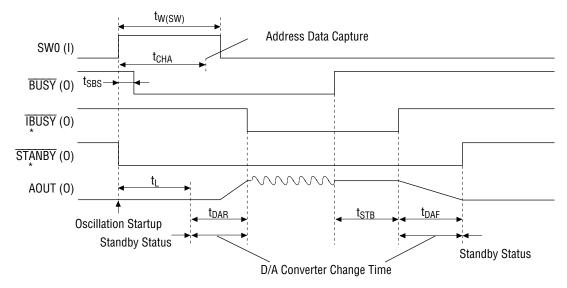

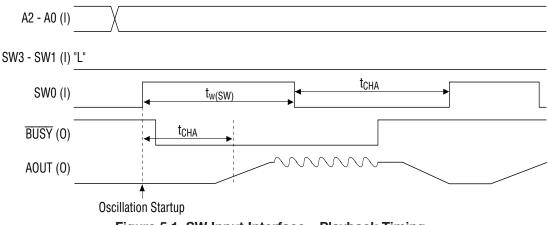

| SW0-SW3 input pulse width              | t <sub>w(SW)</sub>               | —                              | 16   |      |      | ms   |

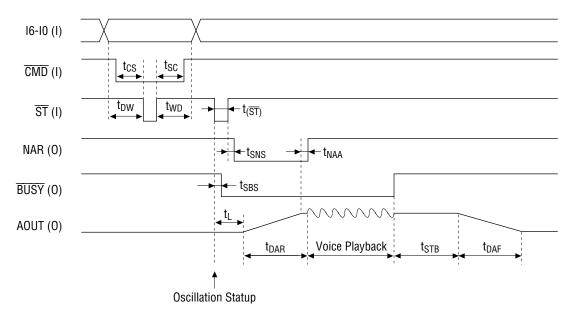

| BUSY output time 1                     | t <sub>SBS</sub>                 | —                              |      |      | 10   | μs   |

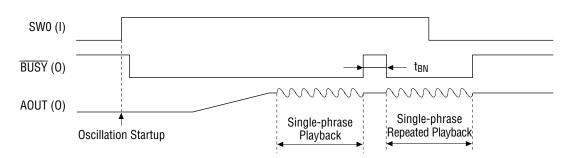

| BUSY output time 2                     | t <sub>BN</sub>                  | At f <sub>SAM</sub> =8 kHz     | 130  | 150  | 170  | μs   |

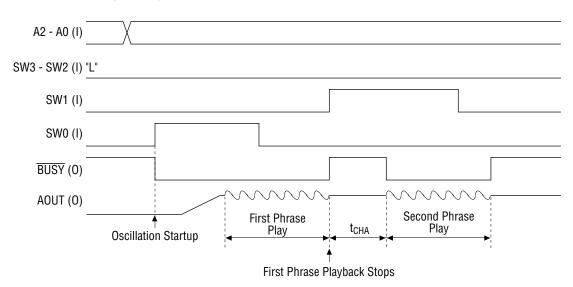

| Chattering prevention time             | t <sub>CHA</sub>                 | —                              | 14   | 15   | 16   | ms   |

| D/A converter change time              | $t_{\text{DAR}}, t_{\text{DAF}}$ | —                              | 60   | 64   | 68   | ms   |

| LPF stable time                        | tL                               | —                              | 6    | 8    | 10   | ms   |

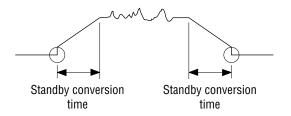

| Standby transition time                | t <sub>STB</sub>                 | _                              | 0.15 | 0.2  | 0.25 | sec  |

| Random address capture time            | t <sub>RA</sub>                  | See Functional Description 5.2 | 16   | 32   | 48   | μs   |

Note: Applied to MSM6658A-xxx and MSM66P54-xx, MSM66P56-xx.

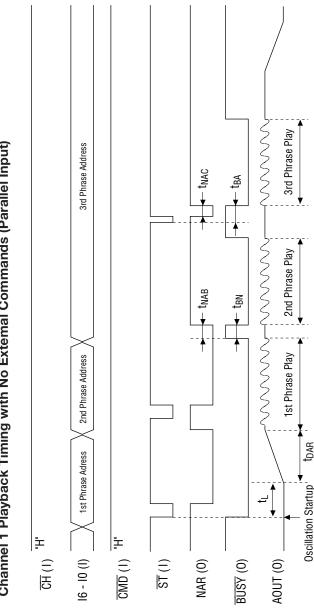

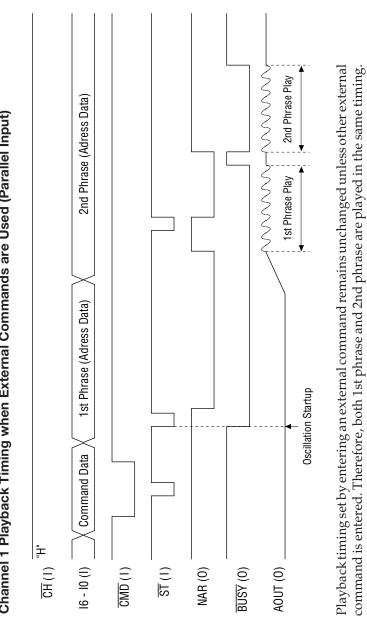

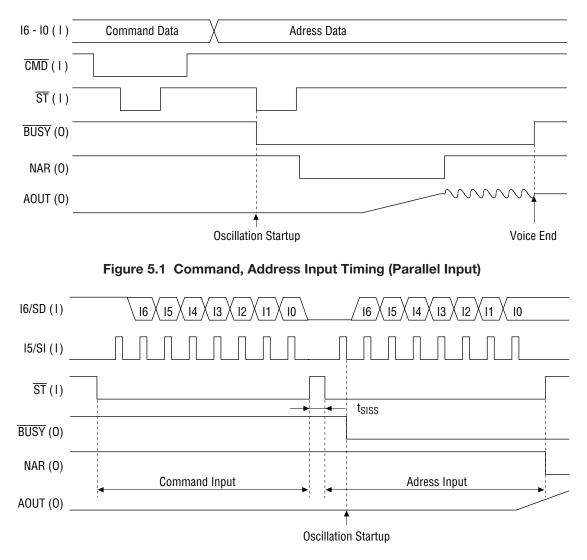

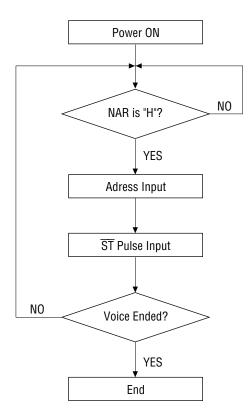

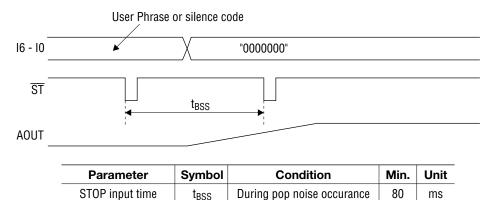

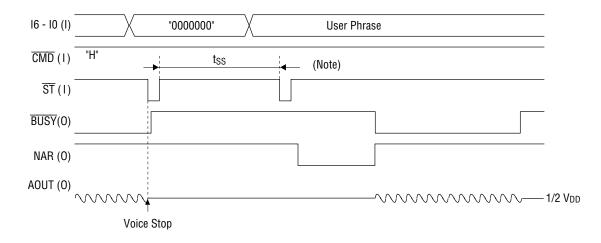

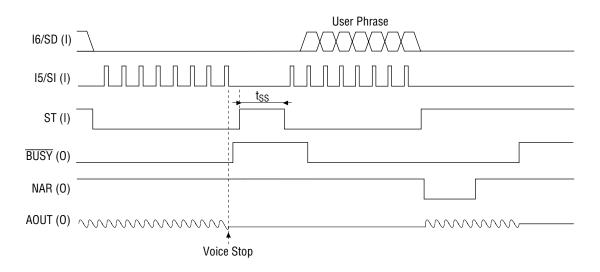

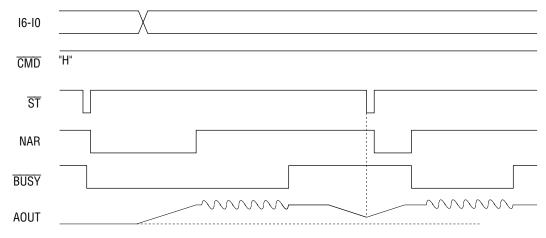

# TIMING DIAGRAMS

#### **Power-On Timing**

### Activation of Standby State Timing when IC is activated

\* IBUSY, STANDBY timings are applied to MSM6650 alone.

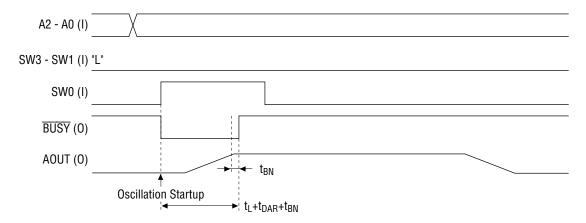

# **Repeated Playback Timing**

### Playback Timing during Transition of SW0-SW3

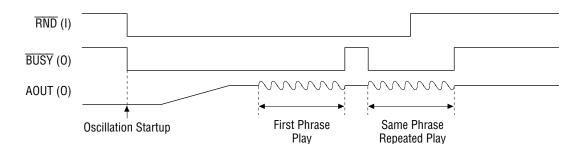

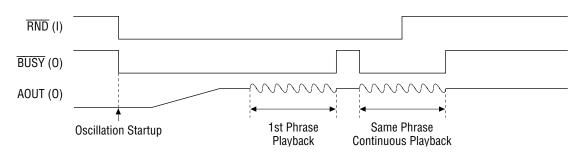

#### **Repeated Random Playback Timing**

# **Random Address Capture Timing**

# FUNCTIONAL DESCRIPTION

### **1. PLAYBACK CODE SPECIFICATION**

The user can specify a maximum of 120 phrases. Table 1.1 shows the settings by A2-A0 and SW3-SW0.

| A2-A0           | SW3-SW0 | Code Description       |

|-----------------|---------|------------------------|

| 000             | 0000    | Inhibit code           |

| 000<br>:<br>111 | 0001    | User Specified Phrases |

| 111             | 1111    | (120 phrases)          |

#### Table 1.1 User Specified Phrase List

#### 2. INTERNAL ROM USAGE AND DISABLED AREA (MSM6652/53/54/55/56-xxx, MSM6652A/53A/54A/55A/56A/58A-xxx, MSM66P54/P56-xx)

The last 3 bytes of the internal ROM are not to be used as shown in Table 2.1. Please do not use these 3 bytes when creating the sound ROM.

Table 2.1 shows the addresses that are not to be used for each model.

| Туре           | Voice Data Area | Disabled Area       |

|----------------|-----------------|---------------------|

| MSM6652, 6652A | 00B00-08FFC     | 08FFD, 08FFE, 08FFF |

| MSM6653, 6653A | 00B00-10FFC     | 10FFD, 10FFE, 10FFF |

| MSM6654, 6654A | 00B00-1FFFC     | 1FFFD, 1FFFE, 1FFFF |

| MSM6655, 6655A | 00B00-2FFFC     | 2FFFD, 2FFFE, 2FFFF |

| MSM6656, 6656A | 00B00-3FFFC     | 3FFFD, 3FFFE, 3FFFF |

| MSM6658A       | 00B00-7FFFC     | 7FFFD, 7FFFE, 7FFFF |

| MSM66P54       | 00B00-1FFFC     | 1FFFD, 1FFFE, 1FFFF |

| MSM66P56       | 00B00-3FFFC     | 3FFFD, 3FFFE, 3FFFF |

Note: Addresses are in hex.

#### 3. PULL-UP/PULL-DOWN RESISTOR

The RESET, RND and TEST pins have internal pull-up resistors and the SW3-SW0 pins have internal pull-down resistors.

|                                                     | Pins with pull-up | Pins with pull-down |

|-----------------------------------------------------|-------------------|---------------------|

| MSM6652/53/54/55/56<br>MSM6652A/53A/54A/55A/56A/58A | RESET, RND, TEST  | SW3-SW0             |

| MSM66P54/P56                                        | RESET, RND, TEST  | SW3-SW0             |

| MCM6650                                             | DECET DND TECTI 2 | C/N/2 C/N/0         |

#### Table 3.1 Pins with Pull-up/Pull-down Resistor

# 4. OPTION(S)

In standalone mode the  $XT/\overline{CR}$  pin can be used to select the oscillation circuit. If this pin is set to "H" level, the circuit is in ceramic oscillation, conversely, if set to "L" level, the circuit is in RC oscillation.

In the case of RC oscillation, however, a 32 kHz sampling frequency cannot be used. An option to move to standby mode can be selected when rewriting ROM data.

# 5. STANDALONE MODE

In standalone mode, the SW input interface function and the random playback function can be used.

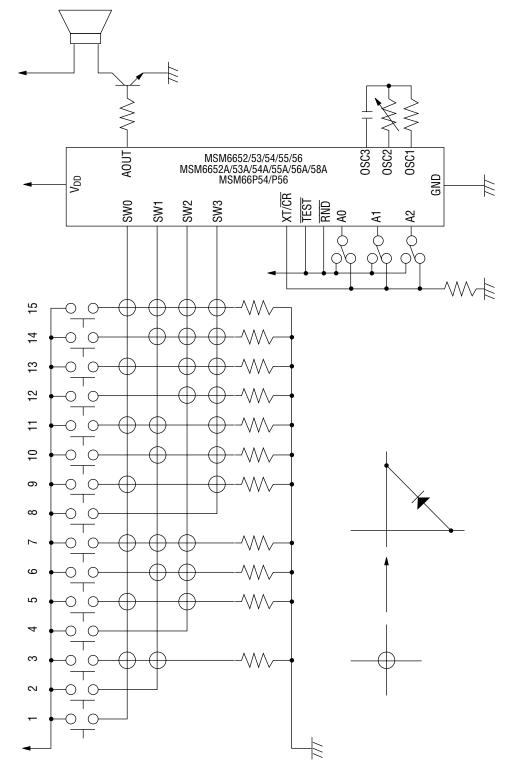

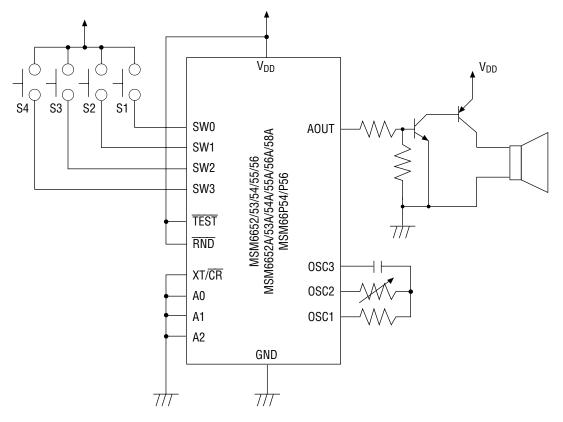

# 5.1 SW Input Interface

With the SW input interface, voice synthesis starts when SW3-SW0 pins have changed. To prevent chattering, the address is captured 16 ms ( $t_{CHA}$ ) after SW3-SW0 pins have changed. Voice synthesis does not start if A2-A0 pins have changed.

Set the RND pin to "H" level if the random playback function is not used.

At power on, SW3-SW0 pins are all "L" level.

The SW input interface is effective when operating the MSM665X using a push-button switch. Speech synthesis starts when an address is changed by pressing the push-button switch. If the push-button switch is released during playback, then playback stops after the current phrase is completed.

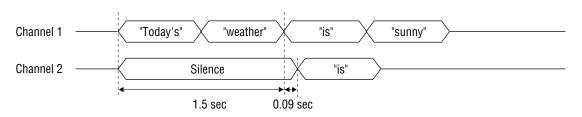

Figure 5.1 SW Input Interface – Playback Timing

Figure 5.1 shows playback timing.

SW3-SW0 pins have chattering prevention circuits.

The pulse period at each pin requires 16ms ( $T_{CHA}$ ) or more.

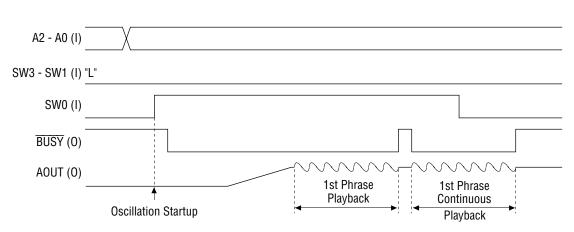

If a push-button switch is continuously pushed, the same phrase is played repeatedly. Figure 5.2 shows repeated playback timing. Figure 5.3 shows timing when A2-A0 are changed during playback.

MSM6650 Family

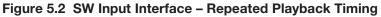

Figure 5.3 SW Input Interface Playback Timing

If SW3-SW0 pins change during playback, then playback stops and the next phrase is played. For the next phrase playback, the voice is first stopped and playback occurs after 16 ms of chattering prevention.

Figure 5.4 shows timing when SW3-SW0 are changed during playback.

MSM6650 Family

### Figure 5.4 Timing when SW3-SW0 are Changed during Playback

If playback is attempted at an unused address in the phrase ROM, then AOUT goes to  $1/2\,V_{DD}$  and playback does not occur. Figure 5.5 shows the timing.

#### Figure 5.5 Timing when Playback is Attempted at an Unused Phrase Address

In the SW interface, addresses (against SW3-SW0) that do not start up voice playback exist without fail. When power is turned ON or when input to RESET, the addresses set from SW3 to SW0 become the addresses that do not start up voice playback. Therefore, when the circuit consists of diode matrixes that use push-button switches, the maximum playback phrases become 120 phrases.

Combinations of A2-A0 are eight kinds. When addresses of SW3-SW0 that do not start up voice playback are 0000;  $2^7 - 8 = 120$  (phrases)

### 5.2 Random Playback Function

The random playback function generates 31 random addresses correspoding to the 5 bits of the addresses of A0, and SW3-SW0 (except ALL "L") on the IC, after which playback commences.

This means there is no external input to the A0, SW3-SW0 pins. Since the A0 pin has no internal pull-up/pull-down resistor, permanently set to "L" or "H".

Playback will not occur if none of the 31 addresses have been assigned a phrase. Caution is advised when creating ROM data.

For example, when four phrases, "sunny", "rainy", "cloudy", and "snowy" are to be played, set the phrases as shown in Table 5.1 to 31 random addresses. The four phrases are then played at random as shown below.

| A2, A1 | A0, SW3-SW0 | Phrase |

|--------|-------------|--------|

| 00     | 00001       | Sunny  |

|        | 00010       | Rainy  |

|        | 00011       | Cloudy |

|        | 00100       | Snowy  |

|        | 00101       | Sunny  |

|        | i           | :      |

|        | 11110       | Rainy  |

|        | 11111       | Snowy  |

# Table 5.1 Random Address Setup Example

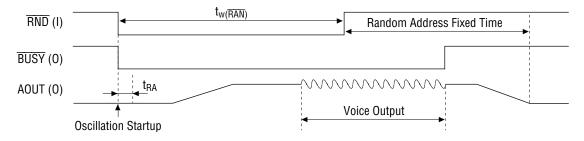

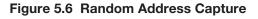

Random playback occurs in accordance with the timing shown in Figure 5.6. The random address is captured at the fall of the  $\overline{\text{RND}}$  pin, and voice playback commences. When power is turned ON, or when  $\overline{\text{RESET}}$  is input, the phrase at address "00001" is played while a random counter remains initialized until random playback is initiated.

| A2, A1 | A0, SW3-SW0 * | Code Description        |  |

|--------|---------------|-------------------------|--|

| 00     | 00001         | Random Playback Address |  |

|        | 11111         | (31 Types)              |  |

| 01     |               |                         |  |

| 10     | Same as above | Same as above           |  |

| 11     |               |                         |  |

| Table 5.2 | Addresses fo  | r Random | Play  |

|-----------|---------------|----------|-------|

|           | Augu 03303 10 | 1 manaom | I IGY |

\* Address(es) corresponding to A0, SW3-SW0 pins.

For a random address, 31 phrases can be set for each LOGICAL condition of addresses A2 and A1 (i.e., "00", "01", "10", and "11").

In random playback, note that the four logic states (00, 01, 10, 11) in user specified phrases cannot be used when the phrase ROM data is prepared.

A random address is set by the "H" level time of the RND pin, so if the same pulse width is input by microcontroller, the random address fixed time becomes constant, and a "random" phrase may not be played under these conditions. The random address fixed time must be inconsistent in order to produce random playback.

Figure 5.7 Timing when a Pulse is Input to the RND Pin during Random Play

Figure 5.8 Repeat Playback Timing of Random Play

As shown in Figure 5.7, if a pulse is input to the  $\overline{\text{RND}}$  pin during voice playback ( $\overline{\text{BUSY}}$  is "L" level), that pulse becomes invalid. If the  $\overline{\text{RND}}$  pin remains "L" level after phrase playback has been completed, then the same phrase is repeated, as shown in Figure 5.8.

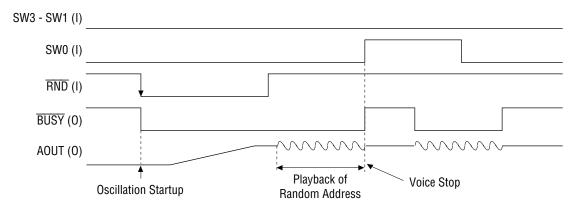

If SW3-SW0 are changed during random playback, voice playback stops, and voice data that corresponds to SW3-SW0 is played.

Figure 5.9 shows the timing when SW3-SW0 are changed during random play.

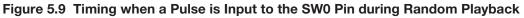

Table 5.3 and Figure 5.10 show the address settings that stop random playback. These settings also stop playback when the "infinite repeat" command is used during edit ROM playback.

| A2, A1 | A0, SW3-SW0 *       | Code Description                  |

|--------|---------------------|-----------------------------------|

| 00     | 00001<br>÷<br>11111 | Random Play Address<br>(31 Types) |

| 01     | 00001               | Stop Address                      |

#### Table 5.3 Random Play and Stop Addresses

\* Addresses corresponding to A0, SW3-SW0 pins.

Figure 5.10 Circuit Example for Random Play Stop

#### 6. SAMPLING FREQUENCY

Sampling frequencies can be specified for each phrase in the voice data of the internal ROM. For channel synthesis, if channels 1 and 2 are played simultaneously, the channel 1 sampling frequency has priority.

When channel 2 is played, only the sampling frequency for the first phrase is valid.

The following eight frequencies can be selected when creating voice data.

4.0 kHz, 5.3 kHz, 6.4 kHz, 8.0 kHz, 10.6 kHz, 12.8 kHz, 16.0 kHz, 32.0 kHz

In standalone, RC oscillation or ceramic oscillation can be selected. If RC oscillation is selected however, 32.0 kHz sampling cannot be selected.

# 7. VOICE PLAYBACK TIME

Table 7.1 shows internal ROM configuration. The actual voice data ROM area is different from the indicated ROM capacity.

The voice data management area shown in Table 7.1 is about 6 Kbits, and the edit ROM area includes 16 Kbits.

| Voice Data Management Area |

|----------------------------|

| Edit ROM Area              |

| Voice Data Area            |

| Disabled Area              |

Use the following formula as a guide to compute voice playback time.

Playback Time = (ROM Capacity -16 - 6)  $\times 1024 \times 255/256 \Pi$ Data Rate (kbps)

For example, if data was created at a  $4.0\,\rm kHz$  sampling rate using the MSM6652 (288-Kbit ROM), the playback time is

$(288 - 16 - 6) \times 1024 \times 255/256 \prod 16 \text{ (kbps)} = 16.9 \text{ (sec.)}$

# 8. CHANNEL STATUS

The BUSY pin outputs the status signals. It outputs "L" level when either channel 1 or 2 is playing voice. "H" level is output when power is turned on.

# 9. PLAYBACK METHOD

The MSM6375 family uses the ADPCM playback method, however the MSM6650 family has three playback methods: ADPCM, PCM and melody playback. The respective features and selection criteria are explained below.

# 9.1 ADPCM Method

With the ADPCM (adaptive differential pulse-code modulation) method, basic quantization width  $\Delta$  is adaptively changed for each sampling, and is encoded to 4-bit data each time. This further improves the follow-up properties to speech wave forms.

Conversion to ADPCM data is performed by the development tool AR761 or AR762.

ADPCM is a compression algorithm which provides the best compromise between quality (bandwidth) and memory usage (data rate). ADPCM can be used for accurate reproduction of voice, music, and sound effects.

#### 9.2 PCM Method

The PCM method of the MSM6650 family uses an 8-bit straight binary format. Of the three methods, PCM is best suited to accurate reproduction of sound effects or waveforms which are pulse shaped or change rapidly (such as high frequency pure tone sine-waves).

### 9.3 Melody Playback Method

The AR761 and AR762 development tools support melody regeneration system. The melody data can be composed by using these tools. Therefore, unique sound can be created.

### 9.4 Data Rate of Each Method

The data rate shows the degree of data compression and the data amount to synthesize for 1 second. The data rate is determined by the relationship between the sampling frequency and the format (number of bits per sample). The following formula is used.

Data rate (kbps) = Sampling frequency (kHz) × Number of bits per sample

The data rate of the three methods are compared below when the sampling frequency is 6.4 kHz.

- 1) ADPCM Method Data Rate (kbps) = 6.4 (kHz)  $\times 4$  (bit) = 25.6 (kbps)

- 2) PCM Method Data Rate (kbps) = 6.4 (kHz)  $\times 8$  (bit) = 51.2 (kbps)

The data rate of the melody playback method is calculated as follows:

Data rate = number of notes per second × data amount per note [kbits]

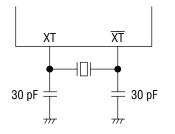

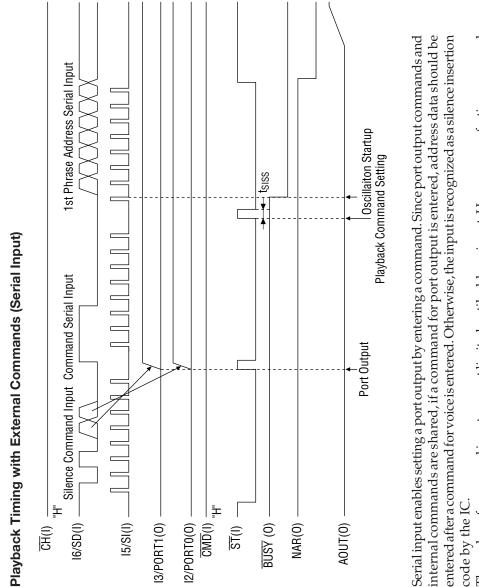

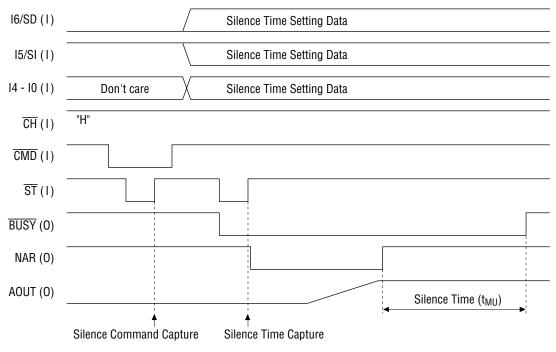

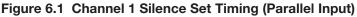

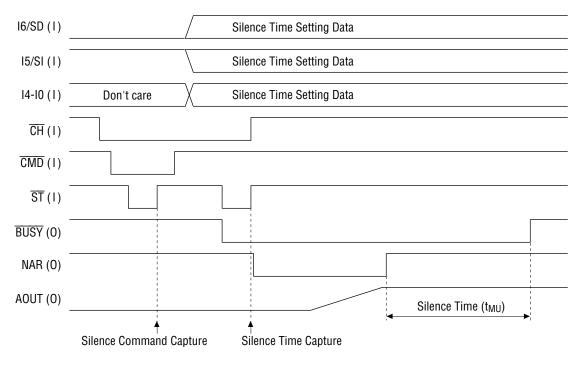

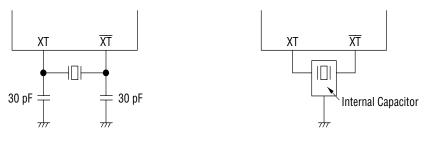

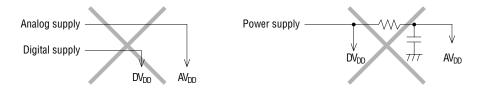

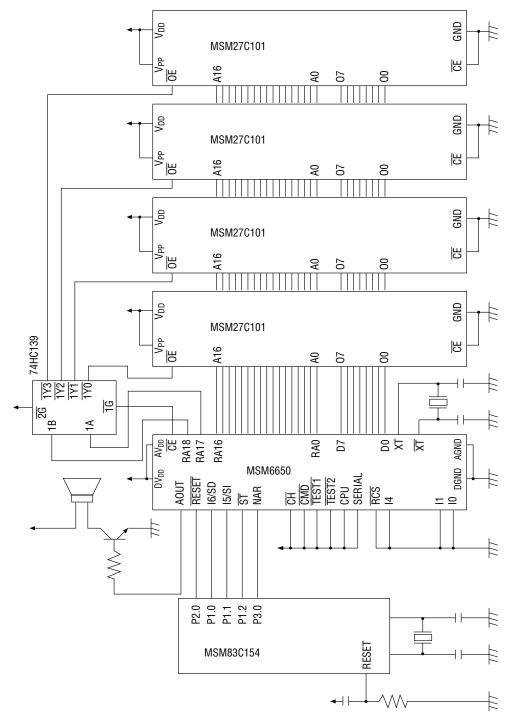

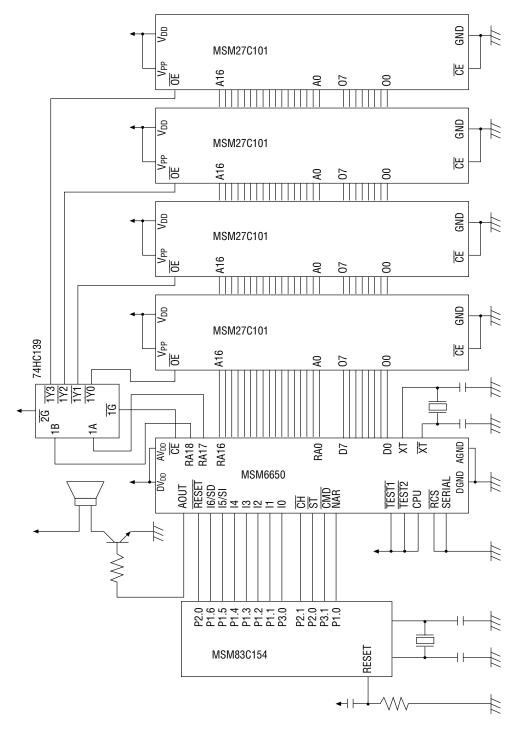

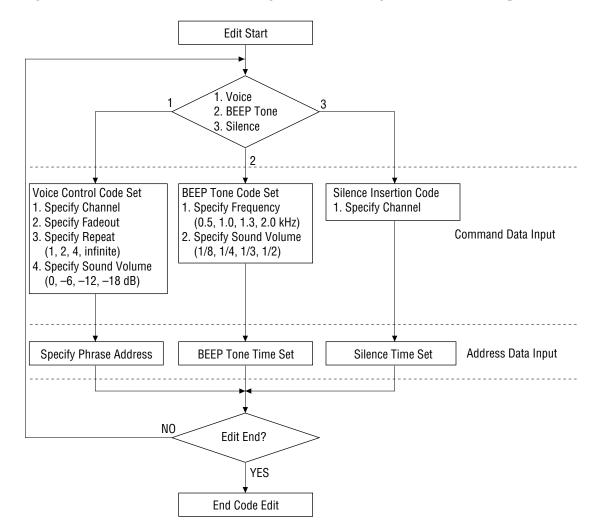

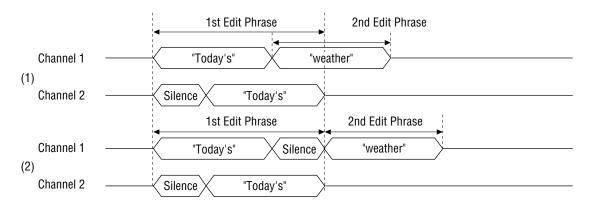

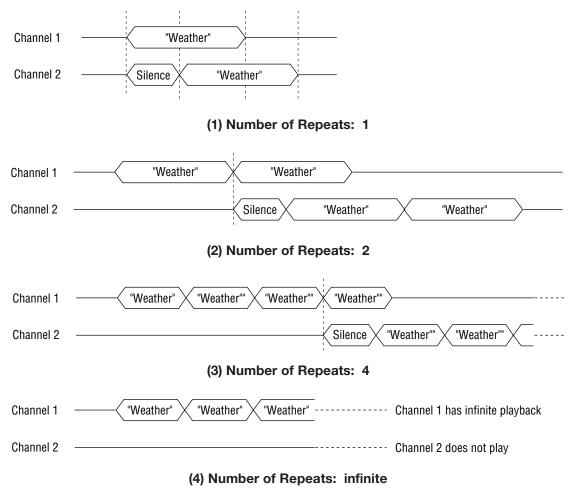

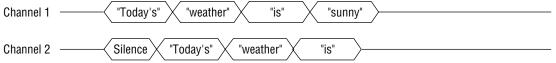

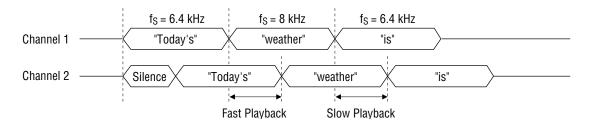

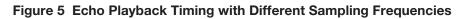

For example, to obtain data rate from the following conditions,