MICRO POWER SYSTEMS INC 查询MP1210HN供应商 T-51-09-12 Micr

FRANCE REAL PROPERTY OF THE CONTROL OF THE PROPERTY OF THE PRO

MP1208/9/10

Microprocessor Compatible Double-Buffered, 12-Bit Digital-to-Analog Converter

#### **FEATURES**

- Lower Data Bus Feedthrough @ CS = 1

- Stable, More Accurate Segmented DAC Approach

- Ultra Stable

- 0.2 ppm/°C Linearity Tempco

- 2 ppm/°C Max Gain Error Tempco

- Low Sensitivity to Amplifier V<sub>OS</sub>

- Low Output Capacitance

- C<sub>OUT1</sub> = 80 pF at Full Scale, Gives Fastest Settling Times, and Larger Stable Bandwidth capability

- Lower Glitch Energy

- · Four Quadrant Multiplication

- All Parts guaranteed 12-Bit Monotonic

- Low Feedthrough Error

- Low Power Consumption

- TTL/CMOS Compatible

- Latch-Up Free

- -55°C to +125°C Operation

- CDIP & PDIP Packages Available

### **GENERAL DESCRIPTION**

The MP1208/09/10 series are 12-bit D/A Converters with an 8/4 bit latched input interface that provide maximum flexibility in interfacing to µP data bus. All data loading and data transfer operations are identical to the WRITE cycle of a static RAM.

The MP1208 series use a unique circuit which significantly reduces transients in the supplies during DATA bus transitions at  $\overline{CS} = 1$ .

The MP1208 series are manufactured using advanced thin film resistors on a double metal CMOS process. The MP1208 series incorporates a unique bit decoding technique yielding lower glitch, higher speed and excellent accuracy over temperature and time. 12-bit linearity is achieved with minimal trimming. Outstanding features include:

- Stability: Both integral and differential linearity are rated at 0.2 ppm/°C typical, and monotonicity is guaranteed over the entire temperature range including the industrial (-40 to +85°C) and military ranges. Scale factor is a low 2 ppm/°C maximum.

- Low Output Capacitance: Due to smaller MOSFET switch geometries allowed by decoding, the output capacitance at

I<sub>OUT1</sub> and I<sub>OUT2</sub> are a low 80pF / 40pF and 25pF / 65 pF for the conditions of full/zero scale. This is over two times less than the National DAC 1208 Series. Lower capacitance allows the MP1208 series to achieve faster CMOS DAC settling times; less than 1 μsec for a 10 V step to 0.01% when utilizing a high speed output amplifier. Larger output amplifier bandwidths are available, for a given amplifier loop gain, because a smaller feedback "zero" compensating capacitor is required to offset the smaller lour capacitance.

Low Sensitivity to Output Amplifier Offset: 4 quadrant multiplying CMOS DACs provide an output current into the virtual ground of an op amp. The additional linearity error incurred by amplifier offset is reduced by a factor of 2 in the MP1208 series over conventional R-2R DACs, to 330µV per millivolt of offset.

Specified for operation over the commercial / industrial (-40 to +85°C) and military (-55 to +125°C) temperature ranges, the MP1208/09/10 is available in Plastic (PDIP) and Ceramic (CDIP) dual-in-line packages.

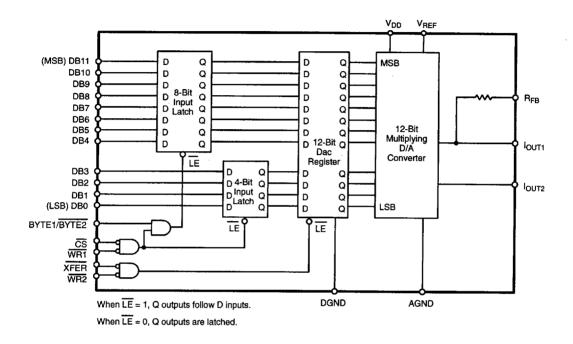

#### SIMPLIFIED BLOCK DIAGRAM

#### ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.     | INL<br>(LSB) | DNL<br>(LSB) | Gain Error<br>(% FSR) |

|-----------------|----------------------|--------------|--------------|--------------|-----------------------|

| Plastic Dip     | -40 to +85°C         | MP1210HN     | <u>+</u> 2   | ±2           | ±0.4                  |

| Plastic Dip     | -40 to +85°C         | MP1209JN     | ±1           | ±1           | ±0.4                  |

| Plastic Dip     | -40 to +85°C         | MP1208KN     | ±1/2         | ±3/4         | ±0.4                  |

| Ceramic Dip     | -40 to +85°C         | MP1208BD     | ±1/2         | ±3/4         | ±0.4                  |

| Ceramic Dip     | -55 to +125°C        | MP1208TD     | ±1/2         | ±3/4         | ±0.4                  |

| Ceramic Dip     | -55 to +125°C        | MP1208TD/883 | ±1/2         | ±3/4         | ±0.4                  |

| Ceramic Dip     | -40 to +85°C         | MP1209AD     | ±1           | ±1           | ±0.4                  |

| Ceramic Dip     | –55 to +125°C        | MP1209SD     | ±1           | <u>+</u> 1   | ±0.4                  |

| Ceramic Dip     | -55 to +125°C        | MP1209SD/883 | ±1           | ±1           | ±0.4                  |

| Ceramic Dip     | -55 to +125°C        | MP1210RD     | ±2           | ±2           | ±0.4                  |

| Ceramic Dip     | −55 to +125°C        | MP1210RD/883 | ±2           | ±2           | ±0.4                  |

| Ceramic Dip     | -40 to +85°C         | MP1210ZD     | ±2           | <u>+</u> 2   | ±0.4                  |

Micro Power Systems

## MP1208/09/10

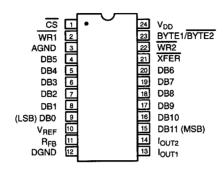

### PIN CONFIGURATION

24 Pin CDIP, PDIP (0.600") D24, N24

## PIN OUT DEFINITIONS

| PIN NO. | NAME              | DESCRIPTION                          |

|---------|-------------------|--------------------------------------|

| 1       | CS                | Chip Select (Active Low)             |

| 2       | WR1               | Write1 (Active Low)                  |

| 3       | AGND              | Analog Ground                        |

| 4       | DB5               | Data Input Bit 5                     |

| 5       | DB4               | Data Input Bit 4                     |

| 6       | DB3               | Data Input Bit 3                     |

| 7       | DB2               | Data Input Bit 2                     |

| 8       | DB1               | Data Input Bit 1                     |

| 9       | DB0               | Data Input Bit 0 (LSB)               |

| 10      | V <sub>REF</sub>  | Reference Input Voltage              |

| 11      | R <sub>FB</sub>   | Internal Feedback Resistor           |

| 12      | DGND              | Digital Ground                       |

| 13      | louT1             | Current Output 1                     |

| 14      | l <sub>OUT2</sub> | Current Output 2                     |

| 15      | DB11              | Data Input Bit 11 (MSB)              |

| 16      | DB10              | Data Input Bit 10                    |

| 17      | DB9               | Data Input Bit 9                     |

| 18      | DB8               | Data Input Bit 8                     |

| 19      | DB7               | Data Input Bit 7                     |

| 20      | DB6               | Data Input Bit 6                     |

| 21      | XFER              | Transfer Control Signal (Active Low) |

| 22      | WR2               | Write 2 (Active Low)                 |

| 23      | BYTE1/<br>BYTE2   | Byte Sequence Control                |

| 24      | V <sub>DD</sub>   | Positive Power Supply                |

## **ELECTRICAL CHARACTERISTICS**

(V<sub>DD</sub> = + 15 V, V<sub>REF</sub> = +10 V unless otherwise noted)

| Parameter STATIC PERFORMANCE (1)             | Symbol                              | Min      |              |              |     | Tmax       |          | 1                                               |

|----------------------------------------------|-------------------------------------|----------|--------------|--------------|-----|------------|----------|-------------------------------------------------|

| STATIC PERFORMANCE (1)                       |                                     | MIII     | Тур          | Max          | Min | Max        | Units    | Test Conditions/Comments                        |

|                                              |                                     |          |              |              |     |            |          | FSR = Full Scale Range                          |

| Resolution (All Grades)                      | N                                   | 12       |              |              | 12  |            | Bits     |                                                 |

| Integral Non-Linearity                       | INL                                 |          |              |              |     |            | LSB      | Best Fit Straight Line Spec.                    |

| (Relative Accuracy)<br>MP1208                |                                     |          |              | ±1/2         |     | ±1/2       |          | (Max INL - Min INL) / 2                         |

| MP1209                                       |                                     |          |              | ±1           |     | ±1         | <b>!</b> |                                                 |

| MP1210                                       |                                     |          |              | ±2           |     | <u>+</u> 2 |          |                                                 |

| Differential Non-Linearity                   | DNL                                 |          |              |              |     |            | LSB      |                                                 |

| MP1208<br>MP1209                             |                                     |          |              | ±3/4<br>±1   |     | ±3/4<br>±1 |          |                                                 |

| MP1210                                       |                                     |          |              | ±2           | l   | ±2         | ,        |                                                 |

| Gain Error                                   | GE                                  |          | <u>+</u> 0.1 | <u>+</u> 0.4 |     | ±0.4       | % FSR    | Using Internal R <sub>FB</sub>                  |

| Gain Temperature Coefficient (2)             | TC <sub>GE</sub>                    |          |              |              |     | ±2         | ppm/°C   | ∆Gain/∆Temperature                              |

| Power Supply Rejection Ratio                 | PSRR                                |          |              | ±50          |     | ±50        | ppm/%.   | ΔGain/ΔV <sub>DD</sub>   ΔV <sub>DD</sub> = ±5% |

| Output Leakage Current                       | lоит                                | -10      | 1            | 10           |     | ±200       | nA       |                                                 |

| DYNAMIC PERFORMANCE (2)                      |                                     |          |              |              |     |            |          | RL=100Ω, CL=13pF                                |

| Current Settling Time                        | ts                                  |          | 1            |              |     |            | μs       | Full Scale Change to 1/2 LSB $R_1 = 100\Omega$  |

| AC Feedthrough at I <sub>OUT1</sub>          | FT                                  |          | 1            |              |     |            | mV p-p   | V <sub>REF</sub> =100kHz, 20 Vp-p, sinewave     |

| REFERENCE INPUT                              |                                     |          |              |              |     |            |          |                                                 |

| Input Resistance                             | R <sub>IN</sub>                     | 5        | 10           | 20           | 5   | 20         | kΩ       |                                                 |

| V <sub>IN</sub> (2)                          |                                     |          | ±10          | ±25          |     |            | ٧        |                                                 |

| DIGITAL INPUTS                               |                                     |          |              |              |     |            | l        |                                                 |

| Logical "1" Voltage                          | $v_{iH}$                            | 2.4      |              |              | 2.4 |            | v        |                                                 |

| Logical "0" Voltage<br>Input Leakage Current | V <sub>IL</sub><br>I <sub>LKG</sub> | _1       | 0.1          | 0.8<br>1     |     | 0.8<br>±1  | V<br>μΑ  | V <sub>IN</sub> = 0 or V <sub>DD</sub>          |

| ANALOG OUTPUTS                               | 'LNG                                | <u>'</u> |              |              |     | Ξ'         | μΛ       | VIN = O OI VDD                                  |

| Output Capacitance (2)                       | ĺ                                   |          |              |              |     |            |          |                                                 |

| output outputtante (2)                       | C <sub>OUT1</sub>                   |          | 80           | 100          |     |            | ρF       | DAC Inputs all 1's                              |

|                                              | C <sub>OUT1</sub>                   |          | 40           | 60           |     |            | pF       | DAC Inputs all 0's                              |

|                                              | C <sub>OUT2</sub>                   |          | 65<br>25     | 85<br>45     |     | - 1        | pF<br>pF | DAC Inputs all 0's<br>DAC Inputs all 1's        |

| POWER SUPPLY                                 | 33.2                                |          |              | -            |     |            |          |                                                 |

| Functional Voltage Range (5)                 | $V_{DD}$                            | 4.5      | 15           | 16           | 4.5 | 16         | v        |                                                 |

| Supply Current                               | IDD                                 |          | 1.2          | 2.0          | **= | 2.0        | mA       | All digital inputs = 0 V or all = 5 V           |

## **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                    | Symbol                          | Min                           | 25°C<br>Typ                | Max | Tmin to<br>Min | Tmax<br>Max | Units                | Test Conditions/Comments |

|--------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------|----------------------------|-----|----------------|-------------|----------------------|--------------------------|

| SWITCHING<br>CHARACTERISTICS (2, 4)                                                                          |                                 |                               |                            |     |                |             |                      |                          |

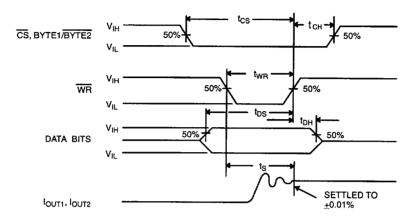

| Write and XFER Pulse Width<br>Data Set-Up Time<br>Data Hold Time<br>Control Set-Up Time<br>Control Hold Time | twn<br>tds<br>tdh<br>tcs<br>tch | 100<br>100<br>90<br>200<br>10 | 50<br>50<br>70<br>100<br>0 |     |                | į           | ns<br>ns<br>ns<br>ns |                          |

#### NOTES:

- (1) Full Scale Range (FSR) is 10V.

- (2) Guaranteed but not production tested.

- (3) Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- (4) See timing diagram.

- (5) Specified values guarantee functionality. Refer to other parameters for accuracy.

Specifications are subject to change without notice

### ABSOLUTE MAXIMUM RATINGS (1, 2, 3) (TA = +25°C unless otherwise noted)

| V <sub>DD</sub> to GND 0 to +17 V                                                                                                               | Storage Temperature65°C to +150°C               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Digital Input Voltage to GND GND -0.5 to V <sub>DD</sub> +0.5 V I <sub>OUT1</sub> , I <sub>OUT2</sub> to GND GND -0.5 to V <sub>DD</sub> +0.5 V | Lead Temperature (Soldering, 10 seconds) +300°C |

| V <sub>REF</sub> to GND±25 V                                                                                                                    | Package Power Dissipation Rating to 75°C        |

| V <sub>RFB</sub> to GND±25 V                                                                                                                    | CDIP, PDIP                                      |

| AGND to DGND                                                                                                                                    |                                                 |

| (Functionality Guaranteed $\pm 0.5 \text{ V}$ )                                                                                                 | Derates above 75°C                              |

#### NOTES:

- (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- (2) Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

- (3) GND refers to AGND and DGND.

### **TIMING DIAGRAM**

# APPLICATION NOTES Refer to Section 8 for Applications Information

The MP1208 series allows direct interface to microprocessor system buses without the need for additional interface circuitry. They also provide all 12 data input lines in parallel for optimum interface to a 16-bit data bus, but can be mapped onto an 8-bit bus by tying lines DB0 through DB3 to lines DB8 through DB11, respectively.

All digital inputs maintain TTL compatibility over the entire range of V<sub>DD</sub>. The internal latches are lever-triggered, and therefore can be hardwired for transparent operation. The MP1208 series can be wired for a single layer of buffering by tying the 12 bit DAC register transparent (ground XFER and WR2) or by tying the 8-bit and 4-bit latch transparent (ground CS, WR1, BYTE1/BYTE2 = V<sub>DD</sub>). In non-microprocessor applications, the MP1208 series can be wired for flow-through operation. The analog output will continuously reflect the state of

the digital inputs by tying the 8-bit latch, 4-bit latch, and 12-bit DAC register transparent.

Double-buffering provides the user with the capability of refreshing simultaneously all 12 data bits to the DAC from an 8-bit data bus. Double-buffering also allows a single DAC or several DACs to be updated from the same data bus at the same time. This will be done asynchronously by an external monitoring device (such as a voltage comparator) or by a system interrupt. In this example, tie WR2 low and use the XFER to update the 12-bit register.

For a two byte load, tie BYTE 1/BYTE 2 and XFER together and WR1 and WR2 together. The first write will update the 8-bit input latch (the 4-bit latch is also changed). The second write will overwrite the 4-bit latch and transfer all 12 bits to the 12-bit DAC register, updating the D/A converter. (See Typical Application.)