# (LCD Driver with 80-Channel Outputs)

## Description

The HD61200 is a column driver LSI for a largearea dot matrix LCD. It employs 1/32 or more duty cycle multiplexing method. It receives serial display data from a micro controller or a display control LSI, HD61830, etc., and generates liquid crystal driving signals.

## **Ordering Information**

| Type No. | Package                     |  |

|----------|-----------------------------|--|

| HD61200  | 100-pin plastic QFP(FP-100) |  |

#### **Features**

- Liquid crystal display driver with serial/parallel conversion function

- Internal liquid crystal display driver: 80 drivers

- Drives liquid crystal panels with 1/32-1/128 duty cycle multiplexing

- Can interface to LCD controllers, HD61830 and HD61830B

- Data transfer rate: 2.5 MHz max

- Power supply: V<sub>CC</sub>: 5 V ± 10% (Internal logic)

- Power supply voltage for liquid crystal display drive: 8 V to 17 V

- CMOS process

## **Absolute Maximum Ratings**

| Item                  | Symbol          | Value                             | Unit | Note |

|-----------------------|-----------------|-----------------------------------|------|------|

| Supply voltage (1)    | Voc             | -0.3 to +7.0                      | ٧    | 2    |

| Supply voltage (2)    | V <sub>EE</sub> | $V_{CC} - 19.0$ to $V_{CC} + 0.3$ | V    |      |

| Terminal voltage (1)  | V <sub>T1</sub> | -0.3 to V <sub>CC</sub> + 0.3     | ٧    | 2, 3 |

| Terminal voltage (2)  | V <sub>T2</sub> | $V_{EE} - 0.3$ to $V_{CC} + 0.3$  | ٧    | 4    |

| Operating temperature | Topr            | -20 to +75                        | °C   |      |

| Storage temperature   | Tstg            | -55 to +125                       | °C   |      |

#### Notes: 1.

- LSIs may be permanently destroyed if being used beyond the absolute maximum ratings. In ordinary operation, it is desirable to use them within the limits of electrical characteristics, because using them beyond these conditions may cause malfunction and poor reliability.

- All voltage values are referenced to GND = 0 V.

- 3. Applies to input terminals, FCS, SHL, CL1, CL2, DL, DR, E, and M.

- 4. Applies to  $V_{1L}$ ,  $V_{1R}$ ,  $V_{2L}$ ,  $V_{2R}$ ,  $V_{3L}$ ,  $V_{3R}$ ,  $V_{4L}$ , and  $V_{4R}$ . Must maintain  $V_{CC} \ge V_{1L} = V_{1R} \ge V_{3L} = V_{3R} \ge V_{4L} = V_{4R} \ge V_{2L} = V_{2R} \ge V_{EE}$ .

- Connect a protection resistor of 15  $\Omega$  ± 10% to each terminal in series.

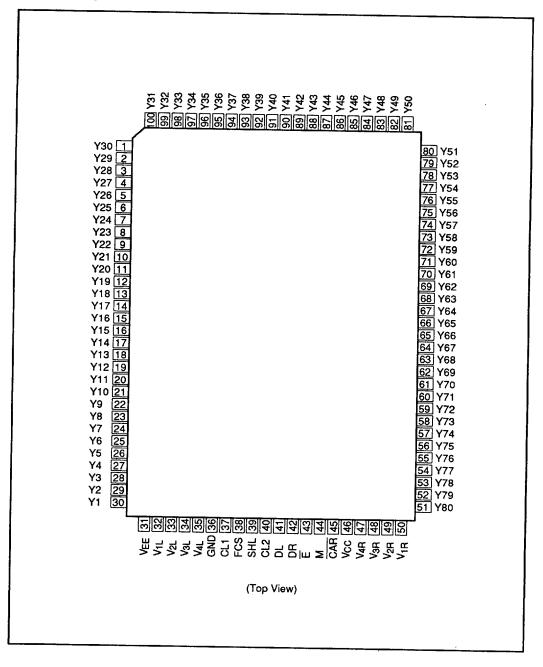

## Pin Arrangement

#### **Electrical Characteristics**

DC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ , GND = 0 V,  $V_{CC} - \text{VEE} = 8 \text{ V}$  to 17 V, Ta = -20 to 75°C)

| ltem                    | Symbol           | Min                  | Тур | Max                      | Unit | <b>Test Condition</b>                                | Note |

|-------------------------|------------------|----------------------|-----|--------------------------|------|------------------------------------------------------|------|

| Input high voltage      | VIH              | 0.7×V <sub>CC</sub>  | _   | Vcc                      | ٧    |                                                      | 1    |

| Input low voltage       | V <sub>IL</sub>  | 0                    | _   | 0.3 ×<br>V <sub>CC</sub> | ٧    |                                                      | 1    |

| Output high voltage     | V <sub>OH</sub>  | V <sub>CC</sub> -0.4 | _   | _                        | ٧    | l <sub>OH</sub> = 400 μA                             | 2    |

| Output low voltage      | VoL              | _                    |     | 0.4                      | V    | l <sub>OL</sub> = 400 μA                             | 2    |

| Driver on resistance    | Ron              | _                    | _   | 7.5                      | kΩ   | Load current =<br>100 μA                             | 5    |

| Input leakage current   | I <sub>IL1</sub> | -1                   | _   | 1                        | μА   | V <sub>IN</sub> = 0 to V <sub>∞</sub>                | 1    |

| Input leakage current   | I <sub>IL2</sub> | -2                   |     | 2                        | μΑ   | V <sub>IN</sub> = V <sub>EE</sub> to V <sub>CC</sub> | 3    |

| Dissipation current (1) | IGND             |                      | _   | 1.0                      | mA   |                                                      | 4    |

| Dissipation current (2) | lEE              |                      | _   | 0.1                      | mA   |                                                      | 4    |

- Notes: 1. Applies to CL1, CL2, SHL, E, M, DL, and DR.

- 2. Applies to CAR.

- 3. Applies to V<sub>1L</sub>, V<sub>1R</sub>, V<sub>2L</sub>, V<sub>2R</sub>, V<sub>3L</sub>, V<sub>3R</sub>, V<sub>4L</sub>, and V<sub>4R</sub>.

- 4. Specified when display data is transferred under following conditions:

CL2 frequency f<sub>CP2</sub> = 2.5 MHz (data transfer rate)

CL1 frequency f<sub>CP1</sub> = 4.48 kHz (data latch frequency)

M frequency f<sub>M</sub> = 35 Hz (frame frequency/2)

Specified at VIH = VCC (V), VIL = 0 V and load on outputs.

IGND: currents between VCC and GND.

IEE: currents between VCC and VEE.

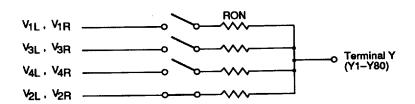

Resistance between terminal Y and terminal V (one of V<sub>1L</sub>, V<sub>1R</sub>, V<sub>2L</sub>, V<sub>2R</sub>, V<sub>3L</sub>, V<sub>3R</sub>, V<sub>4L</sub>, and V<sub>4R</sub> when load current flows through one of the terminals Y1 to Y80. This value is specified under the following condition:

$$\begin{aligned} &V_{CC}-V_{EE} = 17 \text{ V} \\ &V_{1L}=V_{1R}, \text{ } V_{3L}=V_{3R} = V_{CC}-2/7 \text{ } (V_{CC}-V_{EE} \text{ }) \\ &V_{2L}=V_{2R}, \text{ } V_{4L}=V_{4R}=V_{EE}+2/7 \text{ } (V_{CC}-V_{EE} \text{ }) \end{aligned}$$

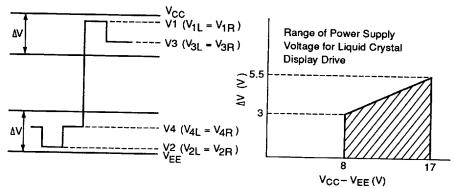

The following here is a description of the range of power supply voltage for liquid crystal display drivers. Apply positive voltage to  $V_{1L} = V_{1R}$  and  $V_{3L} = V_{3R}$  and negative voltage to  $V_{2L} = V_{2R}$  and  $V_{4L} = V_{4R}$  within the  $\Delta V$  range. This range allows stable impedance on driver output (RON). Notice the  $\Delta V$  depends on power supply voltage  $V_{CC}$ – $V_{EE}$ .

Correlation between Driver Output Waveform and Power Supply Voltages for Liquid Crystal Display Drive

Correlation between Power Supply Voltage V<sub>CC</sub>- V<sub>EE</sub> and  $\Delta$  V

# Terminal Configuration

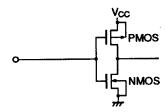

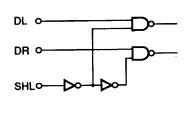

Input Terminal

Applicable terminals: CL1, CL2, SHL, E, M

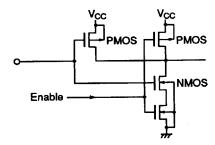

Input Terminal (with Enable)

Applicable terminals: DL, DR

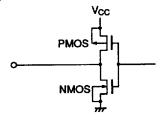

**Output Terminal**

Applicable terminal: CAR

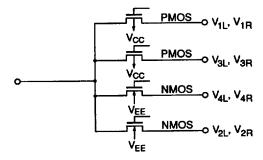

**Output Terminal**

Applicable terminals: Y1-Y80

**HITACHI**

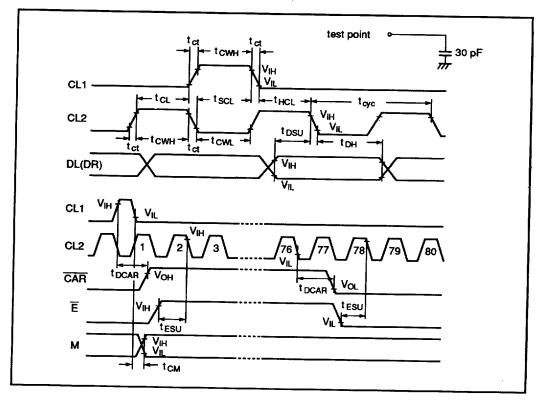

AC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ , GND = 0 V, Ta = -20 to +75°C)

| Item                       | Symbol           | Min | Тур | Max | Unit | Test        | Condition     | Note        |

|----------------------------|------------------|-----|-----|-----|------|-------------|---------------|-------------|

| Clock cycle time           | tcyc             | 400 |     |     | ns   |             |               |             |

| Clock high level width     | tcwH             | 150 | _   |     | ns   | <del></del> |               |             |

| Clock low level width      | tcwL             | 150 |     |     | ns   |             |               |             |

| Clock setup time           | t <sub>SCL</sub> | 100 |     |     | ns   |             |               |             |

| Clock hold time            | tHCL             | 100 |     |     | ns   |             |               |             |

| Clock rise/fall time       | t <sub>Ct</sub>  |     |     | 30  | ns   |             |               |             |

| Clock phase different time | t <sub>CL</sub>  | 100 |     |     | ns   |             | <del></del> _ |             |

| Data setup time            | tosu             | 80  |     | _   | ns   |             | <del></del>   |             |

| Data hold time             | t <sub>DH</sub>  | 100 | _   |     | ns   |             |               | <del></del> |

| E setup time               | t <sub>ESU</sub> | 200 |     |     | ns   |             | <del></del>   |             |

| Output delay time          | tDCAR            |     |     | 300 | ns   |             |               | 1           |

| M phase difference time    | t <sub>CM</sub>  | _   |     | 300 | ns   |             |               |             |

Note: 1. The following load circuit is connected for specification:

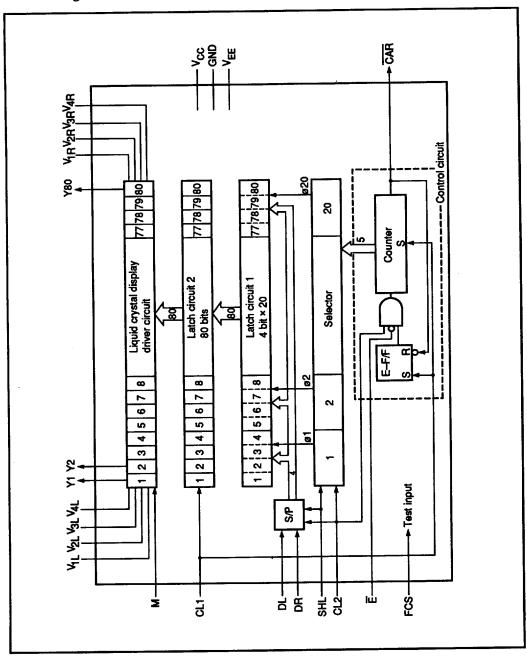

# Block Diagram

#### Block Function

# Liquid Crystal Display Driver Circuit

The combination of the data from the latch circuit 2 and M signal causes one of the 4 liquid crystal driver levels, V1, V2, V3, and V4 to be output.

## 80-bit Latch Circuit 2

The data from latch circuit 1 is latched at the fall of CLI and output to liquid crystal display driver circuit.

#### S/P

Serial/parallel conversion circuit which converts 1bit data into 4-bit data. When SHL is low level, data from DL is converted into 4-bit data and transferred to the latch circuit 1. In this case, don't connect any lines to terminal DR.

When SHL is high level, input data from terminal DR without connecting any lines to terminal DL.

## 80-bit Latch Circuit 1

The 4-bit data is latched at  $\phi 1$ — $\phi 20$  and output to latch circuit 2. When SHL is low level, the data from DL are latched in order of  $1\rightarrow 2\rightarrow 3$  ...  $\rightarrow 80$  of each latch. When SHL is high level, they are latched in a reverse order  $(80\rightarrow 79\rightarrow 78$  ...  $\rightarrow 1)$ .

#### Selector

The selector decodes output signals from the counter and generates latch clock  $\phi 1$  to  $\phi 20$ . When the LSI is not active,  $\phi 1-\phi 20$  are not generated, so the data at latch circuit 1 is stored even if input data (DL, DR) changes.

#### Control Circuit

Controls operation: When E-F/F (enable F/F) indicates 1, S/P conversion is started by inputting low level to E. After 80-bit data has been all converted,  $\overline{CAR}$  output turns into low level and E-F/F is reset to 0, and consequently the conversion stops. E-F/F is RS flip-flop circuit which gives priority to SET over RESET and is set at high level of CL1.

The counter consists of 7 bits, and the output signals upper 5 bits are transferred to the selector.  $\overline{CAR}$  signal turns into high level at the rise of CL1. The number of bits that can be S/P-converted can be increased by connecting  $\overline{CAR}$  terminal with  $\overline{E}$  terminal of the next HD61200.

# **Terminal Functions Description**

| Terminal<br>Name                 | Number of<br>Terminals | 1/0 | Connected<br>to                       | Functions                                              | 3                                |                                |                            |                                              |                             |  |  |

|----------------------------------|------------------------|-----|---------------------------------------|--------------------------------------------------------|----------------------------------|--------------------------------|----------------------------|----------------------------------------------|-----------------------------|--|--|

| V <sub>CC</sub>                  | 1                      |     | Power                                 | V <sub>CC</sub> − GND: Power supply for internal logic |                                  |                                |                            |                                              |                             |  |  |

| GND<br>V <sub>EE</sub>           | i<br>1                 |     | supply                                | V <sub>CC</sub> - V <sub>EE</sub> :                    | Power :                          | supply for LC                  | CD drive cir               | cuit                                         |                             |  |  |

| V <sub>1L</sub> -V <sub>4L</sub> | 8                      |     | Power                                 |                                                        |                                  | quid crystal                   |                            |                                              |                             |  |  |

| V <sub>1R</sub> -V <sub>4R</sub> |                        |     | supply                                | V <sub>3L</sub> (V <sub>3R</sub> ), \                  | / <sub>4L</sub> (V <sub>4F</sub> | ;): Selection<br>;): Non-selec | Ction level                |                                              |                             |  |  |

|                                  |                        |     |                                       | Power sun                                              | dies cor                         | nnected with<br>(4R) should h  | ıV₁ı and V                 | <sub>1R</sub> (V <sub>2L</sub> 8<br>me volta | k V <sub>2R</sub> ,<br>ges. |  |  |

| Y1-Y80                           | 80                     | 0   | LCD                                   | Liquid crys                                            |                                  |                                |                            |                                              |                             |  |  |

| 11-100                           | 50                     | •   |                                       |                                                        |                                  | 4 leveis, V1                   | , V2 V3, ar                | nd V4.                                       |                             |  |  |

|                                  |                        |     |                                       |                                                        |                                  | itput level, M                 |                            |                                              | (D) is as                   |  |  |

|                                  |                        |     |                                       |                                                        | М                                | 1                              | ·                          |                                              |                             |  |  |

|                                  |                        |     |                                       |                                                        | D                                | 1                              | 0 1 0                      | <u>J</u>                                     |                             |  |  |

|                                  |                        |     |                                       |                                                        | Output<br>level                  | <u> V1</u>                     | V3 V2 V                    | 4                                            |                             |  |  |

| M                                | 1                      | ı   | Controller                            | Switch sig<br>AC.                                      | nal to o                         | onvert liquid                  | crystal driv               | ve wavef                                     | orm into                    |  |  |

| CL1                              | 1                      | 1   | Controller                            | Synchronous signal (a counter is reset at high leve    |                                  |                                |                            | /el).                                        |                             |  |  |

| <b>.</b>                         |                        |     |                                       | Latch cloc                                             | k of disp                        | play data (fa                  | ılling edge                | triggered                                    | i).                         |  |  |

|                                  |                        |     |                                       | Synchroni<br>signals co                                | zed with<br>rrespon              | the fall of 0                  | CL1, liquid<br>display dat | crystal d<br>a are out                       | river<br>put.               |  |  |

| CL2                              | 1                      | ī   | Controller                            | Shift clock                                            | of disp                          | lay data (D)                   |                            |                                              |                             |  |  |

| JLE.                             | •                      | •   |                                       | Falling ed                                             |                                  |                                | _                          |                                              |                             |  |  |

| DL, DR                           | 2                      | 1   | Controller                            |                                                        |                                  | olay data (D                   | ).                         |                                              |                             |  |  |

| UL, UN                           | _                      | •   | 222                                   | (D)                                                    | ·                                | Liquid Crys<br>Driver Outr     | tal                        | Liquid<br>Displa                             | Crystal<br>y                |  |  |

|                                  |                        |     |                                       | 1 (High le                                             | /el)                             | Selection I                    | evel                       | On                                           |                             |  |  |

|                                  |                        |     |                                       | 0 (Low lev                                             |                                  | Non-select                     |                            | Off                                          |                             |  |  |

| CHI                              |                        |     | V <sub>CC</sub> or GND                |                                                        |                                  | direction of                   | serial data.               |                                              |                             |  |  |

| SHL                              | 1                      | ı   | , , , , , , , , , , , , , , , , , , , | When the                                               | serial d                         | ata (D) is in                  | out in order               | of D1→                                       | →D86<br>are as              |  |  |

|                                  |                        |     |                                       | SHL                                                    | <b>Y</b> 1                       | Y2                             | Y3                         | ••••                                         | Y80                         |  |  |

|                                  |                        |     |                                       | Low                                                    | D1                               | D2                             | D3                         |                                              | D80                         |  |  |

|                                  |                        |     |                                       | High                                                   | D80                              | D79                            | D78                        |                                              | D1                          |  |  |

# Terminal Functions Description (cont)

| Terminal<br>Name | Number of<br>Terminals | 1/0                          | Connected to                          | Functions                                                                                              |

|------------------|------------------------|------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|

| SHL<br>(cont)    | 1                      | ı                            | V <sub>CC</sub> or GND                | When SHL is low, data is input from the DL terminal. No lines should be connected to the DR terminal.  |

|                  |                        |                              |                                       | When SHL is high, the relation between DL and DR reverses.                                             |

| Ē                | - I GND or the         | Controls the S/P conversion. |                                       |                                                                                                        |

|                  |                        |                              | terminal CAR<br>of the<br>HD61200     | The operation stops on high level, and the S/P conversion starts on low level.                         |

| CAR              | 1                      | 0                            | Input terminal<br>E of the<br>HD61200 | Used for cascade connection with the HD61200 to increase the number of bits that can be S/P converted. |

| FCS              | 1                      | 1                            | GND                                   | Input terminal for test.                                                                               |

| · ·              |                        |                              |                                       | Connect to GND.                                                                                        |

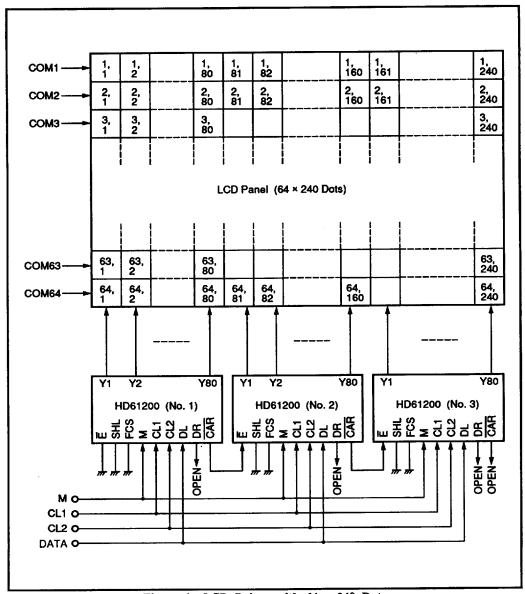

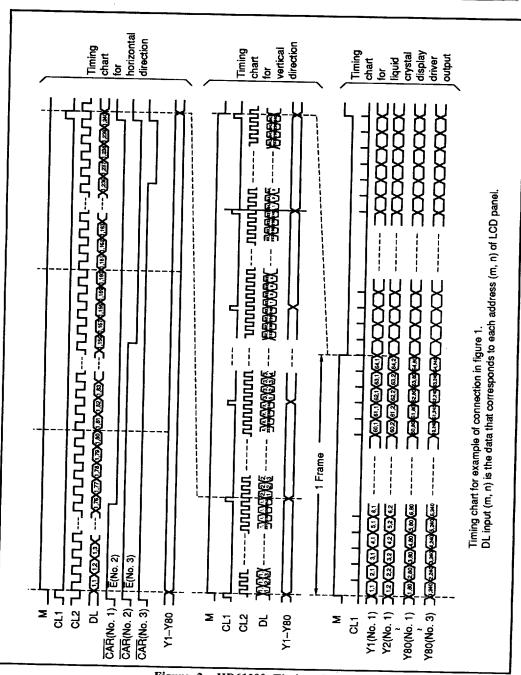

# Operation of the HD61200

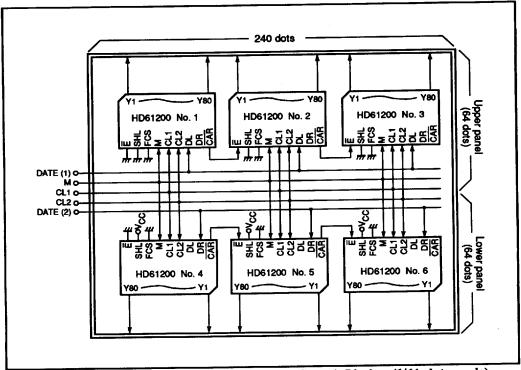

The following describes an LCD panel with  $64 \times 240$  dots on which characters are displayed with 1/64 duty cycle dynamic drive. Figure 1 is an example of liquid crystal display and connection to HD61200s. Figure 2 is a time chart of HD61200 I/O signals.

Figure 1 LCD Driver with 64 × 240 Dots

Cascade three HD61200s. Input data to the DL terminal of No. 1, No. 2, and No. 3. Connect  $\overline{E}$  of No. 1 to GND. Don't connect any lines to  $\overline{CAR}$  of No. 3. Connect common signal terminals (COM1–COM64) to X1–X64 of common driver HD61203. (m, n) of LCD panel is the address corresponding to each dot.

Figure 2 HD61200 Timing Chart

#### HITACHI

## Application Example

Figure 3 Example of 128 × 240 Dot Liquid Crystal Display (1/64 duty cycle)

The liquid crystal panel is divided into upper and lower parts. These two parts are driven separately. HD61200s No. 1 to No. 3 drive the upper half. Serial data, which are input from the DATA (1) terminal, appear at  $Y_1 \rightarrow Y_2 \rightarrow \cdots Y_{80}$  terminal of No. 1, then at  $Y_1 \rightarrow Y_2 \rightarrow \cdots Y_{80}$  of No. 2 and then at  $Y_1 \rightarrow Y_2 \rightarrow \cdots Y_{80}$  of No. 3 in the order in which they were input (in the case of SHL = low). HD61200s No. 4 to No. 6 drive the lower half. Serial data, which are input from DATA (2) terminal, appear at  $Y_{80} \rightarrow Y_{79} \rightarrow \cdots Y_{1}$  of No. 4, then at  $Y_{80} \rightarrow Y_{79} \rightarrow \cdots Y_{1}$  of No. 5 and then  $Y_{80} \rightarrow Y_{79} \rightarrow \cdots Y_{1}$  of No. 6 in the order in which they were input (in the case of SHL = high).

As shown in this example, a PC board for a display divided into upper and lower half can be easily designed by using the SHL terminal effectively.