查询CD40194BF供应商

# **CMOS 4-Bit Bidirectional Universal Shift Register**

High-Voltage Types (20 Volt Rating)

CD40194B Is a universal shift register featuring parallel inputs, parallel outputs SHIFT RIGHT and SHIFT LEFT serial inputs, and a direct overriding clear input. In the parallel-load mode (S0 and S1 are high), data is loaded into the associated flip-flop and appears at the output after the positive transition of the CLOCK Input. During loading, serial data flow is inhibited. Shift right and shift left are accomplished synchronously on the positive clock edge with data entered at the SHIFT RIGHT and SHIFT LEFT serial inputs, respectively. Clocking of the register is inhibited when both mode control inputs are low. When low, the RESET input resets all stages and forces all outputs low.

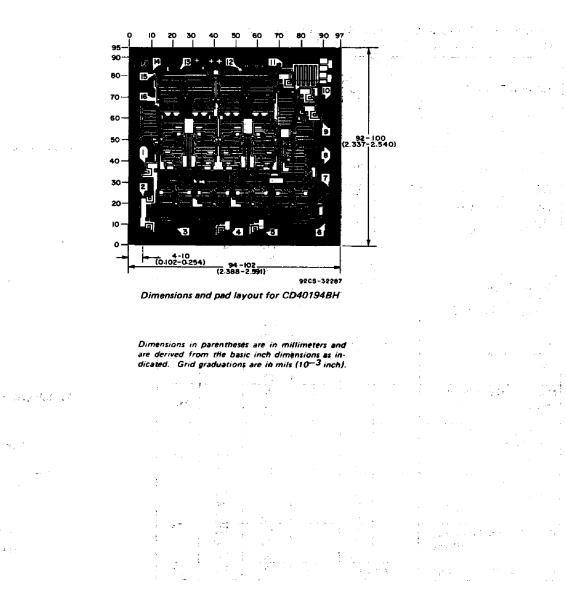

The CD40194B types are supplied in 16lead ceramic dual-in-line packages (D and F suffixes), 16-lead dual-in-line plastic packages (E suffix), and in chip form (H suffix).

The CD40194B is similar to industry types 340194 and MC40194.

# NOT RECOMMENDED FOR NEW DESIGNS

#### Features:

- Medium-speed: 1CL = 12 MHz (typ.) @ VDD = 10 V

Fully static operation

- Synchronous parallel or serial operation Asynchronous master reset

- characteristics

- 5-V, 10-V, and 15-V parametric ratings

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Stand-ard Specifications for Description of **'B' Series CMOS Devices''**

**D**3 SHIFT

SHIFT RIGHT

So

S,

IN

MODE

捷多邦,专业PCB打样工厂,24小时加急出货

- Standardized, symmetrical output

- Arithmetic unit bus registers Serial/parallel conversions

- General-purpose register for busorganized systems

- General-purpose registers

VDD = 16

Vss = 8

9205-24822R2

3

COMMERCIAL CMOS

**VOLTAGE IC8**

HGH

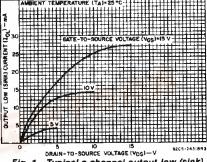

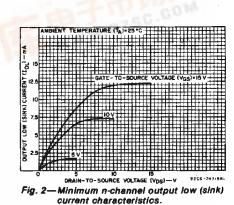

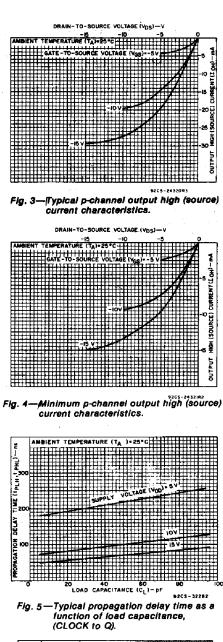

Typical n-channel output low (sink) Fig. 1 current characteristics.

# **CD40194B** Types

RECOMMENDED OPERATING CONDITIONS at  $T_A = 25$ °C, Except as Noted. For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

|                                   | VDD                                  | LIN    | ITS  | UNITS |       |

|-----------------------------------|--------------------------------------|--------|------|-------|-------|

| CHARACTERISTIC                    |                                      | (V)    | Min. |       |       |

| Supply-Voltage Range (For Package |                                      | 3      | 18   | V     |       |

| Setup Time,                       | A                                    | 5      | 100  | —     |       |

|                                   | ts                                   | 10     | 70   | —     |       |

| D0, D3, SRIN, SLINto clock        |                                      | 15     | 50   | —     |       |

|                                   |                                      | 5      | 400  | -     |       |

| SELECT 0, SELECT 1 to clock       |                                      | 10     | 220  | . — ` |       |

| -                                 |                                      | 15     | 130  |       |       |

|                                   |                                      | 5      | 0    | _     | da i  |

| Hold Time,                        | tH .                                 | 10     | 0    | _     | 14 A. |

| D0, D03, SRIN' SLIN to clock      |                                      | 15     | 0    | _     | 1     |

|                                   |                                      | 5      | 0    | —     | ns    |

| SELECT 0, SELECT 1 to clock       |                                      | 10     | 0    |       |       |

|                                   |                                      | 15     | 0    | -     |       |

|                                   |                                      | 5      | 180  | —     |       |

| Clock Pulse Width,                | tw                                   | 10     | 80   |       |       |

|                                   |                                      | 15     | 50   | —     |       |

|                                   |                                      | 5      | —    | 3     |       |

| Clock Input Frequency             | fCL                                  | · 10 . | — .  | 6     | MHz   |

|                                   |                                      | 15     |      | 8     |       |

|                                   |                                      | 5      | 1000 |       |       |

| Clock Input Rise or Fall Time,    | t <sub>r</sub> CL, t <sub>f</sub> CL | 10     | 100  | · '   | μS    |

|                                   |                                      | 15     | 100  | _     |       |

|                                   |                                      | 5      | 300  | -     |       |

| Reset Pulse Width,                | tWB                                  | 10     | 200  | —     | ns    |

|                                   |                                      | 15     | 140  |       |       |

#### CONTROL TRUTH TABLE FOR CD40194B SERIES

| MOD   |                | SELECT          |       |                            |  |  |

|-------|----------------|-----------------|-------|----------------------------|--|--|

| CLOCK | S <sub>0</sub> | \$ <sub>1</sub> | RESET | ACTION                     |  |  |

| х     | 0              | 0               | 1     | No Change                  |  |  |

| Г     | 1              | 0               | 1     | Shift Right (Q0 toward Q3) |  |  |

| 1     | 0              | 1               | 1     | Shift Left (Q3 toward Q0)  |  |  |

|       | 1              | 1               | 1     | Parallel Load              |  |  |

| x     | X              | X               | 0     | Reset                      |  |  |

1 = High level

0 = Low level

X = Don't care $\blacktriangle = Level change$

= Level change

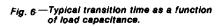

Fig. 8—CD40194B logic diagram.

### STATIC ELECTRICAL CHARACTERISTICS

| CHARAC-<br>TERISTIC                                   | co        | NDITIC     | NS         |       | LIMITS AT INDICATED<br>TEMPERATURES (°C) |                |       |       |       |      | UN<br>T  |

|-------------------------------------------------------|-----------|------------|------------|-------|------------------------------------------|----------------|-------|-------|-------|------|----------|

|                                                       |           |            |            |       |                                          |                |       |       | + 25  |      | Ś        |

|                                                       | VO<br>(V) | VIN<br>(V) | VDD<br>(V) | 55    | -40                                      | + 85           | + 125 | Min.  | Тур.  | Max. | 1        |

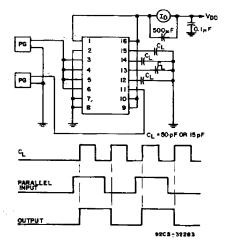

| Quiescent                                             | -         | 0,5        | 5          | 5     | 5                                        | 150            | 150   | _     | 0.04  | 5    |          |

| Device                                                | _         | 0,10       | 10         | 10    | 10                                       | 300            | 300   | —     | 0.04  | 10   | 1.       |

| Current,                                              | _         | 0,15       | 15         | 20    | 20                                       | 600            | 600   |       | 0.04  | 20   | μA       |

| IDD Max.                                              | -         | 0,20       | 20         | 100   | 100                                      | 3000           | 3000  | -     | .0.08 | 100  | 1        |

| Output Low                                            | 0.4       | 0,5        | 5          | 0.64  | 0.61                                     | 0.42           | 0.36  | 0.51  | 1     |      | <u> </u> |

| (Sink)                                                | 0.5       | 0,10       | 10         | 1.6   | 1.5                                      | 1.1            | 0.9   | 1.3   | 2.6   | —    | 1        |

| Current,                                              | 1.5       | 0,15       | 15         | 4.2   | 4                                        | 2.8            | 2.4   | 3.4   | 6.8   |      |          |

| Output<br>High                                        | 4.6       | 0,5        | 5          | -0.64 | -0.61                                    | 0.42           | -0.36 | -0.51 | —1    | _    | ] mA     |

| (Source)                                              | 2.5       | 0,5        | 5          | -2    | 1.8                                      | -1.3           | -1.15 | -1.6  | -3.2  | —    | ]        |

| Current,                                              | 9.5       | 0,10       | 10         | -1.6  |                                          | -1.1           | -0.9  | -1.3  | -2.6  | —    | 1        |

| IOH Min.                                              | 13.5      | 0,15       | 15         | -4.2  | -4                                       | -2.8           | -2.4  | -3.4  | -6.8  | —    |          |

| Output Volt-                                          | -         | 0,5        | 5          |       | 0.0                                      | 5              |       | —     | 0     | 0.05 |          |

| age: Low-                                             | _         | 0,10       | 10         |       | 0.0                                      | )5             |       | —     | 0     | 0.05 | 1        |

| Level,<br>VOLMax.                                     | _         | 0,15       | 15         |       | 0.0                                      | )5             |       | -     | 0     | 0.05 | ]        |

| <b>Output Volt-</b>                                   | _         | 0,5        | 5          |       | 4.9                                      | <del>)</del> 5 |       | 4.95  | 5     | -    | 1        |

| age: High-                                            | -         | 0,10       | 10         |       | 9.9                                      | 95             |       | 9.95  | 10    | -    | 1        |

| Level,<br>VOH Min.                                    | -         | 0,15       | 15         |       | 14.                                      | 95             |       | 14.95 | 15    | -    | V.       |

| Input Low                                             | 0.5,4.5   | —          | 5          |       | 1.                                       | 5              |       | _     |       | 1.5  | 1        |

| Voltage,                                              | 1,9       | -          | 10         |       | 3                                        |                |       |       | =     | 3    | 1        |

| VILMax.                                               | 1.5,13.5  | —          | 15         |       | 4                                        |                |       | _     |       | 4    | 1        |

| Input High                                            | 0.5,4.5   | —          | 5          |       | 3.                                       | 5              |       | 3.5   | -     |      | 1.       |

| Voltage,                                              | 1,9       | —          | 10         |       | 7                                        |                |       | 7     |       | ·    | 1        |

| VIH Min.                                              | 1.5,13.5  | -          | 15         |       | 1                                        | 1              |       | 11    | -     | -    | <b>}</b> |

| Input<br>Current<br>I <sub>IN</sub> Max.              | _         | 0,18       | 18         | ±0.1  | ±0.1                                     | ±1             | ±1    |       | ±105  | ±0.1 | μA       |

| 3-State<br>Output<br>Leakage<br>Current,<br>IOUT Max. | 0,18      | 0,18       | 18         | ±0.4  | ±0,4                                     | ±12            | ±12   | _     | ±104  | ±0.4 | μA       |

.

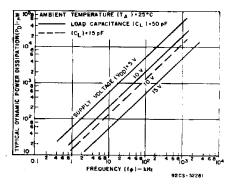

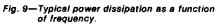

Fig, 10—Dynamic power dissipation test circuit.

a start to

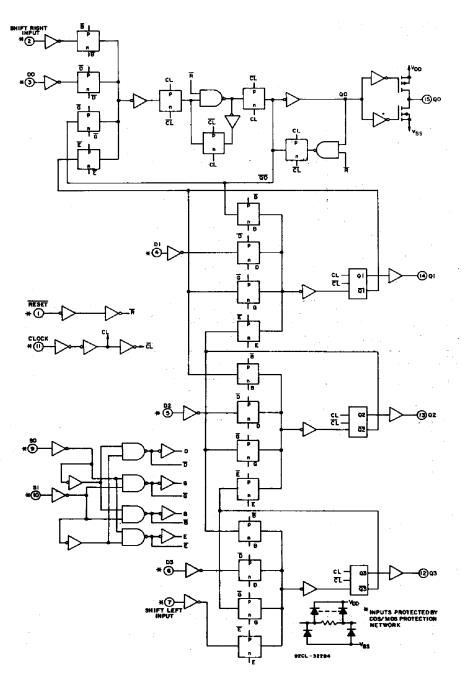

# DYNAMIC ELECTRICAL CHARACTERISTICS at T\_A = 25°C, input t\_r, t\_f = 20 ns, C\_L = 50 pF, R\_L = 200 k\Omega

|                         | TES<br>CONDIT |      |       |          |      |       |  |

|-------------------------|---------------|------|-------|----------|------|-------|--|

| CHARACTERISTIC          |               | VDD  |       | LIMITS   |      | UNITS |  |

|                         |               | v    | Min.  | Тур.     | Max. |       |  |

| Propagation Delay Time: |               | 5    | -     | 220      | 440  |       |  |

| Clock to Q tPHL, tPLH   |               | 10   | _     | 100      | 200  |       |  |

|                         |               | 15   |       | 70       | 140  |       |  |

| Output Transition Time  |               | 5    | -     | 100      | 200  | 1     |  |

| tTHL, tTLH              |               | 10   | · _ · | 50       | 100  |       |  |

|                         |               | 15   | · ·   | 40       | 80   |       |  |

| Minimum Setup Time: ts  |               | 5    | -     | 80       | 160  |       |  |

| D0, D3, SRIN, SLIN to   |               | 10   |       | 35       | 70   | ns    |  |

| Clock                   |               | 15   |       | 20       | 50   |       |  |

| SELECT 0, SELECT 1      |               | 5    |       | 200      | 400  |       |  |

| to Clock                |               | 10   | —     | 110      | 220  |       |  |

|                         |               | 15   | —     | 65       | 130  |       |  |

| Minimum Hold Time: tH   |               | 5    | _     | -65      | 0    | 1     |  |

| D0, D3, SRIN, SLIN      |               | 10   | —     | 25       | 0    |       |  |

| to Clock                |               | 15   |       | —15      | 0    | 1     |  |

| SELECT 0, SELECT 1      |               | 5    | _     | —170     | 0    | 1     |  |

| to Clock                |               | 10   | —     | 95       | 0    |       |  |

|                         |               | 15   | _     | -55      | 0    |       |  |

| Minimum Clock Pulse     |               | 5    | -     | 90       | 180  |       |  |

| Width tw                |               | 10   | -     | 40       | 80   |       |  |

|                         |               | 15   | -     | 25       | 50   | Í     |  |

| Maximum Clock Input     |               | 5    | 3     | · 6      | - I  | 1     |  |

| Frequency fcL           |               | 10   | 6     | 12       | _    | MH    |  |

|                         |               | 15   | . 8   | 15       | -    |       |  |

| Maximum Clock Rise or   |               |      |       |          |      |       |  |

| Fall Time               |               | 5    |       | -        | 1000 |       |  |

| trCL, tfCL              |               | 10   | —     | -        | 100  | μs    |  |

| · · ·                   | L             | 15   |       | <u> </u> | 100  | ļ     |  |

| Mininum Reset Pulse     | 1             |      |       |          |      |       |  |

| Width*                  |               | 5    |       | 150      | 300  |       |  |

| twr                     |               | 10   | -     | 100      | 200  |       |  |

|                         | <b> </b>      | 15   | ļ     | 70       | 140  | l ns  |  |

| Reset Propagation Delay |               | 5    | - 1   | 230      | 460  |       |  |

| <sup>t</sup> PRHL       |               | 10   | -     | 90       | 180  |       |  |

|                         | <u> </u>      | 15   | -     | 65       | 130  | I     |  |

| Input Capacitance CIN   | Any Ir        | iput | _     | 5        | 7.5  | pF    |  |

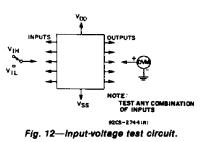

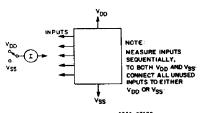

Fig. 13—Input current test circuit.

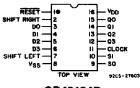

#### **TERMINAL DIAGRAM**

CD40194B

### CD40194B Types

4.5.5

1285

3-442