### **Features**

- Supply voltage up to 40 V

- R<sub>DSon</sub> typ. 0.5 Ω @ 25°C, max. 1Ω @ 150°C

- Up to 1.5 A output current

- Three high-side and three low-side drivers usable as single outputs or half bridges

- Capable to switch all kinds of loads such as DC motors, bulbs, resistors, capacitors and inductors

- PWM capability for each output controlled by external PWM signal

- No crossover current

- Very low quiescent current Is < 10 μA in stand-by mode over total temperature range</li>

- · Outputs short-circuit protected

- Selective overtemperature protection for each switch and overtemperature prewarning

- Undervoltage protection

- Various diagnosis functions such as shorted output, open load, overtemperature and power-supply fail

- Serial data interface, daisy chain capable, up to 2 MHz clock frequency

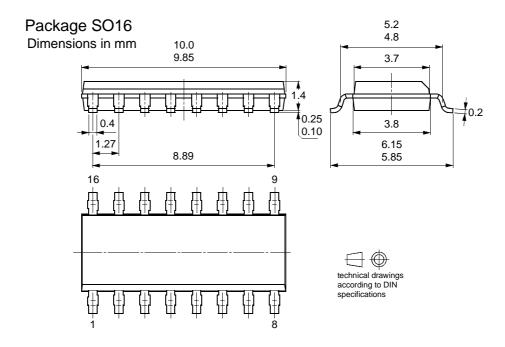

- SO16 power package

T6819 / T6829 are fully protected driver interfaces designed in 0.8 µm BCDMOS technology. It is used to control up to 6 different loads by a microcontroller in automotive and industrial applications.

Each of the 3 high-side and 3 low-side drivers is capable to drive currents up to 1.5 A. Each driver is free configurable and can be controlled separately from a standard serial data interface. Therefore, all kinds of loads such as bulbs, resistors, capacitors and inductors can be combined. The IC design especially supports the applications of H-bridges to drive DC motors. The capability to control each output with an external PWM signal opens additional applications.

Protection is guaranteed in terms of short-circuit conditions, overtemperature and undervoltage. Various diagnosis functions and a very low quiescent current in stand-by mode opens a wide range of applications. Automotive qualification referring to conducted interferences, EMC protection and 2 kV ESD protection give added value and enhanced quality for demanding up-market applications.

## **Ordering Information**

| Extended Type Number | Package | Remarks                                        |

|----------------------|---------|------------------------------------------------|

| T6819-TBS            | SO16    | Power package, tubed                           |

| T6819-TBQ            | SO16    | Power package, taped and reeled                |

| T6829-TBS            | SO16    | Power package with heat slug, tubed            |

| T6829-TBQ            | SO16    | Power package with heat slug, taped and reeled |

Dual Triple

DMOS Output

Driver with

Serial Input

Control

T6819 T6829

Rev. A1, 12-Nov-01

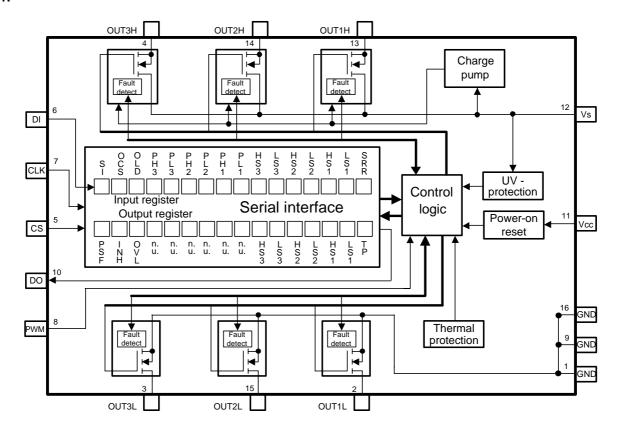

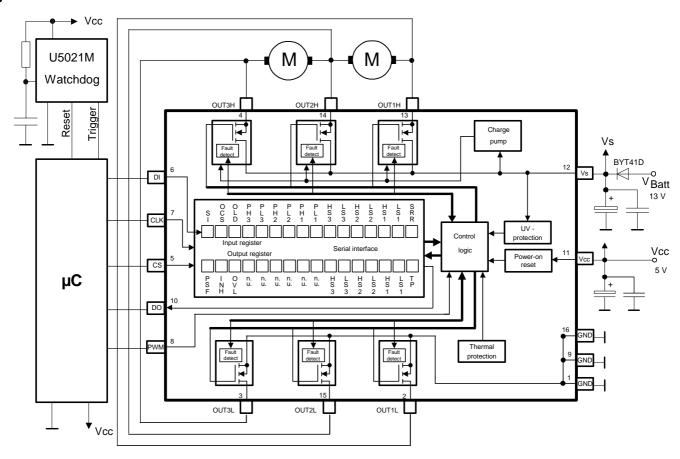

## **Block Diagram**

Figure 1.

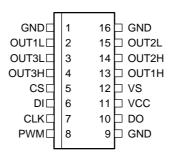

# **Pin Configuration**

Figure 2.

## **Pin Description**

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                     |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND    | T6819: Ground; reference potential; internal connection to Pin 9 and Pin 16; cooling tab T6829: Additional connection to heat slug                                                                                                                                                                           |

| 2   | OUT1L  | Low-side driver output 1; Power-MOS open drain with internal reverse diode; short-circuit protection; overtemperature protection; diagnosis for short and open load; PWM ability                                                                                                                             |

| 3   | OUT3L  | Low-side driver output 3; see Pin 2                                                                                                                                                                                                                                                                          |

| 4   | OUT3H  | High-side driver output 3; Power-MOS open source with internal reverse diode; short-circuit protection; overtemperature protection; diagnosis for short and open load; PWM ability                                                                                                                           |

| 5   | CS     | Chip select input; 5-V CMOS logic level input with internal pull up; low = serial communication is enabled, high = disabled                                                                                                                                                                                  |

| 6   | DI     | Serial data input; 5-V CMOS logic level input with internal pull down; receives serial data from the control device; DI expects a 16-bit control word with LSB being transferred first                                                                                                                       |

| 7   | CLK    | Serial clock input; 5-V CMOS logic level input with internal pull down; controls serial data input interface and internal shift register (f <sub>max</sub> = 2 MHz)                                                                                                                                          |

| 8   | PWM    | PWM input; 5-V CMOS logic level input with internal pull down; receives PWM signal to control outputs which are selected for PWM mode by the serial data interface                                                                                                                                           |

| 9   | GND    | Ground; see Pin 1                                                                                                                                                                                                                                                                                            |

| 10  | DO     | Serial data output; 5-V CMOS logic-level tristate output for output (status) register data; sends 16-bit status information to the $\mu$ C (LSB is transferred first); output will remain tristated, unless device is selected by CS = low, therefore, several ICs can operate on one data-output line only. |

| 11  | VCC    | Logic supply voltage (5 V)                                                                                                                                                                                                                                                                                   |

| 12  | VS     | Power supply for high-side output stages OUT1H, OUT2H, OUT3H, internal supply                                                                                                                                                                                                                                |

| 13  | OUT1H  | High-side driver output 3; see PIN 4                                                                                                                                                                                                                                                                         |

| 14  | OUT2H  | High-side driver output 2; see PIN 4                                                                                                                                                                                                                                                                         |

| 15  | OUT2L  | Low-side driver output 2; see Pin 2                                                                                                                                                                                                                                                                          |

| 16  | GND    | Ground; see Pin 1                                                                                                                                                                                                                                                                                            |

## **Functional Description**

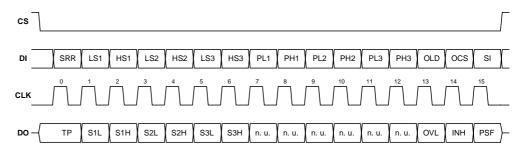

#### **Serial Interface**

Data transfer starts with the falling edge of the CS signal. Data must appear at DI synchronized to CLK and are accepted on the falling edge of the CLK signal. LSB (bit 0, SRR) has to be transferred first. Execution of new input data is enabled on the rising edge of the CS signal. When CS is high, Pin DO is in tristate condition. This output is enabled on the falling edge of CS. Output data will change their state with the rising edge of CLK and stay stable until the next rising edge of CLK appears. LSB (bit 0, TP) is transferred first.

Figure 3. Data transfer

### **Input Data Protocol**

| Bit | Input Register | Function                                                                                                                                                 |

|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | SRR            | Status register reset (high = reset; the bits PSF and OVL in the output data register are set to low)                                                    |

| 1   | LS1            | Controls output LS1 (high = switch output LS1 on)                                                                                                        |

| 2   | HS1            | Controls output HS1 (high = switch output HS1 on)                                                                                                        |

| 3   | LS2            | See LS1                                                                                                                                                  |

| 4   | HS2            | See HS1                                                                                                                                                  |

| 5   | LS3            | See LS1                                                                                                                                                  |

| 6   | HS3            | See HS1                                                                                                                                                  |

| 7   | PL1            | Output LS1 additionally controlled by PWM Input                                                                                                          |

| 8   | PH1            | Output HS1 additionally controlled by PWM Input                                                                                                          |

| 9   | PL2            | See PL1                                                                                                                                                  |

| 10  | PH2            | See PH1                                                                                                                                                  |

| 11  | PL3            | See PL1                                                                                                                                                  |

| 12  | PH3            | See PH1                                                                                                                                                  |

| 13  | OLD            | Open load detection (low = on)                                                                                                                           |

| 14  | ocs            | Overcurrent shutdown (high = overcurrent shutdown is active)                                                                                             |

| 15  | SI             | Software inhibit; low = stand by, high = normal operation (data transfer is not affected by stand by function because the digital part is still powered) |

4 (16)

### **Output Data Protocol**

| Bit | Output (Status)<br>Register | Function                                                                                                                                                                                                                    |

|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TP                          | Temperature prewarning: high = warning                                                                                                                                                                                      |

| 1   | Status LS1                  | Normal operation: high = output is on, low = output is off Open load detection: high = open load, low = no open load (correct load condition is detected if the corresponding output is switched off); not affected by SRR  |

| 2   | Status HS1                  | Normal operation: high = output is on, low = output is off Open load detection: high = open load, low = no open load (correct load condition is detected if the corresponding output is switched off); not affected by SRR  |

| 3   | Status LS2                  | Description see LS1                                                                                                                                                                                                         |

| 4   | Status HS2                  | Description see HS1                                                                                                                                                                                                         |

| 5   | Status LS3                  | Description see LS1                                                                                                                                                                                                         |

| 6   | Status HS3                  | Description see HS1                                                                                                                                                                                                         |

| 7   | n. u.                       | Not used                                                                                                                                                                                                                    |

| 8   | n. u.                       | Not used                                                                                                                                                                                                                    |

| 9   | n. u.                       | Not used                                                                                                                                                                                                                    |

| 10  | n. u.                       | Not used                                                                                                                                                                                                                    |

| 11  | n. u.                       | Not used                                                                                                                                                                                                                    |

| 12  | n. u.                       | Not used                                                                                                                                                                                                                    |

| 13  | OVL                         | Overload detected: set high, when at least one output is switched off by a short circuit condition or an overtemperature event. Bits 1 to 6 can be used to detect the affected switch. (open-load detection bit OLD = high) |

| 14  | INH                         | Inhibit: this bit is controlled by software (bit SI in input register) High = standby, low = normal operation                                                                                                               |

| 15  | PSF                         | Power-supply fail: undervoltage at Pin VS detected                                                                                                                                                                          |

After power-on reset, the input register has the following status

|   | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | SI     | OCS    | OLD    | PH3    | PL3    | PH2    | PL2   | PH1   | PL1   | HS3   | LS3   | HS2   | LS2   | HS1   | LS1   | SRR   |

| Ī | Н      | Н      | Н      | L      | L      | L      | L     | L     | L     | L     | L     | L     | L     | L     | L     | L     |

### **Power-Supply Fail**

In case of undervoltage at Pin VS the power-supply fail bit (PSF) in the output register is set and all outputs are disabled. An undervoltage condition is only detected if it occurs over the undervoltage detection delay time  $t_{\text{dUV}}$ . After the undervoltage occurred the outputs are enabled immediately. The PSF bit keeps high until it is reset by the SRR bit in the input register.

### **Open-Load Detection**

f the open-load detection bit (OLD) is set to low, a pull-up current for each high-side switch and a pull-down current for each low-side switch is turned on (open-load detec-

tion current I<sub>HS1-3</sub>, I<sub>LS1-3</sub>). If the current through a high-side or low-side switch in ON-state does not reach the open-load detection threshold, the corresponding bit of the output in the output register is set to high.

Switching on an output stage with OLD bit set to low disables the open-load function for this output.

# Overtemperature Protection

If the junction temperature at one ore more switches exceeds the thermal prewarning threshold  $T_{jPW\,set}$ , the temperature prewarning bit (TP) in the output register is set. When temperature falls below the thermal prewarning threshold  $T_{jPW\,reset}$ , the Bit TP is reset. The TP bit can be read without transferring a complete 16-bit data word: with CS = high to low the state of TP appears at Pin DO. After the  $\mu$ C has read this information CS is set high and the data transfer is interrupted without affecting the state of input and output registers.

If the junction temperature at a switch exceeds the thermal shutdown threshold  $T_{j \text{ switch off}}$ , the affected output is disabled and the corresponding bit in the output register is set to low. Additional the overload detection bit (OVL) in the output register is set. The output can be enabled again when the temperature falls below the thermal shutdown threshold  $T_{j \text{ switch on}}$  and writing a high to the SRR bit in the input register. Thermal prewarning and shutdown threshold have hysteresis.

### **Short-Circuit Protection**

The output currents are limited by a current regulator. If the overcurrent shutdown bit (OCS) in the input register is set, the affected output is switched off after a short delay time ( $t_{dSd}$ ) when the current exceeds the overcurrent limitation and shutdown threshold. In this case the overload detection bit (OVL) is set and the corresponding status bit in the output register is set to low. For OCS = low the overcurrent shutdown is inactive and the OVL bit is not set by an overcurrent. By writing a high to the SRR bit in the input register the OVL bit is reset and the disabled outputs are enabled.

### **Inhibit**

To inhibit the T6819 / T6829 the INH bit in the input register must be set to zero.

In this case all output stages are turned off but the serial interface stays active. The current consumption is reduced to less than 10  $\mu$ A out of V<sub>S</sub> and less than 20  $\mu$ A out of V<sub>CC</sub>. The output stages can be activated again by bit SI = 1.

## **Absolute Maximum Ratings**

All values refer to GND pins

| Parameter                                    |                                              | Symbol                                                                                                                       | Value                                      | Unit |

|----------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|

| Supply voltage                               | Pin 12                                       | V <sub>VS</sub>                                                                                                              | -0.3 to 40                                 | V    |

| Supply voltage t<0.5s; IS>-2A                | Pin 12                                       | V <sub>VS</sub>                                                                                                              | -1                                         | V    |

| Logic supply voltage                         | Pin 11                                       | V <sub>vcc</sub>                                                                                                             | -0.3 to 7                                  | V    |

| Logic input voltage                          | Pins 5to 8                                   | $V_{CS}, V_{DI}, V_{CLK}, V_{PWM}$                                                                                           | -0.3 to V <sub>VCC</sub> +0.3              | V    |

| Logic output voltage                         | Pin 10                                       | V <sub>DO</sub>                                                                                                              | -0.3 to V <sub>VCC</sub> +0.3              | V    |

| Input current                                | Pins 5to 8                                   | I <sub>CS</sub> ,I <sub>DI</sub> , I <sub>CLK</sub> , I <sub>PWM</sub>                                                       | -10 to +10                                 | mA   |

| Output current                               | Pin 10                                       | I <sub>DO</sub>                                                                                                              | -10 to +10                                 | mA   |

| Output current                               | Pins 2 to 4<br>and 13 to 15                  | I <sub>Out3H</sub> , I <sub>Out2H</sub> , I <sub>Out1H</sub> I <sub>Out3L</sub> , I <sub>Out2L</sub> , I <sub>Out1L</sub>    | Internal limited, see output specification |      |

| Reverse conducting current (tpulse = 150 µs) | Pins 2 to 4<br>and 13 to 15<br>towards Pin 3 | I <sub>Out3H</sub> , I <sub>Out2H</sub> , I <sub>Out1H</sub><br>I <sub>Out3L</sub> , I <sub>Out2L</sub> , I <sub>Out1L</sub> | 17                                         | А    |

| Junction-temperature range                   |                                              | T <sub>J</sub>                                                                                                               | -40 to 150                                 | °C   |

| Storage-temperature range                    |                                              | T <sub>STG</sub>                                                                                                             | -55 to 150                                 | °C   |

## **Thermal Resistance**

| Parameter          | Test Conditions                             | Symbol            | Value | Unit |

|--------------------|---------------------------------------------|-------------------|-------|------|

| T6819              |                                             | ·                 |       |      |

| Junction – pin     | Measured to GND<br>Pins 1, 9, 16            | R <sub>thJP</sub> | 30    | K/W  |

| Junction – ambient |                                             | R <sub>thJA</sub> | 65    | K/W  |

| T6829              |                                             | <u>.</u>          |       |      |

| Junction – pin     | Measured to heat slug, GND<br>Pins 1, 9, 16 | R <sub>thJP</sub> | 5     | K/W  |

| Junction – ambient |                                             | R <sub>thJA</sub> | 30    | K/W  |

# **Operating Range**

| Parameter                        | Symbol                                                                  | Value                    | Unit |

|----------------------------------|-------------------------------------------------------------------------|--------------------------|------|

| Supply voltage                   | V <sub>VS</sub>                                                         | V <sub>UV</sub> 1) to 40 | V    |

| Logic supply voltage             | V <sub>VCC</sub>                                                        | 4.75 to 5.25             | V    |

| Logic input voltage              | V <sub>CS</sub> , V <sub>DI</sub> , V <sub>CLK</sub> , V <sub>PVM</sub> | -0.3 to $V_{\text{VCC}}$ | V    |

| Serial interface clock frequency | f <sub>CLK</sub>                                                        | 2                        | MHz  |

| PWM input frequency              | f <sub>PWM</sub>                                                        | 1                        | kHz  |

| Junction-temperature range       | T <sub>j</sub>                                                          | -40 to 150               | °C   |

Note: 1. Threshold for undervoltage detection

# **Noise and Surge Immunity**

| Parameter                | Test Conditions | Value      |

|--------------------------|-----------------|------------|

| Conducted interferences  | ISO 7637-1      | Level 4 1) |

| Interference suppression | VDE 0879 Part 3 | Level 6    |

| ESD (Human Body Model)   | ESD S 5.1       | 2 kV       |

| ESD (Machine Model)      | JEDEC A115A     | 200 V      |

## **Electrical Characteristics**

$7.5~V < V_S < 40~V$ ;  $4.75~V < V_{CC} < 5.25~V$ ; INH = High;  $-40^{\circ}C < Tj < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No. | Parameters                            | Test Conditions                                                                | Pin        | Symbol                            | Min.        | Тур.       | Max.       | Unit     | Type* |

|-----|---------------------------------------|--------------------------------------------------------------------------------|------------|-----------------------------------|-------------|------------|------------|----------|-------|

| 1   | <b>Current Consumption</b>            |                                                                                |            |                                   |             |            |            |          |       |

| 1.1 | Quiescent current (VS)                | V <sub>VS</sub> < 16 V,<br>SI = low                                            | 12         | I <sub>VS</sub>                   |             | 1          | 5          | μA       | А     |

| 1.2 | Quiescent current (VCC)               | 4.75 V < V <sub>VCC</sub> < 5.25 V, SI = low                                   | 11         | I <sub>vcc</sub>                  |             | 60         | 100        | μA       | А     |

| 1.3 | Supply current (VS)                   | V <sub>VS</sub> < 16 V<br>normal operating, one<br>output stage on, no<br>load | 12         | I <sub>VS</sub>                   |             | 6          | 10         | mA       | А     |

| 1.4 | Supply current (VCC)                  | 4.75 V < V <sub>VCC</sub> < 5.25 V, normal operating                           | 11         | I <sub>vcc</sub>                  |             | 350        | 600        | μА       | А     |

| 2   | Undervoltage Detection                | on, Power-On Reset                                                             |            |                                   |             |            |            |          |       |

| 2.1 | Power-on reset threshold              |                                                                                | 11         | V <sub>VCC</sub>                  | 3.4         | 3.9        | 4.4        | V        | А     |

| 2.2 | Power-on reset delay time             | After switching on V <sub>CC</sub>                                             |            | t <sub>dPor</sub>                 | 30          | 95         | 160        | μs       | А     |

| 2.3 | Undervoltage-<br>detection threshold  | V <sub>CC</sub> = 5 V                                                          | 12         | V <sub>Uv</sub>                   | 5.5         |            | 7.0        | V        | А     |

| 2.4 | Undervoltage-<br>detection hysteresis | V <sub>CC</sub> = 5 V                                                          | 12         | $\Delta V_{Uv}$                   |             | 0.6        |            | V        | А     |

| 2.5 | Undervoltage-<br>detection delay time |                                                                                |            | t <sub>dUV</sub>                  | 10          |            | 40         | μs       | А     |

| 3   | Thermal Prewarning a                  | and Shutdown                                                                   |            |                                   |             |            |            |          |       |

| 3.1 | Thermal prewarning                    |                                                                                |            | T <sub>jPW set</sub>              | 120         | 145        | 170        | °C       | В     |

| 3.2 | Thermal prewarning                    |                                                                                |            | T <sub>jPW reset</sub>            | 105         | 130        | 155        | °C       | В     |

| 3.3 | Thermal prewarning hysteresis         |                                                                                |            | ΔT <sub>jPW</sub>                 |             | 15         |            | К        | В     |

| 3.4 | Thermal shutdown                      |                                                                                |            | T <sub>j switch off</sub>         | 150         | 175        | 200        | °C       | В     |

| 3.5 | Thermal shutdown                      |                                                                                |            | T <sub>j switch on</sub>          | 135         | 160        | 185        | °C       | В     |

| 3.6 | Thermal shutdown hysteresis           |                                                                                |            | $\Delta T_{j \text{ switch off}}$ |             | 15         |            | К        | В     |

|     | *) Type means: A =100%                | 6 tested, B = 100% correl                                                      | ation test | ted, C = Chara                    | cterized or | n samples, | D = Desigr | paramete | r     |

## **Electrical Characteristics**

$7.5~V < V_S < 40~V$ ;  $4.75~V < V_{CC} < 5.25~V$ ; INH = High;  $-40^{\circ}C < Tj < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No.  | Parameters                                           | Test Conditions                                           | Pin          | Symbol                                               | Min. | Тур. | Max. | Unit | Type |

|------|------------------------------------------------------|-----------------------------------------------------------|--------------|------------------------------------------------------|------|------|------|------|------|

| 3.7  | Ratio thermal<br>shutdown / thermal<br>prewarning    |                                                           |              | T <sub>j switch off /</sub><br>T <sub>jPW set</sub>  | 1.05 | 1.2  |      |      | В    |

| 3.8  | Ratio thermal<br>shutdown / thermal<br>prewarning    |                                                           |              | T <sub>j</sub> switch on /<br>T <sub>jPW reset</sub> | 1.05 | 1.2  |      |      | В    |

| 4    | Output Specification                                 | (OUT1-OUT3)                                               |              |                                                      |      |      |      |      |      |

| 4.1  | On resistance                                        | I <sub>Out</sub> = 1.5 A                                  | 2, 3,<br>15  | R <sub>DS On L</sub>                                 |      |      | 1    | W    | А    |

| 4.2  | On resistance                                        | I <sub>Out</sub> = -1.5 A                                 | 4, 13,<br>14 | R <sub>DS On H</sub>                                 |      |      | 1    | W    | А    |

| 4.3  | Source output leakage current                        | V <sub>Out1-3</sub> = 0 V <sub>,</sub> output stages off  | 4, 13,<br>14 | I <sub>Out1-3</sub>                                  | -5   |      |      | μA   | А    |

| 4.4  | Sink output leakage current                          | V <sub>Out1-3</sub> = V <sub>VS</sub> , output stages off | 2, 3,<br>15  | I <sub>Out1-3</sub>                                  |      |      | 5    | μA   | А    |

| 4.5  | High-side switch reverse diode forward voltage       | I <sub>Out</sub> = 1.5 A                                  | 4, 13,<br>14 | V <sub>Out1-3-</sub> V <sub>VS</sub>                 |      |      | 1.3  | V    | А    |

| 4.6  | Low-side switch reverse diode forward voltage        | I <sub>Out</sub> = -1.5 A                                 | 2, 3,<br>15  | V <sub>Out1-3</sub>                                  |      |      | 1.3  | V    | А    |

| 4.7  | Source overcurrent limitation and shutdown threshold |                                                           | 4, 13,<br>14 | I <sub>Out1-3</sub>                                  | -2.5 | -2   | -1.5 | А    | А    |

| 4.8  | Sink overcurrent limitation and shutdown threshold   |                                                           | 2, 3,<br>15  | I <sub>Out1-3</sub>                                  | 1.5  | 2    | 2.5  | А    | А    |

| 4.9  | Overcurrent shutdown delay time                      |                                                           |              | t <sub>dSd</sub>                                     | 10   |      | 40   | μs   | А    |

| 4.10 | Source open load detection current                   | Input register bit 13 (OLD) = low, output off             | 4, 13,<br>14 | I <sub>Out1-3</sub>                                  | -4   | -2   |      | mA   | А    |

| 4.11 | Sink open load detection current                     | Input register bit 13 (OLD) = low, output off             | 2, 3,<br>15  | I <sub>Out1-3</sub>                                  |      | 2    | 4    | mA   | А    |

| 4.12 | Source output switch on delay 1)                     | $V_{VS} = 13 \text{ V},$<br>RLoad=30 $\Omega$             |              | t <sub>don</sub>                                     |      | 5    | 15   | μs   | А    |

| 4.13 | Sink output switch on delay 1)                       | $V_{VS} = 13 \text{ V},$ $R_{Load} = 30 \Omega$           |              | t <sub>don</sub>                                     |      | 15   | 25   | μs   | А    |

| 4.14 | Source output switch off delay 1)                    | $V_{VS} = 13V$ , $R_{Load} = 30 \Omega$                   |              | t <sub>doff</sub>                                    |      | 5    | 15   | μs   | А    |

| 4.15 | Sink output switch off delay 1)                      | $V_{VS} = 13V$ , $R_{Load} = 30 \Omega$                   |              | t <sub>doff</sub>                                    |      | 1    | 2    | μs   | А    |

## **Electrical Characteristics**

$7.5~V < V_S < 40~V$ ;  $4.75~V < V_{CC} < 5.25~V$ ; INH = High;  $-40^{\circ}C < Tj < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No.  | Parameters                                                                                                     | Test Conditions                            | Pin       | Symbol                              | Min.                       | Тур. | Max.                      | Unit | Type* |  |  |

|------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------|-------------------------------------|----------------------------|------|---------------------------|------|-------|--|--|

| 4.16 | Dead time between corresponding high-and low-side switches                                                     | $V_{VS}$ =13V,<br>$R_{Load}$ = 30 $\Omega$ |           | t <sub>don</sub> -t <sub>doff</sub> | 1                          |      |                           | μs   | А     |  |  |

| 5    | Logic Inputs DI, CLK,                                                                                          | CS, PWM                                    |           |                                     |                            |      |                           |      |       |  |  |

| 5.1  | Input voltage low - evel threshold                                                                             |                                            | 5-8       | V <sub>IL</sub>                     | 0.3 ×<br>V <sub>VCC</sub>  |      |                           | V    | А     |  |  |

| 5.2  | Input voltage high-<br>level threshold                                                                         |                                            | 5-8       | $V_{IH}$                            |                            |      | 0.7 ×<br>V <sub>VCC</sub> | V    | А     |  |  |

| 5.3  | Hysteresis of input voltage                                                                                    |                                            | 5-7       | $\Delta V_{I}$                      | 50                         |      | 500                       | mV   | А     |  |  |

| 5.4  | Pull-down current<br>Pins DI, CLK, PWM                                                                         | $V_{DI}, V_{CLK}, V_{PWM} = V_{CC}$        | 6, 7,8    | I <sub>PD</sub>                     | 10                         |      | 60                        | μA   | А     |  |  |

| 5.5  | Pull-up current<br>Pin CS                                                                                      | V <sub>CS</sub> = 0 V                      | 5         | I <sub>PU</sub>                     | -50                        |      | -10                       | μA   | А     |  |  |

| 5.6  | Hysteresis of input voltage                                                                                    |                                            | 8         | $\Delta V_{I}$                      | 50                         |      | 700                       | mV   | А     |  |  |

| 6    | Serial Interface – Logi                                                                                        | ic Output DO                               |           |                                     |                            |      |                           |      |       |  |  |

| 6.1  | Output-voltage low level                                                                                       | I <sub>OL</sub> = 2mA                      | Pin<br>10 | $V_{DOL}$                           |                            |      | 0.4                       | V    | А     |  |  |

| 6.2  | Output-voltage high level                                                                                      | I <sub>OL</sub> = -2mA                     | Pin<br>10 | $V_{DOH}$                           | V <sub>VCC</sub> -<br>0.7V |      |                           | V    | А     |  |  |

| 6.3  | Leakage current (tristate)                                                                                     | $V_{CS} = V_{CC}$ $0V < V_{DO} < V_{VCC}$  | Pin<br>10 | I <sub>DO</sub>                     | -10                        |      | 10                        | μA   | А     |  |  |

| 7    | Inhibit Input – Timing                                                                                         |                                            |           |                                     |                            |      |                           |      |       |  |  |

| 7.1  | Stand-by setup time                                                                                            |                                            |           | t <sub>INHSethl</sub>               |                            |      | 100                       | μs   | Α     |  |  |

| 8.2  | Stand-by setup time                                                                                            |                                            |           | t <sub>INHSetlh</sub>               |                            |      | 100                       | μs   | А     |  |  |

|      | *) Type means: A =100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter |                                            |           |                                     |                            |      |                           |      |       |  |  |

Note: 1. Delay time between rising edge of CS after data transmission and switch on output stages to 90% of final level. Device not in stand-by for t >1ms

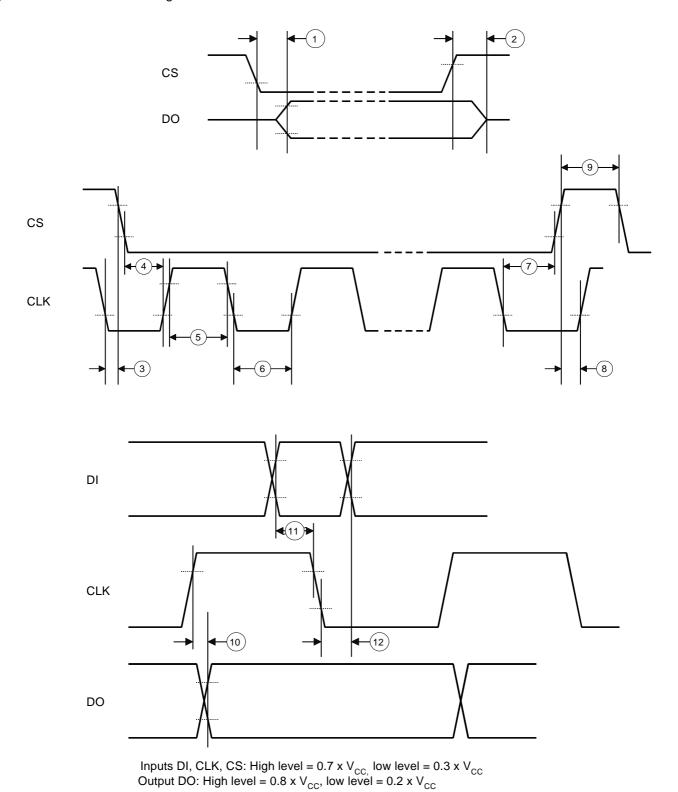

## **Serial Interface – Timing**

| Parameters                      | Test<br>Conditions       | Timing<br>Chart No. | Symbol                | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------------------|---------------------|-----------------------|------|------|------|------|

| DO enable after CS falling edge | C <sub>DO</sub> = 100 pF | 1                   | t <sub>ENDO</sub>     |      |      | 200  | ns   |

| DO disable after CS rising edge | C <sub>DO</sub> = 100 pF | 2                   | t <sub>DISDO</sub>    |      |      | 200  | ns   |

| DO fall time                    | C <sub>DO</sub> = 100 pF | -                   | t <sub>DOf</sub>      |      |      | 100  | ns   |

| DO rise time                    | C <sub>DO</sub> = 100 pF | -                   | t <sub>DOr</sub>      |      |      | 100  | ns   |

| DO valid time                   | C <sub>DO</sub> = 100 pF | 10                  | t <sub>DOVal</sub>    |      |      | 200  | ns   |

| CS setup time                   |                          | 4                   | t <sub>CSSethl</sub>  | 225  |      |      | ns   |

| CS setup time                   |                          | 8                   | t <sub>CSSetIh</sub>  | 225  |      |      | ns   |

| CS high time                    |                          | 9                   | t <sub>CSh</sub>      | 500  |      |      | ns   |

| CLK high time                   |                          | 5                   | t <sub>CLKh</sub>     | 225  |      |      | ns   |

| CLK low time                    |                          | 6                   | t <sub>CLKI</sub>     | 225  |      |      | ns   |

| CLK period time                 |                          | -                   | t <sub>CLKp</sub>     | 500  |      |      | ns   |

| CLK setup time                  |                          | 7                   | t <sub>CLKSethI</sub> | 225  |      |      | ns   |

| CLK setup time                  |                          | 3                   | t <sub>CLKSetlh</sub> | 225  |      |      | ns   |

| DI setup time                   |                          | 11                  | t <sub>Diset</sub>    | 40   |      |      | ns   |

| DI hold time                    |                          | 12                  | t <sub>DIHold</sub>   | 40   |      |      | ns   |

Figure 4. Serial interface timing with chart number

## **Application Circuit**

Figure 5.

### **Application Notes**

It is strongly recommended to connect the blocking capacitors at  $V_{CC}$  and  $V_{S}$  as close as possible to the power supply and GND pins.

Recommended value for capacitors at V<sub>S</sub>:

Electrolytic capacitor C > 22 µF in parallel with a ceramic capacitor C = 100 nF. Value for electrolytic capacitor depends on external loads, conducted interferences and reverse conducting current I<sub>Outzx</sub> (see Absolute Maximum Ratings).

Recommended value for capacitors at V<sub>CC</sub>:

Electrolytic capacitor C > 10  $\mu$ F in parallel with a ceramic capacitor C = 100 nF.

To reduce thermal resistance it is recommended to place cooling areas on the PCB as close as possible to GND pins.

# **Package Information**

### **Ozone Depleting Substances Policy Statement**

It is the policy of Atmel Germany GmbH to

- 1. Meet all present and future national and international statutory requirements.

- Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**Atmel Germany GmbH** has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**Atmel Germany GmbH** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

### **Atmel Wireless & Microcontrollers Sales Offices**

#### France

3, Avenue du Centre 78054 St.-Quentin-en-Yvelines Cedex

Tel: +33 1 30 60 70 00 Fax: +33 1 30 60 71 11

#### Germany

Erfurter Strasse 31 85386 Eching Tel: +49 89 319 70

Tel: +49 89 319 70 0 Fax: +49 89 319 46 21

#### Kruppstrasse 6 45128 Essen

Tel: +49 201 247 30 0 Fax: +49 201 247 30 47

Theresienstrasse 2 74072 Heilbronn

Tel: +49 7131 67 36 36 Fax: +49 7131 67 31 63

### **Italy**

Via Grosio, 10/8 20151 Milano

Tel: +39 02 38 03 71 Fax: +39 02 38 03 72 34

#### Spain

Principe de Vergara, 112 28002 Madrid

Tel: +34 91 564 51 81 Fax: +34 91 562 75 14

#### Sweden

Kavallerivaegen 24, Rissne 17402 Sundbyberg Tel: +46 8 587 48 800 Fax: +46 8 587 48 850

#### **United Kingdom**

Easthampstead Road Bracknell Berkshire RG12 1LX Tel: +44 1344 707 300 Fax: +44 1344 427 371

#### **USA Western**

2325 Orchard Parkway San Jose, California 95131 Tel: +1 408 441 0311 Fax: +1 408 436 4200

#### **USA Eastern**

1465 Route 31, Fifth floor Annandale New Jersey 08801

Tel: +1 908 848 5208 Fax: +1 908 848 5232

### **Hong Kong**

Room #1219, Chinachem Golden Plaza 77 Mody Road, Tsimhatsui East East Kowloon, Hong Kong Tel: +852 23 789 789

Fax: +852 23 789 789

#### Korea

25-4, Yoido-Dong, Suite 605, Singsong Bldg. Youngdeungpo-Ku 150-010 Seoul

Tel: +822 785 1136 Fax: +822 785 1137

### Rep. of Singapore

Keppel Building #03-00 25 Tampines Street 92, Singapore 528877 Tel: +65 260 8223 Fax: +65 787 9819

### Taiwan, R.O.C.

8F-2, 266 Sec.1 Wen Hwa 2 Rd. Lin Kou Hsiang, 244 Taipei Hsien

Tel: +886 2 2609 5581 Fax: +886 2 2600 2735

#### Japan

Tonetsushinkawa Bldg. 1-24-8 Shinkawa Chuo Ku Tokyo 104-0033

Tel: +81 3 3523 3551 Fax: +81 3 3523 7581

### Web Site

http://www.atmel-wm.com

### © Atmel Germany GmbH 2001.

Atmel Germany GmbH makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel Germany GmbH's Terms and Conditions. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel Germany GmbH are granted by the Company in connection with the sale of AtmelGermany GmbH products, expressly or by implication. Atmel Germany GmbH's products are not authorized for use as critical components in life support devices or systems.

Data sheets can also be retrieved fron the Internet: http://www.atmel-wm.com