# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Nov. 1996

WWW.DZSC

# MSM7557

Single Chip MSK Modem with Compandor for Cordless Telephone

#### **GENERAL DESCRIPTION**

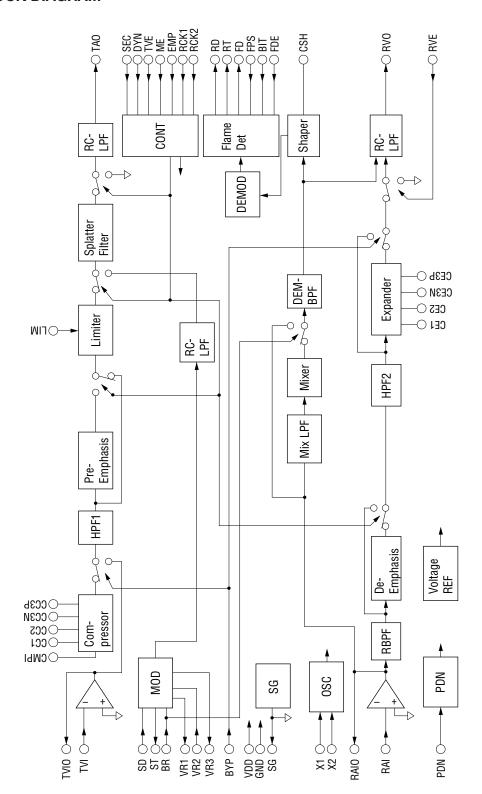

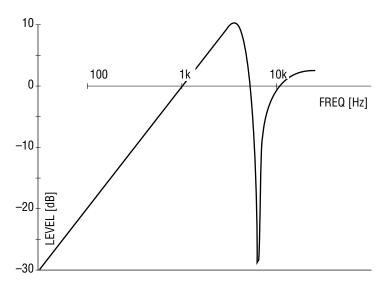

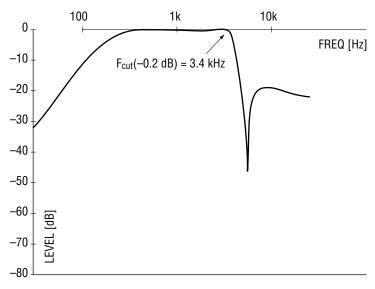

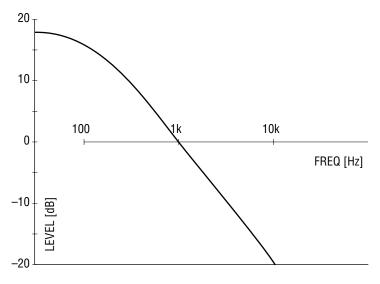

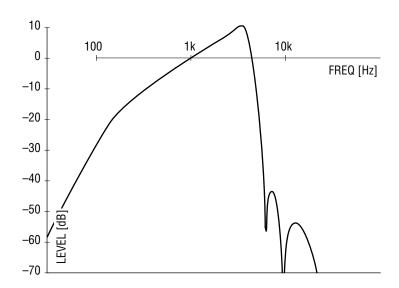

The MSM7557 is a single chip MSK modem with base band voice processor for cordless telephone. The MSM7557 voice transmit block consists of high pass filter, compressor, pre-emphasis, limiter and splatter filter.

W.DZSC.COM

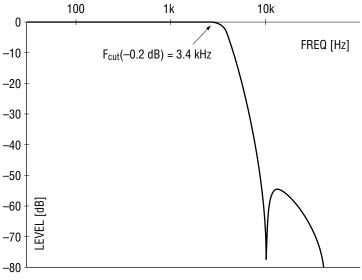

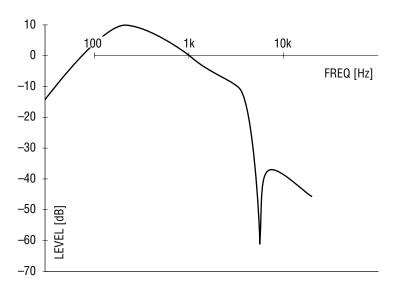

Voice receive block consists of Band pass filter, De-emphasis and Expander.

#### **FEATURES**

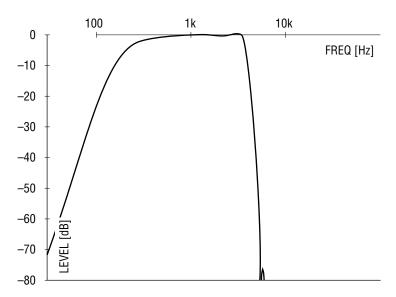

- Available to transmit modem signal and also transmit base band voice signal through wireless transmission path (0.3 kHz to 3.4 kHz)

- Built-in compandor circuit

- Upper limit of voice band (3306 Hz/3400 Hz/3500 Hz) is selectable

- Modem bit rate (2400/1200 bps) is selectable

- Transmit function and receive function operate separately

- Emphasis mode selectable

- Built-in bit synchronous detector and frame synchronous detector

- Built-in limiter level generator and external limit voltage input

- Dynamic range selectable

- Built-in crystal oscillator circuit

- Wide range power supply voltage (2.7V ~ 5.5V)

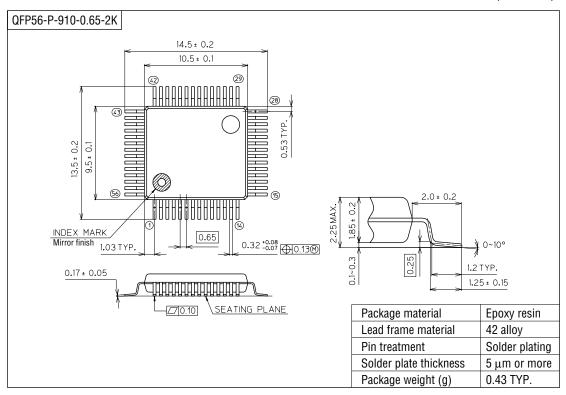

- Package:

56-pin plastic QFP (QFP56-P-910-0.65-2K) (Product name : MSM7557GS-2K)

#### **BLOCK DIAGRAM**

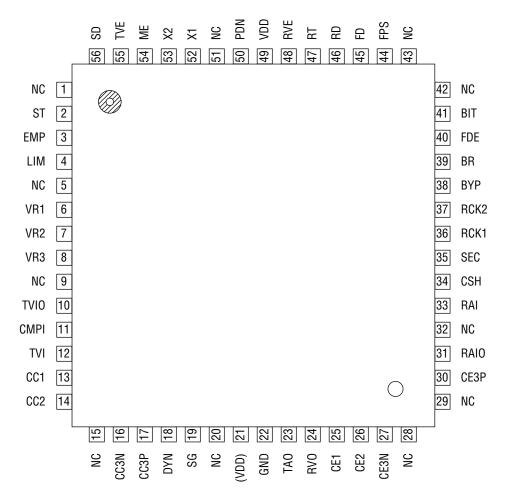

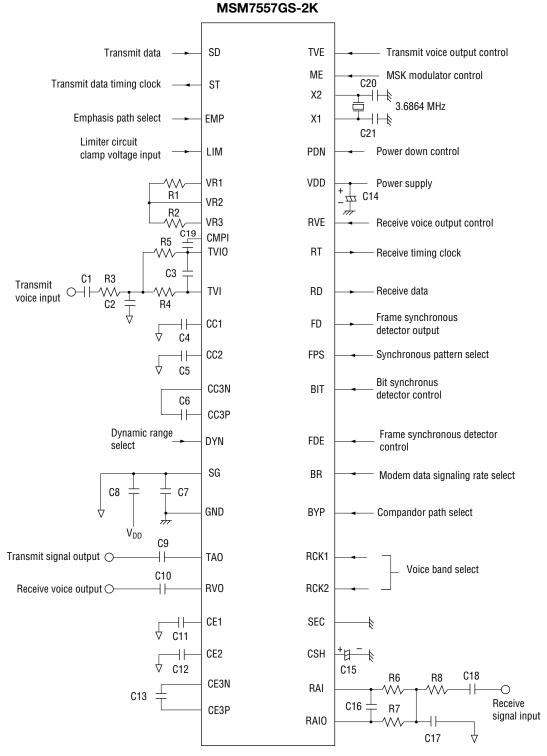

## **PIN CONFIGURATION (TOP VIEW)**

Notes: The pin 49 should be used for V<sub>DD</sub>.

The pin 21 should be connected to V<sub>DD</sub> or opened.

NC: No connect pin

### **PIN DESCRIPTION**

0

| Name |                                                                                            | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | n                                                |  |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|--|

|      |                                                                                            | data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |  |  |  |  |  |  |

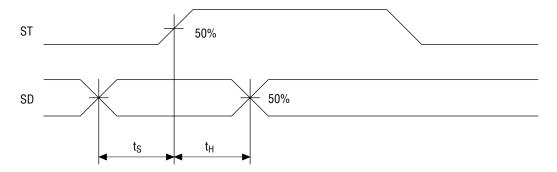

|      | The data                                                                                   | on SD pin are took into MSK modulator and th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ne data are available on the positive edge of ST |  |  |  |  |  |  |

|      |                                                                                            | ME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |  |  |  |  |  |  |

|      | SE                                                                                         | ) input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |  |  |  |  |  |  |

| SD   |                                                                                            | ST The state of th |                                                  |  |  |  |  |  |  |

|      |                                                                                            | lulator<br>t data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                  |  |  |  |  |  |  |

|      | In order to synchronize a receive modem, more than 18bits bit-synchronous signal should be |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |  |  |  |  |  |  |

|      |                                                                                            | transmitted before data transmission. If S/N ratio of the receive signal is always good, more than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |  |  |  |  |  |  |

|      |                                                                                            | 11bits bit-synchronous signal synchronizes the receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                  |  |  |  |  |  |  |

|      |                                                                                            | ta timing clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |  |  |  |  |  |  |

| ST   | When digita                                                                                | I "0" is put on ME pin, ST is fixed to digital "1"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | level.                                           |  |  |  |  |  |  |

|      | Emphasis path selection.                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |  |  |  |  |  |  |

|      | EMP                                                                                        | Transmit side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Receive side                                     |  |  |  |  |  |  |

| EMP  | 0                                                                                          | Pre-emphasis circuit is bypassed to the path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | De-emphasis circuit is bypassed to the path      |  |  |  |  |  |  |

|      |                                                                                            | Dra amphasia sirauit is connected to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | De-emphasis circuit is connected to the          |  |  |  |  |  |  |

|      | 4                                                                                          | Pre-emphasis circuit is connected to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | De-emphasis circuit is confidented to the        |  |  |  |  |  |  |

|      | 1                                                                                          | path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | path                                             |  |  |  |  |  |  |

|      |                                                                                            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | , ·                                              |  |  |  |  |  |  |

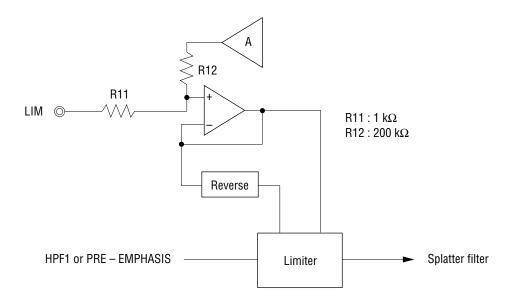

|      | Deviation lir                                                                              | path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | path                                             |  |  |  |  |  |  |

|      | Deviation lir                                                                              | path niter control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | path                                             |  |  |  |  |  |  |

|      | Deviation lir<br>Voice signal<br>this pin.                                                 | path niter control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | path                                             |  |  |  |  |  |  |

|      | Deviation lir<br>Voice signal<br>this pin.<br>Input imped                                  | path niter control. maximum Rf modulation level is controlled b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | path  y connecting external reference voltage to |  |  |  |  |  |  |

| LIM  | Deviation lir<br>Voice signal<br>this pin.<br>Input imped<br>When this p                   | path  niter control.  maximum Rf modulation level is controlled b  ance of this pin is about 200 kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | path  y connecting external reference voltage to |  |  |  |  |  |  |

| LIM  | Deviation lir<br>Voice signal<br>this pin.<br>Input imped<br>When this p                   | path  niter control.  maximum Rf modulation level is controlled b  ance of this pin is about 200 kΩ.  in is left open, internal reference voltage is us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | path  y connecting external reference voltage to |  |  |  |  |  |  |

0.50 V

1.26 V

This internal clamp level is made by internal reference voltage which is unrelated with  $V_{DD}$ . Negative clamp level is made by internal operational amplifier and the voltage is reversed at VSG.

-9 dBV

-1 dBV

| Name              | Description                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                   | Modulator output level control.  Refer to the following figure.                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                   | From modulator $\begin{array}{c c} R1 \geq 40 \ k\Omega \\ R2 \geq 40 \ k\Omega \\ R1 \geq R2 \\ \hline \end{array}$                                                                                                                            |  |  |  |  |  |  |  |

| VR1<br>VR2<br>VR3 | To transmit filter VR2 R2 VR3                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                   | $V_{TAO} = 20 \times log \; (R2/R1) - 9 \; dBV \; (DYN = "0" \; )$ $V_{TAO} = 20 \times log \; (R2/R1) - 1 \; dBV \; (DYN = "1" \; )$ This level is made from internal voltage reference, so this level doesn't depend on power supply voltage. |  |  |  |  |  |  |  |

|                   | Transmit side RC active filter input (TVI) and output (TVIO).  If over 50 kHz frequency element is in the input signal, folding noise is generated from internal SCF circuit, so second order RC-active filter is needed. (fc = 10 kHz)         |  |  |  |  |  |  |  |

| TVIO<br>TVI       | $\begin{array}{c c} C1 & R3 & R5 & \hline TVIO & R5 \geq 60 \text{ k}\Omega \\ \hline C1 & A1 & A2 & A2 & A3 & A3 & A3 & A3 & A3 & A3$                                                                                                          |  |  |  |  |  |  |  |

|                   | SG    SG   SG                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| CC1               | When digital "1" is applied to TVE pin, transmit voice signal comes out to TAO.  Capacitor connection pins to remove for DC offset of the compressor.                                                                                           |  |  |  |  |  |  |  |

| CC2               | A 1 μF capacitor between SG pin and each pin should be connected.                                                                                                                                                                               |  |  |  |  |  |  |  |

| - 002             | Capacitor connection pins for the compressor attack and recovery time.                                                                                                                                                                          |  |  |  |  |  |  |  |

| CC3N              |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| CC3P              | When DYN is digital "0" level, a 0.22 μF capacitor should be connected between CC3N and CC3P.                                                                                                                                                   |  |  |  |  |  |  |  |

|                   | And when DYN is digital "1" level, a 0.47 µF capacitor should be connected between them.                                                                                                                                                        |  |  |  |  |  |  |  |

| Name | Description                                                                                              |                  |                    |                                                                                |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| CMDI | Compressor                                                                                               | r circuit input. |                    |                                                                                |  |  |  |  |  |

| CMPI | Α 0.47 μF ca                                                                                             | apacitor shoul   | d be connected b   | etween CMPI and TVIO.                                                          |  |  |  |  |  |

|      | Dynamic range control input.                                                                             |                  |                    |                                                                                |  |  |  |  |  |

|      | For an application of which $V_{DD}$ is always higher than 4.5 V (Base station), by setting DYN = "1",   |                  |                    |                                                                                |  |  |  |  |  |

|      |                                                                                                          |                  |                    | signal level, limiter clamp level and compandor                                |  |  |  |  |  |

| DYN  |                                                                                                          |                  |                    | nprove S/N ratio.                                                              |  |  |  |  |  |

|      |                                                                                                          |                  |                    | an 4.5 V (Hand-set) DYN shall be digital "0".                                  |  |  |  |  |  |

|      |                                                                                                          |                  | with the RF part,  | one solution is to put digital "0" on DYN pin for both Base                    |  |  |  |  |  |

|      | station and                                                                                              |                  |                    |                                                                                |  |  |  |  |  |

| 00   |                                                                                                          |                  |                    | age is half of V <sub>DD</sub> .                                               |  |  |  |  |  |

| SG   |                                                                                                          | -                |                    | wer and to ensure the device performance, it is necessary to                   |  |  |  |  |  |

| GND  |                                                                                                          | -                | more man iµr b     | etween SG and $\ensuremath{V_{DD}}$ in close physical proximity to the device. |  |  |  |  |  |

| GND  | Ground pin,                                                                                              | . ,              | ıta ut             |                                                                                |  |  |  |  |  |

|      | Transmit analog signal output.  According to control data on ME and TVE, TAO is set as follows.          |                  |                    |                                                                                |  |  |  |  |  |

|      | ME TVE TAO                                                                                               |                  |                    |                                                                                |  |  |  |  |  |

| TAO  | -                                                                                                        |                  |                    | No signal output (potential = SG)                                              |  |  |  |  |  |

| 1710 | =                                                                                                        | 0                | 0                  |                                                                                |  |  |  |  |  |

|      | -                                                                                                        | 0<br>1           | 1<br>X             | Voice signal output  MSK modulator output                                      |  |  |  |  |  |

|      | -                                                                                                        | ı                | Λ                  | X : Don't care                                                                 |  |  |  |  |  |

|      | ъ                                                                                                        |                  |                    |                                                                                |  |  |  |  |  |

|      | Receive voice signal output.                                                                             |                  |                    |                                                                                |  |  |  |  |  |

|      | RVO pin state is defined by RVE control.                                                                 |                  |                    |                                                                                |  |  |  |  |  |

| RV0  |                                                                                                          | RVE              |                    | RVO                                                                            |  |  |  |  |  |

|      | _                                                                                                        | 0                | Output disable     | (potential = SG)                                                               |  |  |  |  |  |

|      |                                                                                                          | 1                | Output enable      |                                                                                |  |  |  |  |  |

|      |                                                                                                          |                  |                    |                                                                                |  |  |  |  |  |

| CE1  | Capacitor co                                                                                             | onnection pins   | s to remove DC o   | ffset of the expander.                                                         |  |  |  |  |  |

| CE2  | A 1 μF capa                                                                                              | citor between    | SG pin and each    | pin should be connected.                                                       |  |  |  |  |  |

| CE3N | -                                                                                                        |                  | -                  | r attack time and recovery time.                                               |  |  |  |  |  |

| CE3P | When DYN is digital "0" level, a 0.22 $\mu\text{F}$ capacitor should be connected between CE3N and CE3P. |                  |                    |                                                                                |  |  |  |  |  |

|      | And when DYN is digital "1" level, a 0.47 μF capacitor should be connected between them.                 |                  |                    |                                                                                |  |  |  |  |  |

| RAI0 |                                                                                                          |                  | ut (RAI) and outp  |                                                                                |  |  |  |  |  |

| RAI  | Second order RC-active filter is needed like TVIO and TVI.  Refer to TVIO and TVI pin description.       |                  |                    |                                                                                |  |  |  |  |  |

|      |                                                                                                          |                  | -                  | set of the modem shaper circuit.                                               |  |  |  |  |  |

| CSH  |                                                                                                          |                  |                    | veen GND pin and CSH.                                                          |  |  |  |  |  |

|      | λιμι σαμα                                                                                                | ortor ortoutu b  | 5 50111100100 DGIV | voon area piir and oori.                                                       |  |  |  |  |  |

| Name         |                                                   | Function        |                    |                     |                                    |                               |  |  |  |  |  |

|--------------|---------------------------------------------------|-----------------|--------------------|---------------------|------------------------------------|-------------------------------|--|--|--|--|--|

| SEC          | Device test input. SEC shall be connected to GND. |                 |                    |                     |                                    |                               |  |  |  |  |  |

|              | Voice band sel                                    | ect.            |                    |                     |                                    |                               |  |  |  |  |  |

| DOIG         | _                                                 | RCK1            | I RCK2 Upper Limit |                     | imit of \                          | /oice Band                    |  |  |  |  |  |

| RCK1<br>RCK2 | _                                                 | 0               | 1                  |                     | 3306 H                             | Iz                            |  |  |  |  |  |

| NUK2         | _                                                 | Х               | 0                  |                     | 3400 H                             | lz                            |  |  |  |  |  |

|              | _                                                 | 1               | 1                  |                     | 3500 H                             | Iz                            |  |  |  |  |  |

|              | Compandor pa                                      | ath selection.  |                    |                     |                                    |                               |  |  |  |  |  |

|              | ВҮР                                               |                 | Transmi            | t side              | Receive side                       |                               |  |  |  |  |  |

| BYP          | 0                                                 | Compress        | or is conn         | ected to the path.  | Expander is connected to the path. |                               |  |  |  |  |  |

|              | 1                                                 | Compress        | or is bypa         | ssed to the path.   | Expa                               | nder is bypassed to the path. |  |  |  |  |  |

|              | Modem data s                                      | ignaling rate s | elect pin.         |                     |                                    |                               |  |  |  |  |  |

| BR           |                                                   | _               | BR                 | Date signaling rate |                                    | _                             |  |  |  |  |  |

| DIT          |                                                   | _               | 0                  | 1200 bps            | 1                                  | _                             |  |  |  |  |  |

|              |                                                   | _               | 1                  | 2400 bps            |                                    | _                             |  |  |  |  |  |

| Name     |                                                                                                            |                                                                                                           | Function                                                                                                                                |                        |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|--|

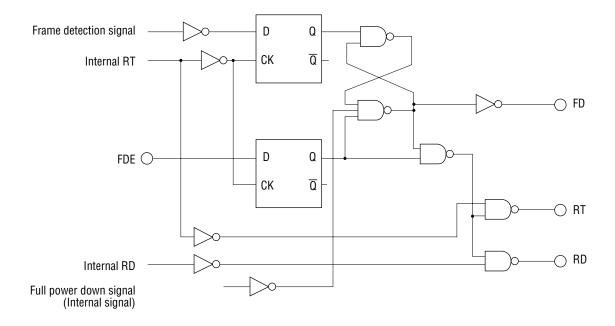

|          | Frame s                                                                                                    | synchro                                                                                                   | onous signal detector control.                                                                                                          |                        |  |  |  |  |  |  |  |

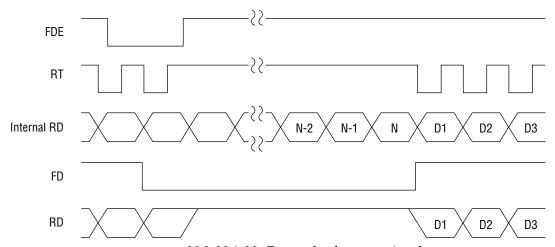

|          | When digital "0" is applied to this pin, FD pin is fixed to "0" level. RT and RD always work.              |                                                                                                           |                                                                                                                                         |                        |  |  |  |  |  |  |  |

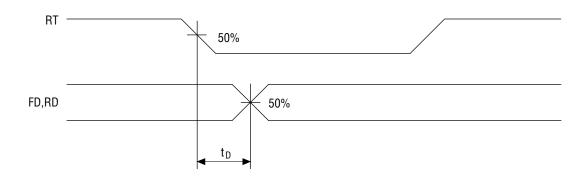

| FDE      | When digital "1" is applied to this pin, frame synchronous detector works, and RT and RD pins are fixed    |                                                                                                           |                                                                                                                                         |                        |  |  |  |  |  |  |  |

|          | to "1" level untill synchronous signal detector detects frame synchronous signal and FD becomes "1" level. |                                                                                                           |                                                                                                                                         |                        |  |  |  |  |  |  |  |

|          | Refer to                                                                                                   | Fig.3                                                                                                     | (receive signal timing).                                                                                                                |                        |  |  |  |  |  |  |  |

|          | Bit synd                                                                                                   | Bit synchronous signal detector control.                                                                  |                                                                                                                                         |                        |  |  |  |  |  |  |  |

|          |                                                                                                            |                                                                                                           | FDE pins are digital "1" level and when bit synchronous signal a                                                                        | nd frame synchronous   |  |  |  |  |  |  |  |

| BIT      | "                                                                                                          |                                                                                                           | cted continously, FD becomes digital "1".                                                                                               |                        |  |  |  |  |  |  |  |

|          |                                                                                                            |                                                                                                           | is digital "0" level and FDE pin is digital "1" level and when 16-bit                                                                   | frame synchronous      |  |  |  |  |  |  |  |