# Compact Smart Card Interface IC

The NCN6000 is an integrated circuit dedicated to the smart card interface applications. The device handles any type of smart card through a simple and flexible microcontroller interface. On top of that, thanks to the built—in chip select pin, several couplers can be connected in parallel. The device is particularly suited for low cost, low power applications, with high extended battery life coming from extremely low quiescent current.

#### **Features**

- 100% Compatible with ISO7816–3 and EMV Standard

- Wide Battery Supply Voltage Range:  $2.7 \le \text{Vbat} \le 6.0 \text{ V}$

- Programmable CRD\_VCC Supply to Cope with either 3.0 V or 5.0 V Card Operation

- Built-in DC/DC Converter Generates the CRD\_VCC Supply with a Single External Low Cost Inductor only, providing a High Efficiency Power Conversion

- Full Control of the Power Up/Down Sequence Yields High Signal Integrity on both the Card I/O and the Signal Lines

- Programmable Card Clock Generator

- Built-in Chip Select Logic allows Parallel Coupling Operation

- ESD Protection on Card Pins (8.0 kV, Human Body Model)

- Fault Monitoring includes Vbat<sub>low</sub> and Vcc<sub>low</sub>, providing Logic Feedback to External CPU

- Card Detection Programmable to Handle Positive or Negative Going Input

- Built-in Programmable CRD\_CLK Stop Function Handles both High or Low State

#### Typical Application

- E-Commerce Interface

- ATM Smart Card

- Pay TV System

## ON Semiconductor

http://onsemi.com

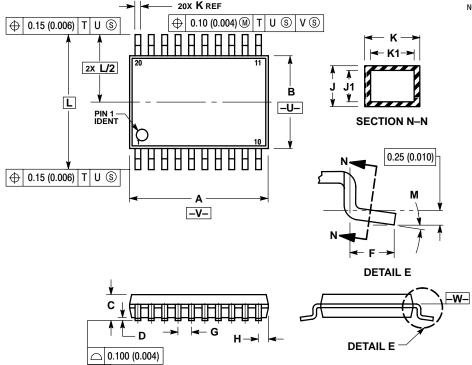

#### MARKING DIAGRAM

TSSOP-20 DTB SUFFIX CASE 948E

A = Assembly Location

= Wafer Lot

Y = Year

W = Work Week

#### **PIN CONNECTIONS**

| A0 1           | 0         | 20 V <sub>bat</sub>      |

|----------------|-----------|--------------------------|

| A1 2           | 97        | 19 L <sub>out</sub> _H   |

| PGM 3          | W W W. O. | 18 L <sub>out</sub> _L   |

| PWR_ON 4       |           | 17 PWR_GND               |

| STATUS 5       |           | 16 GROUND                |

| CS 6           |           | 15 CRD_V <sub>CC</sub>   |

| RESET 7        |           | 14 CRD_IO                |

| I/O 8          |           | 13 CRD_CLK               |

| ĪNT 9          |           | 12 CRD_RST               |

| CLOCK_IN 10    | _ ~       | 11 CRD_DET               |

| I/O 8<br>INT 9 | -         | 13 CRD_CLK<br>12 CRD_RST |

(Top View

#### **ORDERING INFORMATION**

| Device       | Device Package |                  |

|--------------|----------------|------------------|

| NCN6000DTB   | TSSOP-20       | 75 Units/Rail    |

| NCN6000DBTR2 | TSSOP-20       | 2500/Tape & Reel |

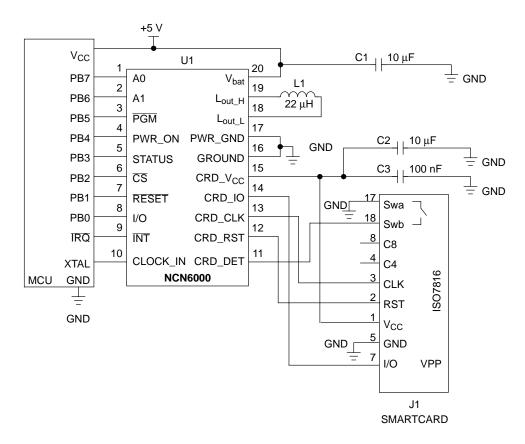

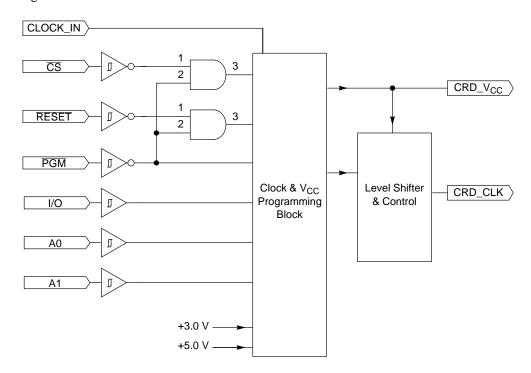

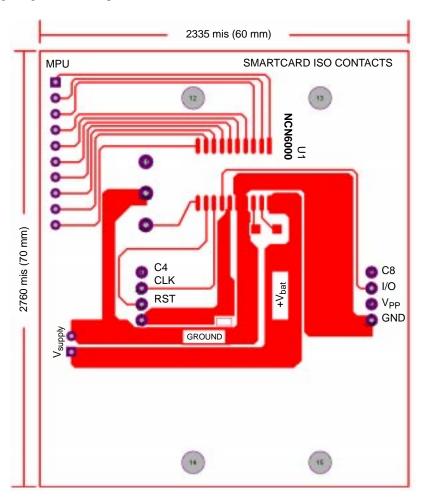

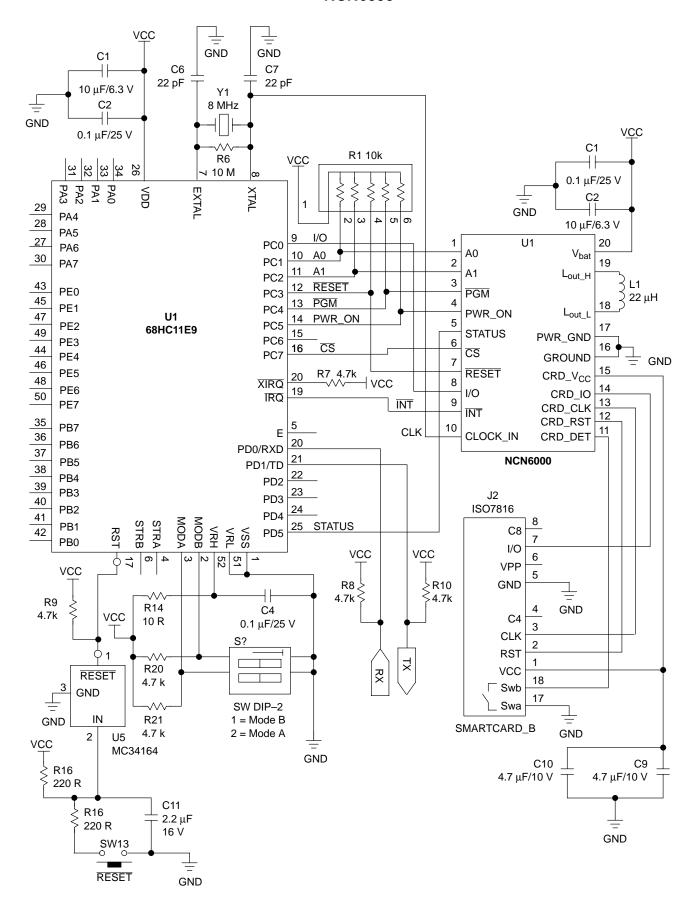

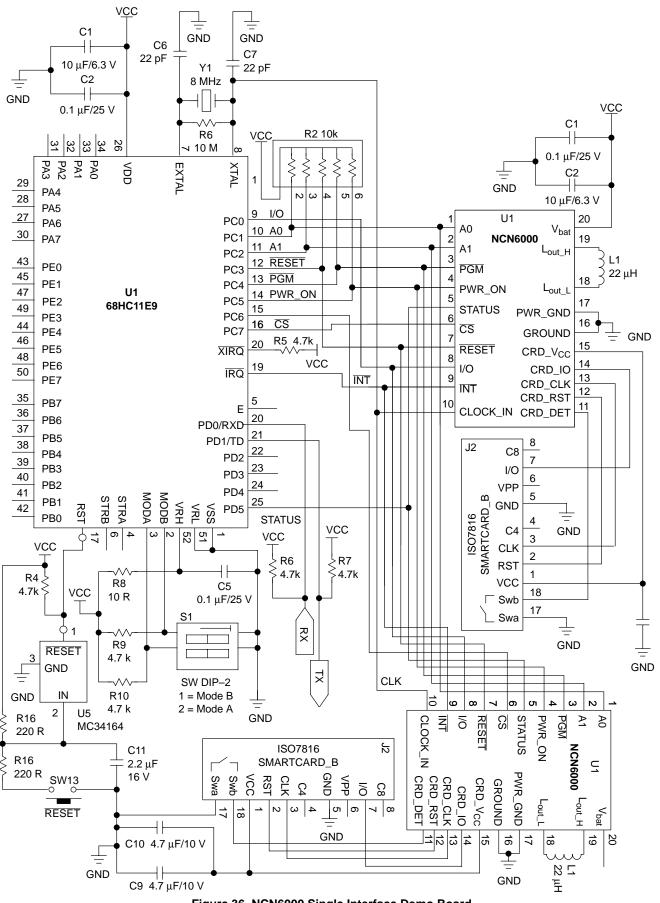

Figure 2. Typical Application

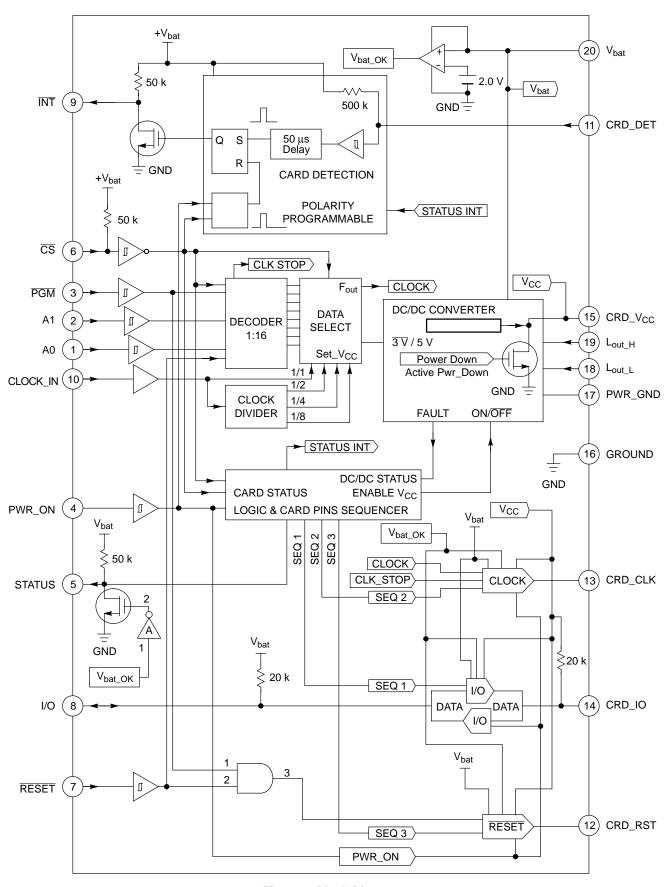

Figure 3. Block Diagram

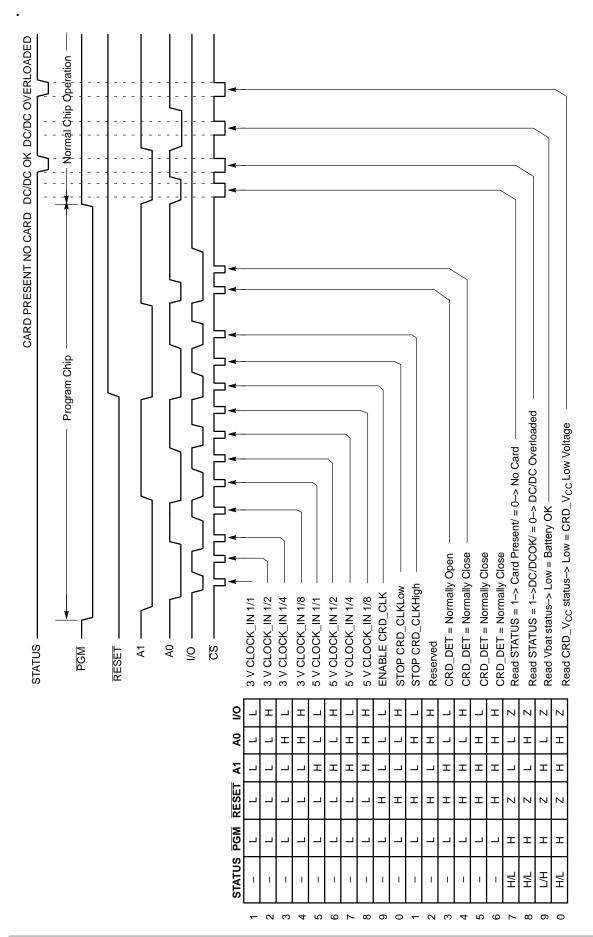

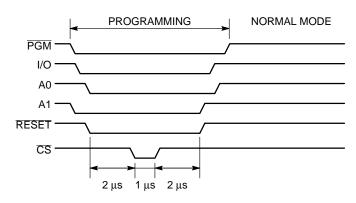

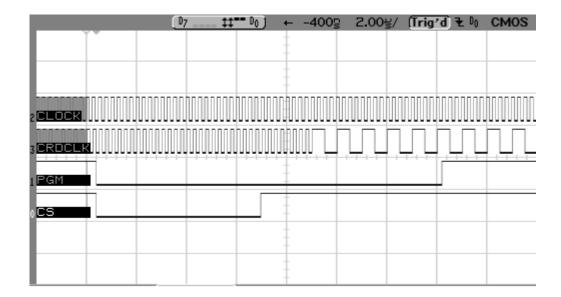

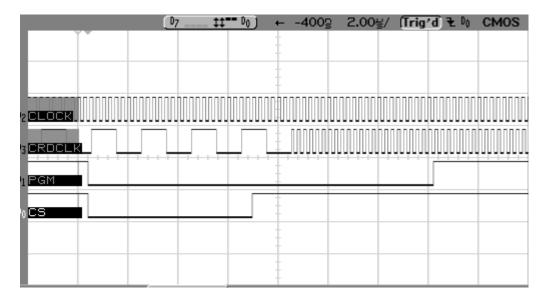

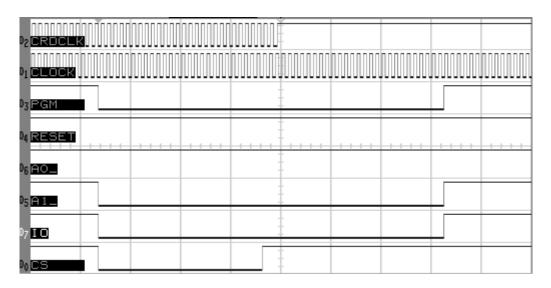

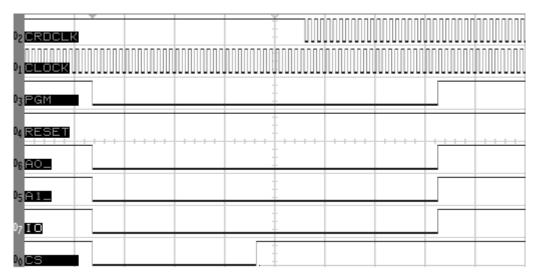

Figure 4. Programming and Normal Operation Basic Timing

The programming can be achieved with the card powered ON or OFF. The identification of the interrupt is carried out by polling the STATUS pin, the Vbat voltage and the DC/DC results being provided on the same pin as depicted by the

table in Figure 4. During the programming mode, the  $\overline{PGM}$  pin can be released to High since the mode is internally latched by the Negative going transition presents on the Chip Select pin.

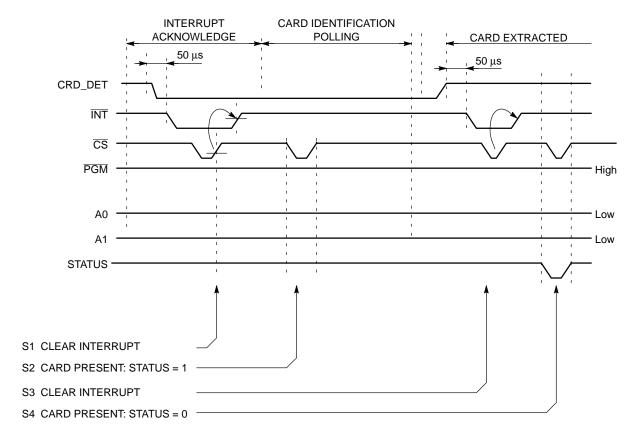

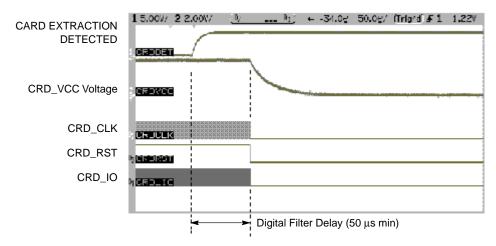

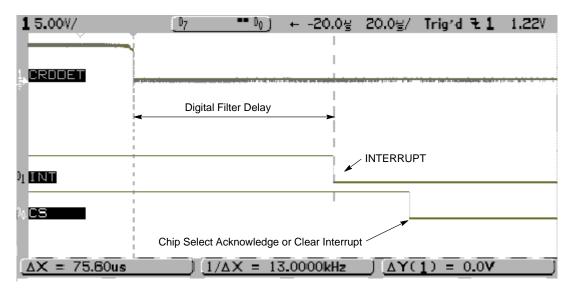

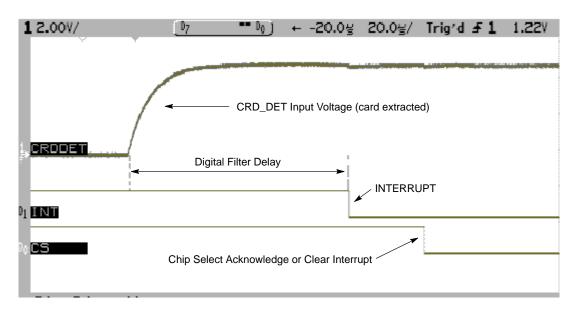

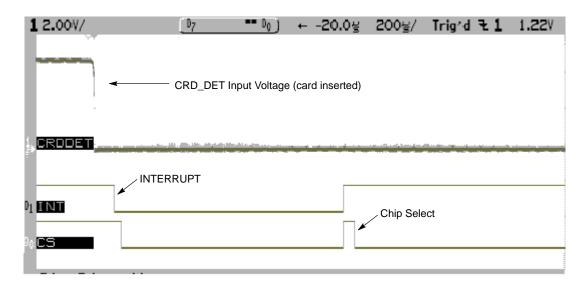

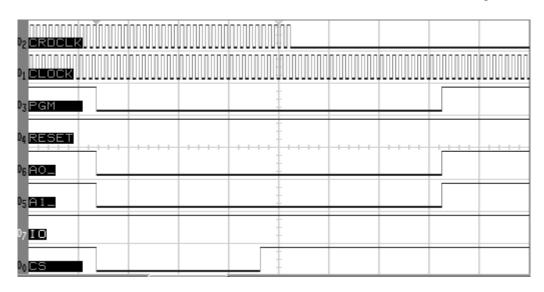

Figure 5. Interrupt Servicing and Card Polling

When a card is either inserted or extracted, the CRD\_DET pin signal is debounced internally prior to pull the  $\overline{\text{INT}}$  pin to Low. The built—in logic circuit automatically accommodates positive or negative input signal slope, on both insertion and extraction state, depending upon the polarity defined during the initialization sequence. The default condition is Normally Open switch, negative going card detection. The external CPU shall acknowledge the request by forcing  $\overline{\text{CS}} = L$  which, in turn, releases the  $\overline{\text{INT}}$  pin to High upon positive going of Chip Select (Table 4). Polling the STATUS pin as depicted in Table 3 identifies the active card. If a card is present, the STATUS returns High,

otherwise a Low is presented pin 5. The 50  $\mu$ s digital filter is activated during both Insertion and Extraction of the card. The MPU shall clear the  $\overline{\rm INT}$  line when the card has been extracted, making the interrupt function available for other purposes. However, neither the NCN6000 operation nor the smart card I/O line or commands are affected by the state of the  $\overline{\rm INT}$  pin.

On the other hand, clearing the  $\overline{INT}$  and reading the STATUS register can be performed by a single read by the MPU: states S1 and S2 can be combined in a single instruction, the same for S3 and S4.

## **ABBREVIATIONS**

| DC/DC External Inductor                           |

|---------------------------------------------------|

| DC/DC External Inductor                           |

| Output Capacitor                                  |

| Card Power Supply Input                           |

| Current at CRD_VCC Pin                            |

| 5.0 V Smart Card                                  |

| 3.0 V Smart Card                                  |

| Chip Select (from MPU)                            |

| High Impedance Logic State (according to ISO7816) |

| Interface IC Card Power Supply Output             |

| Interface IC Card Clock Output                    |

| Interface IC Card Reset Output                    |

| Interface IC Card I/O Signal Line                 |

| Interface IC Card Detection                       |

| Answer to Reset                                   |

| Select Programming or Normal Operation            |

| Interrupt (to MPU)                                |

| Rise Time                                         |

| Fall Time                                         |

| Delay Time                                        |

| Storage Time                                      |

|                                                   |

## PIN FUNCTIONS AND DESCRIPTION

| Pin | Name   | Туре               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | A0     | INPUT              | This pin is combined with A1, PGM, RESET and I/O to program the chip mode of operation and to read the data provided by STATUS. (Figures 4 and 5 and Tables 2 and 3)                                                                                                                                                                                                                                                                                                                                        |

| 2   | A1     | INPUT              | This pin is combined with A0, PGM, RESET and I/O to program the chip mode of operation and to read the data provided by STATUS. (Figures 4 and 5 and Tables 2 and 3)                                                                                                                                                                                                                                                                                                                                        |

| 3   | PGM    | INPUT              | This pin is combined with A0, A1, RESET and I/O to program the chip mode of operation and to read the data provided by STATUS. (Figures 4 and 5 and Tables 2 and 3)                                                                                                                                                                                                                                                                                                                                         |

| 4   | PWR_ON | INPUT<br>Pull Down | This pin validates the operation of the internal DC/DC converter:  \( \overline{CS} = L + PWR_ON = Negative going: DC/DC is OFF \)  \( \overline{CS} = L + PWR_ON = Positive going: DC/DC is ON \)  Note: The PWR_ON bit must be combined with a Low state \( \overline{CS} \) signal to activate the function. (Table 2)                                                                                                                                                                                   |

| 5   | STATUS | OUTPUT             | This pin provides logic state related to the card and NCN6000 status. According to the A0, A1 and $\overline{PGM}$ logic state, this pin carries either the Card present status or the Vbat or the DC/DC operation state. When $\overline{PGM}$ = L, STATUS is not affected, see Table 2.                                                                                                                                                                                                                   |

| 6   | CS     | INPUT<br>Pull Up   | This pin provides the NCN6000 chip select function. The PWR_ON, $\overline{RESET}$ , I/O, A0, A1 and $\overline{PGM}$ signals are disabled when $\overline{CS}$ = H. When $\overline{PGM}$ = L and $\overline{CS}$ = L, the device jumps to the programming mode (Figure 4 and Tables 1, 2 and 3). The Chip Select pin must be a unique physical address when more than one card are controlled by a single MPU. The data presented by the MPU are latched upon positive going edge of the Chip Select pin. |

http://opcomi.com

## PIN FUNCTIONS AND DESCRIPTION (continued)

| Pin | Name     | Туре                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RESET    | INPUT<br>Pull Down            | This pin provides two modes of operation depending upon the logic state of PGM pin 3:  PGM = 1: The signal present at this pin is translated to pin 12 (card reset signal) when CS = L and PWR_ON = H. It is latched when CS = H.  PGM = 0: The signal present on this pin is used as a logic input to program the internal functions (Figure 5 and Tables 2 and 3).                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8   | I/O      | Input/Output<br>Pull Up       | This pin is connected to an external microcontroller interface. A bidirectional level translator adapts the serial I/O signal between the smart card and the microcontroller. The level translator is enabled when $\overline{CS} = L$ . The signal present on this pin is latched when $\overline{CS} = H$ . This pin is also used in programming mode (Tables 1, 2 and 3, Figures 4 and 5).                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9   | ĪNT      | OUTPUT<br>Pull Down           | This pin is activated LOW when a card has been inserted and detected by the interface or when the NCN6000 reports Vbat or CRD_VCC status (See Table 6). The signal is reset to a logic 1 on the rising edge of either $\overline{CS}$ or PWR_ON. The Collector open mode makes possible the wired AND/OR external logic. When two or more interfaces share the $\overline{INT}$ function with a single microcontroller, the software must poll the STATUS pin to identify the origin of the interrupt (Figure 5).                                                                                                                                                                                                                                                                                           |

| 10  | CLOCK_IN | CLOCK INPUT<br>High Impedance | This pin can be connected to either the microcontroller master clock, or to any clock signal, to drive the external smart cards. The signal is fed to internal clock selector circuit and translated to the CRD_CLK pin at either the same frequency, or divided by 2 or 4 or 8, depending upon the programming mode (Tables 1, 2 and 3). Care must be observed, at PCB level, to minimize the pick–up noise coming from the CLOCK_IN line. It is recommended to put a shield, built with a 10 mil copper track, around this line and terminated to the GND.                                                                                                                                                                                                                                                |

| 11  | CRD_DET  | INPUT                         | The signal coming from the external card connector is used to detect the presence of the card. A built–in pull up low current source makes this pin active LOW or HIGH, assuming one side of the external switch is connected to ground. At Vbat start up, the default condition is Normally Open switch, negative going insertion detection. The Normally Closed switch, positive going insertion detection, can be defined by programming the NCN6000 accordingly. In this case, the polarity must be set up during the first cycles of the system initialization, otherwise an already inserted card will not be detected by the chip.                                                                                                                                                                   |

| 12  | CRD_RST  | OUTPUT                        | This pin is connected to the RESET pin of the card connector. A level translator adapts the RESET signal from the microcontroller to the external card. The output current is internally limited to 15 mA. The CRD_RST is validated when PWR_ON = H and PGM = H and hard wired to Ground when the card is deactivated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13  | CRD_CLK  | OUTPUT                        | This pin is connected to the CLK pin of the card connector. The CRD_CLK signal comes from the clock selector circuit output. Combining A0, A1, $\overline{PGM}$ and I/O, as depicted in Table 3 and Figure 3, programs the clock selection. This signal can be forced into a standby mode with CRD_CLK either High or Low, depending upon the mode defined by the programming sequence (Tables 1, 2 and 3 and Figure 4). Care must be observed, at PCB level, to minimize the pick—up noise coming from the CRD_CLK line. It is recommended to put a shield, built with a 10mil copper track, around this line and terminated to the GND.                                                                                                                                                                   |

| 14  | CRD_IO   | I/O                           | This pin handles the connection to the serial I/O pin of the card connector. A bidirectional level translator adapts the serial I/O signal between the card and the microcontroller. The CRD_IO pin current is internally limited to 15 mA. A built–in register holds the previous state presents on the I/O input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15  | CRD_VCC  | POWER                         | This pin provides the power to the external card. It is the logic level "1" for CRD_IO, CRD_RST and CRD_CLK signals. The energy stored by the DC/DC external inductor Lout must be smoothed by a 10 $\mu\text{F}$ capacitor, associated with a 100 nF ceramic in parallel, connected across CRD_VCC and GND. In the event of a CRD_VCC U_VLOW voltage, the NCN6000 detects the situation and feedback the information in the STATUS bit. The device does not take any further action, particularly the DC/DC converter is neither stopped nor reprogrammed by the NCN6000. It is up to the external MPU to handle the situation. However, when the CRD_VCC is overloaded, the NCN6000 shut off the DC/DC converter, pulls the $\overline{\text{INT}}$ pin Low and reports the fault in the STATUS register. |

http://opcomi.com

## PIN FUNCTIONS AND DESCRIPTION (continued)

| Pin | Name    | Туре   | Description                                                                                                                                                                                                                                                                                                                     |

|-----|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | GROUND  | SIGNAL | The logic and low level analog signals shall be connected to this ground pin. This pin must be externally connected to the PWR_GND pin 17. The designer must make sure no high current transients are shared with the low signal currents flowing into this pin.                                                                |

| 17  | PWR_GND | POWER  | This pin is the Power Ground associated with the built–in DC/DC converter and must be connected to the system ground together with GROUND pin 11. Using good quality ground plane is recommended to avoid spikes on the logic signal lines.                                                                                     |

| 18  | Lout_L  | POWER  | The High Side of the external inductor is connected between this pin and Lout_H to provide the DC/DC function. The built–in MOS devices provide the switching function together with the CRD_VCC voltage rectification.                                                                                                         |

| 19  | Lout_H  | POWER  | The High Side of the external inductor is connected between this pin and Lout_L to provide the DC/DC function. The current flowing into this inductor is limited by a sense resistor internally connected from Vbat/pin 20 and pin 19. Typically, Lout = $22 \mu$ H, with ESR < $2.0 \Omega$ , for a nominal 55 mA output load. |

| 20  | Vbat    | POWER  | This pin is connected to the supply voltage and monitored by the NCN6000. The operation is inhibited when Vbat is below the minimum 2.70 V value, followed by a PWR_DOWN sequence and a Low STATUS state.                                                                                                                       |

## MAXIMUM RATINGS (Note 1)

| Rating                                                                                                   | Symbol                | Value                                                                                           | Unit       |

|----------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|------------|

| Battery Supply Voltage                                                                                   | Vbat                  | 7.0                                                                                             | V          |

| Battery Supply Current (Note 2)                                                                          | lbat                  | 300                                                                                             | mA         |

| Power Supply Voltage                                                                                     | Vcc                   | 6.0                                                                                             | V          |

| Power Supply Current                                                                                     | Icc                   | ±100                                                                                            | mA         |

| Digital Input Pins                                                                                       | Vin                   | $-0.5 \text{ V} < \text{V}_{\text{in}} < \text{V}_{\text{bat}} + 0.5 \text{ V},$<br>but < 7.0 V | V          |

| Digital Input Pins                                                                                       | lin                   | ±5.0                                                                                            | mA         |

| Digital Output Pins                                                                                      | Vout                  | -0.5 V < V <sub>in</sub> < V <sub>bat</sub> +0.5 V,<br>but < 7.0 V                              | V          |

| Digital Output Pins                                                                                      | lout                  | ±10                                                                                             | mA         |

| Card Interface Pins                                                                                      | Vcard                 | ard -0.5 V < V <sub>card</sub> < CRD_VCC +0.5 V                                                 |            |

| Card Interface Pins, except CRD_CLK                                                                      | Icard                 | ±15                                                                                             | mA         |

| Inductor Current                                                                                         | ILout                 | 300                                                                                             | mA         |

| ESD Capability (Note 3) Standard Pins Card Interface Pins and CRD_DET                                    | VESD                  | 2.0<br>8.0                                                                                      | kV         |

| TSSOP–20 Package Power Dissipation @ Tamb = +85°C Thermal Resistance Junction to Air ( $R_{\theta ja}$ ) | $P_{DS} R_{	heta ja}$ | 320<br>125                                                                                      | mW<br>°C/W |

| Operating Ambient Temperature Range                                                                      | TA                    | -25 to +85                                                                                      | °C         |

| Operating Junction Temperature Range                                                                     | TJ                    | -25 to +125                                                                                     | °C         |

| Maximum Junction Temperature (Note 4)                                                                    | TJmax                 | +150                                                                                            | °C         |

| Storage Temperature Range                                                                                | Tsg                   | -65 to +150                                                                                     | °C         |

- Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = +25°C.

This current represents the maximum peak current the pin can sustain, not the NCN6000 consumption (see Ibat<sub>op</sub>).

Human Body Model, R = 1500 Ω, C = 100 pF.

Absolute Maximum Rating beyond which damage to the device may occur.

## **POWER SUPPLY SECTION** (-25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                                                                                                                                                                                                                | Symbol                                                          | Pin | Min                  | Тур           | Max               | Unit         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|----------------------|---------------|-------------------|--------------|

| Power Supply                                                                                                                                                                                                                          | Vbat                                                            | 20  | 2.7                  | -             | 6.0               | V            |

| Standby Supply Current Conditions:  PWR_ON = L, STATUS = H, CLOCK_IN = H,  \overline{CS} = H. All other logic inputs and outputs are open:  Vbat = 3.0 V  Vbat = 5.0 V                                                                | Ibat <sub>sb</sub>                                              | 20  | -<br>-               | 3.0           | 8.0<br>15         | μА           |

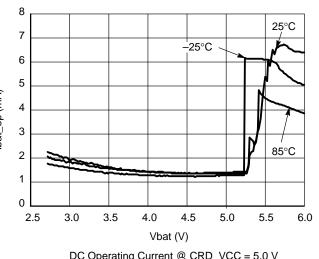

| DC Operating Current (Figure 19)  PWR_ON = H, CLOCK_IN = 0, $\overline{CS}$ = H, all CRD pins unloaded  @ Vbat = 6.0 V, CRD_VCC = 5.0 V  @ Vbat = 3.6 V, CRD_VCC = 5.0 V                                                              | Ibat <sub>op</sub>                                              | 20  | _<br>_               | 7.0<br>2.0    | _<br>5.0          | mA           |

| Vbat Undervoltage Detection <sub>High</sub> Vbat Undervoltage Detection <sub>Low</sub> Vbat Undervoltage Detection <sub>Hysteresis</sub>                                                                                              | Vbat <sub>LH</sub><br>Vbat <sub>LL</sub><br>Vbat <sub>HY</sub>  | 20  | 2.1<br>2.0<br>–      | -<br>-<br>100 | 2.7<br>2.6<br>–   | V<br>V<br>mV |

| Output Card Supply Voltage @ lcc = 55 mA<br>@ $2.70 \text{ V} \leq \text{Vbat} \leq 6.0 \text{ V}$<br>$CRD\_VCC = 3.0 \text{ V}$<br>$CRD\_VCC = 5.0 \text{ V}$<br>@ $Vbat_{LL} < Vbat < 2.70 \text{ V}$<br>$CRD\_VCC = 5.0 \text{ V}$ | Vcc<br>V <sub>C3H</sub><br>V <sub>C5H</sub><br>V <sub>C5H</sub> | 15  | 2.75<br>4.75<br>4.50 | -<br>-<br>-   | 3.25<br>5.25<br>– | V            |

| Output Card Supply Peak Current @ Vcc = 5.0 V<br>@ CRD_VCC = 5.0 V<br>@ CRD_VCC = 3.0 V<br>@ Vbat = 3.6 V, CRD_VCC = 5.0 V, Tamb < 65°C                                                                                               | Iccp                                                            | 15  | 55<br>55<br>65       | _<br>_<br>_   | -<br>-<br>-       | mA           |

| Output Current Limit Time Out                                                                                                                                                                                                         | tdoff                                                           | 15  | -                    | 4.0           | -                 | ms           |

| Output Over Current Limit                                                                                                                                                                                                             | Iccov                                                           | 15  | -                    | -             | 100               | mA           |

| Output Dynamic Peak Current @ CRD_VCC = 3.0 V or 5.0 V, Cout = 10 μF Ceramic XR7, Pulse Width 400 ns (Notes 5 and 6)                                                                                                                  | Iccd                                                            | 15  | 100                  | -             | _                 | mA           |

| Battery Start–Up Current  @ CRD_VCC = 3.0 V, −25°C ≤ TA ≤+ 85°C  @ CRD_VCC = 5.0 V, −25°C ≤ TA ≤+ 85°C                                                                                                                                | Icc <sub>st</sub>                                               | 20  | _<br>_               | 140<br>300    | -<br>-            | mA           |

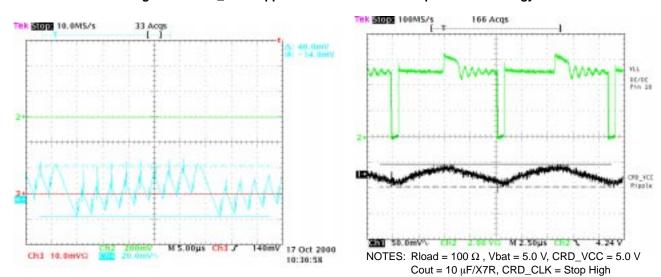

| Output Card Supply Voltage Ripple @ Lout = $22 \mu H$ , Cout 1 = $10 \mu F$ , Cout 2 = $100 nF$ , Vbat = $3.6 V$ lout = $55 mA$ CRD_VCC = $5.0 V$ (Note 5) CRD_VCC = $3.0 V$                                                          | Vcc <sub>rip</sub>                                              | 15  | _<br>_               | _<br>_        | 50<br>50          | mV           |

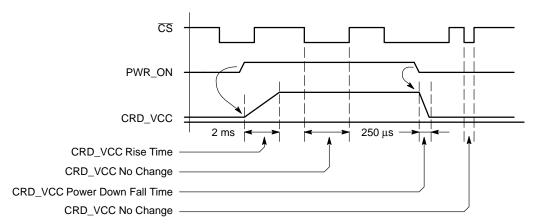

| Output Card Supply Turn On Time @ Lout = $22 \mu F$ , Cout1 = $10 \mu F$ , Cout2 = $100 nF$ , Vbat = $2.7 V$ , CRD_VCC = $5.0 V$                                                                                                      | Vcc <sub>TON</sub>                                              | 15  | -                    | -             | 2.0               | ms           |

| Output Card Supply Shut Off Time @ Cout1 = 10 $\mu$ F, Ceramic, Vbat = 2.7 V, CRD_VCC = 5.0 V, VcCOFF < 0.4 V                                                                                                                         | Vcc <sub>TOFF</sub>                                             | 15  | -                    | _             | 250               | μs           |

| DC/DC Converter Operating Frequency                                                                                                                                                                                                   | Fsw                                                             | 18  | _                    | 600           | -                 | kHz          |

| Power Switch Drain/Source Resistor                                                                                                                                                                                                    | R <sub>ONS</sub>                                                | 18  | -                    | 1.9           | 2.2               | Ω            |

| Output Rectifier ON Resistor                                                                                                                                                                                                          | R <sub>OND</sub>                                                | 15  | -                    | 2.8           | 3.4               | Ω            |

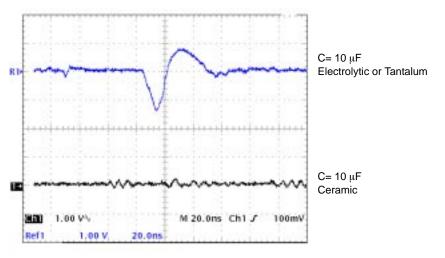

<sup>5.</sup> Ceramic X7R, SMD types capacitors are mandatory to achieve the CRD\_VCC specifications. When electrolytic capacitor is used, the external filter must include a 100 nF, max 50 mΩ ESR capacitor in parallel, to reduce both the high frequency noise and ripple to a minimum. Depending upon the PCB layout, it might be necessary is to use two 6.8 μF/10 V/ceramic/X7R//SMD1206 in parallel, yielding an improved CRD\_VCC ripple over the temperature range.

6. According to ISO7816–3, paragraph 4.3.2.

DIGITAL PARAMETERS SECTION @  $2.70 \text{ V} \le \text{Vbat} \le 6.0 \text{ V}$ , NORMAL OPERATING MODE ( $-25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  ambient temperature, unless otherwise noted.) Note: Digital inputs undershoot <-0.30 V to ground, Digital inputs overshoot <0.30 V to Vbat

| Rating                                                                                                                   | Symbol                               | Pin                           | Min          | Тур    | Max         | Unit |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------|--------------|--------|-------------|------|

| Input Asynchronous Clock Duty Cycle = 50%  @ Vbat = 3.0V over the temperature range                                      | F <sub>CLKIN</sub>                   | 10                            | -            | -      | 40          | MHz  |

| Clock Rise Time<br>Clock Fall Time                                                                                       | F <sub>tr</sub><br>F <sub>tf</sub>   | 10                            | _<br>_       | -<br>- | 5.0<br>5.0  | ns   |

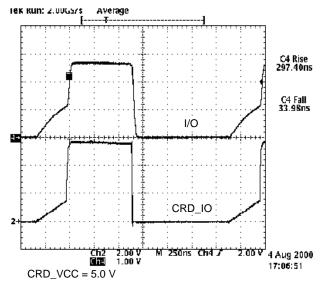

| I/O Data Transfer Switching Time, Both Directions (I/O and CRD_IO), @ Cout = 30 pF I/O Rise Time* (Note 7) I/O Fall Time | T <sub>RIO</sub><br>T <sub>FIO</sub> | 8, 14                         | -            | -      | 0.8<br>0.8  | μs   |

| Input/Output Data Transfer Time, Both Directions<br>@ 50% CRD_VCC, L to H and H to L                                     | T <sub>TIO</sub>                     | 8, 14                         | -            | -      | 150         | ns   |

| Minimum PWR_ON Low Level Logic State Time to Power Down the DC/DC Converter                                              | T <sub>WON</sub>                     | 4                             | 2.0          | -      | -           | μs   |

| CRD_VCC Power Up/Down Sequence Interval                                                                                  | T <sub>DSEQ</sub>                    |                               | -            | 0.5    | 2.0         | μs   |

| STATUS Pull Up Resistance                                                                                                | R <sub>STA</sub>                     | 5                             | 20           | 50     | 80          | kΩ   |

| Chip Select CS Pull Up Resistance                                                                                        | R <sub>CSPU</sub>                    | 6                             | 20           | 50     | 80          | kΩ   |

| Interrupt INT Pull Up Resistance                                                                                         | R <sub>INTPU</sub>                   | 9                             | 20           | 50     | 80          | kΩ   |

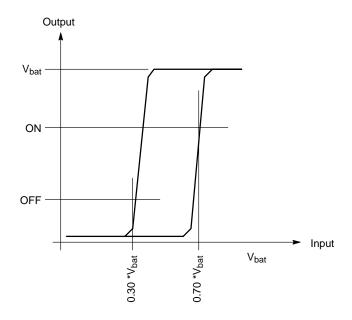

| Positive Going Input High Voltage Threshold (A0, A1, PGM, PWR_ON, CS, RESET, CRD_DET)                                    | V <sub>IH</sub>                      | 1, 2,<br>3, 4,<br>6, 7,<br>11 | 0.70 * Vbat  | -      | Vbat        | V    |

| Negative Going Input High Voltage Threshold (A0, A1, PGM, PWR_ON, CS, RESET, CRD_DET)                                    | V <sub>IL</sub>                      | 1, 2,<br>3, 4,<br>6, 7,<br>11 | 0            | -      | 0.30 * Vbat | V    |

| Output High Voltage<br>STATUS, INT @ I <sub>OH</sub> = -10 μA                                                            | V <sub>OH</sub>                      | 5, 9                          | Vbat – 1.0 V | _      | _           | V    |

| Output High Voltage<br>STATUS, INT @ I <sub>OH</sub> = 200 μA                                                            | V <sub>OL</sub>                      | 5, 9                          | -            | _      | 0.40        | V    |

<sup>7.</sup> Since a 20 k $\Omega$  pull up resistor is provided by the NCN6000, the external MPU can use an Open Drain connection.

## DIGITAL PARAMETERS SECTION @ 2.70 V $\leq$ Vbat $\leq$ 6.0 V, CHIP PROGRAMMING MODE (-25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                              | Symbol            | Pin                    | Min | Тур | Max | Unit |  |  |  |

|-----------------------------------------------------|-------------------|------------------------|-----|-----|-----|------|--|--|--|

| A0, A1, PGM, PWR_ON, RESET and I/O Data Set Up Time | T <sub>SMOD</sub> | 1, 2,<br>3, 4,<br>7, 8 | 2.0 | -   | -   | μs   |  |  |  |

| A0, A1, PGM, PWR_ON, RESET and I/O Data Set Up Time | T <sub>HMOD</sub> | 1, 2,<br>3, 4,<br>7, 8 | 2.0 | _   | -   | μs   |  |  |  |

| Chip Select CS Low State Pulse Width                | T <sub>WCS</sub>  | 6                      | 2.0 | _   | _   | μs   |  |  |  |

http://opcomi.com

SMART CARD SECTION (-25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                                                                                                                                                                                                                                                                                                                                        | Symbol                                                                                               | Pin    | Min                | Тур | Max                                      | Unit                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------|--------------------|-----|------------------------------------------|--------------------------------|

| CRD_RST @ CRD_VCC = $+5.0 \text{ V}$<br>Output RESET V <sub>OH</sub> @ Icrd_rst = $-20 \mu$ A<br>Output RESET V <sub>OL</sub> @ Icrd_rst = $200 \mu$ A<br>Output RESET Rise Time @ Cout = $30 \mu$ P<br>Output RESET Fall Time @ Cout = $30 \mu$ P                                                                                                            | V <sub>OH</sub><br>V <sub>OL</sub><br>t <sub>R</sub><br>t <sub>F</sub>                               | 12     | CRD_VCC - 0.9<br>0 | -   | CRD_VCC<br>0.4<br>100<br>100             | V<br>V<br>ns<br>ns             |

| CRD_RST @ Vcc = $+3.0 \text{ V}$<br>Output RESET V <sub>OH</sub> @ Icrd_rst = $-20 \mu$ A<br>Output RESET V <sub>OL</sub> @ Icrd_rst = $200 \mu$ A<br>Output RESET Rise Time @ Cout = $30 \mu$ P<br>Output RESET Fall Time @ Cout = $30 \mu$ P                                                                                                                | V <sub>OH</sub><br>V <sub>OL</sub><br>t <sub>R</sub><br>t <sub>F</sub>                               |        | CRD_VCC - 0.9<br>0 |     | CRD_VCC<br>0.4<br>100<br>100             | V<br>V<br>ns<br>ns             |

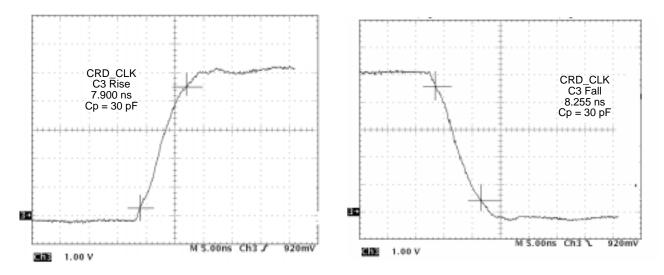

| CRD_CLK @ CRD_VCC = +3.0 V or +5.0 V                                                                                                                                                                                                                                                                                                                          |                                                                                                      | 13     |                    | -   |                                          |                                |

| CRD_VCC = $+5.0 \text{ V}$ Output Frequency (See Note 8) Output Duty Cycle @ DC Fin = $50\% \pm 1\%$ Output CRD_CLK Rise Time @ Cout = $30 \text{ pF}$ Output CRD_CLK Fall Time @ Cout = $30 \text{ pF}$ Output V <sub>OH</sub> @ Icrd_clk = $-20 \mu$ A Output V <sub>OL</sub> @ Icrd_clk = $100 \mu$ A                                                      | FCRDCLK FCRDDC t <sub>R</sub> t <sub>F</sub> VOH VOL                                                 |        | 45<br>3.15<br>0    |     | 5.0<br>55<br>18<br>18<br>CRD_VCC<br>+0.5 | MHz<br>%<br>ns<br>ns<br>V<br>V |

| CRD_VCC = $\pm 3.0 \text{ V}$ Output Frequency (See Note 8) Output Duty Cycle @ DC Fin = $50\% \pm 1\%$ Output CRD_CLK Rise Time @ Cout = $30 \text{ pF}$ Output CRD_CLK Fall Time @ Cout = $30 \text{ pF}$ Output V <sub>OH</sub> @ Icrd_clk = $-20 \mu$ A @ Cout = $30 \text{ pF}$ Output V <sub>OL</sub> @ Icrd_clk = $100 \mu$ A @ Cout = $30 \text{ pF}$ | F <sub>CRDCLK</sub> F <sub>CRDDC</sub> t <sub>R</sub> t <sub>F</sub> V <sub>OH</sub> V <sub>OL</sub> |        | 40<br>1.85<br>0    |     | 5.0<br>60<br>18<br>18<br>CRD_VCC<br>0.7  | MHz<br>%<br>ns<br>ns<br>V<br>V |

| CRD_I/O @ CRD_VCC = $+5.0 \text{ V}$<br>CRD_I/O Data Transfer Frequency<br>CRD_I/O Rise Time @ Cout = $30 \text{ pF}$<br>CRD_I/O Fall Time @ Cout = $30 \text{ pF}$<br>Output V <sub>OH</sub> @ Icrd_i/o = $-20 \mu\text{A}$<br>Output V <sub>OL</sub> @ Icrd_i/o = $500 \mu\text{A}$ , V <sub>IL</sub> = $0 \text{ V}$                                       | FIO<br>T <sub>RIO</sub><br>T <sub>FIO</sub><br>V <sub>OH</sub><br>V <sub>OL</sub>                    | 14     | CRD_VCC - 0.9<br>0 | 315 | 0.8<br>0.8<br>CRD_VCC<br>0.4             | kHz<br>µs<br>µs<br>V<br>V      |

| CRD_I/O @ CRD_VCC = $\pm 3.0 \text{ V}$<br>CRD_I/O Data Transfer Frequency<br>CRD_I/O Rise Time @ Cout = $30 \text{ pF}$<br>CRD_I/O Fall Time @ Cout = $30 \text{ pF}$<br>Output V <sub>OH</sub> @ Icrd_i/o = $-20 \mu$ A<br>Output V <sub>OL</sub> @ Icrd_i/o = $500 \mu$ A, V <sub>IL</sub> = $0 \text{ V}$                                                 | F <sub>IO</sub><br>T <sub>RIO</sub><br>T <sub>FIO</sub><br>VOH<br>VOL                                |        | CRD_VCC - 0.9<br>0 | 315 | 0.8<br>0.8<br>CRD_VCC<br>0.4             | kHz<br>μs<br>μs<br>V<br>V      |

| CRD_IO Pull Up Resistor @ PWR_ON = H                                                                                                                                                                                                                                                                                                                          | R <sub>CRDPU</sub>                                                                                   | 14     | 14                 | 20  | 26                                       | kΩ                             |

| Card Detection Debouncing Delay:<br>Card Insertion<br>Card Extraction                                                                                                                                                                                                                                                                                         | T <sub>CRDIN</sub><br>T <sub>CRDOFF</sub>                                                            | 11     | 50<br>50           | _   | 150<br>150                               | μs<br>μs                       |

| Card Insertion or Extraction Positive Going Input High Voltage                                                                                                                                                                                                                                                                                                | V <sub>IHDET</sub>                                                                                   | 11     | 0.70 * Vbat        | -   | Vbat                                     | V                              |

| Card Insertion or Extraction Negative Going Input<br>Low Voltage                                                                                                                                                                                                                                                                                              | V <sub>ILDET</sub>                                                                                   | 11     | 0                  | -   | 0.30 * Vbat                              | V                              |

| Card Detection Bias Pull Up Current @<br>Vbat = 5.0 V                                                                                                                                                                                                                                                                                                         | I <sub>DET</sub>                                                                                     | 11     | -                  | 10  | -                                        | μΑ                             |

| Output Peak Max Current Under Card Static<br>Operation Mode @ Vcc = 3.0 V or Vcc = 5.0 V                                                                                                                                                                                                                                                                      | Icrd_iorst                                                                                           | 12, 14 | -                  | -   | 15                                       | mA                             |

| Output Peak Max Current Under Card Static Operation Mode @ Vcc = 3.0 V or Vcc = 5.0 V                                                                                                                                                                                                                                                                         | lcrd_clk                                                                                             | 13     | -                  | -   | 70                                       | mA                             |

<sup>8.</sup> The CRD\_CLK clock can operate up to 20 MHz, but the rise and fall time are not guaranteed to be fully within the ISO7816 specification over the temperature range. Typically, tr and tf are 12 ns @ CRD\_CLK = 10 MHz.

http://opcomi.com

## **Programming and Status Functions**

The NCN6000 features a programming interface and a status interface. Figure 4 illustrates the programming mode.

**Table 1. Programming and Status Functions Pinout Logic**

| Pins | Name     | CRD_VCC<br>Prg. 3.0 V/5.0 V | CLOCK_IN<br>Divide Ratio | CRD_DET                 | CLOCK STOP<br>AND START | Poll Card<br>Status | DC/DC<br>Status | Vbat<br>Status | CRD_VCC<br>Status |

|------|----------|-----------------------------|--------------------------|-------------------------|-------------------------|---------------------|-----------------|----------------|-------------------|

| 5    | STATUS   | Not Affected                | Not Affected             | Not Affected            | Not Affected            | READ                | READ            | READ           | READ              |

| 6    | CS       | Latch On<br>Rising Edge     | Latch On<br>Rising Edge  | Latch On<br>Rising Edge | Latch On<br>Rising Edge | 0                   | 0               | 0              | 0                 |

| 3    | PGM      | 0                           | 0                        | 0                       | 0                       | 1                   | 1               | 1              | 1                 |

| 1    | A0       | 0/1                         | 0/1                      | 0/1                     | 0/1                     | 0                   | 1               | 0              | 1                 |

| 2    | A1       | 0/1                         | 0/1                      | 1                       | 0                       | 0                   | 0               | 1              | 1                 |

| 7    | RESET    | 0                           | 0                        | 1                       | 1                       | Z                   | Z               | Z              | Z                 |

| 8    | I/O (in) | 0/1                         | 0/1                      | 0/1                     | 0/1                     | Z                   | Z               | Z              | Z                 |

The  $\overline{PGM}$  signal, pin 3, controls the mode of operation (chip programming or smart card transaction) and must be set up accordingly prior to pull Chip Select (pin 6) Low.

**Table 2. Status Pin Logic Output**

| Name             | CS | PGM | A1 | A0 | Status Logic Level                                              |

|------------------|----|-----|----|----|-----------------------------------------------------------------|

| None             | Н  | Х   | Х  | Х  | No Chip Access                                                  |

| None             | L  | L   | Х  | Х  | Programming Mode, No Read Available                             |

| CARD PRESENT     | L  | Н   | L  | L  | Low: No Card Inserted<br>High: Card inserted                    |

| DC/DC            | L  | Н   | L  | Н  | Low: DC/DC Over Range<br>High: DC/DC Operates Normally          |

| Vbat             | L  | Н   | Н  | L  | Low: Vbat Within Range<br>High: Vbat Below Minimum range        |

| CRD_VCC Overload | L  | Н   | Н  | Н  | Low: CRD_VCC Voltage Below Minimum Range High: CRD_VCC in Range |

http://opsami.com

## Card VCC, Card CLOCK and Card Detection Polarity Programming

The CRD\_VCC and CLOCK\_IN programming options allows matching the system frequency with the card clock frequency, and to select 3.0 V or 5.0 V CRD\_VCC supply. The CRD\_DET programming option allows the usage of either Normally Open or Normally Close detection switch. Table 3 highlights the A0, A1,  $\overline{PGM}$  and I/O logic states for the possible options. **The default power up reset condition**

is state 1: asynchronous clock, ratio 1/1, CRD\_CLK active, CRD\_DET = Normally Open, CRD\_VCC = 3.0 V. All states are latched for each output variable in programming mode at the positive going slope of Chip Select  $\overline{[CS]}$  signal. It is the system designer's responsibility to set up the options needed to match the chip with the peripherals. In particular, when using Normally Close switch, the CRD\_DET polarity must be defined during the first cycles of the initialization.

Table 3. Card VCC, Card Clock and Card Detection Polarity Truth Table

| HEXA | CS | PWR_ON | PGM | RESET | <b>A1</b> | A0 | I/O | CRD_VCC | CRD_CLK      | CRD_DET                     | STATUS       |

|------|----|--------|-----|-------|-----------|----|-----|---------|--------------|-----------------------------|--------------|

| \$00 | L  | _      | L   | L     | L         | L  | L   | 3.0 V   | CLOCK_IN 1/1 | -                           | H (Note 13)  |

| \$01 | L  | -      | L   | L     | L         | L  | Н   | 3.0 V   | CLOCK_IN 1/2 | _                           | H (Note 13)  |

| \$02 | L  | -      | L   | L     | L         | Н  | L   | 3.0 V   | CLOCK_IN 1/4 | _                           | H (Note 13)  |

| \$03 | L  | -      | L   | L     | L         | Н  | Н   | 3.0 V   | CLOCK_IN 1/8 | _                           | H (Note 13)  |

| \$04 | L  | -      | L   | L     | Н         | L  | L   | 5.0 V   | CLOCK_IN 1/1 | _                           | H (Note 13)  |

| \$05 | L  | -      | L   | L     | Н         | L  | Н   | 5.0 V   | CLOCK_IN 1/2 | _                           | H (Note 13)  |

| \$06 | L  | -      | L   | L     | Н         | Н  | L   | 5.0 V   | CLOCK_IN 1/4 | _                           | H (Note 13)  |

| \$07 | L  | -      | L   | L     | Н         | Н  | Н   | 5.0 V   | CLOCK_IN 1/8 | _                           | H (Note 13)  |

| \$08 | L  | -      | L   | Н     | L         | L  | L   | -       | START        | _                           | H (Note 13)  |

| \$09 | L  | -      | L   | Н     | L         | L  | Н   | -       | STOP Low     | _                           | H (Note 13)  |

| \$0A | L  | -      | L   | Н     | L         | Н  | L   | -       | STOP High    | -                           | H (Note 13)  |

| \$0B | L  | -      | L   | Н     | L         | Н  | Н   | -       | Reserve      | -                           | H (Note 13)  |

| \$0C | L  | -      | L   | Н     | Н         | L  | L   | -       | -            | Normally Open<br>(Note 12)  | H (Note 13)  |

| \$0D | L  | -      | L   | Н     | Н         | L  | Н   | -       | -            | Normally Close<br>(Note 12) | H (Note 13)  |

| \$0E | L  | -      | L   | Н     | Н         | Н  | L   | -       | -            | Normally Close<br>(Note 12) | H (Note 13)  |

| \$0F | L  | -      | L   | Н     | Н         | Н  | Н   | -       | -            | Normally Close<br>Note 12)  | H (Note 13)  |

| \$10 | L  | -      | Н   | Z     | L         | L  | Z   | -       | -            | _                           | Card Present |

| \$12 | L  | 1      | Н   | Z     | L         | Н  | Z   | -       | -            | _                           | DC/DC status |

| \$14 | L  | -      | Н   | Z     | Н         | L  | Z   | -       | -            | _                           | Vbat         |

| \$16 | L  | 1      | Н   | Z     | Н         | Н  | Z   | -       | -            | _                           | CRD_VCC      |

<sup>9.</sup> The programmed conditions are latched upon the Chip Select (CS, pin 6) positive going transient.

<sup>10.</sup> Card clock integrity is guaranteed no spikes whatever be the frequency switching.

<sup>11.</sup> The STATUS register is not affected when the NCN6000 operates in any of the programming functions.

<sup>12.</sup> The CRD\_VCC and CRD\_CLK are not affected when the NCN6000 operates outside their respective decoded logic address.

<sup>13.</sup> The High Level on STATUS in registors \$00 to \$0F, inclusive, having being implemented to reduce current comsumption but have no other meanings.

<sup>14.</sup> At turn on, the NCN6000 is initialized with CRD\_VCC = 3.0V, CLOCK\_IN Ratio = 1/1, CRD\_CLK = START, CRD\_DET = Normally Open.

#### DC/DC Converter and Card Detector Status

The NCN6000 status can be polled when  $\overline{CS} = L$ . Please consult Figures 4 and 5 for a description of input and output signals. The status message is described in Table 4.

Note: in order to cope with a start up under low battery condition, the Vbat OK message uses a negative logic as depicted here below.

Table 4. Card and DC/DC Status Output

| PGM  | A1 | A0 | STATUS | Message                       |

|------|----|----|--------|-------------------------------|

| HIGH | L  | L  | LOW    | No Card                       |

| HIGH | L  | L  | HIGH   | Card Present                  |

| HIGH | L  | Н  | LOW    | DC/DC Converter<br>Overloaded |

| HIGH | L  | Н  | HIGH   | DC/DC Converter OK            |

| HIGH | Н  | L  | LOW    | Vbat OK                       |

| HIGH | Н  | L  | HIGH   | Vbat Undervoltage             |

| HIGH | Н  | Н  | HIGH   | CRD_VCC OK                    |

| HIGH | Н  | Н  | LOW    | CRD_VCC Undervoltage          |

The STATUS pin provides a feedback related to the detection of the card, the state of the DC/DC converter, the Vbat undervoltage and CRD\_VCC undervoltage situations. When  $\overline{PGM} = H$ , the STATUS pin returns a High if a card is detected present, a Low being asserted if there is no card inserted. In any case, the external card is not automatically powered up. When the external MPU asserts PWR\_ON = H, together with  $\overline{CS} = L$ , the CRD\_VCC supply is provided to the card and the state of the DC/DC converter, the Vbat and the CRD\_VCC can be polled through the STATUS pin.

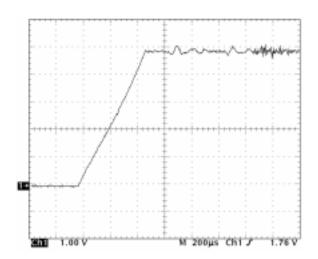

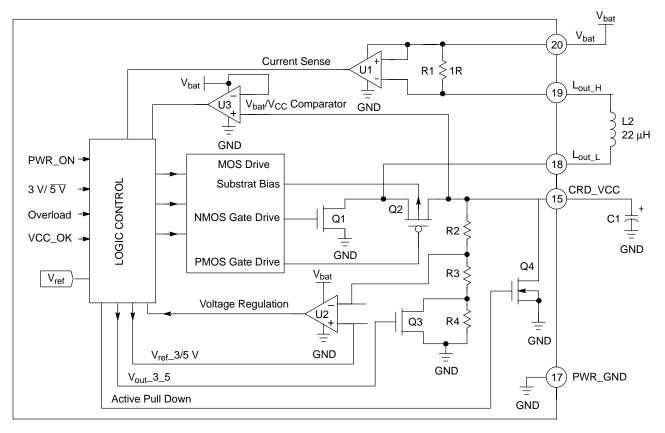

## **Card Power Supply Timing**

At power up, the CRD\_VCC power supply rise time depends upon the current capability of the DC/DC converter associated with the external inductor L1 and the reservoir capacitor connected across CRD\_VCC and GROUND.

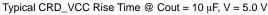

On the other hand, at turn off, the CRD\_VCC fall time depends upon the external reservoir capacitor and the peak current absorbed by the internal CMOS transistor built across CRD\_VCC and GROUND. These behaviors are depicted in Figure 6. Since these parameters have finite values, depending upon the external constraints, the designer must take care of these limits if the  $t_{ON}$  or the  $t_{OFF}$  provided by the data sheets does not meet his requirements.

Typical CRD\_VCC Fall Time @ Cout = 10  $\mu$ F, V = 5.0 V

Figure 6. Card Power Supply Turn ON and OFF Timing

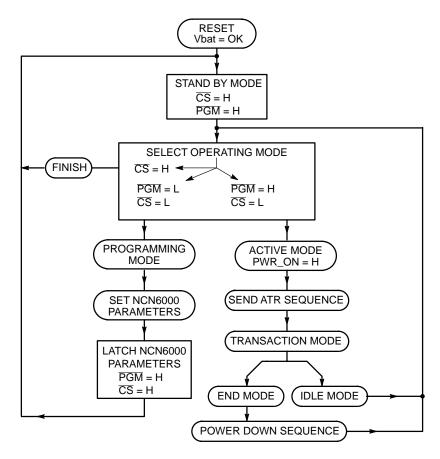

## **Basic Operating Modes Flow Chart**

The NCN6000 brings all the functions necessary to handle data communication between a host computer and the smart card. The built—in Chip Select pin provides a simple way to share the same MPU bus with several card interface. On top of that, the logic control are derived from specific pins, avoiding the risk of mixing up the operation when the interface is controlled by a low end microcontroller.

During the transaction operation, the external MPU takes care of whatever is necessary to he data on the single bidirectional I/O line. Leaving aside the DC–DC control and associated failures, the NCN6000 does not take any further responsibility in the data transaction.

When the chip operates in the programming mode, the NCN6000 provide a flexible access to set up the CRD\_VCC voltage, the CRD\_CLK and the CRD\_DET smart card signals.

The external micro controller takes care of the smart card transaction and shall handle the interface accordingly.

Figure 7. Operating Modes Flow Chart

#### Standby Mode

The Standby Mode allows the NCN6000 to detect a card insertion, keeping the power consumption at a minimum. The power supply CRD\_VCC is not applied to the card, until the external controllers set PWR\_ON = H with  $\overline{\text{CS}}$  = L.

| Standby I<br>Logic Cor |     | Card Output:  |

|------------------------|-----|---------------|

| CS                     | = H | CRD_VCC = 0 V |

| PWR_ON                 | = H | CRD_CLK = L   |

| A0                     | = Z | $CRD_RST = L$ |

| A1                     | = Z | $CRD_IO = L$  |

| PGM                    | = Z |               |

| I/O                    | = Z |               |

| RESET                  | = Z |               |

When a card is inserted, the internal logic filters the signal present pin 11, then asserts the  $\overline{INT}$  pin to Low if the pulse applied to CRD\_DET is longer than 150  $\mu s$ . The external MPU shall run whatever is necessary to handle the card.

The  $\overline{\text{INT}}$  is cleared (return to High) when a positive going transition is asserted to either the  $\overline{\text{CS}}$  or to the PWR\_ON signal logically combined with Chip Select = Low.

#### **Programming Mode**

The programming mode allows the configuration of the card power supply, card clock and Card Detection input logic polarity. These signals (CRD\_VCC, CRD\_CLK and CRD\_DET) are described in the pin description paragraph associated with Tables 1 and 3 and Figures 4 and 8.

| Programming Mode Logic Conditions:              |                                              | Card Output:                                                                                       |

|-------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|

| CS<br>PWR_ON<br>A0<br>A1<br>PGM<br>I/O<br>RESET | = L<br>= L<br>= H/L<br>= H/L<br>= L<br>= L/H | CRD_VCC = 0 V CRD_CLK = L CRD_RST = L CRD_IO = H/L depending upon the previous I/O pin logic state |

The I/O and  $\overline{RESET}$  pins are not connected to the smart card and become logic inputs to control the NCN6000 programming sequence. The programmed values are latched upon transition of  $\overline{CS}$  from Low to High,  $\overline{PGM}$  being Low during the transition.

When a programming mode is validated by a Chip Select negative going transient, the mode is latched and  $\overline{PGM}$  can be released to High. This latch is automatically reset when  $\overline{CS}$  returns to High.

The logic input signals can be set simultaneously, or one bit a time (using either a STAA or a BSET function), the key point being the minimum delay between the shorter bit and the Chip Select pulse. The programmed value is latched into the NCN6000 register on the  $\overline{\text{CS}}$  positive going edge.

**Figure 8. Minimum Programming Timings**

#### **Active Mode**

In the active mode, the NCN6000 is selected by the external MPU and the STATUS pin can be polled to get the status of either the DC/DC converter or the presence of the card (inserted or not valid). The power is not connected to the card:  $CRD_VCC = 0$  V.

| Active Mo                            |                                                                      | Card Outp                               | out: |

|--------------------------------------|----------------------------------------------------------------------|-----------------------------------------|------|

| CS PWR_ON A0 A1 PGM I/O RESET STATUS | = L<br>= L<br>= L<br>= H<br>= Z<br>= Z<br>= L/H is Card<br>Inserted? | CRD_VCC<br>CRD_CLK<br>CRD_RST<br>CRD_IO | = L  |

The Chip Select pulse  $[\overline{CS}]$  will automatically clear the previously asserted  $\overline{INT}$  signal upon the positive going transition.

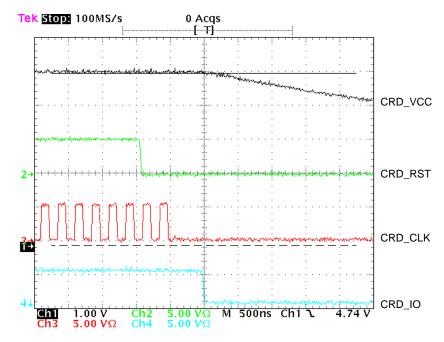

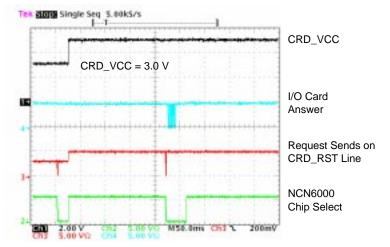

If a card is present, the MPU shall activate the DC/DC converter by asserting PWR\_ON = H. The NCN6000 will automatically run a power up sequence when the CRD\_VCC reaches the undervoltage level (either  $V_{C5H}$  or  $V_{C3H}$ , depending upon the CRD\_VCC voltage supply programmed). The CRD\_IO, CRD\_RST and CRD\_CLK pins are validated, according to the ISO7816–3 sequence. The interface is now in transaction mode and the system is ready for data exchange through the I/O and  $\overline{RESET}$  lines. At any time, the micro controller can change the CRD\_CLK frequency and mode, or the CRD\_VCC value as determined by the card being in use.

#### **Transaction Mode**

During the transaction mode, the NCN6000 maintains power supply and clock signal to the card. All the signal levels related with the card are translated as necessary to cope with the MPU and the card.

The DC/DC converter status and the Vbat state can be monitored on the STATUS by using the A0 and A1 logic inputs as depicted Tables 3 and 4.

#### **Transaction Mode Logic Conditions: Card Output:** CS $CRD_VCC = 3.0 \text{ or } 5.0 \text{ V}$ = 1 $PWR_ON = H$ CRD\_CLK = CLOCK Α0 = H $CRD_RST = H/L$ = DATA CRD\_IO Α1 = HPGM **TRANSFER** = H I/O = DATA **TRANSFER** RESET = H/L= L/H DC/DC STATUS status: Fail/Pass?

To make sure the data are not polluted by power losses, it is recommended to check the state of  $CRD\_VCC$  before launching a new data transaction. Since  $\overline{CS} = L$ , this is achieved by forcing bits A0 and A1 according to Table 4, and reading the STATUS pin 5.

#### **Idle Mode**

The idle mode is used when a card is powered up (CRD VCC = Vcc), without communication on going.

| Idle Mode<br>Logic Cor            | nditions:                       | Card Output:                                                                   |

|-----------------------------------|---------------------------------|--------------------------------------------------------------------------------|

| PWR_ON A0 A1 PGM I/O RESET STATUS | = H<br>= H<br>= H<br>= Z<br>= H | CRD_VCC = 3.0 or 5.0 V CRD_CLK = CLOCK active or L or H CRD_RST = H CRD_IO = Z |

|                                   | register results                |                                                                                |

In addition, the CRD\_CLK signal can be stopped, as depicted in Tables 3 and 4, to minimize the current consumption of the external smart card, leaving CRD\_VCC active.

#### **Power Down Operation**

The power down mode can be initiated by either the external MPU (pulling PWR\_ON = L) or by one of the internal error condition (CRD\_VCC overload or Vbat Low). The communication session is terminated immediately, according to the ISO7816–3 sequence. On the other hand, the MPU can run the Standby mode by forced  $\overline{\text{CS}}$  = H.

When the card is extracted, the interface shall detect the operation and run the Power Shut Off of the card as described by the ISO/CEI 7816–3 sequence depicted here after:

ISO7816–3 sequence:

- ⇒ Force RST to Low

- ⇒ Force CLK to Low, unless it is already in this state ⇒ Force CRD\_IO to Low

- ⇒ Shut Off the CRD\_VCC supply

Since the internal digital filter is activated for any card insertion or extraction, the physical power sequence will be activated 150 µs maximum after the card has been extracted. Of course, such a delay does not exist when the MPU launch the power down intentionally.

The time delay between each negative going signal is 500 ns typical (Figure 10).

http://opcomi.com

Figure 9. Typical Power Down Sequence in the NCN6000 Interface

Figure 10. Power Down Sequence Details

## **Card Detection**

The card detector circuit provides a 500 k $\Omega$  pull up resistor to bias the CRD\_DET pin, yielding a logic High when the pin is left open (assuming a NO switch). The internal logic associated with pin 11 provides an automatic selection of the slope card detection, depending upon the polarity set by the external MPU. At start up, the CRD\_DET is preset to cope with Normally Open switch. When a Normally Close switch is used in the card socket, it is mandatory to program the NCN6000 chip during the initialization sequence, otherwise the system will not start if a card was previously inserted. Table 3 gives the programming code for such a function. The next lines provide a typical assembler source to handle this CRD\_DET Normally Close polarity:

Smart

EQU

\$20

; NCN6000 Physical \overline{CS} Address

LDX

#\$1000

; Offset

LDAA

#\$09

; I/O = H, A0 = A1 = L, \overline{RESET} = H

STAA smart, X

; Set CRD\_DET = Normally Closed

Switch

The CRD\_DET polarity can be updated at any time, during the Program Mode sequence ( $\overline{PGM} = L$ ), but, generally speaking, is useless since the switch does not change during the usage of the considered module. On the other hand, the card detection switch shall be connected across pin 11 and ground, for any polarity selected.

The transition presents pin 11, whatever be the polarity, is filtered out by the internal digital filter circuit, avoiding false interrupt. In addition to the minimum internal 50 µs timing, the MPU shall provide an additional delay to cope with the mechanical stabilization of the card interface (typically 3 ms), prior to valid the CRD\_VCC supply.

When a card is inserted, the detector circuit asserts  $\overline{\text{INT}} = \text{Low}$  as depicted before. When the NCN6000 detects a card extraction, the power down sequence is activated, regardless of the PWR\_ON state, and the  $\overline{\text{INT}}$  pin is asserted Low. It is up to the external MPU to clear this interrupt by forcing a chip select pulse as depicted in Figure 5.

The 75  $\mu$ s delay represent the digital filter built—in the NCN6000 chip being used for the characterization. Any pulse shorter than this delay does not generate an interrupt. However, to guarantee an interrupt will be generated, the CRD\_DET signal must be longer than 150  $\mu$ s as defined by the specification.

The Chip Select pulse is generated by the external micro controller, the minimum pulse width being  $2\,\mu s$  to make sure the card is detected.

The oscillogram, Figure 11, depicts the behavior for a Normally Open switch, the delay existing between the interrupt negative going state and the  $\overline{CS}$  being Low comes from the particular software latency existing in this particular MPU.

Figure 11. Card Insertion Detection and Interrupt Signals

Figure 12. Card Extraction Detection and Interrupt Signals

When the card is extracted, the CRD\_DET signal generates an interrupt, assuming the positive pulse width is longer than the digital filter. The oscillogram, Figure 12, depicts the behavior for a Normally Open switch.

Note: since the internal pull up resistor is relatively high (500 k $\Omega$  typical), one must use a 10 M $\Omega$  input impedance probe to read this signal.

Figure 13. Interrupt Acknowledgement During a Card Insertion Detection Sequence

The interrupt signal, provided pin 9, is cleared by a positive going Chip Select signal as depicted by the oscillogram, Figure 13. The  $\overline{\text{CS}}$  pulse width is irrelevant, as long as it is larger than 2.0  $\mu$ s, to activate a different sequence. Leaving the interrupt signal Low has no influence

on the internal behavior of the NCN6000, but will be automatically cleared when the DC/DC will be activated by the MPU ( $\overline{\text{CS}}$ =L, PWR\_ON = Positive High transition)

#### **Power Management**

The purpose of the power management is to activate the circuit functions needed to run a given mode of operation, yielding a minimum current consumption on the Vbat supply. In the Standby mode ( $PWR\_ON = L$ ), the power management provides energy to the card detection circuit only. All the card interface pins are forced to ground potential.

In the event of a power up request coming from the external MPU (PWR\_ON = H,  $\overline{CS}$  = L), the power manager starts the DC/DC converter.

When the CRD\_VCC voltage reaches the programmed value (3.0 V or 5.0 V), the circuit activates the card signals according to the following sequence:

```

CRD_VCC

⇒CRD_IO

⇒CRD_CLK

⇒CRD_RST

```

The logic level of the data lines are asserted High or Low, depending upon the state forced by the external MPU, when the start up sequence is completed. Under no situation the NCN6000 shall launch automatically a smart card ATR sequence. Assuming PWR\_ON = H, the CRD\_VCC voltage

is maintained whatever be the logic level presents on Chip Select, pin 6.

At the end of the transaction, asserted by the MPU (PWR\_ON = L,  $\overline{CS}$  = L), or under a card extraction, the ISO7816–3 power down sequence takes place:

When  $\overline{CS} = H$ , the bi–directional I/O line (pins 8 and 15) is forced into the High impedance mode to avoid signal collision with any data coming from the external MPU.

The CRD\_VCC voltage is controlled by means of  $\overline{CS}$  and PWR\_ON logic signal as depicted Figure 14. The PWR\_ON logic level define the CRD\_VCC voltage status, the amplitude being the one pre programmed into the chip.

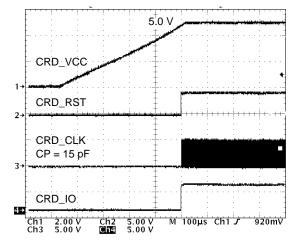

In order to avoid uncontrolled command applied to the smart card, the NCN6000 internal logic circuit, together with the Vbat monitoring, clamps the card outputs until the CRD\_VCC voltage reaches the minimum value. During the CRD\_VCC slope, all the card outputs are kept Low and no spikes can be write to the smart card. The oscillogram on the right hand side is a magnification of the curves given on the opposite side.

Figure 14. Card Power Supply Control

Figure 15. Smart Card Signals Sequence at Power On

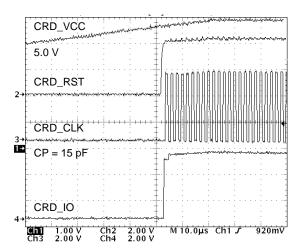

## **Vbat Supply Voltage Monitoring**

The built–in comparator, associated with the band gap reference, continuously monitors the +Vbat input. During the start up, all the NCN6000 functions are deactivated and no data transfer can take place. When the +Vbat voltage rises above 2.35 V (typical), the chip is activated and all the functions becomes available. The typical behavior is provided here after Figure 16. At this point, the internal Power On Reset signal is activated (not accessible externally) and all the logic signals are forced into the states as defined by Table 3.

If the +Vbat voltage drops below 2.25 V (typical) during the operation, the NCN6000 generate a Power Down sequence and is forced in a no operation mode. The built–in 100 mV (typical) hysteresis avoids unstable operation when the battery voltage slowly varies around the 2.30 V.

On the other hand, the micro controller can read the STATUS signal, pin 5, to control the state of the battery prior to launch either a NCN6000 programming or an ATR sequence (Table 4).

Note: Drawing is not to scale and voltages are typical. See specifications data for details.

Figure 16. Typical Vbat Monitoring

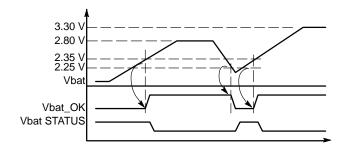

## **DC/DC Converter Operation**

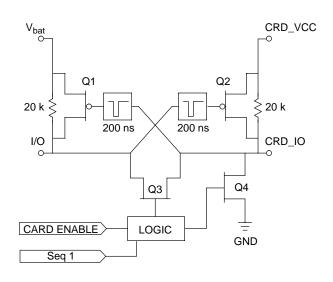

The built–in DC/DC converter is based on a modified boost structure to cover the full battery and card operating voltage range. The built–in battery voltage monitor provides an automatic system to accommodate the mode of operation whatever be the Vbat and CRD\_VCC voltages. Comparator U3/Figure 17 tracks the two voltages and set up the operating mode accordingly.

Figure 17. Basic DC/DC Structure

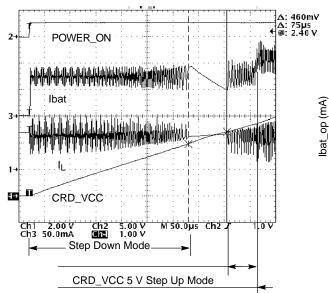

When the input voltage Vbat is lower than the programmed CRD\_VCC, the system operates under the boost mode, providing the voltage regulation and current limit to the smart card. In this mode, the external inductor, typically 22 µH, stores the energy to drive the +5.0 V card supply from the external low voltage battery. The oscillogram, Figure 18, depicts the DC/DC behavior under these two modes of operation.

Beside the DC/DC converter, NMOS Q4 provides a low impedance to ground during the Power Down sequence, vielding the 250 us maximum switch time depicted in the data sheet.

Figure 18. DC/DC Operating Modes

When the input voltage Vbat is higher than the programmed CRD VCC, the system operates under a step down mode, yielding the voltage regulation and current limit identical to the boost mode. In this case, the built-in structure turns Off Q1 and inverts the Q2 substrate bias to control the current flowing to the load. These operations are fully automatic and transparent for the end user.

The High and Low limits of the current flowing into the external inductor L1 are sensed by the operational amplifier U1 associated with the internal shunt R1. Since this shunt resistor is located on the hot side of the inductor, the device reads both the charge and discharge of the inductor, providing a clean operation of the converter.

In order to optimize the DC/DC power conversion efficiency, it is recommended to use external inductor with  $R < 2.0 \Omega$ .

The output capacitor C1 stores the energy coming from the converter and smooths the CRD\_VCC voltage applied to the external card. At this point, care must be observed, beside the micro farad value, to select the right type of capacitor. According to the capacitor's manufacturers, the internal ESR can range from a low  $10 \text{ m}\Omega$  to more than  $3.0 \Omega$ , thus yielding high losses during the DC/DC operation, depending upon the technology used to build the capacitor.

DC Operating Current @ CRD\_VCC = 5.0 V

Figure 19. Typical DC Operating Current

The standard electrolytic capacitors have the low cost advantage for a relative high micro farad value, but have poor tolerance, high leakage current and high ESR.

The tantalum type brings much lower leakage current together with high capacity value per volume, but cost can be an issue and ESR is rarely better than 500 m $\Omega$ .

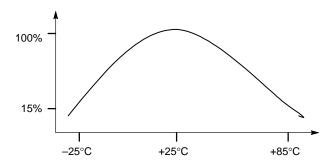

The new ceramic type have a very low leakage together with ESR in the 50 m $\Omega$  range, but value above 10  $\mu$ F are relatively rare. Moreover, depending upon the low cost ceramic material used to build these capacitors, the thermal coefficient can be very bad, as depicted in Figure 20. The X7R type is highly recommended to achieve low voltage ripple.