捷多邦,专业PCB打样工厂,24小时加急

出货 This version: Mar. 1999

Preliminary

# **OKI** Semiconductor

## **MSM9565**

IC for FM Multiplex Data Demodulation

## GENERAL DESCRIPTION

The MSM9565 is an IC which demodulates FM character multiplex signals in the DARC (Data Radio Channel)<sup>\*1</sup> format to obtain digital data. The MSM9565 operates at 3.3 V.

DZSC.COM

The MSM9565 contains on one chip a band pass filter using a switched capacitor filter (SCF) and a group of circuits including frame memory, a frame synchronization circuit, and an error correction circuit.

By connecting an external FM receiver and memory for temporary data storage, and microcontroller, a system for obtaining digital data can easily be constructed.

The FM multiplex demodulation ICs, the MSM9500-series devices, are configured with minimum functions; so they will, by changing the software of the external microcontroller, be able to respond flexibly to the many FM multiplex broadcast services that are going to come about in the future.

The MSM9565 is best suited to radios and information processing devices that support DARC FM multiplex broadcasting. It is also best suited to car radios and car navigation systems that support VICS (Vehicle Information and Communication System), which started its service in 1996.

\*1 DARC is a registered trademark of NHK Engineering Services.

Any manufacturer who has a contract with NHK Engineering Services can produce and sell electronic equipment utilizing the DARC technology.

Any manufacturer who has a contract with NHK Engineering Services and VICS Center can produce and sell electronic equipment utilizing the VICS technology.

## FEATURES

- Built-in VICS-supporting descrambler

- Built-in two receive channels including main channel and sub-channel (receives both VICS and D-GPS simultaneously)

- Pin compatible with MSM9553/MSM9555

- Internal frame memory enables automatic error correction.

- Built-in bandpass filter (SCF)

- Built-in block synchronization circuit and frame synchronization circuit

- Setting of the number of synchronization protection steps can be changed.

- Data clocks are regenerated by digital PLL.

- 1T delay detection

- Built-in vertical and horizontal error correction circuits

- Built-in layer 4 and layer 2 CRC processing circuits

- Parallel interface with microcontroller

- Clock output for external devices (64 kHz to 8.192 MHz variable)

- Compatible with the international standard frame formats A (real time block also supported), B, C

- Power supply: 3.0 V to 3.6 V

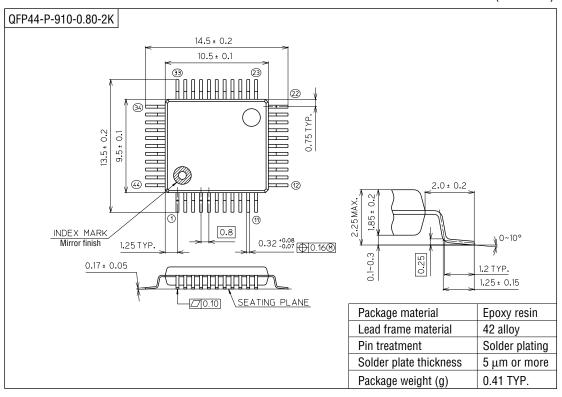

- Package: 44-pin plastic QFP (QFP44-P-910-0.80-2K) (Product name: MSM9565GA)

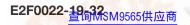

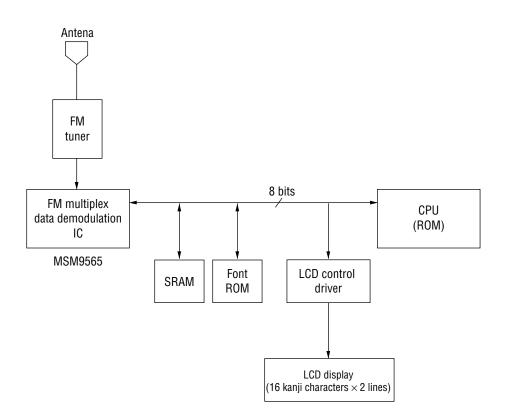

## **BLOCK DIAGRAM**

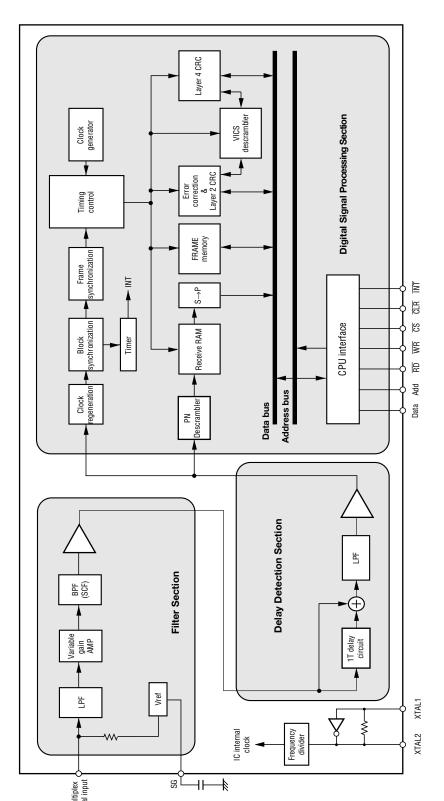

## **PIN CONFIGURATION (TOP VIEW)**

NC : No-connection pin

44-Pin Plastic QFP

## **PIN DESCRIPTIONS**

| Function                | Pin      | Symbol            | Туре | Description                                                                                                        |  |

|-------------------------|----------|-------------------|------|--------------------------------------------------------------------------------------------------------------------|--|

| Microcontroller         | 16       | WR                | I    | Write signal to internal register.                                                                                 |  |

| Interface               | 18       | RD                | I    | Read signal to internal register.                                                                                  |  |

|                         | 15       | ĪNT               | 0    | Interrupt signal to microcontroller. "L": An interrupt is generated.                                               |  |

|                         | 31       | CS                | I    | Chip select signal.<br>"L": Read, write, and data bus signals become active.                                       |  |

|                         | 40       | CLR               | Ι    | "L" : the internal registers are initialized and the device enters power down mode.                                |  |

|                         | 33 to 38 | A0 to A5          | I    | Address signal to internal register.                                                                               |  |

|                         | 19 to 26 | DB0 to DB7        | I/0  | Data bus signal to internal register.                                                                              |  |

| Tuner                   | 6        | AIN               | I    | FM multiplex signal input.                                                                                         |  |

| Interface               | 5        | SG                | 0    | Analog reference voltage output pin. Connect a capacitor between this pin and analog ground to prevent noise.      |  |

| Analog<br>Section Test  | 1        | MON               | 0    | Analog section waveform monitoring pin. The analog bl<br>mode setting is specified by the analog control register. |  |

|                         | 2        | ADETIN            | I    | Digital signal input pin for testing analog section.                                                               |  |

| Digital<br>Section Test | 8 to 14  | MOUTO to<br>MOUT6 | 0    | Digital section test signal output and monitor output pins.                                                        |  |

| Clock                   | 29       | XTAL1             | I    | 8.192 MHz crystal connection pin.                                                                                  |  |

|                         | 30       | XTAL2             | 0    | 8.192 MHz crystal connection pin.                                                                                  |  |

|                         | 32       | XOUT              | 0    | Pin for supply of 64 kHz to 8.192 MHz variable clock to the outside.                                               |  |

|                         | 7        | XOUTC             | I    | XOUT output control pin.<br>"L" = Clock output, "H" = Output disabled. Pulled up internally.                       |  |

| Power<br>Supply         | 3        | AV <sub>DD</sub>  | _    | Analog section power supply pin.                                                                                   |  |

|                         | 4        | AGND              | _    | Analog ground pin.                                                                                                 |  |

|                         | 28       | DV <sub>DD</sub>  | _    | Digital section power supply pin.                                                                                  |  |

|                         | 27       | DGND              | _    | Digital ground pin.                                                                                                |  |

| Parameter                 | Symbol           | Condition              | Rating                         | Unit |  |

|---------------------------|------------------|------------------------|--------------------------------|------|--|

| Power Supply Voltage      | AV <sub>DD</sub> |                        | 0.2 to .7.0                    |      |  |

| Power Supply Voltage      | DV <sub>DD</sub> | $AV_{DD} = DV_{DD}$    | –0.3 to +7.0                   | V    |  |

| Input Voltage             | VI               | Ta = 25°C              | -0.3 to AV <sub>DD</sub> + 0.3 |      |  |

| Output Voltage            | Vo               |                        | -0.3 to DV <sub>DD</sub> + 0.3 |      |  |

| Maximum Dawar Dissinction | Р                | Ta = 25°C, per package | 400                            | m\\/ |  |

| Maximum Power Dissipation | PD               | Ta = 25°C, per output  | 50                             | mW   |  |

| Storage Temperature       | T <sub>STG</sub> | —                      | -55 to +150                    | °C   |  |

#### **ABSOLUTE MAXIMUM RATINGS**

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                     | Symbol                                | Condition                             | Condition Range      |                  | Applied Pin      |

|-------------------------------|---------------------------------------|---------------------------------------|----------------------|------------------|------------------|

| Dower Cupply Voltage          | $AV_{DD}$                             |                                       | 3.0 to 3.6           | V                | AV <sub>DD</sub> |

| Power Supply Voltage          | DV <sub>DD</sub>                      | $AV_{DD} = DV_{DD}$                   | 3.0 10 3.0           | v                | DV <sub>DD</sub> |

| Cructal Occillation Frequency | f <sub>XTAL</sub>                     |                                       | 9 100 MUIT . 100 ppm |                  | XTAL1,           |

| Crystal Oscillation Frequency |                                       | _                                     | 8.192 MHz ±100 ppm   |                  | XTAL2            |

|                               | V <sub>AIN</sub> *                    | Variable amplifier gain: $\times$ 1   | 0.6 to 0.9           |                  | AIN              |

| FM Multiplex Signal Input     |                                       | Variable amplifier gain: $\times 1.5$ | 0.4 to 0.6           | V                |                  |

| Voltage                       |                                       | Variable amplifier gain: $\times 2$   | 0.3 to 0.4           | V <sub>P-P</sub> |                  |

|                               |                                       | Variable amplifier gain: $\times 3$   | 0.2 to 0.3           |                  |                  |

| Operating Temperature         | erating Temperature T <sub>op</sub> — |                                       | -40 to +85           | °C               | _                |

- \* Peak values (a total voltage of the following signals (a) to (c)) of composite signals including multiplex signals.

- (a) Voice signals (100% modulated: voice max.)

- (b) Pilot signal

- (c) FM multiplex signals (10%: LMSK max.)

The maximum amplitude of an input signal is in the range of 0.9  $V_{P-P}$  in which the internal IC circuit is not saturated.

Therefore, multiplex signals of up to  $0.9 V_{P-P}$  can be input if only multiplex signals (excluding composite signals) are input from a signal generator.

## **ELECTRICAL CHARACTERISTICS**

| Parameter                 | Symbol          | Condition                                               | Min. | Тур. | Max. | Unit | Applied Pin                            |

|---------------------------|-----------------|---------------------------------------------------------|------|------|------|------|----------------------------------------|

|                           | I <sub>DD</sub> | When operating, no load                                 |      | 14   | 28   | mA   | AV <sub>DD</sub> ,<br>DV <sub>DD</sub> |

| Supply Current            |                 | f = 8.192 MHz                                           |      |      |      |      |                                        |

| Supply Current            |                 | When in power down mode,                                |      | _    | 50   | μA   |                                        |

|                           |                 | no load                                                 |      |      |      |      |                                        |

| BPF Pass Band Attenuation | GAIN1           | 72 to 80 kHz<br>Variable gain amplifier<br>gain: 0 dB   | _    | _    | 3.0  | dB   | MON                                    |

| BPF Stop Band Attenuation | GAIN2           | 0 to 53 kHz<br>Variable gain amplifier<br>gain: 0 dB    | 50   | _    | _    | dB   | MON                                    |

| BPF Stop Band Attenuation | GAIN3           | 100 to 500 kHz<br>Variable gain amplifier<br>gain: 0 dB | 50   |      |      | dB   | MON                                    |

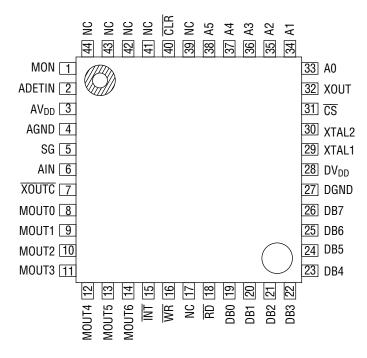

- (Note 1) Use a tantalum capacitor.

- (Note 2) The AV<sub>DD</sub> and  $DV_{DD}$  should have different paths, respectively.

- (Note 3) The AGND and tuner ground should use the same ground.

## **APPLICATION CIRCUIT EXAMPLE**

## PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, TQFP, LQFP, SOJ, QFJ (PLCC), SHP, and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person on the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.