*Advance Information*

**1M Late Write HSTL**

The MCM69R536/618 is a 1 megabit synchronous late write fast static RAM designed to provide high performance in secondary cache, ATM switch, Telecom, and other high speed memory applications. The MCM69R618 organized as 64K words by 18 bits, and the MCM69R536 organized as 32K words by 36 bits wide are fabricated in Motorola's high performance silicon gate BiCMOS technology.

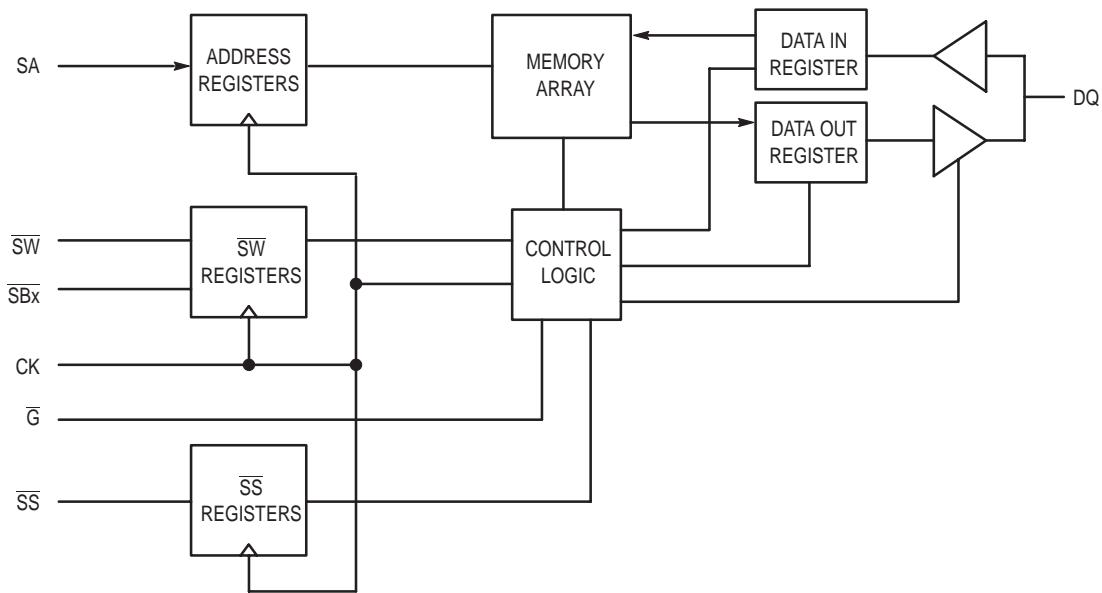

The differential CK clock inputs control the timing of read/write operations of the RAM. At the rising edge of the CK clock all addresses, write enables, and synchronous selects are registered. An internal buffer and special logic enable the memory to accept write data on the rising edge of the CK clock a cycle after address and control signals. Read data is driven on the rising edge of the CK clock also.

The RAM uses HSTL inputs and outputs. The adjustable input trip-point ( $V_{ref}$ ) and output voltage ( $V_{DDQ}$ ) gives the system designer greater flexibility in optimizing system performance.

The synchronous write and byte enables allow writing to individual bytes or the entire word.

The impedance of the output buffers is programmable allowing the outputs to match the impedance of the circuit traces which reduces signal reflections.

- Byte Write Control

- Single 3.3 V + 10%, - 5% Operation

- HSTL – I/O (JEDEC Standard JESD8-6 Class 1 Compatible)

- HSTL – User Selectable Input Trip-Point

- HSTL – Compatible Programmable Impedance Output Drivers

- Register to Register Synchronous Operation

- Asynchronous Output Enable

- Boundary Scan (JTAG) IEEE 1149.1 Compatible

- Differential Clock Inputs

- Optional x18 or x36 organization

- MCM69R536/618-5 = 5 ns

MCM69R536/618-6 = 6 ns

MCM69R536/618-7 = 7 ns

MCM69R536/618-8 = 8 ns

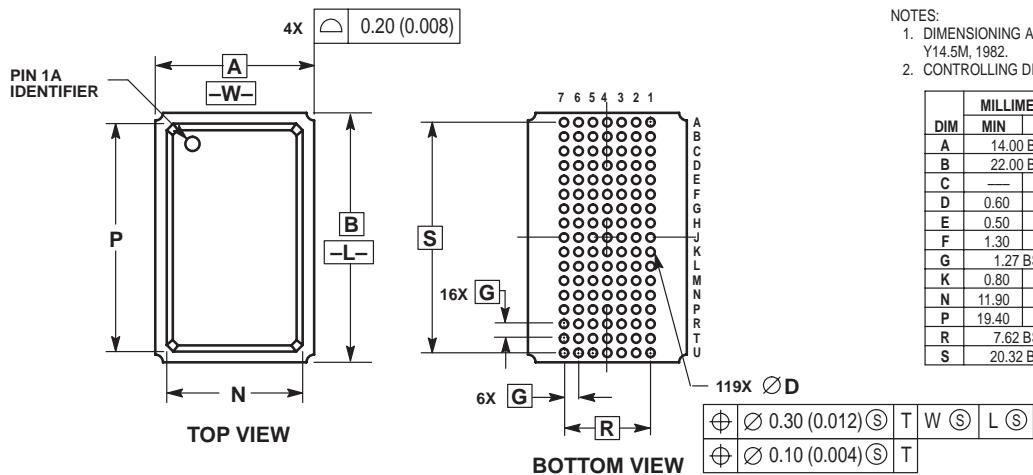

- 119 Bump, 50 mil (1.27 mm) Pitch, 14 mm x 22 mm Plastic Ball Grid Array (PBGA) Package

**MCM69R536**

**MCM69R618**

**ZP PACKAGE**

**PBGA**

**CASE 999-01**

### FUNCTIONAL BLOCK DIAGRAM

### PIN ASSIGNMENTS

#### TOP VIEW

**MCM69R536**

|   | 1                | 2   | 3               | 4               | 5               | 6               | 7                |

|---|------------------|-----|-----------------|-----------------|-----------------|-----------------|------------------|

| A | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| B | V <sub>DDQ</sub> | SA  | SA              | NC              | SA              | SA              | V <sub>DDQ</sub> |

| C | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| D | NC               | NC  | NC              | NC              | NC              | NC              | NC               |

| E | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| F | NC               | SA  | SA              | V <sub>DD</sub> | SA              | SA              | NC               |

| G | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| H | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| J | DQc              | DQc | V <sub>SS</sub> | ZQ              | V <sub>SS</sub> | DQb             | DQb              |

| K | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| L | DQc              | DQc | V <sub>SS</sub> | SB <sub>c</sub> | NF              | SB <sub>b</sub> | DQb              |

| M | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| N | DQc              | DQd | V <sub>SS</sub> | CK              | V <sub>SS</sub> | DQa             | DQa              |

| P | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| R | V <sub>DDQ</sub> | DQd | V <sub>SS</sub> | SW              | V <sub>SS</sub> | DQa             | V <sub>DDQ</sub> |

| T | ○                | ○   | ○               | ○               | ○               | ○               | ○                |

| U | NC               | SA  | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DD</sub> | SA              | NC               |

|   | V <sub>DDQ</sub> | TMS | TDI             | TCK             | TDO             | NC              | V <sub>DDQ</sub> |

**MCM69R618**

|   | 1                | 2   | 3               | 4               | 5               | 6   | 7                |

|---|------------------|-----|-----------------|-----------------|-----------------|-----|------------------|

| A | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| B | V <sub>DDQ</sub> | SA  | SA              | NC              | SA              | SA  | V <sub>DDQ</sub> |

| C | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| D | NC               | NC  | NC              | NC              | NC              | NC  | NC               |

| E | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| F | NC               | SA  | SA              | V <sub>DD</sub> | SA              | SA  | NC               |

| G | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| H | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| J | DQb              | NC  | V <sub>SS</sub> | ZQ              | V <sub>SS</sub> | DQa | NC               |

| K | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| L | DQb              | NC  | V <sub>SS</sub> | NF              | V <sub>SS</sub> | DQa | NC               |

| M | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| N | V <sub>DDQ</sub> | DQb | V <sub>SS</sub> | SW              | V <sub>SS</sub> | NC  | V <sub>DDQ</sub> |

| P | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| R | NC               | DQb | V <sub>SS</sub> | CK              | V <sub>SS</sub> | NC  | DQa              |

| T | ○                | ○   | ○               | ○               | ○               | ○   | ○                |

| U | V <sub>DDQ</sub> | TMS | TDI             | TCK             | TDO             | NC  | V <sub>DDQ</sub> |

## MCM69R536 PIN DESCRIPTIONS

| PBGA Pin Locations                                                                                                                                                   | Symbol           | Type   | Description                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4K                                                                                                                                                                   | CK               | Input  | Address, data in and control input register clock. Active high.                                                                                  |

| 4L                                                                                                                                                                   | $\overline{CK}$  | Input  | Address, data in and control input register clock. Active low.                                                                                   |

| (a) 6K, 7K, 6L, 7L, 6M, 6N, 7N, 6P, 7P<br>(b) 6D, 7D, 6E, 7E, 6F, 6G, 7G, 6H, 7H<br>(c) 1D, 2D, 1E, 2E, 2F, 1G, 2G, 1H, 2H<br>(d) 1K, 2K, 1L, 2L, 2M, 1N, 2N, 1P, 2P | DQx              | I/O    | Synchronous Data I/O.                                                                                                                            |

| 4F                                                                                                                                                                   | $\overline{G}$   | Input  | Output Enable: Asynchronous pin, active low.                                                                                                     |

| 2A, 3A, 5A, 6A, 2C, 3C, 5C, 6C, 4N, 4P, 2R, 6R, 3T, 4T, 5T                                                                                                           | SA               | Input  | Synchronous Address Inputs: Registered on the rising clock edge.                                                                                 |

| 5L, 5G, 3G, 3L<br>(a), (b), (c), (d)                                                                                                                                 | $\overline{SBx}$ | Input  | Synchronous Byte Write Enable: Enables writes to byte x in conjunction with the $\overline{SW}$ input. Has no effect on read cycles, active low. |

| 4E                                                                                                                                                                   | $\overline{SS}$  | Input  | Synchronous Chip Enable: Registered on the rising clock edge, active low.                                                                        |

| 4M                                                                                                                                                                   | $\overline{SW}$  | Input  | Synchronous Write: Registered on the rising clock edge, active low. Writes all enabled bytes.                                                    |

| 4U                                                                                                                                                                   | TCK              | Input  | Test Clock (JTAG).                                                                                                                               |

| 3U                                                                                                                                                                   | TDI              | Input  | Test Data In (JTAG).                                                                                                                             |

| 5U                                                                                                                                                                   | TDO              | Output | Test Data Out (JTAG).                                                                                                                            |

| 2U                                                                                                                                                                   | TMS              | Input  | Test Mode Select (JTAG).                                                                                                                         |

| 3J, 5J                                                                                                                                                               | $V_{ref}$        | Supply | Input Reference: provides reference voltage for input buffers.                                                                                   |

| 4D                                                                                                                                                                   | ZQ               | Input  | Programmable Output Impedance: Programming pin.                                                                                                  |

| 7T                                                                                                                                                                   | ZZ               | Input  | Reserved for future use. Must be grounded.                                                                                                       |

| 4C, 2J, 4J, 6J, 4R, 5R                                                                                                                                               | $V_{DD}$         | Supply | Core Power Supply.                                                                                                                               |

| 1A, 7A, 1F, 7F, 1J, 7J, 1M, 7M, 1U, 7U                                                                                                                               | $V_{DDQ}$        | Supply | Output Power Supply: Provides operating power for output buffers.                                                                                |

| 3D, 5D, 3E, 5E, 3F, 5F, 3H, 5H, 3K, 5K, 3M, 5M, 3N, 5N, 3P, 5P, 3R                                                                                                   | $V_{SS}$         | Supply | Ground.                                                                                                                                          |

| 4A, 1B, 2B, 3B, 4B, 5B, 6B, 7B, 1C, 7C, 1R, 7R, 1T, 2T, 6T, 6U                                                                                                       | NC               | —      | No Connection: There is no connection to the chip.                                                                                               |

| 4G, 4H                                                                                                                                                               | NF               | —      | No Function: There is an internal connection to the chip, but the pin has no function on this device.                                            |

## MCM69R618 PIN DESCRIPTIONS

| PBGA Pin Locations                                                                                                                          | Symbol           | Type   | Description                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4K                                                                                                                                          | CK               | Input  | Address, data in and control input register clock. Active high.                                                                                  |

| 4L                                                                                                                                          | $\overline{CK}$  | Input  | Address, data in and control input register clock. Active low.                                                                                   |

| (a) 6D, 7E, 6F, 7G, 6H, 7K, 6L, 6N, 7P<br>(b) 1D, 2E, 2G, 1H, 2K, 1L, 2M, 1N, 2P                                                            | DQx              | I/O    | Synchronous Data I/O.                                                                                                                            |

| 4F                                                                                                                                          | $\overline{G}$   | Input  | Output Enable: Asynchronous pin, active low.                                                                                                     |

| 2A, 3A, 5A, 6A, 2C, 3C, 5C,<br>6C, 4N, 4P, 2R, 6R, 2T, 3T, 5T, 6T                                                                           | SA               | Input  | Synchronous Address Inputs: Registered on the rising clock edge.                                                                                 |

| 5L, 3G<br>(a), (b)                                                                                                                          | $\overline{SBx}$ | Input  | Synchronous Byte Write Enable: Enables writes to byte x in conjunction with the $\overline{SW}$ input. Has no effect on read cycles, active low. |

| 4E                                                                                                                                          | $\overline{SS}$  | Input  | Synchronous Chip Enable: Registered on the rising clock edge, active low.                                                                        |

| 4M                                                                                                                                          | $\overline{SW}$  | Input  | Synchronous Write: Registered on the rising clock edge, active low. Writes all enabled bytes.                                                    |

| 4U                                                                                                                                          | TCK              | Input  | Test Clock (JTAG).                                                                                                                               |

| 3U                                                                                                                                          | TDI              | Input  | Test Data In (JTAG).                                                                                                                             |

| 5U                                                                                                                                          | TDO              | Output | Test Data Out (JTAG).                                                                                                                            |

| 2U                                                                                                                                          | TMS              | Input  | Test Mode Select (JTAG).                                                                                                                         |

| 3J, 5J                                                                                                                                      | $V_{ref}$        | Supply | Input Reference: provides reference voltage for input buffers.                                                                                   |

| 4D                                                                                                                                          | ZQ               | Input  | Programmable Output Impedance: Programming pin.                                                                                                  |

| 7T                                                                                                                                          | ZZ               | Input  | Reserved for future use. Must be grounded.                                                                                                       |

| 4C, 2J, 4J, 6J, 4R, 5R                                                                                                                      | $V_{DD}$         | Supply | Core Power Supply.                                                                                                                               |

| 1A, 7A, 1F, 7F, 1J, 7J, 1M, 7M, 1U, 7U                                                                                                      | $V_{DDQ}$        | Supply | Output Power Supply: Provides operating power for output buffers.                                                                                |

| 3D, 5D, 3E, 5E, 3F, 5F, 5G, 3H, 5H,<br>3K, 5K, 3L, 3M, 5M, 3N, 5N, 3P, 5P, 3R                                                               | $V_{SS}$         | Supply | Ground.                                                                                                                                          |

| 4A, 1B, 2B, 3B, 4B, 5B, 6B, 7B, 1C, 7C,<br>2D, 7D, 1E, 6E, 2F, 1G, 6G,<br>2H, 7H, 1K, 6K, 2L, 7L, 6M, 2N,<br>7N, 1P, 6P, 1R, 7R, 1T, 4T, 6U | NC               | —      | No Connection: There is no connection to the chip.                                                                                               |

| 4G, 4H                                                                                                                                      | NF               | —      | No Function: There is an internal connection to the chip, but the pin has no function on this device.                                            |

### ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to V<sub>SS</sub>. See Note 1)

| Rating                         | Symbol            | Value                         | Unit |

|--------------------------------|-------------------|-------------------------------|------|

| Core Supply Voltage            | V <sub>DD</sub>   | –0.5 to + 4.6                 | V    |

| Output Supply Voltage          | V <sub>DDQ</sub>  | –0.5 to V <sub>DD</sub> + 0.5 | V    |

| Voltage On Any Pin             | V <sub>in</sub>   | –0.5 to V <sub>DD</sub> + 0.5 | V    |

| Input Current (per I/O)        | I <sub>in</sub>   | ± 50                          | mA   |

| Output Current (per I/O)       | I <sub>out</sub>  | ± 70                          | mA   |

| Power Dissipation (See Note 2) | P <sub>D</sub>    | —                             | W    |

| Operating Temperature          | T <sub>A</sub>    | 0 to + 70                     | °C   |

| Temperature Under Bias         | T <sub>bias</sub> | –10 to + 85                   | °C   |

| Storage Temperature            | T <sub>stg</sub>  | –55 to + 125                  | °C   |

#### NOTES:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

2. Power dissipation capability will be dependent upon package characteristics and use environment. See enclosed thermal impedance data.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

This BiCMOS memory circuit has been designed to meet the dc and ac specifications shown in the tables, after thermal equilibrium has been established.

This device contains circuitry that will ensure the output devices are in High-Z at power up.

### PBGA PACKAGE THERMAL CHARACTERISTICS

| Rating                            | Symbol           | Max | Unit | Notes |

|-----------------------------------|------------------|-----|------|-------|

| Junction to Ambient (Still Air)   | R <sub>θJA</sub> | 59  | °C/W | 1, 2  |

| Junction to Ambient (@200 ft/min) | R <sub>θJA</sub> | 44  | °C/W | 1, 2  |

| Junction to Ambient (@200 ft/min) | R <sub>θJA</sub> | 28  | °C/W |       |

| Junction to Board (Bottom)        | R <sub>θJB</sub> | 18  | °C/W | 3     |

| Junction to Case (Top)            | R <sub>θJC</sub> | 9   | °C/W | 4     |

#### NOTES:

1. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87.

3. Indicates the average thermal resistance between the die and the printed circuit board.

4. Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

### CLOCK TRUTH TABLE

| K   | ZZ | SS | SW | SB <sub>a</sub> | SB <sub>b</sub> | SB <sub>c</sub> | SB <sub>d</sub> | DQ (n) | DQ (n+1)              | Mode                  |

|-----|----|----|----|-----------------|-----------------|-----------------|-----------------|--------|-----------------------|-----------------------|

| L–H | L  | L  | H  | X               | X               | X               | X               | High–Z | D <sub>out</sub> 0–35 | Read Cycle All Bytes  |

| L–H | L  | L  | L  | L               | H               | H               | H               | High–Z | D <sub>in</sub> 0–8   | Write Cycle 1st Byte  |

| L–H | L  | L  | L  | H               | L               | H               | H               | High–Z | D <sub>in</sub> 9–17  | Write Cycle 2nd Byte  |

| L–H | L  | L  | L  | H               | H               | L               | H               | High–Z | D <sub>in</sub> 18–26 | Write Cycle 3rd Byte  |

| L–H | L  | L  | L  | H               | H               | H               | L               | High–Z | D <sub>in</sub> 27–35 | Write Cycle 4th Byte  |

| L–H | L  | L  | L  | L               | L               | L               | L               | High–Z | D <sub>in</sub> 0–35  | Write Cycle All Bytes |

| L–H | L  | L  | L  | H               | H               | H               | H               | High–Z | High–Z                | Abort Write Cycle     |

| L–H | L  | H  | H  | X               | X               | X               | X               | High–Z | High–Z                | Deselect Cycle        |

| L–H | L  | H  | L  | X               | X               | X               | X               | High–Z | High–Z                | Deselect Cycle        |

| X   | H  | X  | X  | X               | X               | X               | X               | High–Z | High–Z                | Sleep Mode            |

## DC OPERATING CONDITIONS AND CHARACTERISTICS

(0°C ≤ TA ≤ 70°C, Unless Otherwise Noted)

### RECOMMENDED OPERATING CONDITIONS (See Notes 1 through 4)

| Parameter                                             | Symbol                | Min    | Typical -5 | Typical -6 | Typical -7 | Typical -8 | Max        | Unit | Notes |

|-------------------------------------------------------|-----------------------|--------|------------|------------|------------|------------|------------|------|-------|

| Core Power Supply Voltage                             | V <sub>DD</sub>       | 3.15   | —          | —          | —          | —          | 3.6        | V    |       |

| Output Driver Supply Voltage                          | V <sub>DDQ</sub>      | 1.4    | —          | —          | —          | —          | 1.6        | V    |       |

| Active Power Supply Current (x18)<br>(x36)            | I <sub>DD1</sub>      | —<br>— | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | mA   | 5     |

| Quiescent Active Power Supply Current (x18)<br>(x36)  | I <sub>DD2</sub>      | —<br>— | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD        | mA   | 6, 10 |

| Active Standby Power Supply Current (x18)<br>(x36)    | I <sub>SB1</sub>      | —<br>— | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD        | mA   | 7     |

| Quiescent Standby Power Supply Current (x18)<br>(x36) | I <sub>SB2</sub>      | —<br>— | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD<br>TBD | TBD        | mA   | 8, 10 |

| Sleep Mode Power Supply Current                       | I <sub>SB3</sub>      | —      | TBD        | TBD        | TBD        | TBD        | TBD        | mA   | 9, 10 |

| Input Reference DC Voltage                            | V <sub>ref</sub> (dc) | 0.6    | —          | —          | —          | —          | 1.1        | V    | 11    |

#### NOTES:

1. All data sheet parameters specified to full range of V<sub>DD</sub> unless otherwise noted. All voltages are referenced to voltage applied to V<sub>SS</sub> bumps.

2. Supply voltage applied to V<sub>DD</sub> connections.

3. Supply voltage applied to V<sub>DDQ</sub> connections.

4. All power supply currents measured with outputs open or deselected.

5. V<sub>DD</sub> = V<sub>DD</sub> (max), t<sub>KHKH</sub> = t<sub>KHKH</sub> (min), SS registered active, 50% read cycles.

6. V<sub>DD</sub> = V<sub>DD</sub> (max), t<sub>KHKH</sub> = dc, SS registered active.

7. V<sub>DD</sub> = V<sub>DD</sub> (max), t<sub>KHKH</sub> = t<sub>KHKH</sub> (min), SS registered inactive.

8. V<sub>DD</sub> = V<sub>DD</sub> (max), t<sub>KHKH</sub> = dc, SS registered inactive, ZZ low.

9. V<sub>DD</sub> = V<sub>DD</sub> (Max), t<sub>KHKH</sub> = dc, registered inactive, ZZ high.

10. 200 mV ≥ V<sub>in</sub> ≥ V<sub>DDQ</sub> – 200 mV.

11. Although considerable latitude in the selection of the nominal dc value (i.e., rms value) of V<sub>ref</sub> is supported, the peak to peak ac component superimposed on V<sub>ref</sub> may not exceed 5% of the dc component of V<sub>ref</sub>.

### DC INPUT CHARACTERISTICS

| Parameter                                               | Symbol                | Min                    | Max                    | Unit | Notes |

|---------------------------------------------------------|-----------------------|------------------------|------------------------|------|-------|

| DC Input Logic High                                     | V <sub>IH</sub> (dc)  | V <sub>ref</sub> + 0.1 | V <sub>DD</sub> + 0.3  | V    |       |

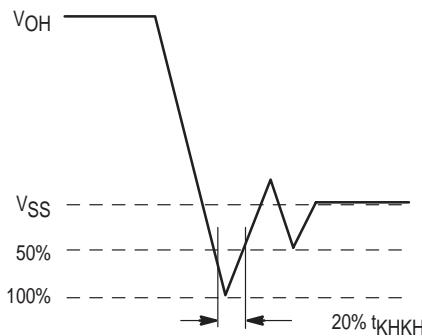

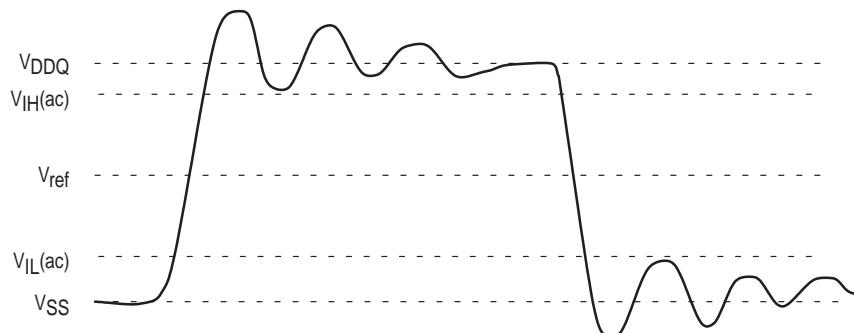

| DC Input Logic Low (See Figure 2)                       | V <sub>IL</sub> (dc)  | – 0.3                  | V <sub>ref</sub> – 0.1 | V    | 1     |

| Input Leakage Current                                   | I <sub>lkg</sub>      | —                      | ± 5                    | µA   | 2     |

| Clock Input Signal Voltage                              | V <sub>in</sub>       | – 0.3                  | V <sub>DD</sub> + 0.3  | V    |       |

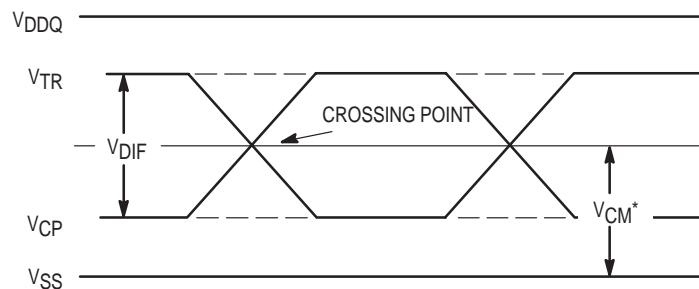

| Clock Input Differential Voltage                        | V <sub>DIF</sub> (dc) | 0.2                    | V <sub>DD</sub> + 0.6  | V    | 3     |

| Clock Input Common Mode Voltage Range (See Figure 3)    | V <sub>CM</sub> (dc)  | 0.68                   | 1.1                    | V    | 4     |

| Clock Input Crossing Point Voltage Range (See Figure 3) | V <sub>X</sub>        | 0.68                   | 1.1                    | V    |       |

#### NOTES:

1. Inputs may undershoot to –0.5 V (peak) for up to 20% t<sub>KHKH</sub> (e.g., 2 ns at a clock cycle time of 10 ns).

2. 0 V ≤ V<sub>in</sub> ≤ V<sub>DDQ</sub> for all pins.

3. Minimum differential input voltage required for differential input clock operation.

4. Maximum rejectable common mode input voltage variation.

**DC OUTPUT BUFFER CHARACTERISTICS – PROGRAMMABLE IMPEDANCE PUSH–PULL OUTPUT BUFFER MODE**

(0°C ≤ TA ≤ 70°C, Unless Otherwise Noted, See Notes 1 and 2)

| Parameter                    | Symbol           | Min                         | Max                         | Unit | Notes |

|------------------------------|------------------|-----------------------------|-----------------------------|------|-------|

| Output Logic Low             | V <sub>OL</sub>  | V <sub>DDQ</sub> /2 – 0.025 | V <sub>DDQ</sub> /2 + 0.025 | V    | 3     |

| Output Logic High            | V <sub>OH</sub>  | V <sub>DDQ</sub> /2 – 0.025 | V <sub>DDQ</sub> /2 + 0.025 | V    | 4     |

| Light Load Output Logic Low  | V <sub>OL1</sub> | V <sub>SS</sub>             | 0.2                         | V    | 5     |

| Light Load Output Logic High | V <sub>OH1</sub> | V <sub>DDQ</sub> – 0.2      | V <sub>DDQ</sub>            | V    | 6     |

NOTES:

1. The impedance controlled mode is expected to be used in point-to-point applications, driving high impedance inputs.

2. The ZQ pin is connected through RQ to V<sub>SS</sub> for the controlled impedance mode.

3. I<sub>OL</sub> = (V<sub>DDQ</sub>/2)/(RQ/5) for values of RQ = 175 Ω ≤ RQ ≤ 350 Ω.

4. | I<sub>OH</sub> | = (V<sub>DDQ</sub>/2)/(RQ/5) for values of RQ = 175 Ω ≤ RQ ≤ 350 Ω.

5. I<sub>OL</sub> ≤ 100 μA.

6. | I<sub>OH</sub> | ≤ 100 μA.

**DC OUTPUT BUFFER CHARACTERISTICS – MINIMUM IMPEDANCE PUSH–PULL OUTPUT BUFFER MODE**

(0°C ≤ TA ≤ 70°C, ZQ = V<sub>DD</sub>, See Notes 1 and 2)

| Parameter                    | Symbol           | Min.                   | Max.             | Unit | Notes |

|------------------------------|------------------|------------------------|------------------|------|-------|

| Output Logic Low             | V <sub>OL2</sub> | V <sub>SS</sub>        | 0.4              | V    | 3     |

| Output Logic High            | V <sub>OH2</sub> | V <sub>DDQ</sub> – 0.4 | V <sub>DDQ</sub> | V    | 4     |

| Light Load Output Logic Low  | V <sub>OL3</sub> | V <sub>SS</sub>        | 0.2              | V    | 5     |

| Light Load Output Logic High | V <sub>OH3</sub> | V <sub>DDQ</sub> – 0.2 | V <sub>DDQ</sub> | V    | 6     |

NOTES:

1. The push–pull output mode is expected to be used in bussed applications and may be series or parallel terminated. Conforms to the JEDEC Standard JESD8–6 Class 1.

2. The ZQ pin is connected to V<sub>DD</sub> to enable the minimum impedance mode.

3. I<sub>OL</sub> ≤ 8 mA.

4. | I<sub>OH</sub> | ≤ 8 mA.

5. I<sub>OL</sub> ≤ 100 μA.

6. | I<sub>OH</sub> | ≤ 100 μA.

**CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, 0°C ≤ TA ≤ 70°C, Periodically Sampled Rather Than 100% Tested)**

| Characteristic           | Symbol           | Typ | Max | Unit |

|--------------------------|------------------|-----|-----|------|

| Input Capacitance        | C <sub>in</sub>  | 4   | 5   | pF   |

| Input/Output Capacitance | C <sub>I/O</sub> | 7   | 8   | pF   |

| CK, CK Capacitance       | C <sub>CK</sub>  | 4   | 5   | pF   |

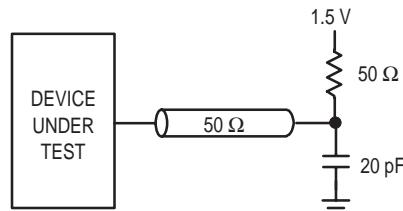

## AC OPERATING CONDITIONS AND CHARACTERISTICS

(0°C ≤ TA ≤ 70°C, Unless Otherwise Noted)

|                                          |                     |                                    |                          |

|------------------------------------------|---------------------|------------------------------------|--------------------------|

| Input Pulse Levels                       | 0.25 to 1.25 V      | Output Timing Reference Level      | 0.75 V                   |

| Input Rise/Fall Time                     | 1 V/ns (20% to 80%) | Clock Input Timing Reference Level | Differential Cross-Point |

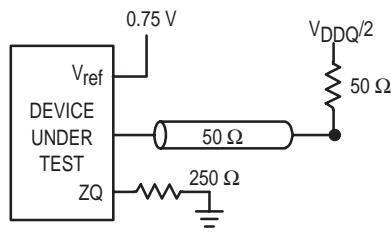

| Input Timing Measurement Reference Level | 0.75 V              | ZQ for 50 Ω Impedance              | 250 Ω                    |

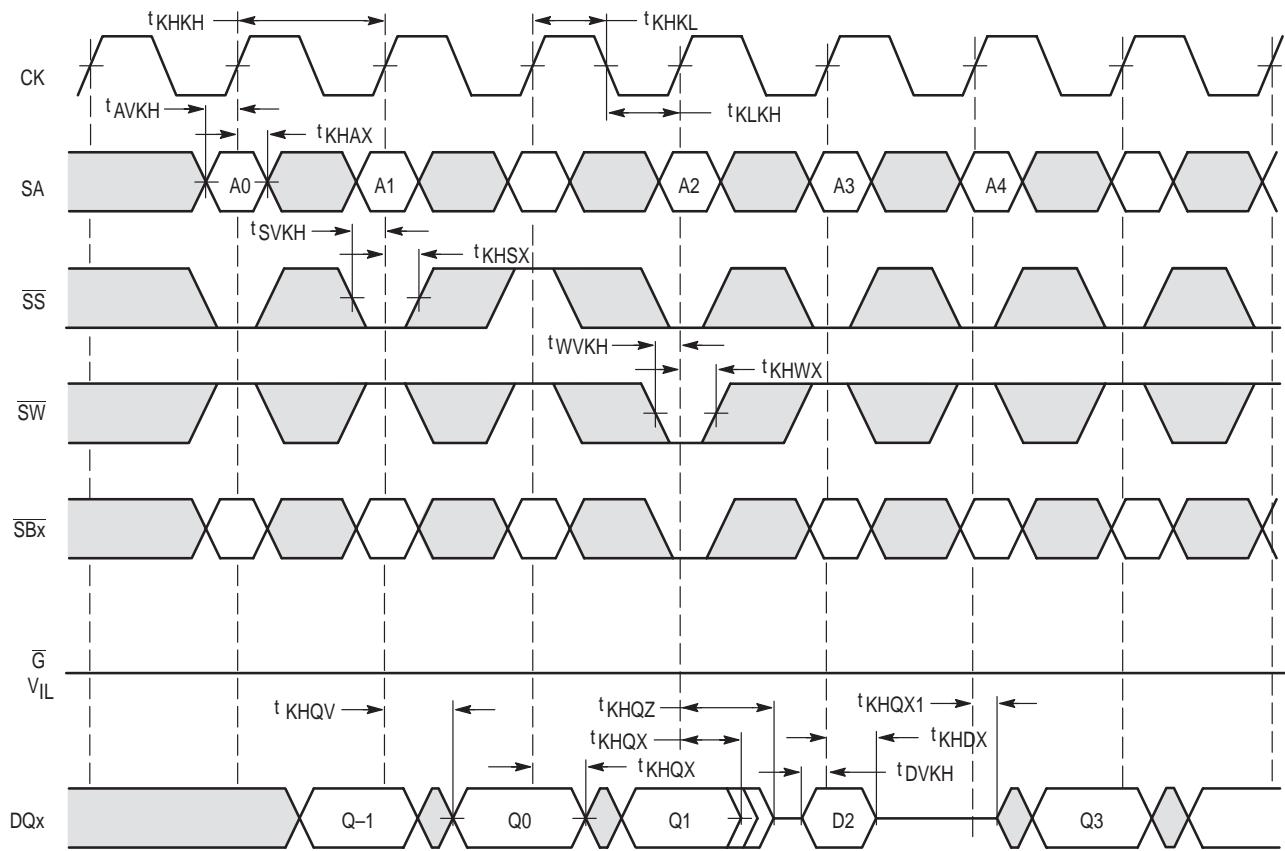

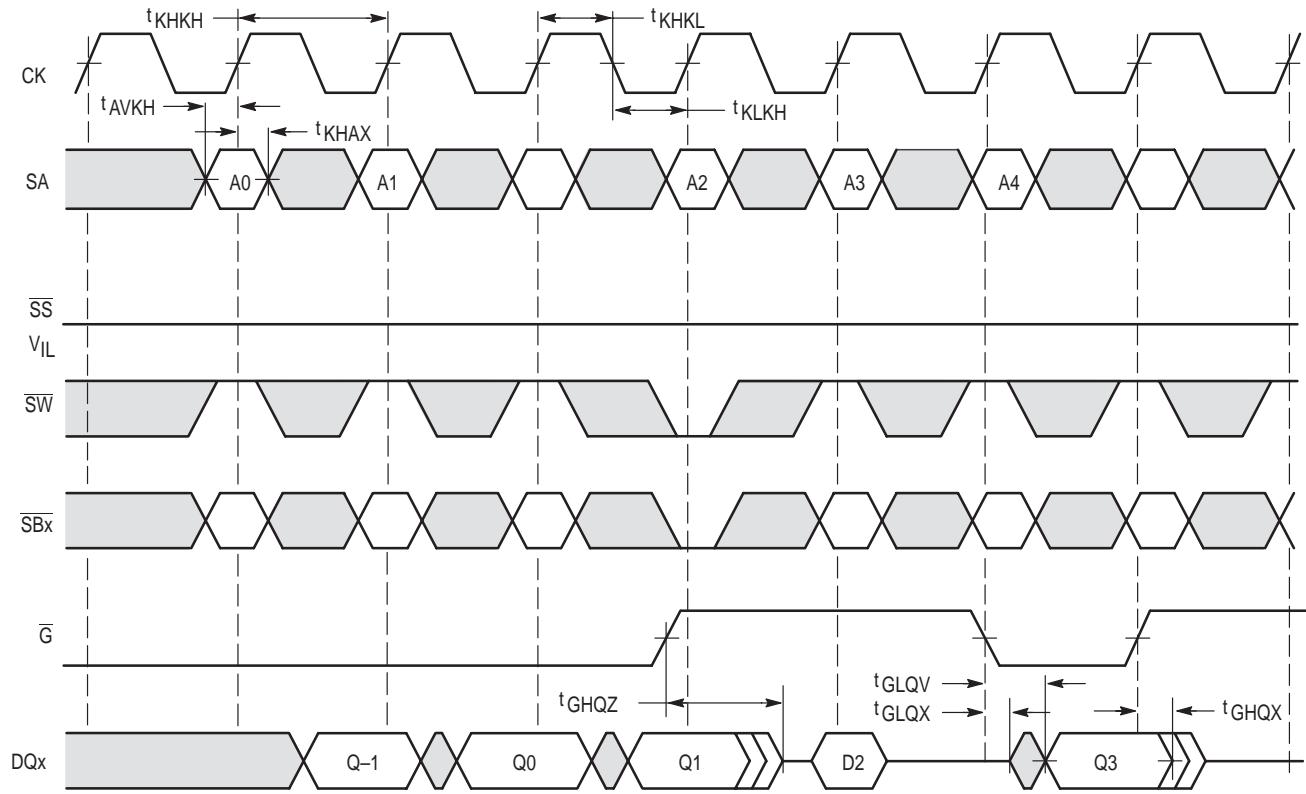

### READ/WRITE CYCLE TIMING (See Note 1)

| Parameter                                                      | Symbol                                                                           | MCM69R536-5<br>MCM69R618-5 |     | MCM69R536-6<br>MCM69R618-6 |     | MCM69R536-7<br>MCM69R618-7 |     | MCM69R536-8<br>MCM69R618-8 |     | Unit | Notes |

|----------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------|-----|----------------------------|-----|----------------------------|-----|----------------------------|-----|------|-------|

|                                                                |                                                                                  | Min                        | Max | Min                        | Max | Min                        | Max | Min                        | Max |      |       |

| Cycle Time                                                     | t <sub>KHHK</sub>                                                                | 5                          | —   | 6                          | —   | 7                          | —   | 8                          | —   | ns   |       |

| Clock High Pulse Width                                         | t <sub>KHKL</sub>                                                                | 2                          | —   | 2.4                        | —   | 2.8                        | —   | 3.2                        | —   | ns   |       |

| Clock Low Pulse Width                                          | t <sub>KLKH</sub>                                                                | 2                          | —   | 2.4                        | —   | 2.8                        | —   | 3.2                        | —   | ns   |       |

| Clock High to Output Low-Z                                     | t <sub>KHQX1</sub>                                                               | 1                          | —   | 1                          | —   | 1                          | —   | 1                          | —   | ns   | 2, 3  |

| Clock High to Output Valid                                     | t <sub>KHQV</sub>                                                                | —                          | 2.5 | —                          | 3   | —                          | 3.5 | —                          | 4   | ns   |       |

| Clock High to Output Hold                                      | t <sub>KHQX</sub>                                                                | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | ns   | 2     |

| Clock High to Output High-Z                                    | t <sub>KHQZ</sub>                                                                | —                          | 2.5 | —                          | 3   | —                          | 3.5 | —                          | 4   | ns   | 2, 3  |

| Output Enable Low to Output Low-Z                              | t <sub>GLQX</sub>                                                                | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | ns   |       |

| Output Enable Low to Output Valid                              | t <sub>GLQV</sub>                                                                | —                          | 2.5 | —                          | 3   | —                          | 3.5 | —                          | 4   | ns   |       |

| Output Enable to Output Hold                                   | t <sub>GHQX</sub>                                                                | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | ns   |       |

| Output Enable High to Output High-Z                            | t <sub>GHQZ</sub>                                                                | —                          | 2.5 | —                          | 3   | —                          | 3.5 | —                          | 4   | ns   | 2, 3  |

| Setup Times: Address<br>Data In<br>Chip Select<br>Write Enable | t <sub>AVKH</sub><br>t <sub>DVKH</sub><br>t <sub>SVKH</sub><br>t <sub>WVKH</sub> | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | 0.5                        | —   | ns   |       |

| Hold Times: Address<br>Data In<br>Chip Select<br>Write Enable  | t <sub>KHAX</sub><br>t <sub>KHDX</sub><br>t <sub>KHSX</sub><br>t <sub>KHWX</sub> | 1                          | —   | 1                          | —   | 1                          | —   | 1                          | —   | ns   |       |

#### NOTES:

1. In no case may control input signals (e.g.,  $\overline{SS}$ ) be operated with pulse widths less than the minimum clock input pulse width specifications (e.g.,  $t_{KHKL}$ ) or at frequencies that exceed the applied K clock frequency.

2. This parameter is sampled and not 100% tested.

3. Measured at  $\pm 200$  mV from steady state.

## AC INPUT CHARACTERISTICS

| Parameter                               | Symbol                | Min                       | Max                       | Note |

|-----------------------------------------|-----------------------|---------------------------|---------------------------|------|

| AC Input Logic High (See Figure 4)      | V <sub>IH</sub> (ac)  | V <sub>ref</sub> + 200 mV | —                         |      |

| AC Input Logic Low (See Figure 2 and 4) | V <sub>IL</sub> (ac)  | —                         | V <sub>ref</sub> - 200 mV | 1    |

| Input Reference Peak to Peak ac Voltage | V <sub>ref</sub> (ac) | —                         | 5% V <sub>ref</sub> (dc)  | 2    |

| Clock Input Differential Voltage        | V <sub>dif</sub> (ac) | 400 mV                    | V <sub>DDQ</sub> + 600 mV | 3    |

#### NOTES:

1. Inputs may undershoot to  $-0.5$  V (peak) for up to 20%  $t_{KHHK}$  (e.g., 2 ns at a clock cycle time of 10 ns).

2. Although considerable latitude in the selection of the nominal dc value (i.e., rms value) of V<sub>ref</sub> is supported, the peak to peak ac component superimposed on V<sub>ref</sub> may not exceed 5% of the dc component of V<sub>ref</sub>.

3. Minimum differential input voltage required for differential input clock operation.

## TIMING LIMITS

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address setup time is shown as a minimum since the system must supply at least that much time. On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

**Figure 1. AC Test Load**

**Figure 2. Undershoot Voltage**

\*V<sub>CM</sub>: the Common Mode Input Voltage, equals  $V_{TR} - ((V_{TR} - V_{CP})/2)$ .

**Figure 3. Differential Inputs/Common Mode Input Voltage**

**Figure 4. AC Input Conditions**

### REGISTER/REGISTER READ-WRITE-READ CYCLES

**REGISTER/REGISTER READ-WRITE-READ

( $\bar{G}$  Controlled)**

## FUNCTIONAL OPERATION

### READ AND WRITE OPERATIONS

All control signals except  $\overline{G}$  are registered on the rising edge of the CK clock. These signals must meet the setup and hold times shown in the AC Characteristics table. On the rising edge of the following clock, read data is clocked into the output register and available at the outputs at  $t_{KHQV}$ . During this same cycle a new read address can be applied to the address pins.

A deselect cycle (dead cycle) must occur prior to a write cycle. Read cycles may follow write cycles immediately.

$\overline{G}$ ,  $\overline{SS}$ , and  $\overline{SW}$  control output drive. Chip deselect via a high on  $\overline{SS}$  at the rising edge of the CK clock has its effect on the output drivers after the next rising edge of the CK clock.  $\overline{SW}$  low deselects the output drivers immediately (as registered by CK). Output drive is also controlled directly by output enable,  $\overline{G}$ . No clock edges are required to generate output disable with  $\overline{G}$ .  $\overline{G}$  asynchronously enables the output drivers.

Output data will be valid the latter of  $t_{GLQV}$  and  $t_{KHQV}$ . Outputs will begin driving at  $t_{KHQX1}$ . Outputs will hold previous data until  $t_{KHQX}$  or  $t_{GHQX}$ .

### WRITE AND BYTE WRITE FUNCTIONS

Note that in the following discussion the term "byte" refers to nine bits of the RAM I/O bus. In all cases, the timing parameters described for synchronous write input ( $\overline{SW}$ ) apply to each of the byte write enable inputs ( $SBa$ ,  $SBb$ , etc.).

Byte write enable inputs have no effect on read cycles. This allows the system designer not interested in performing byte writes to connect the byte enable inputs to active low ( $VSS$ ). Reads of all bytes proceed normally and write cycles, activated via a low on  $\overline{SW}$ , and the rising edge of the CK clock, write the entire RAM I/O width. This way the designer is spared having to drive multiple write input buffer loads.

Byte writes are performed using the byte write enable inputs in conjunction with the synchronous write input ( $\overline{SW}$ ). It is important to note that writing any one byte will inhibit a read of all bytes at the current address. The RAM cannot simultaneously read one byte and write another at the same address. A write cycle initiated with none of the byte write enable inputs active is neither a read or a write. No write will

occur, but the outputs will be deselected as in a normal write cycle.

### LATE WRITE

The write address is sampled on the first rising edge of clock and write data is sampled on the following rising edge.

The late write feature is implemented with single stage write buffering. Write buffering is transparent to the user. A comparator monitors the address bus and, when necessary, routes buffer contents to the outputs to assure coherent operation. This occurs in all cases whether there is a byte write or a full word is written.

### PROGRAMMABLE IMPEDANCE OPERATION

The designer can program the RAMs output buffer impedance by terminating the  $ZQ$  pin to  $VSS$  through a precision resistor ( $RQ$ ). The value of  $RQ$  is five times the output impedance desired. For example,  $250\ \Omega$  resistor will give an output impedance of  $50\ \Omega$ .

Impedance updates occur continuously and the frequency of the update is based on the subdivided K clock. Note that if the K clock stops so does the impedance update.

The actual change in the impedance occurs in small increments and is monotonic. There are no significant disturbances that occur on the output because of this smooth update method.

The impedance update is not related to any particular type of cycle because the impedance is updated continuously and is based on the K clock. Updates occur regardless of whether the device is performing a read, write or a deselect cycle and does not depend on the state of  $\overline{G}$ .

At power up, the output impedance defaults to approximately  $50\ \Omega$ . It will take 4,000 to 16,000 cycles for the impedance to be completely updated if the programmed impedance is much higher or lower than  $50\ \Omega$ .

The output buffers can also be programmed in a minimum impedance configuration by connecting  $ZQ$  to  $VDD$ .

### POWER UP AND INITIALIZATION

Once supplies have reached specification levels, a minimum dwell of 1.0 ms with CK clock inputs cycling is required before beginning normal operations. At power up the output impedance will be set at approximately  $50\ \Omega$  as stated above.

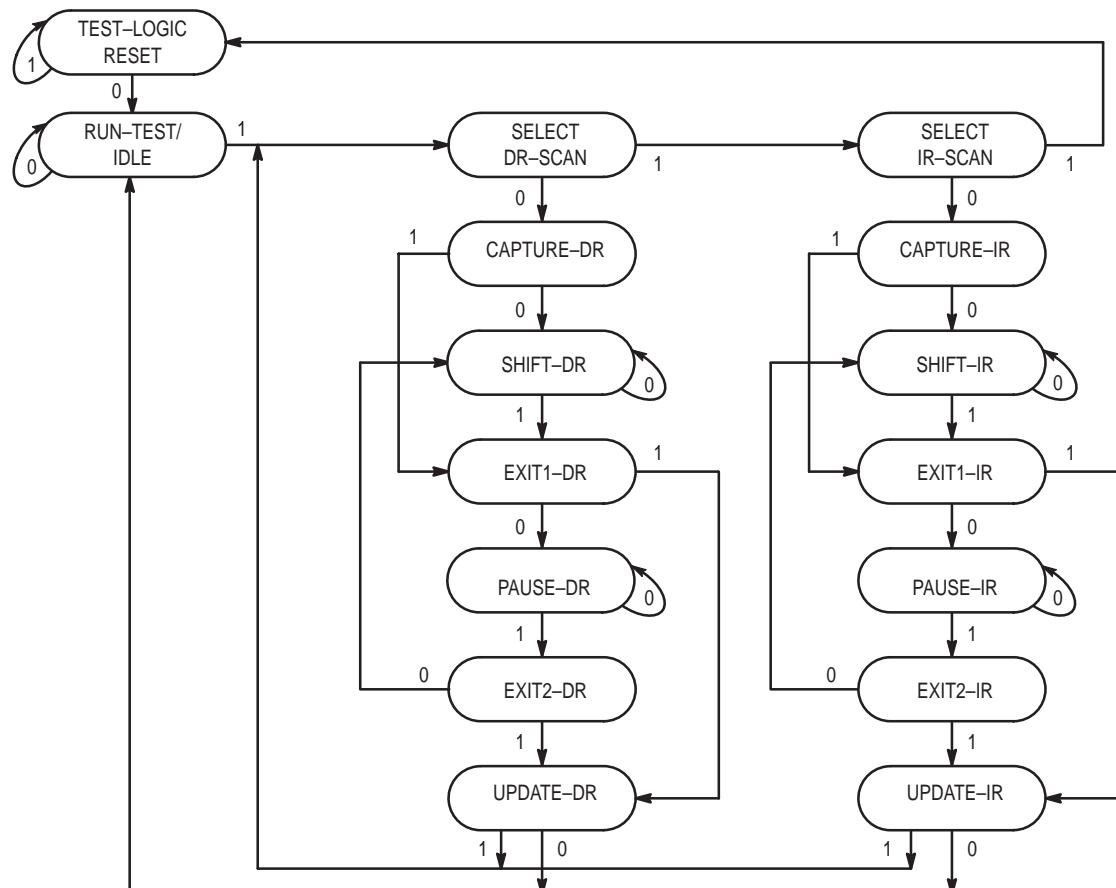

## SERIAL BOUNDARY SCAN TEST ACCESS PORT OPERATION

### OVERVIEW

The serial boundary scan test access port (TAP) on this RAM is designed to operate in a manner consistent with IEEE Standard 1149.1–1990 (commonly referred to as JTAG), but does not implement all of the functions required for 1149.1 compliance. Certain functions have been modified or eliminated because their implementation places extra delays in the RAMs critical speed path. Nevertheless, the RAM supports the standard TAP controller architecture. (The TAP controller is the state machine that controls the TAPs operation) and can be expected to function in a manner that does not conflict with the operation of devices with Standard

1149.1 compliant TAPs. The TAP operates using conventional JEDEC Standard 8–1B Low Voltage (3.3 V) TTL/CMOS logic level signaling.

### DISABLING THE TEST ACCESS PORT

It is possible to use this device without utilizing the TAP. To disable the TAP Controller without interfering with normal operation of the device, TCK must be tied to V<sub>SS</sub> to preclude mid level inputs. TDI and TMS are designed so an undriven input will produce a response identical to the application of a logic 1, and may be left unconnected. But they may also be tied to V<sub>DD</sub> through a 1 k resistor. TDO should be left unconnected.

### TAP DC OPERATING CHARACTERISTICS

(0°C ≤ T<sub>A</sub> ≤ 70°C, Unless Otherwise Noted)

| Parameter                   | Symbol           | Min                   | Max                   | Unit | Note |

|-----------------------------|------------------|-----------------------|-----------------------|------|------|

| Logic Input Logic High      | V <sub>IH1</sub> | 2.0                   | V <sub>DD</sub> + 0.3 | V    |      |

| Logic Input Logic Low       | V <sub>IL1</sub> | – 0.3                 | 0.8                   | V    |      |

| Logic Input Leakage Current | I <sub>lkg</sub> | —                     | ± 5                   | µA   | 1    |

| Output Logic Low            | V <sub>OL1</sub> | —                     | 0.2                   | V    | 2    |

| Output Logic High           | V <sub>OH1</sub> | V <sub>DD</sub> – 0.2 | —                     | V    | 3    |

| Output Logic Low            | V <sub>OL2</sub> | —                     | 0.4                   | V    | 4    |

| Output Logic High           | V <sub>OH2</sub> | 2.4                   | —                     | V    | 5    |

#### NOTES:

1. 0 V ≤ V<sub>in</sub> ≤ V<sub>DD</sub> for all logic input pins.

2. I<sub>OL1</sub> ≤ 100 µA @ V<sub>OL</sub> = 0.2 V. Sampled, not 100% tested.

3. |I<sub>OH1</sub>| ≤ 100 µA @ V<sub>DDQ</sub> – 0.2 V. Sampled, not 100% tested.

4. I<sub>OL2</sub> ≤ 8 mA @ V<sub>OL</sub> = 0.4 V.

5. |I<sub>OH2</sub>| ≤ 8 mA @ V<sub>OH</sub> = 2.4 V.

## TAP AC OPERATING CONDITIONS AND CHARACTERISTICS

( $0^{\circ}\text{C} \leq T_A \leq 70^{\circ}\text{C}$ , Unless Otherwise Noted)

|                                          |                     |

|------------------------------------------|---------------------|

| Input Pulse Levels                       | 0 to 3.0 V          |

| Input Rise/Fall Time                     | 1 V/ns (20% to 80%) |

| Input Timing Measurement Reference Level | 1.5 V               |

| Output Timing Reference Level            | 1.5 V               |

|                                                |                                                   |

|------------------------------------------------|---------------------------------------------------|

| Output Test Load                               | 50 $\Omega$ Parallel Terminated T-line with 20 pF |

| Receiver Input Capacitance                     |                                                   |

| Test Load Termination Supply Voltage ( $V_T$ ) | 1.5 V                                             |

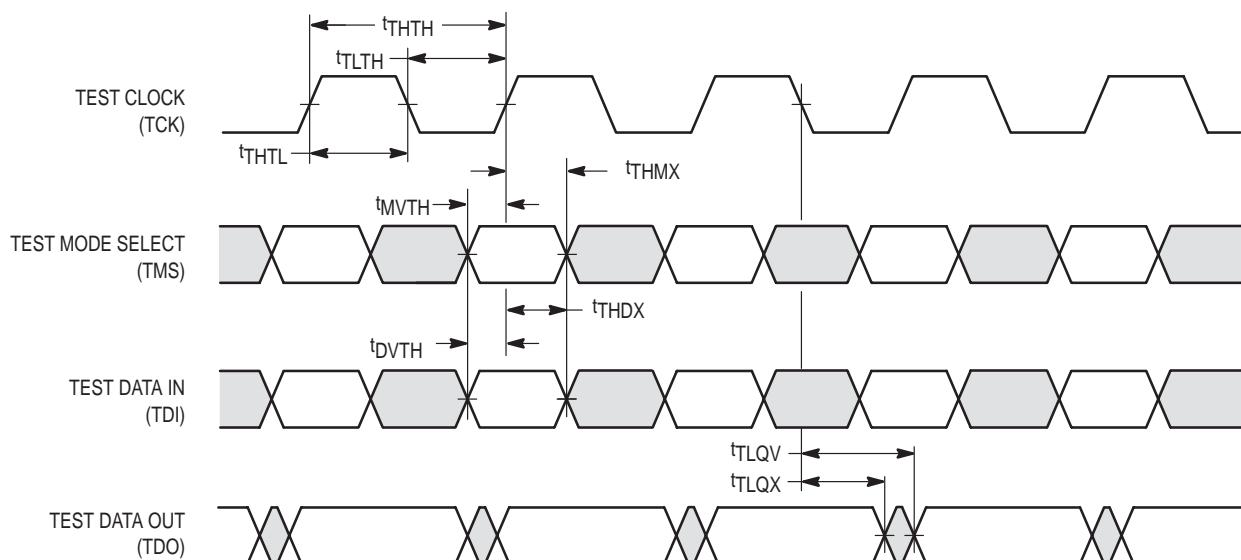

## TAP CONTROLLER TIMING

| Parameter                  | Symbol     | Min | Max | Unit | Notes |

|----------------------------|------------|-----|-----|------|-------|

| Cycle Time                 | $t_{THTH}$ | 100 | —   | ns   |       |

| Clock High Time            | $t_{THTL}$ | 40  | —   | ns   |       |

| Clock Low Time             | $t_{TLTH}$ | 40  | —   | ns   |       |

| TMS Setup                  | $t_{MVTH}$ | 10  | —   | ns   |       |

| TMS Hold                   | $t_{THMX}$ | 10  | —   | ns   |       |

| TDI Valid to TCK High      | $t_{DVTH}$ | 10  | —   | ns   |       |

| TCK High to TDI Don't Care | $t_{THDX}$ | 10  | —   | ns   |       |

| Capture Setup              | $t_{CS}$   | 10  | —   | ns   | 1     |

| Capture Hold               | $t_{CH}$   | 10  | —   | ns   | 1     |

| TCK Low to TDO Unknown     | $t_{TLQX}$ | 0   | —   | ns   |       |

| TCK Low to TDO Valid       | $t_{TLQV}$ | —   | 20  | ns   |       |

### NOTES:

1.  $t_{CS} + t_{CH}$  defines the minimum pause in RAM I/O pad transitions to assure accurate pad data capture.

## AC TEST LOAD

## TAP CONTROLLER TIMING DIAGRAM

## TEST ACCESS PORT PINS

### TCK — TEST CLOCK (INPUT)

Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.

### TMS — TEST MODE SELECT (INPUT)

The TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. An undriven TMS input will produce the same result as a logic one input level.

### TDI — TEST DATA IN (INPUT)

The TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP controller state machine and the instruction that is currently loaded in the TAP instruction register (refer to Figure 6, TAP Controller State Diagram). An undriven TDI pin will produce the same result as a logic one input level.

### TDO — TEST DATA OUT (OUTPUT)

Output that is active depending on the state of the TAP state machine (refer to Figure 6, TAP Controller State Diagram). Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO.

### TRST — TAP RESET

This device does not have a TRST pin. TRST is optional in **IEEE 1149.1**. The test-logic reset state is entered while TMS is held high for five rising edges of TCK. Power on reset circuitry is included internally. This type of reset does not affect the operation of the system logic. The reset affects test logic only.

## TEST ACCESS PORT REGISTERS

### OVERVIEW

The various TAP registers are selected (one at a time) via the sequences of ones and zeros input to the TMS pin as the TCK is strobed. Each of the TAPs registers are serial shift registers that capture serial input data on the rising edge of TCK and push serial data out on subsequent falling edge of TCK. When a register is selected it is “placed” between the TDI and TDO pins.

### INSTRUCTION REGISTER

The instruction register holds the instructions that are executed by the TAP controller when it is moved into the run test/idle or the various data register states. The instructions are three bits long. The register can be loaded when it is placed between the TDI and TDO pins. The instruction register is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in test-logic-reset state.

### BYPASS REGISTER

The bypass register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAMs TAP to another device in the scan chain with as little delay as possible.

### BOUNDARY SCAN REGISTER

The boundary scan register is identical in length to the number of active input and I/O connections on the RAM (not counting the TAP pins). This also includes a number of place holder locations (always set to a logic 1) reserved for density upgrade address pins. There are a total of 70 bits in the case of the x36 device and 51 bits in the case of the x18 device. The boundary scan register, under the control of the TAP controller, is loaded with the contents of the RAMs I/O ring when the controller is in capture-DR state and then is placed between the TDI and TDO pins when the controller is moved to shift-DR state. Several TAP instructions can be used to activate the boundary scan register.

The Bump/Bit Scan Order tables describe which device bump connects to each boundary scan register location. The first column defines the bit's position in the boundary scan register. The shift register bit nearest TDO (i.e., first to be shifted out) is defined as bit 1. The second column is the name of the input or I/O at the bump and the third column is the bump number.

### IDENTIFICATION (ID) REGISTER

The ID Register is a 32-bit register that is loaded with a device and vendor specific 32-bit code when the controller is put in capture-DR state with the IDCODE command loaded in the instruction register. The code is loaded from a 32 bit on-chip ROM. It describes various attributes of the RAM as indicated below. The register is then placed between the TDI and TDO pins when the controller is moved into shift-DR state. Bit 0 in the register is the LSB and the first to reach TDO when shifting begins.

#### ID Register Presence Indicator

| Bit # | 0 |

|-------|---|

| Value | 1 |

#### Motorola JEDEC ID Code (Compressed Format, per IEEE Standard 1149.1 – 1990)

| Bit # | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|-------|----|----|---|---|---|---|---|---|---|---|---|

| Value | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

#### Reserved For Future Use

| Bit # | 17 | 16 | 15 | 14 | 13 | 12 |

|-------|----|----|----|----|----|----|

| Value | x  | x  | x  | x  | x  | x  |

#### Device Width

| Configuration | Bit # | 22 | 21 | 20 | 19 | 18 |

|---------------|-------|----|----|----|----|----|

| 32K x 36      | Value | 0  | 0  | 1  | 0  | 0  |

| 64K x 18      | Value | 0  | 0  | 0  | 1  | 1  |

#### Device Depth

| Configuration | Bit # | 27 | 26 | 25 | 24 | 23 |

|---------------|-------|----|----|----|----|----|

| 32K x 36      | Value | 0  | 0  | 0  | 1  | 1  |

| 64K x 18      | Value | 0  | 0  | 1  | 0  | 0  |

#### Revision Number

| Bit # | 31 | 30 | 29 | 28 |

|-------|----|----|----|----|

| Value | x  | x  | x  | x  |

Figure 5. ID Register Bit Meanings

**MCM69R536 Bump/Bit Scan Order**

| BIT No. | Signal Name      | Bump ID | Bit No. | Signal Name      | Bump ID |

|---------|------------------|---------|---------|------------------|---------|

| 1       | M2               | 5R      | 36      | NC               | 3B      |

| 2       | SA               | 4P      | 37      | NC               | 2B      |

| 3       | SA               | 4T      | 38      | SA               | 3A      |

| 4       | SA               | 6R      | 39      | SA               | 3C      |

| 5       | SA               | 5T      | 40      | SA               | 2C      |

| 6       | ZZ               | 7T      | 41      | SA               | 2A      |

| 7       | DQa              | 6P      | 42      | DQc              | 2D      |

| 8       | DQa              | 7P      | 43      | DQc              | 1D      |

| 9       | DQa              | 6N      | 44      | DQc              | 2E      |

| 10      | DQa              | 7N      | 45      | DQc              | 1E      |

| 11      | DQa              | 6M      | 46      | DQc              | 2F      |

| 12      | DQa              | 6L      | 47      | DQc              | 2G      |

| 13      | DQa              | 7L      | 48      | DQc              | 1G      |

| 14      | DQa              | 6K      | 49      | DQc              | 2H      |

| 15      | DQa              | 7K      | 50      | DQc              | 1H      |

| 16      | $\overline{SBa}$ | 5L      | 51      | $\overline{SBc}$ | 3G      |

| 17      | $\overline{CK}$  | 4L      | 52      | ZQ               | 4D      |

| 18      | CK               | 4K      | 53      | $\overline{SS}$  | 4E      |

| 19      | $\overline{G}$   | 4F      | 54      | NF               | 4G      |

| 20      | $\overline{SBb}$ | 5G      | 55      | NF               | 4H      |

| 21      | DQb              | 7H      | 56      | $\overline{SW}$  | 4M      |

| 22      | DQb              | 6H      | 57      | $\overline{SBd}$ | 3L      |

| 23      | DQb              | 7G      | 58      | DQd              | 1K      |

| 24      | DQb              | 6G      | 59      | DQd              | 2K      |

| 25      | DQb              | 6F      | 60      | DQd              | 1L      |

| 26      | DQb              | 7E      | 61      | DQd              | 2L      |

| 27      | DQb              | 6E      | 62      | DQd              | 2M      |

| 28      | DQb              | 7D      | 63      | DQd              | 1N      |

| 29      | DQb              | 6D      | 64      | DQd              | 2N      |

| 30      | SA               | 6A      | 65      | DQd              | 1P      |

| 31      | SA               | 6C      | 66      | DQd              | 2P      |

| 32      | SA               | 5C      | 67      | SA               | 3T      |

| 33      | SA               | 5A      | 68      | SA               | 2R      |

| 34      | NC               | 6B      | 69      | SA               | 4N      |

| 35      | NC               | 5B      | 70      | M1               | 3R      |

NOTES:

1. The NC pads listed in this table are indeed no connects, but are represented in the boundary scan register by a “place holder” bit that is forced to logic 1. These pads are reserved for use as address inputs on higher density RAMs that follow this pad out and scan order standard.

2. In scan mode, differential inputs CK and  $\overline{CK}$  are referenced to each other and must be at opposite logic levels for reliable operation.

3. ZQ, M1, and M2 are not ordinary inputs and may not respond to standard I/O logic levels. ZQ, M1, and M2 must be driven to within 100 mV of a  $V_{DD}$  or  $V_{SS}$  supply rail to ensure consistent results.

4. ZZ must remain at  $V_{IL}$  during boundary scan to ensure consistent results.

**MCM69R618 Bump/Bit Scan Order**

| Bit No. | Signal Name      | Bump ID | Bit No. | Signal Name      | Bump ID |

|---------|------------------|---------|---------|------------------|---------|

| 1       | M2               | 5R      | 36      | $\overline{SBb}$ | 3G      |

| 2       | SA               | 6T      | 37      | ZQ               | 4D      |

| 3       | SA               | 4P      | 38      | $\overline{SS}$  | 4E      |

| 4       | SA               | 6R      | 39      | NF               | 4G      |

| 5       | SA               | 5T      | 40      | NF               | 4H      |

| 6       | ZZ               | 7T      | 41      | $\overline{SW}$  | 4M      |

| 7       | DQa              | 7P      | 42      | DQb              | 2K      |

| 8       | DQa              | 6N      | 43      | DQb              | 1L      |

| 9       | DQa              | 6L      | 44      | DQb              | 2M      |

| 10      | DQa              | 7K      | 45      | DQb              | 1N      |

| 11      | $\overline{SBa}$ | 5L      | 46      | DQb              | 2P      |

| 12      | $\overline{CK}$  | 4L      | 47      | SA               | 3T      |

| 13      | CK               | 4K      | 48      | SA               | 2R      |

| 14      | $\overline{G}$   | 4F      | 49      | SA               | 4N      |

| 15      | DQa              | 6H      | 50      | SA               | 2T      |

| 16      | DQa              | 7G      | 51      | M1               | 3R      |

| 17      | DQa              | 6F      |         |                  |         |

| 18      | DQa              | 7E      |         |                  |         |

| 19      | DQa              | 6D      |         |                  |         |

| 20      | SA               | 6A      |         |                  |         |

| 21      | SA               | 6C      |         |                  |         |

| 22      | SA               | 5C      |         |                  |         |

| 23      | SA               | 5A      |         |                  |         |

| 24      | NC               | 6B      |         |                  |         |

| 25      | NC               | 5B      |         |                  |         |

| 26      | NC               | 3B      |         |                  |         |

| 27      | NC               | 2B      |         |                  |         |

| 28      | SA               | 3A      |         |                  |         |

| 29      | SA               | 3C      |         |                  |         |

| 30      | SA               | 2C      |         |                  |         |

| 31      | SA               | 2A      |         |                  |         |

| 32      | DQb              | 1D      |         |                  |         |

| 33      | DQb              | 2E      |         |                  |         |

| 34      | DQb              | 2G      |         |                  |         |

| 35      | DQb              | 1H      |         |                  |         |

## TAP CONTROLLER INSTRUCTION SET

### OVERVIEW

There are two classes of instructions defined in the Standard 1149.1-1990; the standard (public) instructions, and device specific (private) instructions. Some public instructions, are mandatory for 1149.1 compliance. Optional public instructions must be implemented in prescribed ways.

Although the TAP controller in this device follows the 1149.1 conventions, it is not 1149.1 compliant because some of the mandatory instructions are not fully implemented. The TAP on this device may be used to monitor all input and I/O pads, but can not be used to load address, data or control signals into the RAM or to preload the I/O buffers. In other words, the device will not perform Standard 1149.1 EXTEST, INTEST or the preload portion of the SAMPLE/PRELOAD command.

When the TAP controller is placed in capture-IR state the two least significant bits of the instruction register are loaded with 01. When the controller is moved to the shift-IR state the instruction register is placed between TDI and TDO. In this state the desired instruction is serially loaded through the TDI input (while the previous contents are shifted out at TDO). For all instructions, the TAP executes newly loaded instructions only when the controller is moved to update-IR state. The TAP instruction sets for this device are listed in the following tables.

### STANDARD (PUBLIC) INSTRUCTIONS

#### BYPASS

The BYPASS instruction is loaded in the instruction register when the bypass register is placed between TDI and TDO. This occurs when the TAP controller is moved to the shift-DR state. This allows the board level scan path to be shortened to facilitate testing of other devices in the scan path.

#### SAMPLE/PRELOAD

Sample/preload is a Standard 1149.1 mandatory public instruction. When the sample/preload instruction is loaded in the Instruction register, moving the TAP controller into the capture-DR state loads the data in the RAMs input and I/O buffers into the boundary scan register. Because the RAM clock(s) are independent from the TAP clock (TCK) it is possible for the TAP to attempt to capture the I/O ring contents while the input buffers are in transition (i.e., in a metastable state). Although allowing the TAP to sample metastable inputs will not harm the device, repeatable results can not be

expected. RAM input signals must be stabilized for long enough to meet the TAPs input data capture set-up plus hold time ( $t_{CS}$  plus  $t_{CH}$ ). The RAMs clock inputs need not be paused for any other TAP operation except capturing the I/O ring contents into the boundary scan register.

Moving the controller to shift-DR state then places the boundary scan register between the TDI and TDO pins. Because the PRELOAD portion of the command is not implemented in this device, moving the controller to the update-DR state with the SAMPLE/PRELOAD instruction loaded in the instruction register has the same effect as the pause-DR command. This functionality is not Standard 1149.1 compliant.

#### EXTEST

EXTEST is an IEEE 1149.1 mandatory public instruction. It is to be executed whenever the instruction register, whatever length it may be in the device, is loaded with all logic 0s. EXTEST is not implemented in this device. Therefore this device is not 1149.1 compliant. Nevertheless, this RAMs TAP does respond to an all zeros instruction, as follows. With the EXTEST (000) instruction loaded in the instruction register the RAM responds just as it does in response to the SAMPLE / PRELOAD instruction described above, except the RAM outputs are forced to high-Z any time the instruction is loaded.

#### IDCODE

The IDCODE instruction causes the ID ROM to be loaded into the ID register when the controller is in capture-DR mode and places the ID register between the TDI and TDO pins in shift-DR mode. The IDCODE instruction is the default instruction loaded in at power up and any time the controller is placed in the test-logic-reset state.

### THE DEVICE SPECIFIC (PUBLIC) INSTRUCTION

#### SAMPLE-Z

If the SAMPLE-Z instruction is loaded in the instruction register, all RAM outputs are forced to an inactive drive state (high-Z) and the boundary scan register is connected between TDI and TDO when the TAP controller is moved to the shift-DR state.

### THE DEVICE SPECIFIC (PRIVATE) INSTRUCTION

#### NOOP

Do not use these instructions; they are reserved for future use.

## STANDARD (PUBLIC) INSTRUCTION CODES

| Instruction      | Code* | Description                                                                                                                                                                            |

|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST           | 000   | Captures I/O ring contents. Places the boundary scan register between TDI and TDO. Forces all RAM outputs to High-Z state. *NOT 1149.1 COMPLIANT*                                      |

| IDCODE           | 001** | Preloads ID register and places it between TDI and TDO. Does not affect RAM operation.                                                                                                 |

| SAMPLE / PRELOAD | 100   | Captures I/O ring contents. Places the boundary scan register between TDI and TDO. Does not affect RAM operation. Does not implement 1149.1 Preload function. * NOT 1149.1 COMPLIANT * |

| BYPASS           | 111   | Places bypass register between TDI and TDO. Does not affect RAM operation.                                                                                                             |

| SAMPLE-Z         | 010   | Captures I/O ring contents. Places the boundary scan register between TDI and TDO. Forces all RAM output drivers to High-Z.                                                            |

\* Instruction codes expressed in binary, MSB on left, LSB on right.

\*\* Default instruction automatically loaded at power-up and in test-logic-reset state.

## STANDARD (PRIVATE) INSTRUCTION CODES

| Instruction | Code* | Description                                                      |

|-------------|-------|------------------------------------------------------------------|

| NO OP       | 011   | Do not use these instructions; they are reserved for future use. |

| NO OP       | 101   | Do not use these instructions; they are reserved for future use. |

| NO OP       | 110   | Do not use these instructions; they are reserved for future use. |

\* Instruction codes expressed in binary, MSB on left, LSB on right.

NOTE: The value adjacent to each state transition represents the signal present at TMS at the rising edge of TCK.

Figure 6. TAP Controller State Diagram

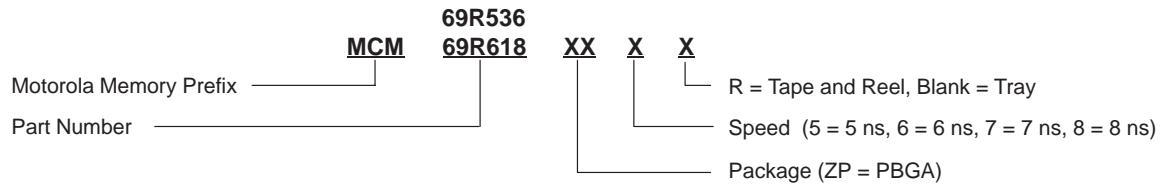

## ORDERING INFORMATION (Order by Full Part Number)

|                     |               |               |               |               |

|---------------------|---------------|---------------|---------------|---------------|

| Full Part Numbers — | MCM69R536ZP5  | MCM69R536ZP6  | MCM69R536ZP7  | MCM69R536ZP8  |

|                     | MCM69R618ZP5  | MCM69R618ZP6  | MCM69R618ZP7  | MCM69R618ZP8  |

|                     | MCM69R536ZP5R | MCM69R536ZP6R | MCM69R536ZP7R | MCM69R536ZP8R |

|                     | MCM69R618ZP5R | MCM69R618ZP6R | MCM69R618ZP7R | MCM69R618ZP8R |

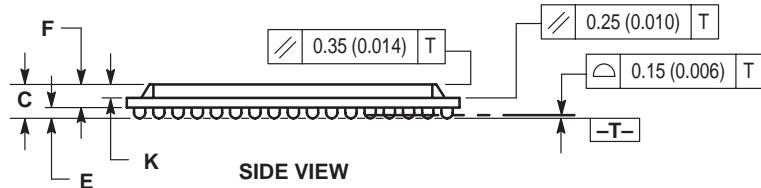

## PACKAGE DIMENSIONS

### ZP PACKAGE 7 X 17 BUMP PBGA CASE 999-01

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

| DIM | MILLIMETERS |       | INCHES |       |

|-----|-------------|-------|--------|-------|

|     | MIN         | MAX   | MIN    | MAX   |

| A   | 14.00       | BSC   | 0.551  | BSC   |

| B   | 22.00       | BSC   | 0.866  | BSC   |

| C   | —           | 2.40  | —      | 0.094 |

| D   | 0.60        | 0.90  | 0.024  | 0.035 |

| E   | 0.50        | 0.70  | 0.020  | 0.028 |

| F   | 1.30        | 1.70  | 0.051  | 0.067 |

| G   | 1.27        | BSC   | 0.050  | BSC   |

| K   | 0.80        | 1.00  | 0.031  | 0.039 |

| N   | 11.90       | 12.10 | 0.469  | 0.476 |

| P   | 19.40       | 19.60 | 0.764  | 0.772 |

| R   | 7.62        | BSC   | 0.300  | BSC   |

| S   | 20.32       | BSC   | 0.800  | BSC   |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and  are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Mfax is a trademark of Motorola, Inc.

#### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution;

P.O. Box 5405, Denver, Colorado, 80217. 1-303-675-2140 or 1-800-441-2447

**Mfax™:** RMFAX0@email.sps.mot.com – TOUCHTONE 1-602-244-6609

Motorola Fax Back System – US & Canada ONLY 1-800-774-1848

– <http://sps.motorola.com/mfax/>

**HOME PAGE:** <http://motorola.com/sps/>

**JAPAN:** Motorola Japan Ltd.; SPS, Technical Information Center,

3-20-1, Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre,

2 Dai King Street, Tai Po Industrial Estate, Tao Po, N.T., Hong Kong.

852-26668334

**CUSTOMER FOCUS CENTER:** 1-800-521-6274