# FMS7951

## Zero Delay Clock Multiplier

### Features

- Low Voltage CMOS or PECL reference input

- Up to 175 MHz of output frequency

- Nine configurable outputs

- Output enable pin

- 250 pS of output to output skew

- 300 pS of Cycle to Cycle Jitter

- V<sub>DD</sub> Range of 3.3V ±0.2V

- Commercial temperature range

- Available in 32 pin TQFP

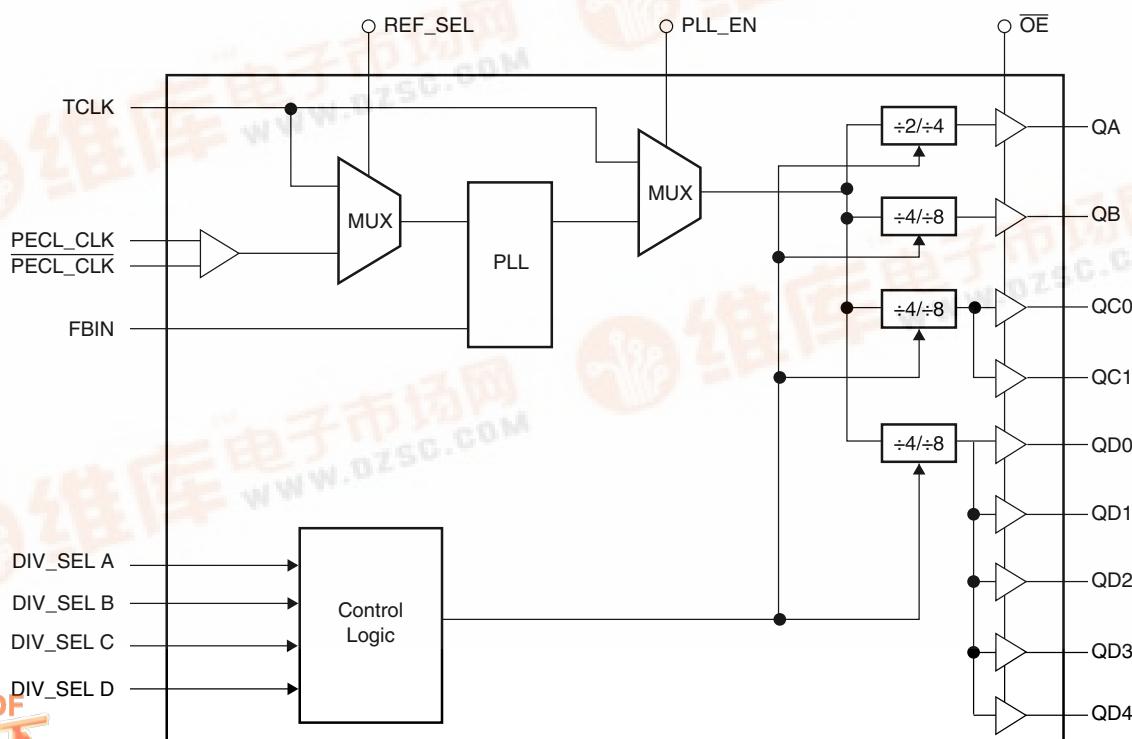

It has four banks of configurable outputs. By externally connecting one of the outputs to FBIN, the internal PLL will lock in both phase and frequency to the incoming clock. Any changes to the input clock will be tracked by the outputs. Depending on the selected output for feedback connection, the output frequencies will be as 1X, 2X or 4X of the input.

REF\_SEL allows selection between PECL input or TCLK a CMOS clock driven input. Connecting PLL\_EN LOW and REF\_SEL HIGH will bypass the Phase locked loop. In this mode, FMS7951 will be in clock buffer mode where any clock applied to TCLK will be divided down to the four output banks. This is ideal for system diagnostic test. When PLL\_EN is HIGH, the PLL is enabled, and any clock applied to TCLK will be locked in both phase and frequency to FBIN. PECL\_CLK is activated when REF\_SEL is high.

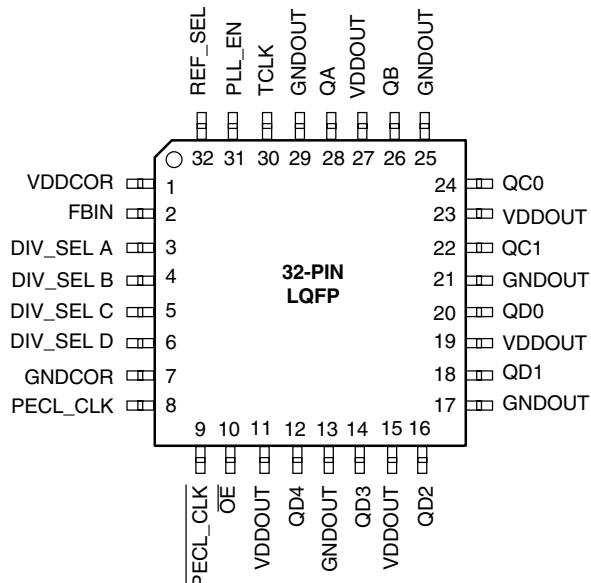

FMS7951 operates at 3.3 Volts and is available in 32 pin LQFP.

### Description

FMS7951 is a high speed, zero delay, low skew clock driver. It uses phase locked loop technology to generate frequencies up to 175 MHz.

### Block Diagram

## Pin Assignments

## Pin Description

| Pin Name                    | Pin #                                 | Pin Type | Description                                                                                                      |

|-----------------------------|---------------------------------------|----------|------------------------------------------------------------------------------------------------------------------|

| VDDCOR                      | 1                                     | PWR      | <b>Power Connection.</b> Power supply for core logic and PLL circuitry. Connect to 3.3 Volts nominal.            |

| FBIN                        | 2                                     | IN       | <b>Feedback In.</b> PLL feedback input. The user connects it to one of the outputs.                              |

| DIV_SEL(A:D)                | 3, 4, 5, 6                            | IN       | <b>Divider Select:</b> It divides the clock to a desirable value. See table 2. No internal pull up or pull down. |

| GNDCOR                      | 7                                     | PWR      | <b>Ground Connection.</b> Ground for core logic and PLL circuitry. Connect to the common system ground plane.    |

| PECL_CLK/<br>PECL_CLK       | 8, 9                                  | IN       | <b>PECL Clock Input:</b> These are differential PECL inputs when REF_SEL is Low, they are activated.             |

| OE                          | 10                                    | IN       | <b>Output Enable.</b> When high, all outputs are in high impedance. Normal operation when asserted low.          |

| VDDOUT                      | 11, 15, 19, 23, 27                    | PWR      | <b>Power Connection.</b> Power supply for all the output buffers. Connect to 3.3 Volts nominal.                  |

| QA; QB; Qc(0:1);<br>QD(0:4) | 12, 14, 16, 18, 20,<br>22, 24, 26, 28 | OUT      | <b>Clock Outputs.</b> These outputs are multiple of the input.                                                   |

| GNDOUT                      | 13, 17, 21, 25, 29                    | PWR      | <b>Ground Connection.</b> Ground for all the outputs. Connect to common system ground plane.                     |

| TCLK                        | 30                                    | IN       | <b>Test Clock.</b> When PLL-EN is low, all outputs are buffer copy of TCLK.                                      |

| PLL_EN                      | 31                                    | IN       | <b>PLL Enable.</b> When low, PLL is bypassed.                                                                    |

| REF_SEL                     | 32                                    | IN       | <b>Reference Select.</b> When low, PECL_CLK/PECL_CLK is used for input. When high, TCLK is used for input.       |

**Table 1. Functionality**

| REF_SEL | PLL_EN | OE | PLL     | All Outputs | Input    |

|---------|--------|----|---------|-------------|----------|

| 0       | 0      | 1  | By Pass | Hi-Z        | PECL_CLK |

| 0       | 0      | 0  | By Pass | Running     | PECL_CLK |

| 0       | 1      | 0  | Enabled | Running     | PECL_CLK |

| 1       | 0      | 1  | By Pass | Hi-Z        | TCLK     |

| 1       | 0      | 0  | By Pass | Running     | TCLK     |

| 1       | 1      | 0  | Enabled | Running     | TCLK     |

**Table 2. Input Versus Output Frequency**

| DIV_SELA | DIV_SELB | DIV_SELC | DIV_SELD | QA    | QB     | QC     | QD  |

|----------|----------|----------|----------|-------|--------|--------|-----|

| 0        | 0        | 0        | 0        | 2XREF | REF    | REF    | REF |

| 0        | 0        | 0        | 1        | 4XREF | 2XREF  | 2XREF  | REF |

| 0        | 0        | 1        | 0        | 2XREF | REF    | 1/2REF | REF |

| 0        | 0        | 1        | 1        | 4XREF | 2XREF  | REF    | REF |

| 0        | 1        | 0        | 0        | 2XREF | 1/2REF | REF    | REF |

| 0        | 1        | 0        | 1        | 4XREF | REF    | 2XREF  | REF |

| 0        | 1        | 1        | 0        | 2XREF | 1/2REF | 1/2REF | REF |

| 0        | 1        | 1        | 1        | 4XREF | REF    | REF    | REF |

| 1        | 0        | 0        | 0        | REF   | REF    | REF    | REF |

| 1        | 0        | 0        | 1        | 2XREF | 2XREF  | 2XREF  | REF |

| 1        | 0        | 1        | 0        | REF   | REF    | 1/2REF | REF |

| 1        | 0        | 1        | 1        | 2XREF | 2XREF  | REF    | REF |

| 1        | 1        | 0        | 0        | REF   | 1/2REF | REF    | REF |

| 1        | 1        | 0        | 1        | 2XREF | REF    | 2XREF  | REF |

| 1        | 1        | 1        | 0        | REF   | 1/2REF | 1/2REF | REF |

| 1        | 1        | 1        | 1        | 2XREF | REF    | REF    | REF |

**Note:**

1. Reference input could be either PECL\_CLK or TCLK input.

2. FBIN is tied to QD output for table

**Table 3. Divide Select Functionality**

| DIV_SEL A | DIV_SEL B | DIV_SEL D | DIV_SEL D | QA | QB | QC | QD |

|-----------|-----------|-----------|-----------|----|----|----|----|

| 0         | 0         | 0         | 0         | ÷2 | ÷4 | ÷4 | ÷4 |

| 1         | 1         | 1         | 1         | ÷4 | ÷8 | ÷8 | ÷8 |

## Absolute Maximum Ratings

| Symbol           | Parameter                                 | Ratings     | Units |

|------------------|-------------------------------------------|-------------|-------|

| $V_{DD}, V_{IN}$ | Voltage on any pin with respect to ground | -0.5 to 7.0 | V     |

| $T_{STG}$        | Storage Temperature                       | -65 to 150  | °C    |

| $T_B$            | Ambient Temperature                       | -55 to 125  | °C    |

| $T_A$            | Operating Temperature                     | 0 to 70     | °C    |

Stresses greater than those listed in the table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may effect reliability.

## DC Electrical Characteristics

$T_A = 0$  to  $70^\circ\text{C}$ ; Supply Voltage  $3.3\text{ V} \pm 0.2\text{V}$  (unless otherwise stated)

| Parameter                          | Symbol     | Conditions                               | Min.         | Typ. | Max.         | Units         |

|------------------------------------|------------|------------------------------------------|--------------|------|--------------|---------------|

| Input Low Voltage                  | $V_{IL}$   | TCLK; control pins                       |              |      | 0.8          | V             |

| Input High Voltage                 | $V_{IH}$   | TCLK; control pins                       | 2.0          |      | 3.6          | V             |

| Input Low Current                  | $I_{IL}$   | $V_{IN} = 0$                             | -10          |      | 10           | $\mu\text{A}$ |

| Input High Current                 | $I_{IH}$   | $V_{IN} = V_{DD}$                        | -30          |      | 30           | $\mu\text{A}$ |

| Peak to Peak Input Voltage         | $V_{PP}$   | PECL_CLK/PCL_CLK                         | 0.3          |      | 1.0          | V             |

| Common Mode Range                  | $V_{CMR}$  |                                          | $V_{DD}-2.0$ |      | $V_{DD}-0.6$ | mV            |

| Output Low Voltage                 | $V_{OL}$   | $I_{OL} = 40\text{ mA}$                  |              |      | 0.5          | V             |

| Output High Voltage                | $V_{OH}$   | $I_{OH} = -40\text{ mA}$                 | 2.2          |      |              | V             |

| Input Capacitance <sup>(1)</sup>   | $C_{IN}$   |                                          |              |      | 7.0          | pF            |

| Supply Current                     | $I_{DD}$   | Outputs loaded                           |              | TBD  | 150          | mA            |

| Clock Stabilization <sup>(1)</sup> | $T_{STAB}$ | From $V_{DD} = 3.3\text{V}$ to 1% Target |              |      | 10           | $\text{mS}$   |

**Note:**

- Guaranteed by design, not subject to 100% production testing.

## AC Electrical Characteristics

$T_A = 0$  to  $70^\circ\text{C}$ ; Supply Voltage  $V_{DD} = 3.3\text{V} \pm 0.2\text{V}$ ,  $C_L = 10\text{ pF}$  (unless otherwise stated)

| Parameter                                | Symbol                | Conditions                                   | Min. | Typ. | Max. | Units       |

|------------------------------------------|-----------------------|----------------------------------------------|------|------|------|-------------|

| Input Frequency                          | $F_{IN}$              | Feedback Divide = 2                          | 10   |      | 175  | MHz         |

|                                          |                       | Feedback Divide = 4                          | 10   |      | 85   |             |

|                                          |                       | Feedback Divide = 8                          | 10   |      | 42   |             |

| TCLK Input Rise/Fall Time <sup>(1)</sup> | $T_{R\_IN}/T_{F\_IN}$ |                                              | —    |      | 3.0  | ns          |

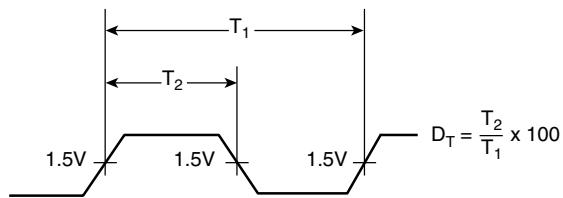

| TCLK Input Duty Cycle <sup>(1)</sup>     | $D_{T\_IN}$           |                                              | 25   |      | 75   | %           |

| Output Frequency Range                   | $F_{OUT}$             | $Q_A$ ; DIV_SEL A = 0V                       |      |      | 175  | MHz         |

|                                          |                       | $Q_B, Q_C$ & $Q_D$ ;<br>DIV_SEL B, C, D = 0V |      |      | 88   | MHz         |

| Output to Output Skew                    | $T_{SK1}$             | $V_{TH} = V_{DD}/2$ ; DIV_SEL A = 0          |      |      | 750  | $\text{pS}$ |

|                                          |                       | $V_{TH} = V_{DD}/2$ ; DIV_SEL A = 1          | -300 |      | 300  |             |

| Input to FBIN Delay                      | $T_{SK2}$             | TCLK                                         | 50   |      | 400  | $\text{pS}$ |

|                                          |                       | PECL_CLK                                     | -950 |      | -600 |             |

**AC Electrical Characteristics (Cont.)**

TA = 0 to 70°C; Supply Voltage VDD = 3.3V ±0.2V, CL = 10 pF (unless otherwise stated)

| Parameter                 | Symbol | Conditions        | Min. | Typ. | Max. | Units |

|---------------------------|--------|-------------------|------|------|------|-------|

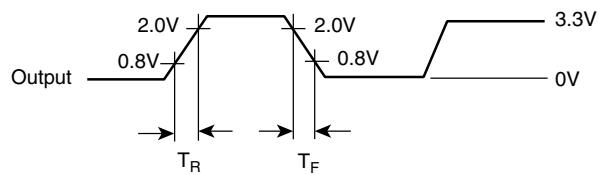

| Rise Time <sup>(1)</sup>  | TR     | 0.8 to 2.0V       | 0.10 |      | 1.0  | nS    |

| Fall Time <sup>(1)</sup>  | TF     | 2.0 to 0.8V       | 0.10 |      | 1.0  | nS    |

| Duty Cycle <sup>(1)</sup> | DT     | VTH = VDD/2       | 45   |      | 55   | %     |

| Jitter (Cycle-Cycle)      | TJIT   | QA: DIV_SEL A = 0 |      |      | 450  | pS    |

|                           |        | QA: DIV_SEL A = 1 |      |      | 200  |       |

|                           |        | QB Output         |      |      | 200  |       |

|                           |        | QC(0:1) Outputs   |      |      | 300  |       |

|                           |        | QD(0:4) Outputs   |      |      | 375  |       |

**Note:**

1. Guaranteed by design, not subject to 100% production testing.

## Parameter Measurement Information

### Duty Cycle (D<sub>T</sub>)

### Rise/Fall Time (T<sub>R</sub>/T<sub>F</sub>)

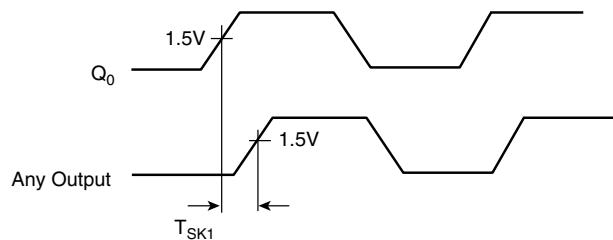

### Output to Output Skew (T<sub>SK1</sub>)

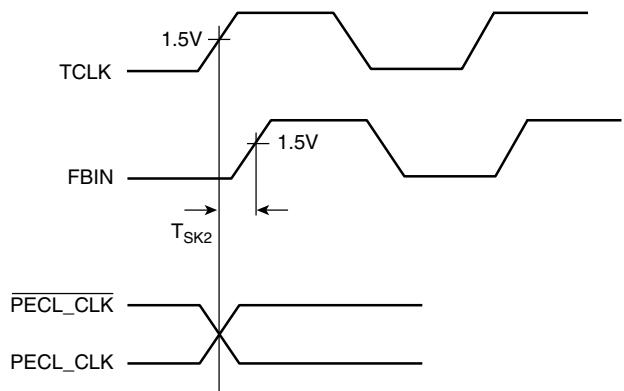

### Input to Output Delay (T<sub>SK2</sub>)

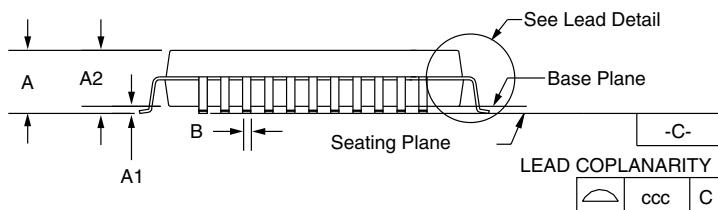

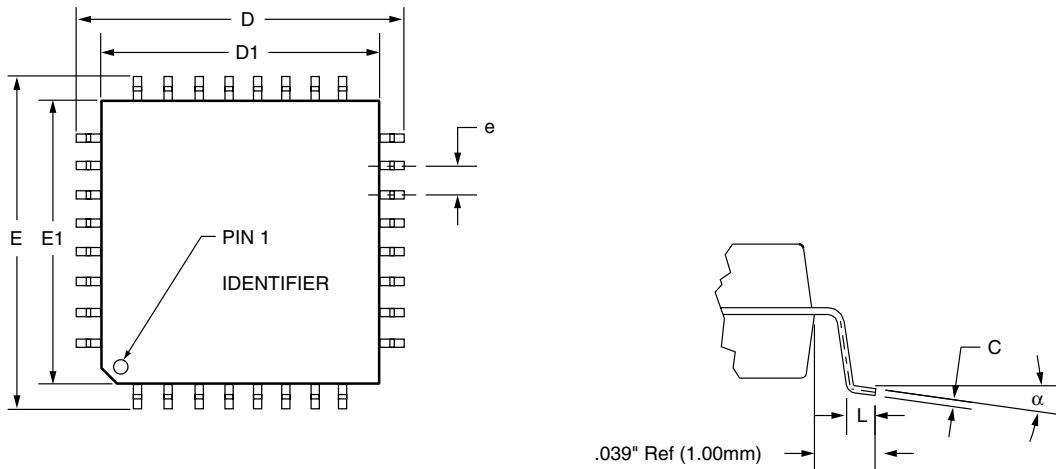

## Mechanical Dimensions

### 32-Pin LQFP

| Symbol   | Inches    |       | Millimeters |      | Notes |

|----------|-----------|-------|-------------|------|-------|

|          | Min.      | Max.  | Min.        | Max. |       |

| A        | —         | 0.063 | —           | 1.60 |       |

| A1       | 0.002     | 0.006 | 0.05        | 0.15 |       |

| A2       | 0.053     | 0.057 | 1.35        | 1.45 |       |

| B        | 0.012     | 0.018 | 0.30        | 0.45 | 7     |

| C        | —         | 0.004 | —           | 0.10 |       |

| D/E      | 0.354 BSC |       | 9.00 BSC    |      |       |

| D1/E1    | 0.276 BSC |       | 7.00 BSC    |      | 2     |

| e        | 0.032 BSC |       | 0.800 BSC   |      |       |

| L        | 0.018     | 0.030 | 0.45        | 0.75 | 6     |

| N        | 32        |       | 32          |      | 4     |

| ND       | 8         |       | 8           |      | 5     |

| $\alpha$ | 0°        | 7°    | 0°          | 7°   |       |

| ccc      | —         | 0.004 | —           | 0.10 |       |

#### Notes:

1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

2. Dimensions "D1" and "E1" do not include mold protrusion.

3. Pin 1 identifier is optional.

4. Dimension N: number of terminals.

5. Dimension ND: Number of terminals per package edge.

6. "L" is the length of terminal for soldering to a substrate.

7. "B" includes lead finish thickness.

## Ordering Information

| Product Number | Package Description | Package Marking |

|----------------|---------------------|-----------------|

| FMS7951KWC     | LQFP-32             | 7951KWC         |

| FMS7951KWCX    | LQFP-32 w/T+R       | 7951KWC         |

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.