### CMOS 4-BIT MICROCONTROLLER

## TMP47C446ADF

The 47C446A is high speed and high performance 4-bit single chip micro computers, integrating LCD driver, the 8-bit A/D converter and watchdog timer based on the TLCS-47 series.

The 47C446A has two oscillation circuit. It is possible to switch the operation mode; high speed operation and low power consumption operation.

| PART No.     | ROM          | RAM         | PACKAGE            | ОТР          |

|--------------|--------------|-------------|--------------------|--------------|

| TMP47C446ADF | 4096 × 8-bit | 256 × 4-bit | QFP64-P-1420-1.00A | TMP47P446VDF |

### **FEATURES**

◆ 4-bit single chip microcomputer

lacktriangle Instruction execution time : 1.9  $\mu$ s (at 4.2 MHz),

244 μs (at 32.8 kHz)

♦ 89 basic instructions

• Table look-up instructions

◆ Subroutine nesting: 15 levels max.

♦ 6 interrupt sources (External : 2, Internal : 4)

All sources have independent latches each, and multiple interrupt control is available

♦ I/O port (24 pins)

• Input 1 port 4 pins

• I/O 4 ports 20 pins

◆ Interval timer

◆ Two 12-bit Timer / Counters

Timer, event counter, and pulse width measurement mode

♦ Watchdog Timer

◆ Serial Interface with 4-bit buffer

External / internal clock, leading / trailing edge shift mode

◆ LCD driver (automatic display)

LCD direct drive (Max. 12-digit display at 1/4 duty LCD)

• 1/4, 1/3, 1/2 duty or static drive are programmably selectable.

◆ 8-bit successive approximate type A/D converter

• With sample and hold

4 analog inputs

• Converting time : 48 μs (4 MHz)

◆ Dual-clock operation

High-speed / Low-power-comsumption operating mode

◆ Real Time Emulator: BM47220A

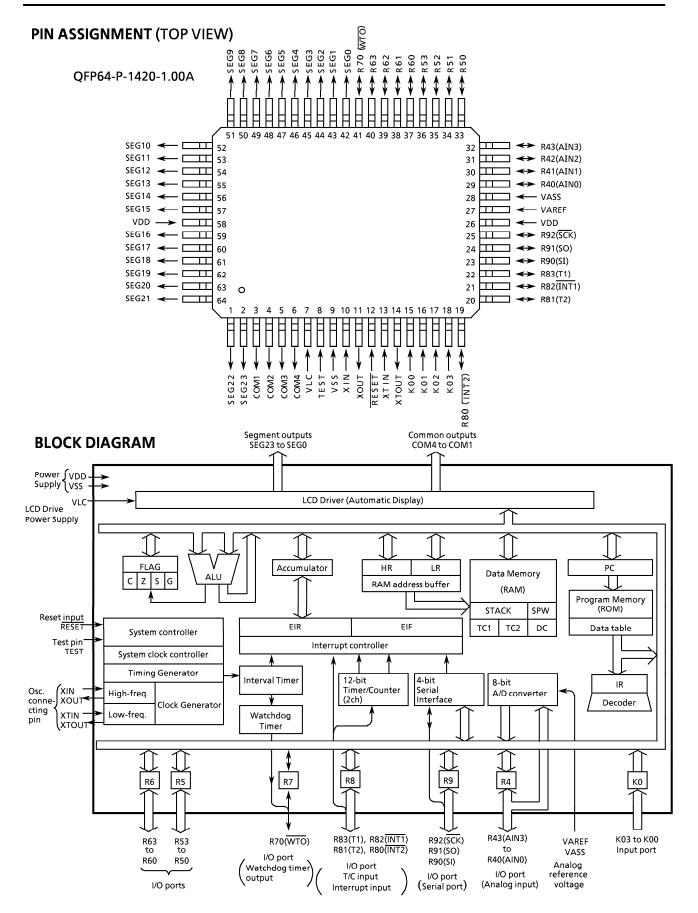

# **PIN FUNCTION**

| PIN NAME                       | Input/Output | FUNCTION                                                                                  | S                                                            |  |  |

|--------------------------------|--------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| K03 to K00                     | Input        | 4-bit input port                                                                          |                                                              |  |  |

| R43 (AIN3)<br>to<br>R40 (AIN0) | I/O (Input)  | 4-bit I/O port with latch.  When using as input port, the latch must be set to "1".       | A/D converter analog input                                   |  |  |

| R53 to R50<br>R63 to R60       | I/O          | 4-bit I/O port with latch.                                                                |                                                              |  |  |

| R70 (WTO)                      | I/O (Output) | 1-bit I/O port with latch                                                                 | Watchdog timer output                                        |  |  |

| R83 (T1)<br>R82 (ĪNT1)         |              | 4-bit I/O port with latch.  When using as input port, external interrupt                  | Timer / Counter 1 external input  External interrupt 1 input |  |  |

| R81 (T2)<br>R80 (ĪNT2)         | I/O (Input)  | input pin, or timer / counter external input pin, the latch must be set to "1".           | Timer / Counter 2 external input  External interrupt 2 input |  |  |

| R92 (SCK)                      | I/O(I/O)     | 3-bit I/O port with latch.                                                                | Serial clock I/O                                             |  |  |

| R91 (SO)                       | I/O (Output) | When using as input port or serial port, the                                              | Serial data output                                           |  |  |

| R90 (SI)                       | I/O (Input)  | latch must be set to "1".                                                                 | Serial data input                                            |  |  |

| SEG23 to SEG0                  | Output       | LCD Segment output                                                                        |                                                              |  |  |

| XIN                            | Input        | Occupanting pine (High frequency)                                                         |                                                              |  |  |

| XOUT                           | Output       | Osc. connecting pins (High -frequency).  For inputting external clock, XIN is used and XC | DUT is opened.                                               |  |  |

| RESET                          | Input        | Reset signal input                                                                        |                                                              |  |  |

| XTIN                           | Input        | Osc. connecting pins (Low-frequency) .                                                    |                                                              |  |  |

| XTOUT                          | Output       | For inputting external clock, XTIN is used and X                                          | TOUT is opened.                                              |  |  |

| TEST                           | Input        | Test pin for out-going test. Be opened or fixed                                           | to low level.                                                |  |  |

| VDD<br>VSS                     |              | + 5 V<br>0V (GND)                                                                         |                                                              |  |  |

| VLC                            | Power supply | LCD drive power supply                                                                    |                                                              |  |  |

| VAREF                          |              | A/D converter analog reference voltage (High)                                             |                                                              |  |  |

| VASS                           |              | A/D converter analog reference voltage (Low)                                              |                                                              |  |  |

#### **OPERATIONAL DESCRIPTION**

Conserning the 47C446A, the hardware configuration and operation are described.

As the description included mainly differences from the 47C400B, refer to thr technical data sheets for the 47C400B. The 47C446A does not have the hold function.

#### 1. SYSTEM CONFIGURATION

**♦** INTERNAL CPU FUNCTION

They are the same as those of the 47C400B except for the system control circuit.

- ◆ PERIPHERAL HARDWARE FUNCTION

- 1 I/O Ports

- 2 Interval Timer

- ③ Timer / Counters (TC1, TC2)

- 4 Serial Interface

- (5) Wachdog Timer

- 6 A/D Converter

- 7 LCD Driver

The 47C446A has the dual clock operation, so it differs from the 47C400B in the system timing to the peripheral hardware.

### 2. INTERNAL CPU FUNCTION

## 2.1 System Clock Controller

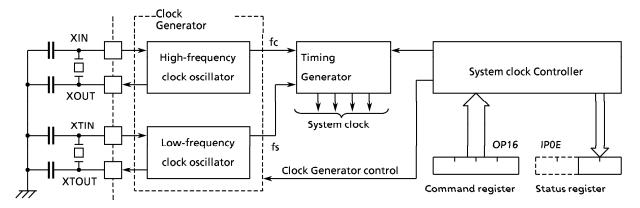

The 47C446A has two oscillation circuits with a high-frequency clock and a low-frequency clock. Power consumption can be decreased by switching to low-speed operation using the low-frequency clock when necessary (dual clock operation). The high-frequency clock can be obtained by connecting an oscillator to the XIN and XOUT pins; the low-frequency clock can be obtained by connecting the oscillator to the XTIN and XTOUT pins. Figure 2-1 shows the configuration of system clock controller.

Figure 2-1. System Clock Controller

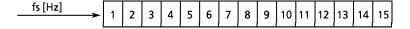

### 2.1.1 Configuration of Timing Generator (TG)

The timing generator is configured with a 15-stage binary counter and inputs the oscillation circuit output (fs) for the low-frequency clock; therefore, the final stage output is fs/2<sup>15</sup> [Hz]. This timing generator is cleared to "0" during reset.

Also, "fs" is input directly into the timing generator; therefore, the interval timer interrupts, timer / counter and LCD driver will not operate normally if the low-frequency oscillation is not stable.

Figure 2-2. Timing Generator

## 2.1.2 Dual Clock Operation and Control

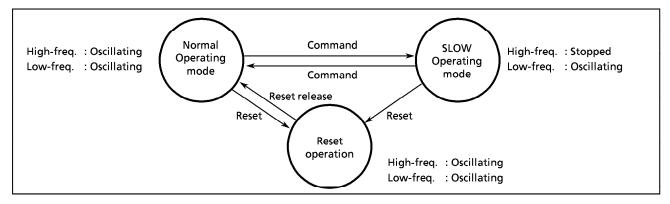

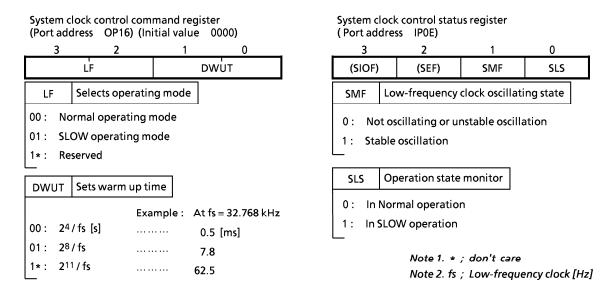

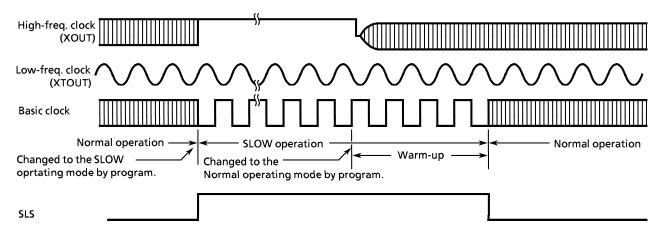

Dual clock operation involves two modes: Normal operating mode using the high-frequency clock, and SLOW operating mode using the low-frequency clock. Both oscillators start operating when the power is turned on, after which the Normal operation is selected automatically. The high-frequency clock stops oscillating when a command is issued to switch to the SLOW operation. Operating mode switching is performed using the command register (OP16). The status of the low-frequency clock and the current operating mode can be monitored using the status register (IP0E). Figure 2-3 shows the operating mode transitions, and Figure 2-3 shows the command and status registers.

Figure 2-3. Operating Mode Transmission Diagram

### (1) Operation Mode Control

Figure 2-5. Command register and Status register

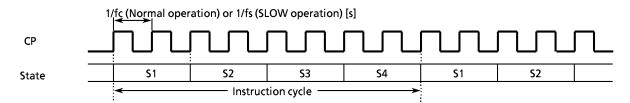

### (2) Instruction Cycle

Figure 2-5. Instruction Cycle

Note. The power consumption of the oscillator and internal hardware is decreased in the SLOW operation, but power consumption through pin interfaces (dependent on the external circuitry and program) may prevent overall low power consumption operation; therefore, caution is necessary during system design and interface circuit design. The following operations and functions cannot be used in the SLOW operation; therefore, this must be taken into consideration in programming.

- ① Timer/Counter 4096 Hz (at fs = 32.8 kHz) count operation (can be used with other count rates).

- ② Interval timer interrupt 4096 Hz (at fs = 32.8 kHz) operation (can be used with other timer rates).

- 3 Serial Interface

#### (3) Operation mode switching

The following procedure is used to switch between the Normal operation and the SLOW operation. The Normal operation is selected during reset. Also, the current operating mode can be checked by monitoring SLS (status register bit 0).

a. Switching from Normal operation to SLOW operation

After monitoring SMF (status register bit 1) by program and confirming that the low-frequency clock is stable, set bit 2 of the command register to "1". The high-frequency clock will then stop. Also, after switching from Normal operation to SLOW operation (accessing the command register), execute the NOP (No Operation) instruction.

#### b. Returning from SLOW operation to Normal operation

When bit 2 of the command register is cleared to "0", the warm-up time must be set in DWUT. When the set warm-up time elapses, operation is switched to the Normal operation.

Example 1 : Normal operation  $\rightarrow$  SLOW operation.

SSMF: TEST %IP0E, 1 ; To wait until SMF goes to "1".

B SSMF

LD A, #0100B ; Selects SLOW operating mode

OUT A, %OP16

NOP ; no operation

:

Example 2 : SLOW operation  $\rightarrow$  Normal operation

LD A, #0001B ; Selects Normal operation and sets warm-up OUT A, %0P16 time (7.8 ms)

:

Figure 2-6. System Clock Switching Timing

#### 3. PERIPHERAL HARDWARE FUNCTION

#### 3.1 Ports

The 47C446A has 7 I/O ports (24 pins) each as follows:

① K0 ; 4-bit input

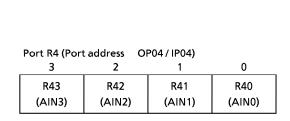

② R4 ; 4-bit input / output (shared by the A/D converter analog inputs)

③ R5, R6 ; 4-bit input / output

⑤ R8 ; 4-bit input / output (shared by external interrupt request input and timer

/ counter input)

6 R9 ; 3-bit input / output (shared by serial port)

This section describes ports of ② and ④ which are changed from the 47C400B.

Ports P1, P2 and KE are eliminated from the 47C400B.

The 5-bit to 8-bit data conversion instruction [OUTB @HL] is not valid.

Table 3-1 lists the port address assignments and the I/O instructions that can access the ports.

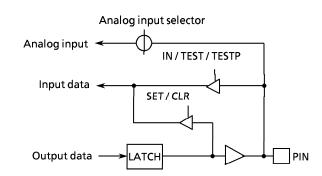

### (1) Port R4 (R43 to R40)

Port R4 is 4-bit I/O ports with latch shared by the analog inputs for A/D converter. When used as an input port or analog input, the latch should be set to "1". If other port is used as an output, be careful not to execute the output instruction for any port during A/D conversion in order to keep accuracy of conversion. The latch is initialized to "1" and analog input is selected R40 (AINO) pin during reset.

Figure 3-1. Port R4

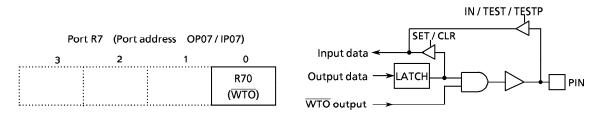

### (2) Port R7 (R70)

Port R7 is 1-bits I/O port with latch. R70 pin is shared by the watchdog timer output. To use R70 pin for the watchdog timer output, the latch should be set to "1". The latch is initialized to "1" during reset. R71, R72 and R73 pins do not exist actually but "1" is read when an input instruction is executed.

Figure 3-2. Port R7

Table 3-1. Port Address Assignments and Available I/O Instructions

| tiod            |                       | Port                            |                        |                        | Input/     | Input/output instruction | tion                 |                           |                            |

|-----------------|-----------------------|---------------------------------|------------------------|------------------------|------------|--------------------------|----------------------|---------------------------|----------------------------|

| Address (**)    |                       | Output (OP**)                   | IN %p, A<br>IN %p, @HL | ОUT A,%р<br>ОUT @HL,%р | OUT #k, %p | OUTB @HL                 | SET %p,b<br>CLR %p,b | TEST %p, b<br>TESTP %p, b | SET @L<br>CLR @L<br>TEST@L |

| <sup>H</sup> 00 | K0 input port         |                                 | 0                      | ı                      | 1          | 1                        | . 1                  | 0                         | ı                          |

| 01              |                       |                                 | ı                      | ı                      | ı          | ı                        | I                    | ı                         | ı                          |

| 05              | !                     |                                 | 1                      | ı                      | I          | 1                        | I                    | 1                         | ı                          |

| 03              |                       |                                 | ı                      | ı                      | ı          | ı                        | ı                    | 1                         | ı                          |

| 04              | (Analog input)        | R4 output port                  | 0                      | 0                      | 0          | ı                        | 0                    | 0                         | 0                          |

| 02              |                       | R5 output port                  | 0                      | 0                      | 0          | ı                        | 0                    | 0                         | 0                          |

| 90              |                       | R6 output port                  | 0                      | 0                      | 0          | ı                        | 0                    | 0                         | 0                          |

| 07              |                       | R7 output port (WTO) output     | 0                      | 0                      | 0          | ı                        | 0                    | 0                         | 0                          |

| 80              |                       | R8 output port                  | 0(                     | 0(                     | 0          | ı                        | 0(                   | 0                         | ı                          |

| 60              | R9 input port         | R9 output port                  | )                      | )                      | )          | ı                        | )                    | )                         | ı                          |

| ٥<br>م          |                       |                                 | ı                      | ı                      | ı          | ı                        | ı                    | 1                         | ı                          |

| 0B              |                       |                                 | 1                      | 1                      | ı          | ı                        | 1                    | 1                         | ı                          |

| 00              | A/D Status input      |                                 | 0                      | ı                      | ı          | ı                        | ı                    | 0                         | 1                          |

| 0               | A/D converted Value   |                                 | 0                      | ı                      | ı          | ı                        | ı                    | 1                         | ı                          |

| 90              | SIO status            |                                 | 0                      | ı                      | ı          | ı                        | ı                    | 0                         | ı                          |

| P.              | Serial recieve buffer | Serial transmit buffer          | 0                      | 0                      | 0          | ı                        | ı                    | 1                         | ı                          |

| 10 <sub>H</sub> | Undefined             |                                 | 1                      | ı                      | 1          | 1                        | . 1                  | ı                         | ı                          |

| 11              | Undefined             |                                 | 1                      | ı                      | ı          | ı                        | ı                    | 1                         | ı                          |

| 12              | Undefined             | A/D analog input selector       | ı                      | 0                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 13              | Undefined             | A/D start register              | 1                      | 0                      | ı          | ı                        | I                    | 1                         | ı                          |

| 14              | Undefined             |                                 | ı                      | ı                      | ı          | ı                        | I                    | ı                         | ı                          |

| 15              | Undefined             | Watchdog Timer control          | ı                      | 0                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 16              | Undefined             | System clock control            | ı                      | 0                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 17              | Undefined             |                                 | ı                      | ı                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 18              | Undefined             |                                 | ı                      | ı                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 19              | Undefined             | Interval timer intrrupt control | ı                      | 0                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 4               | Undefined             |                                 | ı                      | ı                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 18              | Undefined             | LCD Drive control               | 1                      | 0                      | ı          | 1                        | ı                    | 1                         | ı                          |

| 7               | Undefined             | Timer/counter 1 control         | ı                      | 0                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 0               | Undefined             | Timer/counter 2 control         | ı                      | 0                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 1E              | Undefined             | -                               | ı                      | ı                      | ı          | ı                        | ı                    | ı                         | ı                          |

| 1F              | Undefined             | Serial interface control        | 1                      | 0                      | 1          | ı                        | 1.                   | 1                         | I                          |

|                 |                       |                                 |                        |                        |            |                          |                      |                           |                            |

"——" means the reserved state. Unavailable for the user programs.

Note.

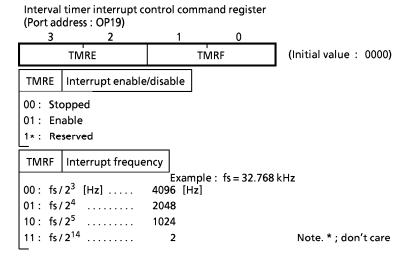

#### 3.2 Interval Timer

Constant-frequency interrupts can be generated using the interval timer, Four different frequencies can be selected for interval timer interrupts using the command register (OP19). The command register is also initialized to "0" during reset.

An interval timer interrupt is generated at the first rising edge of the binary counters output after the command is set to the command register.

Figure 3-3. Command Register

### 3.3 Timer / Counter

The timer / counter of the 47C446A is operated by a low-frequency clock (fs); therefore, the following operating frequencies differ from those of the 47C400B.

- 1 Internal pulse rate.

- ② Maximum frequency applied in the event counter mode.

- 3 Drop ratio of instruction execution time when the timer is used.

- (1) Internal pulse rate

The intrnal pulse rates shown in Table 3-2 can be selected by setting the values of the lower 2 bits of the TC1 and TC2 control command registers (OP1C, OP1D).

| ١ | The values of lower 2 bits | Internal pulse ra      | to. | Max. settin          | og timo | At fs = 32          | 768 kHz           |

|---|----------------------------|------------------------|-----|----------------------|---------|---------------------|-------------------|

| ı | (bit1, 0)                  | internal pulse ra      | ite | Iviax. settii        | ig time | Internal pulse rate | Max. setting time |

|   | 00                         | fs / 2 <sup>3</sup> [H | z]  | 2 <sup>15</sup> / fs | [s]     | 4096 [Hz]           | 1 [s]             |

| 1 | 01                         | fs / 2 <sup>7</sup>    |     | 2 <sup>19</sup> / fs |         | 265                 | 16                |

| ı | 10                         | fs / 2 <sup>11</sup>   |     | 2 <sup>23</sup> / fs |         | 16                  | 256               |

| 1 | 11                         | fs / 2 <sup>15</sup>   |     | 2 <sup>27</sup> / fs |         | 1                   | 4096              |

Table 3-2. Internal Pulse Rate

(2) Maximum frequency applied in the event counter mode.

(3) Drap ratio of instruction execution time when the timer is used.

With the 47C446A, count operation is inserted in the ratio of once per [(basic clock frequency) / 2<sup>3</sup>] / (internal pulse rate ) instruction cycle; therefore, execution speed drops as follows:

Example 1: When fc = 4 MHz and fs = 32.8 kHz in the Normal operation and the internal pulse rate fs/2<sup>3</sup> is selected, count operation is inserted once per each cycle of 122 instructions; therefore, there is a drop of 100/121 = 0.83 % for an instruction execution speed of 2  $\mu$ s.

Example 2: When fs = 32.8 kHz in the SLOW operation and the internal pulse rate fs/211 is selected, count operation is inserted once per each cycle of 256 instructions; therefore, there is a drop of 0.39 % for an instruction execution speed of 244  $\mu$ s. In addition, when the basic clock is obtained from "fs" (SLOW operation), count operation cannot be used with an internal pulse rate of fs/23.

### 3.4 Serial Interface

When operating using the internal clock, fs/2<sup>2</sup> [Hz] is used as the serial clock. Consequently, when operating at fs = 32.768 kHz, the maximum transfer rate is 8192 bps. When the reading and writing of serial data cannot follow this clock rate, the serial clock is automatically stopped and the next shift operation stands by untill the processing is completed.

External clock can be used in the same way as for the 47C400B. The serial interface cannot be used in the SLOW operating mode.

## 3.5 Watchdog timer (WDT)

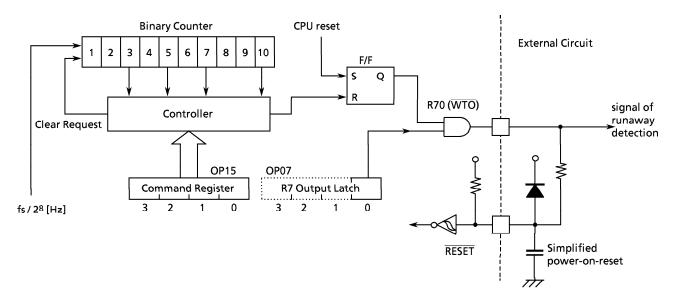

The purpose of the watchdog timer is to detect the malfunction (ranaway) of program due to external noise or other causes and return the operation to the normal condition. The watchdog timer output is output to R70 (WTO) pin.

When the watchdog timer is used, the output latch of R70 must be set to "1". Further, during reset, the output latch of R70 is set to "1", and the watchdog timer becomes disable state.

The initialization at time of runaway will become possible when the  $\overline{\text{WTO}}$  pin and  $\overline{\text{RESET}}$  pin are connected each other.

### 3.5.1 Configuration of Watchdog Timer

The watchdog timer consists of 10-stage binary counter, flip-flop (F/F), and its control circuit. The F/F is set to "1" during reset, and cleared to "0" at the rising edge of the binary counter output.

Figure 3-4. Watchdog Timer

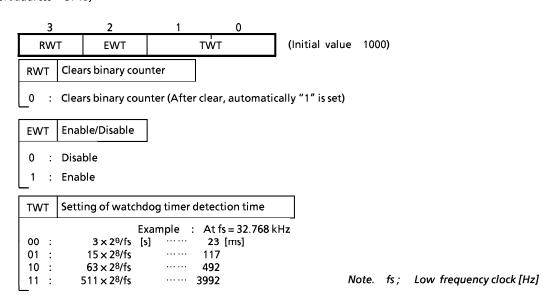

## 3.5.2 Control of watchdog timer

The watchdog timer is controlled by the command register (OP15). This command register is initialized to "1000<sub>B</sub>" during reset. The following are procedure to detect the malfunction (runaway) of CPU by the watchdog timer.

- ① At first, detection time of the watchdog timer should be set and binary counter should be cleared.

- ② The watchdog timer should be become enable.

- ③ Binary counter must be cleared before the detection time of the watchdog timer. When the runaway of CPU is taken place for some reason and binary counter is not cleared, the F/F is cleared to "0" at the rising edge of the binary counter and signal of runaway detection is become active (WTO output is "L").

Watchdog Timer control command register (Port address OP15)

Figure 3-5. Command Register

```

To set the watchdog detection time (63 \times 2^8/fs [s]). And to enable the watchdog timer.

Example:

LD

A, #0010B

; OP15 ← 0010<sub>B</sub>

(Sets WDT detection time. Clears binary counter)

OUT

A, %OP15

A. #0110B

; OP15 ← 0110<sub>B</sub> (Enables WDT)

LD

OUT

A, %OP15

Within WDT

detection time

LD

A, #0110B

; OP15 ← 0110<sub>B</sub> (Clears binary counter)

OUT

A. %OP15

```

Note. It is necessary to clear the binary counter prior to enabling watchdog timer.

Further, when switching the system clock, the watchdog timer has to halt during the warm-up time at changing from the SLOW operating mode to the Normal operating mode.

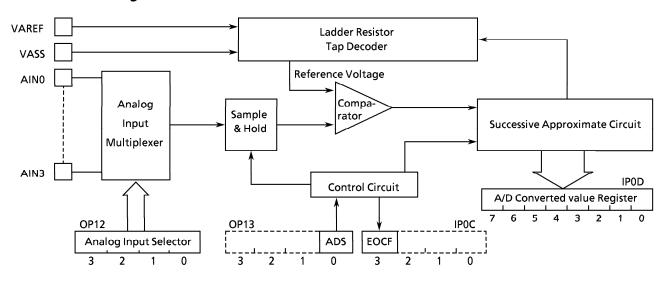

#### 3.6 A/D Converter

The 47C446A has a 8-bit successive approximate type A/D converter and is capable of processing 4 analog inputs.

# 3.6.1 Circuit configuration

Figure 3-6. Block Diagram of A/D Converter

## 3.6.2 Control of A/D converter

The operation of A/D converter is controlled by a command register (OP12, OP13, IPOC, IPOD).

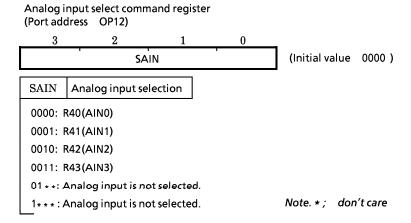

(1) Analog input selector (OP12)

Analog inputs (AIN0 through AIN3) are selected by values of this register.

Figure 3-7. Analog input selector

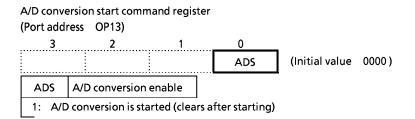

### (2) Start of A/D conversion (OP13)

A/D conversion is started when ADS is set to "1". After the conversion is started, ADS is cleared by hardware. If the restart is requested during the conversion, the conversion is started again at the time.

Analog input voltage is hold by the sample hold circuit.

Figure 3-8. A/D conversion start register

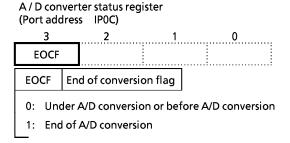

(3) A/D converter end register (IPOC)

End of conversion flag (EOCF) is a single bit flag showing the end of conversion and is set to "1" when conversion ended. When both upper 4 bits and lower 4 bits of a converted value are read or A/D conversion is started, EOCF is cleared to "0".

Figure 3-9. A/D converter status register

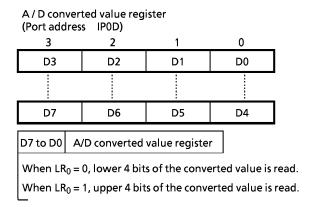

(4) A/D converted value register (IP0D)

An A/D converted value is read by accessing port address IP0D. An A/D converted value is read by splitting into upper 4 bits and lower 4 bits by a value of  $LR_0$  (LSB of the L-registers).

Figure 3-10. A/D converted value register

### 3.6.3 How to use A/D converter

Apply positive of analog reference voltage to the VAREF pin and negative to the VASS pin. The A/D conversion is carried out by splitting reference voltage between VAREF and VASS to bit corresponding voltage by a ladder resistor and making a judgement by comparing it with analog input voltage.

(1) Start of A/D conversion

Prior to conversion, select one of the analog input AIN0 through AIN3 by the analog input selector.

Place output of the analog input, which is to be A/D converted, in the high impedance state by

setting "1". If other port is used as an output, be careful not to execute the output instruction for any port during conversion in order to keep accuracy of conversion.

A/D conversion is started by setting ADS (bit 1 of the A/D conversion start register). When conversion ends after 24 instruction cycles, EOCF showing the end of conversion is set to "1".

Analog input voltage is sampled during the following 2 instruction cycles after setting conversion enable.

Note. The sample and hold circuit has capacitor ( $C_A = 12 \text{ pF typ.}$ ) with resistor ( $RA = 5 \text{ k}\Omega \text{ typ.}$ ). See I/O circuitry table. This capacitor should be charged or discharged within 2 instruction cycles.

### (2) Reading of an A/D converted value

After the end of conversion, read an A/D converted value is read by splitting into lower 4 bits and upper 4 bits by the A/D converted value register (IPOD).

Lower 4 bits of the A/D converted value can be read when  $LR_0 = 0$  and upper 4 bits when  $LR_0 = 1$ . Usually an A/D converted value is stored in RAM by an instruction [IN %p, @HL]. Further, if an A/D converted value is read during the conversion, it becomes an indefinite value.

Example: Selecting analog input (AIN3), starting A/D conversion, monitoring EOCF and storing lower 4 bits and upper 4 bits of a converted value to RAM [10<sub>H</sub>] and RAM [11<sub>H</sub>] respectively.

LD A, #3 ; Selecting analog input (AIN3) OUT A, %OP12 LD A. #1 ; Start of A/D conversion A, %OP13 OUT SLOOP: **TEST** %IPOC, 3 ; To wait until EOCF goes to "1" SL00P В LD HL, #10H ; HL ← 10<sub>H</sub> %IPOD, @HL ; RAM [10<sub>H</sub>]  $\leftarrow$  Lower 4 bits IN ; Increment of L registers INC %IPOD, @HL ; RAM  $[11_H] \leftarrow Upper 4 bits$ IN

#### 3.7 LCD Driver

The 47C446A has the circuit that directly drivers the Liquid Crystal Display (LCD) and its control circuit. The 47C446A has the following connecting pins with LCD.

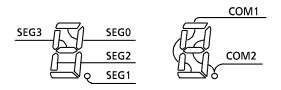

- ① Segment output pins 24 pins (SEG23 to SEG0)

- ② Common output pins 4 pins (COM4 to COM1)

In addition, VLC pin is provided as the driver power.

The devices that can be directly driven is selectable from LCD of following drive methods:

| ① 1/4 duty (1/3 bias) LCD | Max.96 segments (8 segments x 12 | digits) |

|---------------------------|----------------------------------|---------|

| ② 1/3 duty (1/3 bias) LCD | Max.72 segments (8 segments × 9  | digits) |

| ③ 1/2 duty (1/2 bias) LCD | Max.48 segments (8 segments × 6  | digits) |

| 4 Static LCD              | Max.24 segments (8 segments × 3  | digits) |

# 3.7.1 Configuration of LCD driver

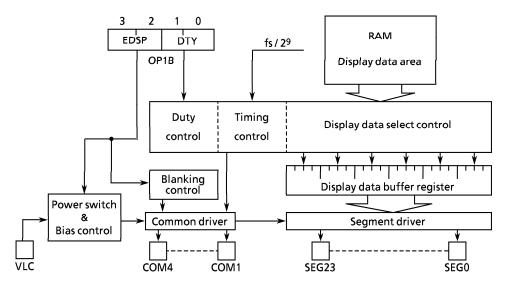

Figure 3-11 shows the configuration of LCD driver.

Figure 3-11. Configuration of LCD Driver

## 3.7.2 Control of LCD Driver

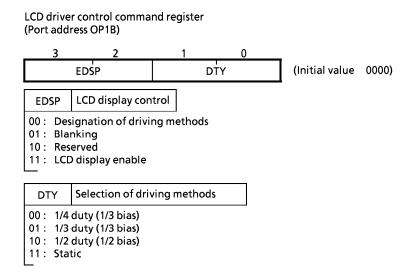

The LCD driver is controlled by the command register (OP1B).

Figure 3-12 shows the configuraation of LCD dreiver.

Figure 3-12. LCD Driver Control Command Register

### (1) Driving methods of LCD

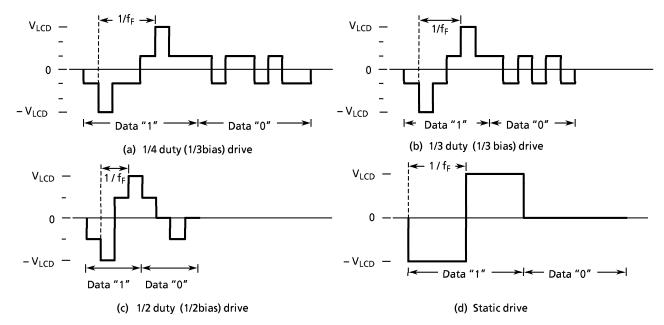

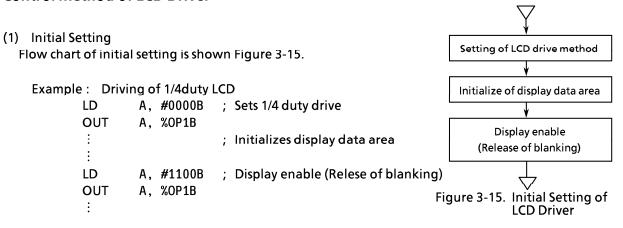

4 kinds of driving methods can be selected by DTY (bits 1 and 0 of OP1B). Figure 3-13 shows driving waveforms for LCD.

Note. :  $f_F$ ; LCD Frame frequency  $V_{LCD}$ ; LCD drive voltage ( =  $V_{DD}$  to  $V_{LC}$ )

Figure 3-13. Driving Waveform for LCD (Voltage COM-SEG Pins)

#### (2) Frame frequency

The frame frequency is set according to the driving method and base frequency as shown in Table 3-3. The base frequency is given by the Interval Timer.

| Delition                     |                | Frame Frequenc   | cy [Hz]  |                |

|------------------------------|----------------|------------------|----------|----------------|

| Base Method<br>Frequency[Hz] | 1/4 duty       | 1/3 duty         | 1/2 duty | static         |

| fs                           | fs             | 4 fs             | 4 fs     | fs             |

| 2 <sup>9</sup>               | 2 <sup>9</sup> | 3 2 <sup>9</sup> | 2 29     | 2 <sup>9</sup> |

| At fs = 32.768 kHz           | 64             | 85               | 128      | 64             |

Table 3-3. Frame Frequency Setting

fs; Basic clock frequency [Hz]

#### (3) LCD drive voltage

The LCD drive voltage ( $V_{LCD}$ ) is given by the difference in potential ( $V_{DD}$  to  $V_{LC}$ ) between pins VDD and VLC. Therefore, when the CPU operating voltage and LCD drive voltage are the same, the VLC pin is connected to the VSS pin.

The LCD light only when the difference in potential between the segment output and common output is  $\pm V_{LCD}$ , and turn off at all other times.

During reset, the power switch of the LCD driver is turned off automatically, shutting off the VLC voltage. Both the segment output and common output become V<sub>DD</sub> level at this time and the LCD turn off.

The power switch is turned on to supply VLC voltage to the LCD driver by setting EDSP (bits 2 and 3 of the command register) to " $11_B$ ". After that, the power switch will not turn off even during blanking (setting EDSP to " $01_B$ ") and the VLC voltage continues to flow.

## 3.7.3 LCD Display Operation

### (1) Display data setting

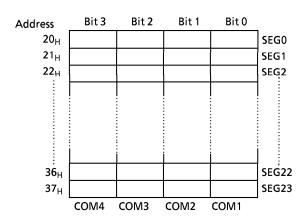

Display data are stored to the display data area (Max. 24 words) in the data memory.

The display data stored to the display data area are read automatically and sent to the LCD driver by the hardware.

The LCD driver generates the segment signals and common signals in accordance with the display data and drive method. Thus, display patterns can be changed by merely overwriting the contents of the display data area with a program. The table look up instruction is mainly used for this overwriting.

Figure 3-14 shows the correspondence between the display data area and the SEG/COM pins. The LCDs light when the display data is "1" and turn off when "0".

The number of segment which can be driven differs depending on the LCD drive method; therefore, the number of display data area bits used to store the data also differs (Refer to Table 3-4). Consequently, data memory not used to store display data and data memory for which the addresses are not connected to LCDs can be used to store ordinary user's processing data.

Table 3-4. Driving Method and Bit for Display Data

|                |       |       |       | •     |

|----------------|-------|-------|-------|-------|

| Driving Method | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 1/4 duty       | COM4  | сомз  | COM2  | СОМ1  |

| 1/3 duty       | ı     | сомз  | COM2  | сом1  |

| 1/2 duty       | 1     | -     | COM2  | сом1  |

| Static         | -     | -     | -     | сом1  |

Note. -; This bit is not used for display data.

Figure 3-14. Display Data Area and SEG/COM

#### (2) Blanking

Blanking is applied by setting EDSP to " $01_B$ " and turns off the LCD by outputting the non light operation level to the COM pin. The SEG pin continuously outputs the signal level in accordance the display data and drive method.

With static drive, no voltage is applied between the COM and SEG pins when the LCD is turned off by data (display data cleared to "0"), but the COM pin output becomes constant at the  $V_{LCD}/2$  level when turning off the LCD by blanking, so the COM and SEG pins are then driven by  $V_{LCD}/2$ .

#### 3.7.4 Control Method of LCD Driver

## (2) Display data setting

Normally, display data are kept permanently in the program memory and are then stored to the display data area by the table look-up instruction.

The example of the program displayed with the table look-up instruction and driving outputs are referred to the technical document of the 47C221A/421A.

The COM, SEG and the LCD which are connected with the 1/4 duty LCD are shown in Figure 3-16, and the display and data are shown in Table 3-5.

Figure 3-16. Example of COM and SEG Connections

Table 3-5. Examples of Display Data (1/4 Duty LCD)

| Numeral | Display                                 | Displa | y data | Numeral | Display | Displa | y data |

|---------|-----------------------------------------|--------|--------|---------|---------|--------|--------|

| Numera  | ызріау                                  | Upper  | Lower  | Numera  | Бізріцу | Upper  | Lower  |

| 0       |                                         | 1101   | 1111   | 5       |         | 1011   | 0101   |

| 1       | *************************************** | 0000   | 0110   | 6       |         | 1111   | 0101   |

| 2       |                                         | 1110   | 0011   | 7       |         | 0001   | 0111   |

| 3       | *************************************** | 1010   | 0111   | 8       |         | 1111   | 0111   |

| 4       | **************************************  | 0011   | 0110   | 9       |         | 1011   | 0111   |

Example 2: Table 3-6 shows the same numerical display used in Table 3-5, but using 1/2 duty LCD are the same as those shown in Figure 3-17.

Figure 3-17. Example of COM and SEG Connections

Table 3-6. Examples of Display Data (1/2 Duty LCD)

| Num  |       | Displa | y data |       | Num  |       | Displa | y data |       |

|------|-------|--------|--------|-------|------|-------|--------|--------|-------|

| eral | Upper |        | I      | _ower | eral | Upper |        | I      | Lower |

| 0    | **01  | **11   | **01   | **11  | 5    | **11  | **10   | **01   | **01  |

| 1    | **00  | **10   | **00   | **10  | 6    | **11  | **11   | **01   | **01  |

| 2    | **10  | **01   | **01   | **11  | 7    | **01  | **10   | **00   | **11  |

| 3    | **10  | **10   | **01   | **11  | 8    | **11  | **11   | **01   | **11  |

| 4    | **11  | **10   | **00   | **10  | 9    | **11  | **10   | **01   | **11  |

Note. \*; don't care

# INPUT / OUTPUT CIRCUITRY

(1) Control pins

Input / Output circuitries of the 47C446A control pins are shown below.

| CONTROL PIN   | I/O             | CIRCUITRY                                 | REMARKS                                                                                                                                                                                |

|---------------|-----------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN<br>XOUT   | INPUT<br>OUTPUT | OSC. enable R <sub>f</sub> R <sub>O</sub> | Resonator connecting pins $ (\text{High frequency}) \\ R = 1  \text{k}\Omega \ (\text{typ.}) \\ R_f = 1.5  \text{M}\Omega \ (\text{typ.}) \\ R_O = 2  \text{k}\Omega \ (\text{typ.}) $ |

| XTIN<br>XTOUT | INPUT<br>OUTPUT | R R R RO                                  | Resonator connecting pins (Low frequency) $R = 1 \text{ k}\Omega \text{ (typ.)}$ $R_f = 15 \text{ M}\Omega \text{ (typ.)}$ $R_O = 200 \text{ k}\Omega \text{ (typ.)}$                  |

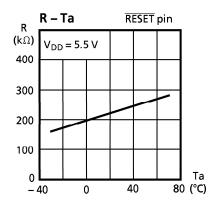

| RESET         | INPUT           | R <sub>IN</sub> R R                       | Hysteresis input Pull-up resistor $R_{\text{IN}} = 220 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$                                                          |

| TEST          | INPUT           | R <sub>IN</sub> W                         | Contained pull-down resistor $R_{\text{IN}} = 70 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$                                                                |

# (2) I/O Ports

The input / output circuitries of the 47C446A I/O ports are shown as below, any one of the circuitries can be chosen by a code (SA to SF) as a mask option.

| PORT     | 1/0   |                           | UT/OUTPUT CIR |                   |                                                                                                                                                                                                                                                                                                                                                                         | REMARKS                                                                                                                             |

|----------|-------|---------------------------|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

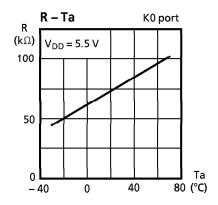

| К0       | Input | SA, SD  R R               | SB,           | od<br><b>∧-</b> □ | SC, SF  R <sub>IN</sub> | Pull-up/pull-down resistor $R_{\text{IN}} = 70 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$               |

| R4       | I/O   | C <sub>A</sub>            | AIN selector  | //// \$R          |                                                                                                                                                                                                                                                                                                                                                                         | Sink open drain output Initial "Hi-Z" $R = 1 \ k\Omega \ (typ.)$ Analog input $R_A = 5 \ k\Omega \ (typ.)$ $C_A = 12 \ pF \ (typ.)$ |

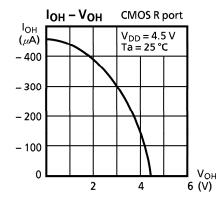

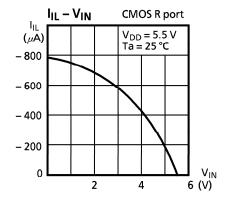

| R5<br>R6 | I/O   | SA, SB, SC Initial "Hi-Z" | R R           | Initial "High'    | SD, SE, SF                                                                                                                                                                                                                                                                                                                                                              | Sink open drain output or push-pull output $R = 1  \mathrm{k}\Omega  \text{(typ.)}$                                                 |

| R7       | I/O   |                           |               |                   |                                                                                                                                                                                                                                                                                                                                                                         | Sink open drain<br>output<br>Initial "Hi-Z"<br>R = 1 kΩ (typ.)                                                                      |

| R8<br>R9 | 1/0   |                           |               |                   | ]                                                                                                                                                                                                                                                                                                                                                                       | Sink open drain output Initial "Hi-Z" Hysteresis input $R = 1  k\Omega  (typ.)$                                                     |

## **ELECTRICAL CHARACTERISTICS**

ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0 V)$

| PARAMETER                                    | SYMBOL            | PINS                                       | RATING                         | UNIT |

|----------------------------------------------|-------------------|--------------------------------------------|--------------------------------|------|

| Supply Voltage                               | V <sub>DD</sub>   |                                            | – 0.3 to 7                     | V    |

| Supply Voltage (LCD drive)                   | $V_{LC}$          |                                            | - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |

| Input Voltage                                | V <sub>IN</sub>   |                                            | - 0.3 to V <sub>DD</sub> + 0.3 | V    |

|                                              | V <sub>OUT1</sub> | Ports R4, R (push-pull)                    | - 0.3 to V <sub>DD</sub> + 0.3 | .,   |

| Output Voltage                               | V <sub>OUT2</sub> | Except sink open drain pin, but include R4 | - 0.3 to 10                    | V    |

| Output Current (per 1 pin)                   | I <sub>OUT</sub>  |                                            | 3.2                            | mA   |

| Power Dissipation $[T_{opr} = 70 \degree C]$ | PD                |                                            | 600                            | mW   |

| Soldering Temperature (time)                 | T <sub>sld</sub>  |                                            | 260 (10 s)                     | °C   |

| Storage Temperature                          | T <sub>stg</sub>  |                                            | – 55 to 125                    | °C   |

| Operating Temperature                        | T <sub>opr</sub>  |                                            | – 30 to 70                     | °C   |

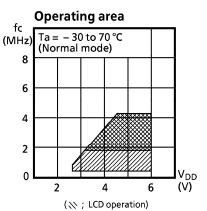

RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0 \text{ V}, T_{opr} = -30 \text{ to } 70 \text{ °C})$

| PARAMETER                       | SYMBOL           | PINS                    | CONDITIONS              | Min.                   | Max.                   | UNIT |

|---------------------------------|------------------|-------------------------|-------------------------|------------------------|------------------------|------|

| Supply Voltage                  |                  |                         | In the Normal mode      | 4.5                    |                        |      |

|                                 | V <sub>DD</sub>  |                         | In the SLOW mode        | 2.7                    | 6.0                    | V    |

| Input High Voltage              | V <sub>IH1</sub> | Except Hysteresis Input | V >45V                  | $V_{DD} \times 0.7$    | -                      |      |

|                                 | V <sub>IH2</sub> | Hysteresis Input        | V <sub>DD</sub> ≧4.5 V  | V <sub>DD</sub> × 0.75 | V <sub>DD</sub>        | V    |

|                                 | V <sub>IH3</sub> |                         | V <sub>DD</sub> <4.5 V  | $V_{DD} \times 0.9$    |                        |      |

| Input Low Voltage               | V <sub>IL1</sub> | Except Hysteresis Input | V >45V                  |                        | $V_{DD} \times 0.3$    |      |

|                                 | V <sub>IL2</sub> | Hysteresis Input        | V <sub>DD</sub> ≧ 4.5 V | 0                      | V <sub>DD</sub> × 0.25 | v    |

|                                 | V <sub>IL3</sub> |                         | V <sub>DD</sub> <4.5 V  |                        | V <sub>DD</sub> × 0.1  |      |

| Clock Frequency<br>(High freq.) | fc               | XIN, XOUT               |                         | 0.4                    | 4.2                    | MHz  |

| Clock Frequency<br>(Low freq.)  | fs               | XTIN, XTOUT             |                         | 30.0                   | 34.0                   | kHz  |

Note 1. Input Voltage  $V_{IH3}$ ,  $V_{IL3}$ : in the SLOW mode

D.C. CHARACTERISTICS

$(V_{SS} = 0 \text{ V}, T_{opr} = -30 \text{ to } 70 \text{ °C})$

|                                        |                   |                                             |                                                            | 1    |      |      |      |

|----------------------------------------|-------------------|---------------------------------------------|------------------------------------------------------------|------|------|------|------|

| PARAMETER                              | SYMBOL            | PINS                                        | CONDITIONS                                                 | Min. | Тур. | Max. | UNIT |

| Hysteresis Voltage                     | V <sub>HS</sub>   | Hysteresis Input                            |                                                            | _    | 0.7  | _    | V    |

| Input Current                          | I <sub>IN1</sub>  | Port K0, TEST, RESET                        | V <sub>DD</sub> = 5.5 V,                                   |      |      |      |      |

|                                        | I <sub>IN2</sub>  | Ports R (open drain)                        | V <sub>IN</sub> = 5.5 V / 0 V                              |      | _    | ± 2  | μA   |

| Low Input Current                      | I <sub>IL</sub>   | Ports R (push-pull)                         | $V_{DD} = 5.5 \text{ V}, \ V_{IN} = 0.4 \text{ V}$         | _    | _    | - 2  | mΑ   |

|                                        | R <sub>IN1</sub>  | Port K0 with pull-up/pull-<br>down resistor |                                                            | 30   | 70   | 150  | kΩ   |

| Input Resistance                       | R <sub>IN2</sub>  | RESET                                       |                                                            | 100  | 220  | 450  |      |

| Output Leakage<br>Current              | I <sub>LO</sub>   | Ports R (open drain)                        | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V          | _    | _    | 2    | μA   |

| Output High Voltage                    | V <sub>OH</sub>   | Ports R (push-pull)                         | $V_{DD} = 4.5 \text{ V}, I_{OH} = -200 \ \mu\text{A}$      | 2.4  | _    | _    | V    |

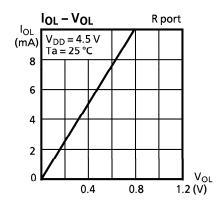

| Output Low Voltage                     | V <sub>OL2</sub>  | Except XOUT                                 | $V_{DD} = 4.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$          | _    | _    | 0.4  | v    |

| Segment Output Low<br>Resistance       | R <sub>OS1</sub>  | SEG pin                                     |                                                            |      |      |      |      |

| Common Output Low<br>Resistance        | R <sub>OC1</sub>  | COM pin                                     |                                                            |      | 20   | _    |      |

| Segment Output High<br>Resistance      | R <sub>OS2</sub>  | SEG pin                                     |                                                            |      |      |      | kΩ   |

| Common Output High<br>Resistance       | R <sub>OC2</sub>  | COM pin                                     | $V_{DD} = 5 \text{ V}, V_{DD} - V_{LC} = 3 \text{ V}$      |      | 200  | _    |      |

| Segment / Common Output Voltage        | V <sub>O2/3</sub> |                                             |                                                            | 3.8  | 4.0  | 4.2  |      |

|                                        | V <sub>O1/2</sub> | SEG / COM pin                               |                                                            | 3.3  | 3.5  | 3.7  | V    |

|                                        | V <sub>O1/3</sub> |                                             |                                                            | 2.8  | 3.0  | 3.2  |      |

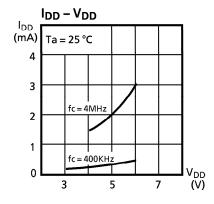

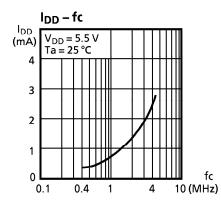

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>   |                                             | $V_{DD} = 5.5 \text{ V}, V_{LC} = V_{SS}$<br>fc = 4 MHz    | _    | 3    | 6    | mA   |

| Supply Current<br>(in the SLOW mode)   | I <sub>DDS</sub>  |                                             | $V_{DD} = 3 \text{ V}, V_{LC} = V_{SS}$<br>fs = 32.768 kHz | _    | 15   | 30   | μA   |

- Note 1. Typ. values shows those at  $T_{opr} = 25 \,^{\circ}\text{C}$ ,  $V_{DD} = 5 \,^{\circ}\text{V}$ .

- Note 2. Input Current  $I_{IN1}$ : The current through resistor is not included, when the input resistor (pull-up/pull-down) is contained.

- Note 3. Output Resistance  $R_{\text{os}}$ ,  $R_{\text{oc}}$ : Shows on-resistance at the level switching.

- Note 4.  $V_{O2/3}$ : Shows 2/3 level output voltage, when the 1/4 or 1/3 duty LCD is used.

- $V_{O1/2}$ : Shows 1/2 level output voltage, when the 1/2 duty or static LCD is used.

- $V_{O1/3}$ : Shows 1/3 level output voltage, when the 1/4 or 1/3 duty LCD is used.

- Note 5. Supply Current  $I_{DD}$ :  $V_{IN} = 5.3 \text{ V} / 0.2 \text{ V}$

The Port KO is open when the input resistor is contained.

The voltage applied to the Port R is within the valid range.

Note 6. Supply Current  $I_{DDS}$ :  $V_{IN} = 2.8 \text{ V} / 0.2 \text{ V}$ . Only low frequency clock is only osillated (connecting

XTIN, XTOUT).

- Note 7. When using LCD, it is necessary to consider values of R<sub>OS1/2</sub> and R<sub>OC1/2</sub>.

- Note 8. Timers for SEG / COM output resistance switching on:

ROS1, ROC1: 2/fs (s)

$R_{OS2}$ ,  $R_{OC2}$ :  $1/(n \cdot f_F)$  (1/n: duty,  $f_F$ : frame frequency)

## A / D CONVERSION CHARACTERISTICS

$(T_{opr} = -30 \text{ to } 70 \,^{\circ}\text{C})$

| PARAMETER                      | SYMBOL             | CONDITIONS                                                                                               | Min.                  | Тур. | Max.              | UNIT |

|--------------------------------|--------------------|----------------------------------------------------------------------------------------------------------|-----------------------|------|-------------------|------|

| Analog Reference Voltage       | VAREF              |                                                                                                          | V <sub>DD</sub> – 1.5 | _    | V <sub>DD</sub>   | .,   |

|                                | V <sub>ASS</sub>   |                                                                                                          | V <sub>SS</sub>       | _    | 1.5               | V    |

| Analog Reference Voltage Range | △V <sub>AREF</sub> | V <sub>AREF</sub> - V <sub>ASS</sub>                                                                     | 2.5                   | _    | -                 | V    |

| Analog Input Voltage           | V <sub>AIN</sub>   |                                                                                                          | V <sub>ASS</sub>      | _    | V <sub>AREF</sub> | V    |

| Analog Supply Current          | I <sub>REF</sub>   |                                                                                                          | _                     | 0.5  | 1.0               | mA   |

| Nonlinearity Error             |                    |                                                                                                          | _                     | -    | ± 1               |      |

| Zero Point Error               |                    | $V_{DD} = 5.0 \text{ V}, V_{SS} = 0.0 \text{ V}$ $V_{AREF} = 5.00 \text{ V}$ $V_{ASS} = 0.000 \text{ V}$ | _                     | _    | ± 1               | LSB  |

| Full Scale Error               |                    |                                                                                                          | _                     | _    | ± 1               |      |

| Total Error                    |                    |                                                                                                          | _                     | _    | ± 2               |      |

## A. C. CHARACTERISTICS

(V<sub>SS</sub> = 0 V, V<sub>DD</sub> = 4.5 to 6.0 V,  $T_{opr}$  = -30 to 70 °C)

| PARAMETER SYMBO              |                  | CONDITIONS          | Min.                      | Тур. | Max. | UNIT |

|------------------------------|------------------|---------------------|---------------------------|------|------|------|

| Instruction Cycle Time       | t <sub>cy</sub>  | In the Normal mode  | 1.9                       | _    | 20   | μs   |

|                              |                  | In the SLOW mode    | 235                       | _    | 267  |      |

| High level Clock pulse Width | t <sub>WCH</sub> | External clock mode | 80                        |      | -    | ns   |

| Low level Clock pulse Width  | t <sub>WCL</sub> | External clock mode |                           |      |      |      |

| A/D Sampling Time            | t <sub>AIN</sub> | fc = 4 MHz          | _                         | 4    | _    | μ\$  |

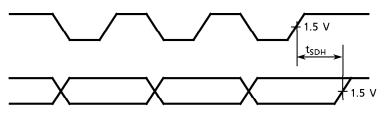

| Shift data Hold Time         | t <sub>SDH</sub> |                     | 0.5 t <sub>cy</sub> – 300 | _    | _    | ns   |

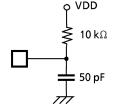

Note. Shift data Hold Time

External circuit for SCK pin and SO pin

Serial port (completion of transmission)

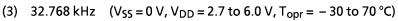

## **RECOMMENDED OSCILLATING CONDITIONS**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}, T_{opr} = -30 \text{ to } 70 ^{\circ}\text{C})$

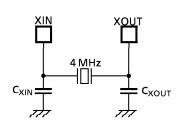

(1) 4 MHz

**Ceramic Resonator**

CSA4. 00MG (MURATA)  $C_{XIN} = C_{XOUT} = 30 \text{ pF}$ KBR-4. 00MS (KYOCERA)  $C_{XIN} = C_{XOUT} = 30 \text{ pF}$

**Crystal Oscillator**

204B-6F 4. 0000 (TOYOCOM)  $C_{XIN} = C_{XOUT} = 20 pF$

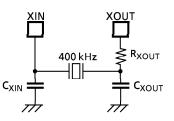

(2) 400 kHz

**Ceramic Resonator**

CSB400B (MURATA)  $C_{XIN} = C_{XOUT} = 220 \text{ pF}, R_{XOUT} = 6.8 \text{ k}\Omega$

KBR-400B (KYOCERA)  $C_{XIN} = C_{XOUT} = 100 \text{ pF, } R_{XOUT} = 10 \text{ k}\Omega$

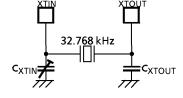

Crystal Oscillator C<sub>XTIN</sub>, C<sub>XTOUT</sub>; 10 to 33 pF

Note: In order to get the accurate oscillation frequency, the adjustment of capacitors must be required.

## **TYPICAL CHARACTERISTICS**