# AIRCHIL SEMICONDUCTOR

# **CD4538BC Dual Precision Monostable**

### **General Description**

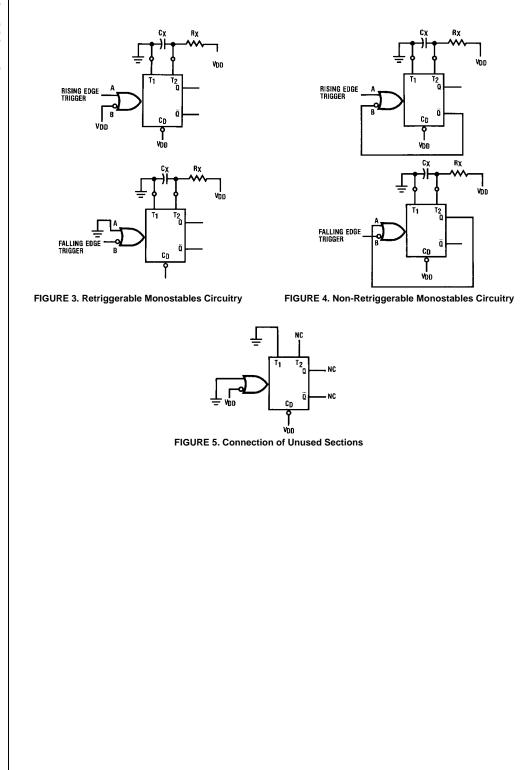

The CD4538BC is a dual, precision monostable multivibrator with independent trigger and reset controls. The device is retriggerable and resettable, and the control inputs are internally latched. Two trigger inputs are provided to allow either rising or falling edge triggering. The reset inputs are active LOW and prevent triggering while active. Precise control of output pulse-width has been achieved using linear CMOS techniques. The pulse duration and accuracy are determined by external components  $R_X$  and  $C_X$ . The device does not allow the timing capacitor to discharge through the timing pin on power-down condition. For this reason, no external protection resistor is required in series with the timing pin. Input protection from static discharge is provided on all pins.

October 1987 Revised April 2002 D4538BC Dual Precision Monostable

#### **Features**

- Wide supply voltage range: 3.0V to 15V

- High noise immunity: 0.45 V<sub>CC</sub> (typ.)

- Low power TTL compatibility: Fan out of 2 driving 74L or 1 driving 74LS

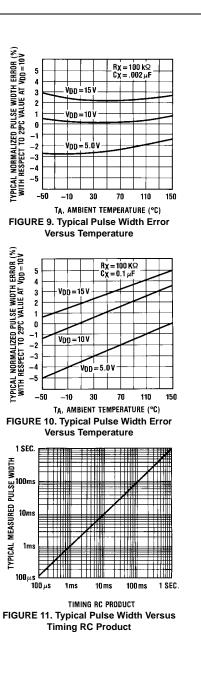

- New formula: PW<sub>OUT</sub> = RC (PW in seconds, R in Ohms, C in Farads)

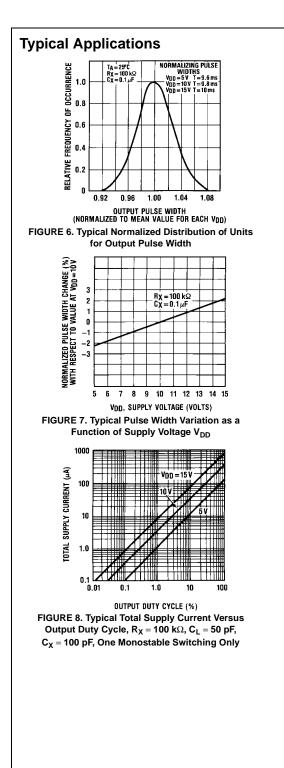

- ±1.0% pulse-width variation from part to part (typ.)

- Wide pulse-width range: 1 µs to ∞

- Separate latched reset inputs

- Symmetrical output sink and source capability

- Low standby current: 5 nA (typ.) @ 5 V<sub>DC</sub>

- Pin compatible to CD4528BC

# **Ordering Code:**

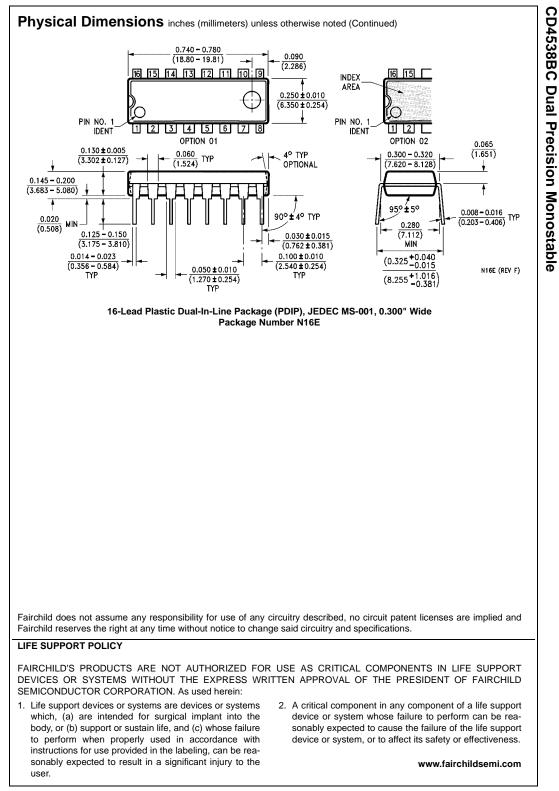

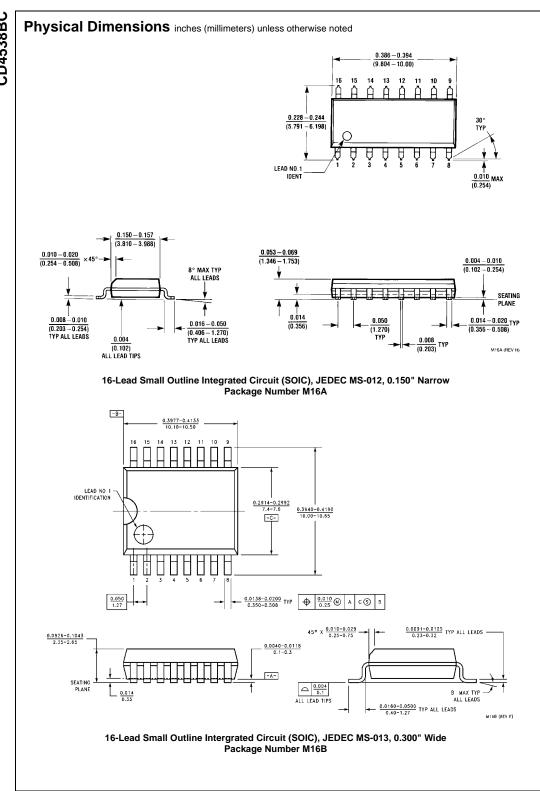

| Order Number           | Package Number            | Package Description                                                          |

|------------------------|---------------------------|------------------------------------------------------------------------------|

| CD4538BCM              | M16A                      | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| CD4538BCWM             | M16B                      | 16-Lead Small Outline Intergrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide  |

| CD4538BCN              | N16E                      | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |

| Devices also available | in Tape and Reel, Specify | by appending the suffix letter "X" to the ordering code.                     |

#### **Truth Table**

| In                                                                                         | Inputs     |              |   | Outputs |  |  |

|--------------------------------------------------------------------------------------------|------------|--------------|---|---------|--|--|

| Clear                                                                                      | Α          | в            | Q | Q       |  |  |

| L                                                                                          | Х          | Х            | L | Н       |  |  |

| х                                                                                          | н          | Х            | L | н       |  |  |

| Х                                                                                          | х          | L            | L | н       |  |  |

| н                                                                                          | L          | $\downarrow$ | л | v       |  |  |

| н                                                                                          | $\uparrow$ | Н            | л | υr      |  |  |

| GH Level<br>W Level<br>ansition from LOW-to<br>ansition from HIGH-t<br>One HIGH Level Puls | o-LOW      | 5            | ¥ | WW      |  |  |

X = Irrelevant

L = ↑ =

1 =

dzsc.com

FIGURE 2.

#### **Trigger Operation**

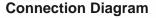

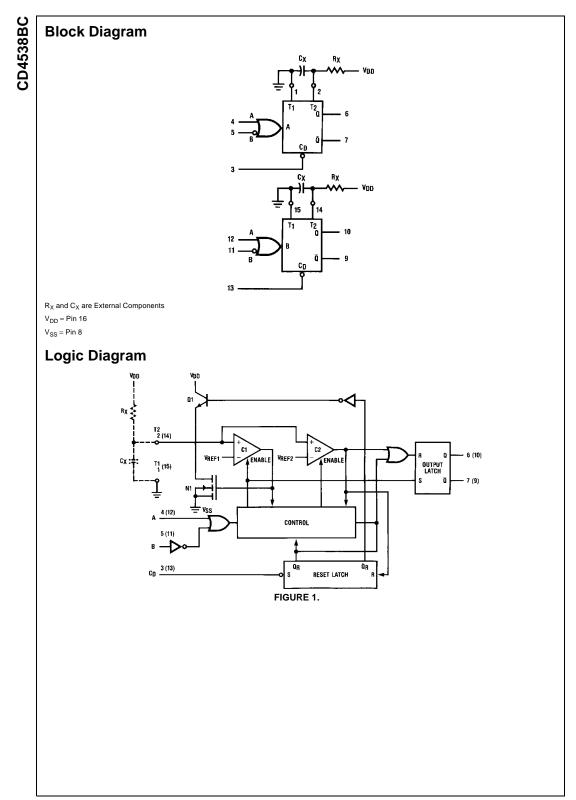

The block diagram of the CD4538BC is shown in Figure 1, with circuit operation following.

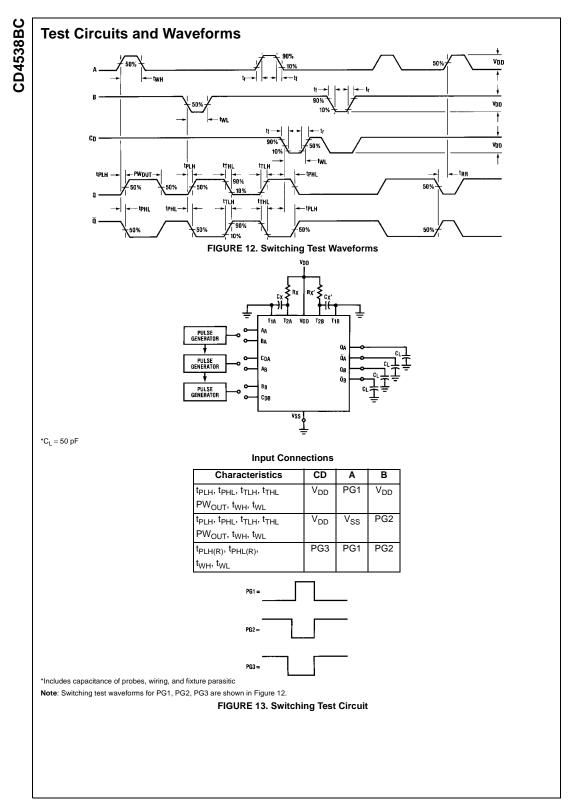

As shown in Figure 1 and Figure 2, before an input trigger occurs, the monostable is in the quiescent state with the Q output low, and the timing capacitor  $C_{\boldsymbol{X}}$  completely charged to  $V_{DD}$ . When the trigger input A goes from  $V_{SS}$  to  $V_{DD}$ (while inputs B and C<sub>D</sub> are held to V<sub>DD</sub>) a valid trigger is recognized, which turns on comparator C1 and N-Channel transistor N1<sup>(1)</sup>. At the same time the output latch is set. With transistor N1 on, the capacitor  $C_{\mathsf{X}}$  rapidly discharges toward  $V_{SS}$  until  $V_{REF1}$  is reached. At this point the output of comparator C1 changes state and transistor N1 turns off. Comparator C1 then turns off while at the same time comparator C2 turns on. With transistor N1 off, the capacitor C<sub>X</sub> begins to charge through the timing resistor,  $R_X$ , toward  $V_{DD}$ . When the voltage across  $C_X$  equals  $V_{REF2}$ , comparator C2 changes state causing the output latch to reset (Q goes low) while at the same time disabling comparator C2. This ends the timing cycle with the monostable in the quiescent state, waiting for the next trigger.

A valid trigger is also recognized when trigger input B goes from  $V_{DD}$  to  $V_{SS}$  (while input A is at  $V_{SS}$  and input  $C_D$  is at  $V_{DD})^{(2)}$ .

It should be noted that in the quiescent state  $C_X$  is fully charged to  $V_{DD},$  causing the current through resistor  $R_X$  to be zero. Both comparators are "off" with the total device current due only to reverse junction leakages. An added feature of the CD4538BC is that the output latch is set via the input trigger without regard to the capacitor voltage. Thus, propagation delay from trigger to Q is independent of the value of  $C_X,\,R_X,$  or the duty cycle of the input waveform.

#### **Retrigger Operation**

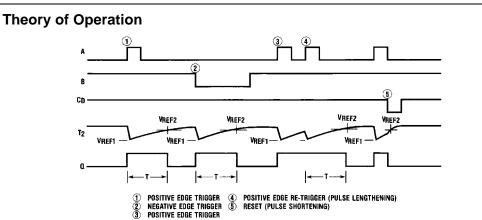

The CD4538BC is retriggered if a valid trigger occurs<sup>(3)</sup> followed by another valid trigger<sup>(4)</sup> before the Q output has returned to the quiescent (zero) state. Any retrigger, after the timing node voltage at pin 2 or 14 has begun to rise from V<sub>REF1</sub>, but has not yet reached V<sub>REF2</sub>, will cause an increase in output pulse width T. When a valid retrigger is initiated<sup>(4)</sup>, the voltage at T2 will again drop to V<sub>REF1</sub> before progressing along the RC charging curve toward V<sub>DD</sub>. The Q output will remain high until time T, after the last valid retrigger.

CD4538BC

#### **Reset Operation**

The CD4538BC may be reset during the generation of the output pulse. In the reset mode of operation, an input pulse on  $C_D$  sets the reset latch and causes the capacitor to be

fast charged to V<sub>DD</sub> by turning on transistor Q1<sup>(5)</sup>. When the voltage on the capacitor reaches V<sub>REF2</sub>, the reset latch will clear and then be ready to accept another pulse. If the C<sub>D</sub> input is held low, any trigger inputs that occur will be inhibited and the Q and  $\overline{Q}$  outputs of the output latch will not change. Since the Q output is reset when an input low level is detected on the C<sub>D</sub> input, the output pulse T can be made significantly shorter than the minimum pulse width specification.

## Absolute Maximum Ratings(Note 1)

| (Note 2)                             | -                                 |

|--------------------------------------|-----------------------------------|

| DC Supply Voltage (V <sub>DD</sub> ) | -0.5 to $+18$ V <sub>DC</sub>     |

| Input Voltage (V <sub>IN</sub> )     | –0.5V to $V_{DD}$ + 0.5 $V_{DC}$  |

| Storage Temperature Range $(T_S)$    | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Power Dissipation (P <sub>D</sub> )  |                                   |

| Dual-In-Line                         | 700 mW                            |

| Small Outline                        | 500 mW                            |

| Lead Temperature (TL)                |                                   |

| (Soldering, 10 seconds)              | 260°C                             |

### **Recommended Operating** Conditions (Note 2)

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed, they are not meant to imply that the devices should be operated at these limits. The tables of "Recom-

DC Supply Voltage (V<sub>DD</sub>) Input Voltage (VIN) Operating Temperature Range (T<sub>A</sub>)

3 to 15  $\mathrm{V}_\mathrm{DC}$ 0 to V<sub>DD</sub> V<sub>DC</sub>

+125°C

150

300

600

0.05

0.05

0.05

Min Max

Max

5

10

20

0.05

0.05

0.05

±10<sup>-t</sup>

±10<sup>-1</sup>

±0.05

±0.1

±0.02

±0.1

-55°C to +125°C

Units

μΑ

V

V

V

V

mΑ

mΑ

μΑ

μΑ

±0.5

±1.0

CD4538BC

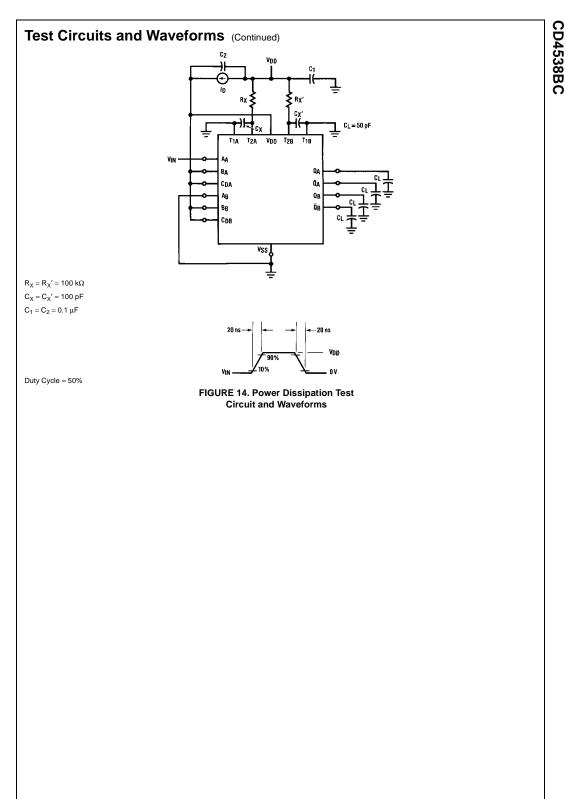

mended Operating Conditions" and "Electrical Characteristics" provide conditions for actual device operation. Note 2:  $V_{SS} = 0V$  unless otherwise specified. c DC Electrical Characteristics (Note 2) -55°C +25°C Symbol Parameter Conditions Min Max Min Тур Quiescent  $I_{DD}$  $V_{DD} = 5V$  $V_{IH} = V_{DD}$ 20 0.005 Device Current  $V_{DD} = 10V$  $V_{IL} = V_{SS}$ 40 0.010  $V_{DD} = 15V$ All Outputs Open 0.015 80 VOL LOW Level  $V_{DD} = 5V$ |I<sub>O</sub>| < 1 μA 0.05 0 Output Voltage  $V_{DD} = 10V$  $V_{IH} = V_{DD}, V_{IL} = V_{SS}$ 0.05 0 0.05  $V_{DD} = 15V$ 0  $V_{DD} = 5V$ HIGH Level  $|I_0| < 1 \, \mu A$ V<sub>OH</sub> 5 4.95 4.95 Output Voltage V<sub>DD</sub> = 10V  $V_{IH} = V_{DD}, \, V_{IL} = V_{SS}$ 9.95 9.95 10  $V_{DD} = 15V$ 14.95 14.95 15 LOW Level  $|I_0| < 1 \ \mu A$ VIL

$V_{DD} = 15V, V_{IN} = 0V \text{ or } 15V$

$V_{DD} = 15V, V_{IN} = 0V \text{ or } 15V$

#### 4.95 9.95 14.95 $V_{DD} = 5V, V_{O} = 0.5V \text{ or } 4.5V$ Input Voltage 1.5 2.25 1.5 1.5 V<sub>DD</sub> = 10V, V<sub>O</sub> = 1.0V or 9.0V 3.0 4.50 3.0 3.0 $V_{DD} = 15V, V_O = 1.5V \text{ or } 13.5V$ 4.0 6.75 4.0 4.0 VIH HIGH Level $|I_0| < 1 \ \mu A$ $V_{DD} = 5V, V_O = 0.5V \text{ or } 4.5V$ Input Voltage 3.5 3.5 2.75 3.5 $V_{DD} = 10V, V_{O} = 1.0V \text{ or } 9.0V$ 5.50 7.0 7.0 7.0 $V_{DD} = 15V, V_O = 1.5V \text{ or } 13.5V$ 11.0 11.0 8.25 11.0 LOW Level $V_{DD} = 5V, V_{O} = 0.4V$ 0.64 0.51 0.88 0.36 IOL $V_{IH} = V_{DD}$ $V_{DD} = 10V, V_O = 0.5V$ $V_{IL} = V_{SS}$ Output Current 1.6 1.3 2.25 0.9 $V_{\rm D} = 15$ V, $V_{\rm O} = 1.5$ V (Note 3) 42 34 88 24 $V_{DD} = 5V, V_{O} = 4.6V$ HIGH Level -0.6 -0.51 -0.88 -0.36 I<sub>OH</sub> V<sub>DD</sub> = 10V, V<sub>O</sub> = 9.5V Output Current -2.25 -0.9 $V_{IL} = V_{SS}$ -1.6 -1.3 (Note 3) $V_{\rm D} = 15 V, V_{\rm O} = 13.5 V$ -4.2 -3.4 -8.8 -2.4

Note 3: I<sub>OH</sub> and I<sub>OL</sub> are tested one output at a time.

Input Current,

Pin 2 or 14 Input Current

Other Inputs

I<sub>IN</sub>

IIN

| C |

|---|

| â |

| ω |

| 3 |

| ŝ |

| Z |

|   |

| C |

Γ

| Symbol                                  | Parameter                                 | Cor                             | nditions       | Min  | Тур   | Max      | Units |

|-----------------------------------------|-------------------------------------------|---------------------------------|----------------|------|-------|----------|-------|

| t <sub>TLH</sub> , t <sub>THL</sub>     | Output Transition Time                    | $V_{DD} = 5V$                   |                | 100  | 200   |          |       |

|                                         |                                           | $V_{DD} = 10V$                  |                | 50   | 100   | ns       |       |

|                                         |                                           | $V_{DD} = 15V$                  |                |      | 40    | 80       |       |

| t <sub>PLH</sub> , t <sub>PHL</sub>     | Propagation Delay Time                    | Trigger Operation—              |                |      |       |          |       |

|                                         | A or B to Q or Q                          |                                 |                |      |       |          |       |

|                                         |                                           | $V_{DD} = 5V$                   |                |      | 300   | 600      |       |

|                                         |                                           | $V_{DD} = 10V$                  |                |      | 150   | 300      | ns    |

|                                         |                                           | $V_{DD} = 15V$                  |                |      | 100   | 220      |       |

|                                         |                                           | Reset Operation—                |                |      | -     |          |       |

|                                         |                                           | $C_{D}$ to Q or $\overline{Q}$  |                |      |       |          |       |

|                                         |                                           | $V_{DD} = 5V$                   |                | 250  | 500   |          |       |

|                                         |                                           | $V_{DD} = 30$<br>$V_{DD} = 10V$ |                |      | 125   | 250      | ns    |

|                                         |                                           | $V_{DD} = 15V$                  |                |      | 95    | 190      |       |

| t <sub>WL</sub> , t <sub>WH</sub>       | Minimum Input Pulse Width                 | $V_{DD} = 5V$                   |                |      | 35    | 70       |       |

|                                         | A, B, or C <sub>D</sub>                   | $V_{\rm DD} = 10V$              |                |      | 30    | 60       | ns    |

|                                         |                                           | $V_{DD} = 15V$                  |                |      | 25    | 50       |       |

| <sup>t</sup> RR                         | Minimum Retrigger Time                    | $V_{DD} = 5V$                   |                |      |       | 0        |       |

|                                         |                                           | $V_{DD} = 10V$                  |                | 0    | 0     | ns       |       |

|                                         |                                           | V <sub>DD</sub> = 15V           |                |      |       | 0        |       |

| C <sub>IN</sub>                         | Input Capacitance                         | Pin 2 or 14                     |                |      | 10    |          | -     |

|                                         |                                           | Other Inputs                    |                | 5    | 7.5   | pF       |       |

| PWOUT                                   | Output Pulse Width (Q or $\overline{Q}$ ) | $R_X = 100 \text{ k}\Omega$     | $V_{DD} = 5V$  | 208  | 226   | 244      |       |

|                                         | (Note: For Typical Distribution,          | $C_X = 0.002 \mu\text{F}$       | $V_{DD} = 10V$ | 211  | 230   | 248      | μs    |

|                                         | see Figure 6)                             |                                 | $V_{DD} = 15V$ | 216  | 235   | 254      |       |

|                                         |                                           | R <sub>X</sub> = 100 kΩ         | $V_{DD} = 5V$  | 8.83 | 9.60  | 10.37    |       |

|                                         |                                           | $C_X = 0.1 \ \mu F$             | $V_{DD} = 10V$ | 9.02 | 9.80  | 10.59    | ms    |

|                                         |                                           |                                 | $V_{DD} = 15V$ | 9.20 | 10.00 | 10.80    |       |

|                                         |                                           | $R_X = 100 \text{ k}\Omega$     | $V_{DD} = 5V$  | 0.87 | 0.95  | 1.03     |       |

|                                         |                                           | $C_X = 10.0 \ \mu F$            | $V_{DD} = 10V$ | 0.89 | 0.97  | 1.05     | s     |

|                                         |                                           |                                 | $V_{DD} = 15V$ | 0.91 | 0.99  | 1.07     |       |

| Pulse Width Match between               |                                           | $R_X = 100 \text{ k}\Omega$     | $V_{DD} = 5V$  |      | ±1    |          |       |

| Circuits in the Same Package            |                                           | $C_X = 0.1 \ \mu F$             | $V_{DD} = 10V$ |      | ±1    |          | %     |

| $C_X = 0.1 \ \mu\text{F}, \ \text{R}_X$ | = 100 kΩ                                  |                                 | $V_{DD} = 15V$ |      | ±1    |          |       |

| Operating Con                           | ditions                                   | <u>.</u>                        |                |      | ·     | •        | ·     |

| R <sub>X</sub>                          | External Timing Resistance                |                                 |                | 5.0  |       | (Note 5) | kΩ    |

| C <sub>X</sub>                          | External Timing Capacitance               |                                 |                | 0    |       | No Limit | pF    |

Note 4: AC parameters are guaranteed by DC correlated testing.

No Limit

pF

Note 5: The maximum usable resistance R<sub>X</sub> is a function of the leakage of the Capacitor C<sub>X</sub>, leakage of the CD4538BC, and leakage due to board layout, surface resistance, etc.

# CD4538BC

**CD4538BC**